AURIX 设备概述(硬件部分)

AUtomotive Realtime Integrated neXt

Generation Architecture

我的理解是像ARM Cortext M3内核一样

�

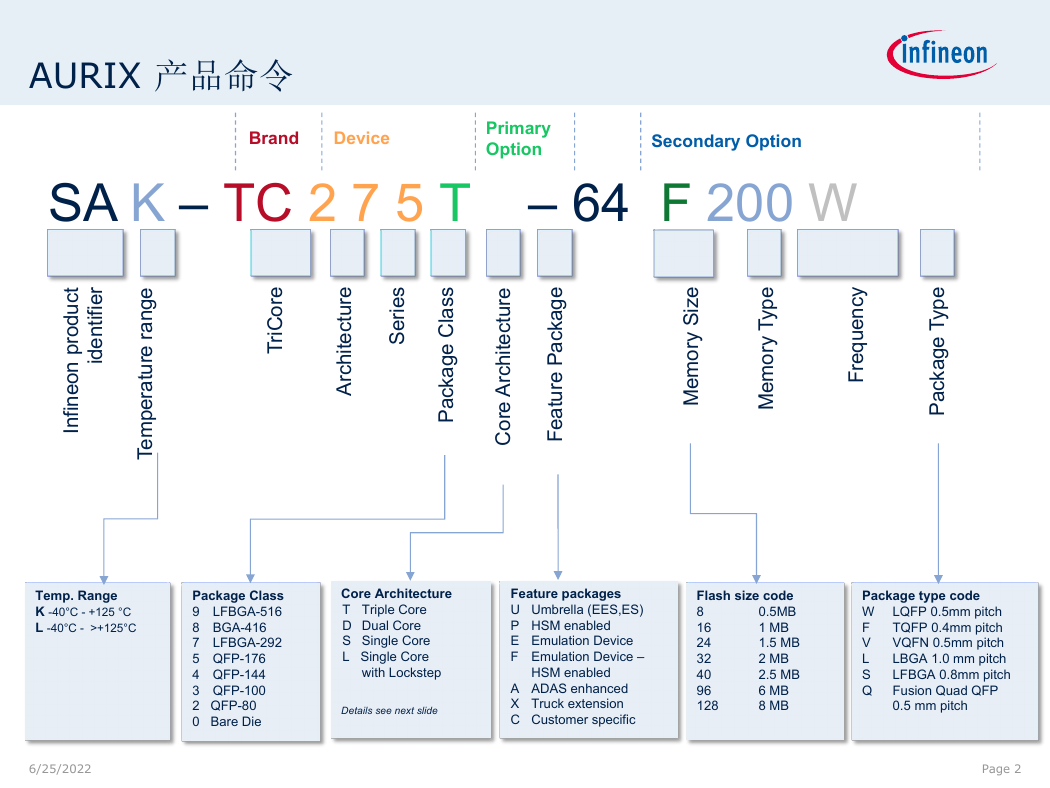

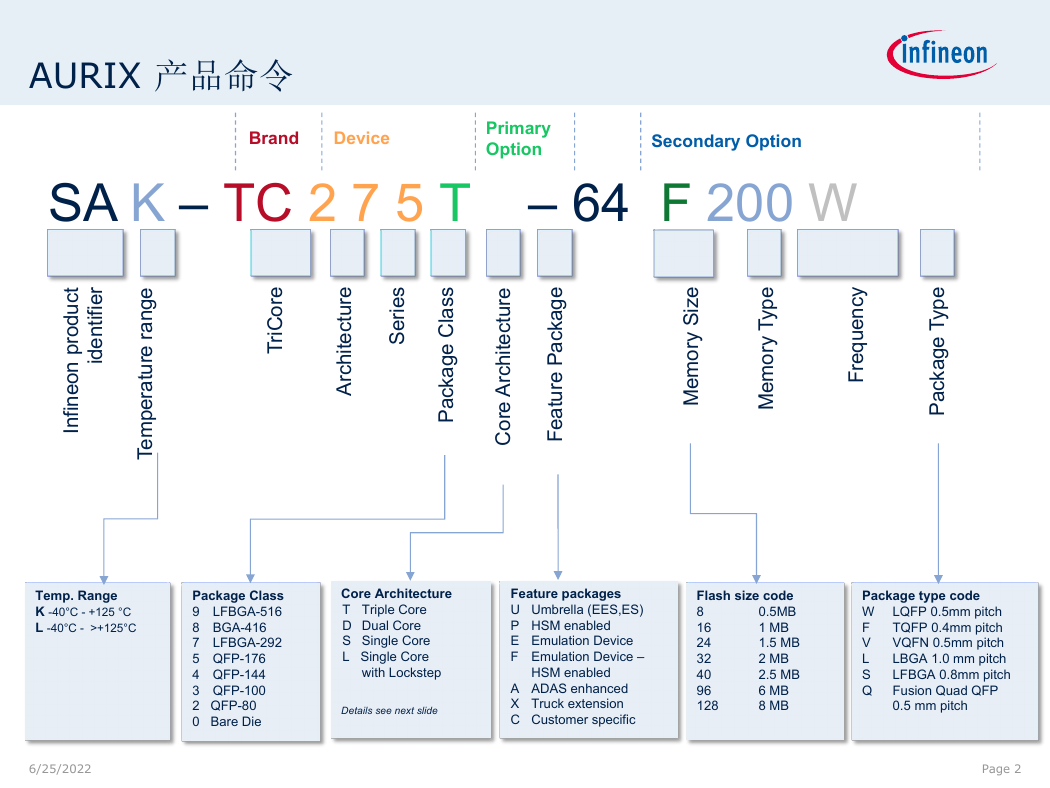

AURIX 产品命令

Brand

Device

Primary

Option

Secondary Option

SA K – TC 2 7 5 T – 64 F 200 W

r

e

i

f

i

t

n

e

d

i

t

c

u

d

o

r

p

n

o

e

n

i

f

n

I

e

r

o

C

i

r

T

s

e

i

r

e

S

e

r

u

t

c

e

t

i

h

c

r

A

e

g

n

a

r

e

r

u

a

r

e

p

m

e

T

t

l

s

s

a

C

e

g

a

k

c

a

P

e

r

u

t

c

e

t

i

h

c

r

A

e

r

o

C

e

g

a

k

c

a

P

e

r

u

a

e

F

t

Temp. Range

K -40°C - +125 °C

L -40°C - >+125°C

Package Class

9 LFBGA-516

8 BGA-416

7 LFBGA-292

5 QFP-176

4 QFP-144

3 QFP-100

2 QFP-80

0 Bare Die

Core Architecture

T Triple Core

D Dual Core

S Single Core

L Single Core

with Lockstep

Details see next slide

Feature packages

U Umbrella (EES,ES)

P HSM enabled

E Emulation Device

F Emulation Device –

HSM enabled

A ADAS enhanced

X Truck extension

C Customer specific

i

e

z

S

y

r

o

m

e

M

e

p

y

T

y

r

o

m

e

M

y

c

n

e

u

q

e

r

F

e

p

y

T

e

g

a

k

c

a

P

Flash size code

0.5MB

8

16

1 MB

1.5 MB

24

2 MB

32

2.5 MB

40

96

6 MB

8 MB

128

Package type code

W LQFP 0.5mm pitch

F

TQFP 0.4mm pitch

VQFN 0.5mm pitch

V

LBGA 1.0 mm pitch

L

LFBGA 0.8mm pitch

S

Q

Fusion Quad QFP

0.5 mm pitch

6/25/2022

Page 2

�

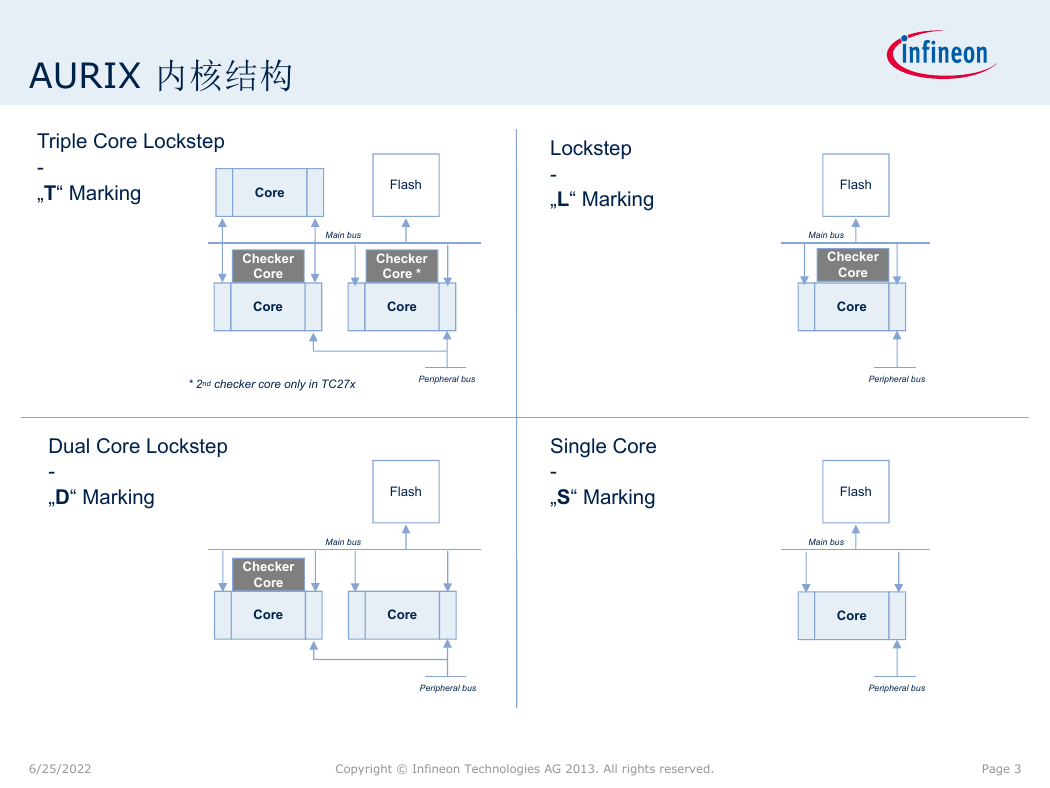

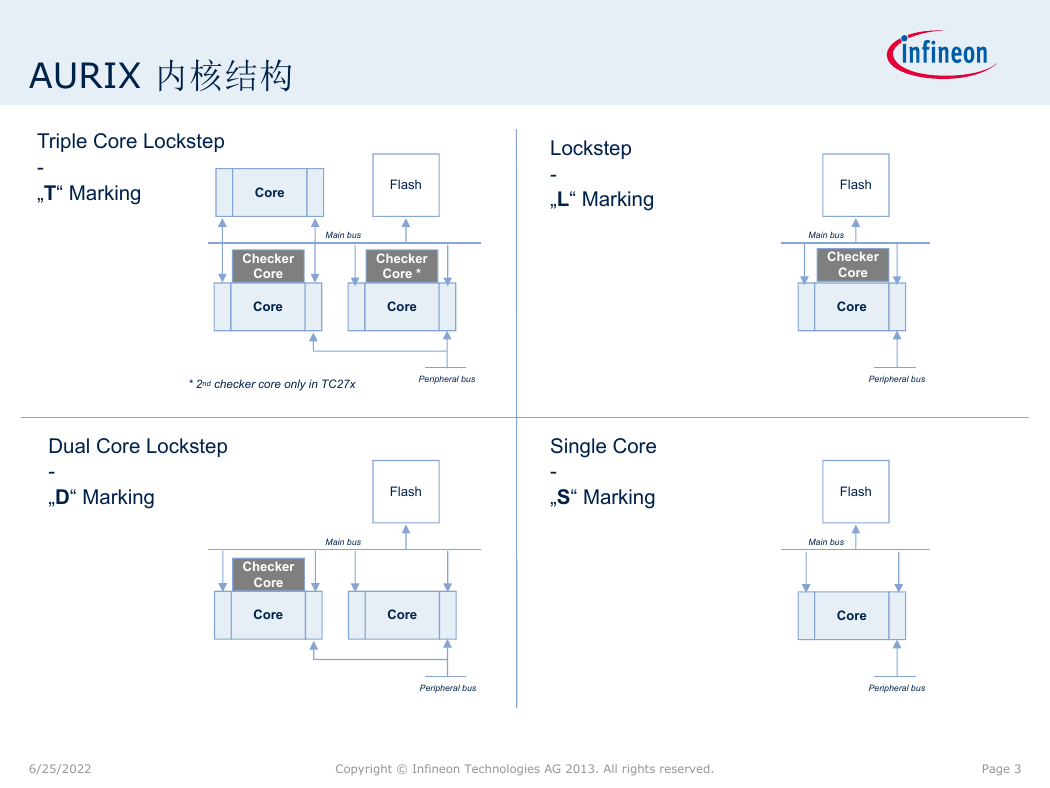

AURIX 内核结构

Triple Core Lockstep

-

„T“ Marking

Core

Checker

Core

Core

Main bus

Flash

Checker

Core *

Core

Lockstep

-

„L“ Marking

Flash

Main bus

Checker

Core

Core

* 2nd checker core only in TC27x

Peripheral bus

Peripheral bus

Dual Core Lockstep

-

„D“ Marking

Flash

Core

Main bus

Checker

Core

Core

Single Core

-

„S“ Marking

Flash

Main bus

Core

Peripheral bus

Peripheral bus

6/25/2022

Copyright © Infineon Technologies AG 2013. All rights reserved.

Page 3

�

TriCore 概述

TC 1.3

TC 1.3.1

TC 1.6

TC 1.6Performance

(version TC 1.6.1)

TC 1.6Efficiency

(version TC 1.6 Scalar)

Architecture

32-bit superscalar

Harvard

32-bit superscalar

Harvard

32-bit superscalar

Harvard

32-bit superscalar

Harvard

32-bit scalar

Harvard

200 MHz

4

1.4+

Max. Frequency

150 MHz

Pipeline stages

DMIPS / MHz

Instruction cache

4

1,55

180 MHz

4

1,68

300 MHz

6

1,7

300 MHz

6

1,7

Two way set associative,

256-bit cache line length

Two way set associative,

256-bit cache line length

Data cache

Not in Automotive

Products

Two way set associative

128-bit cache line length

Four way set associative,

256-bit cache line

length

Two way set associative,

256-bit cache line

length

Two way set associative,

256-bit cache line length

Four way set associative

256-bit cache line

length

Two way set associative

256-bit cache line

length

4 line read buffer or

Two way set associative

256-bit cache line length

HW int. division

unit

No

No

Yes

Yes

Yes

MAC units

FPU

dual 16x16 multipliers

dual 16x32 multipliers

dual 16x32 multipliers

dual 16x32 multipliers

dual 16x32 multipliers

Single precision (32-bit)

Single precision (32-bit)

Single precision (32-bit)

Single precision (32-bit)

Single precision (32-bit)

FPU performance

0,66 FLOPs/cycle

0,66 FLOPs/cycle

2 FLOPs/cycle (pipelined)

2 FLOPs/cycle (pipelined)

2 FLOPs/cycle (pipelined)

User modes

Memory

protection

Supervisor, user 1, user

0

Supervisor, user 1, user 0

Supervisor, user 1, user

0

Supervisor, user 1, user

0

Supervisor, user 1, user

0

2 protection sets

(overlaid HW breakpoints)

4 protection sets

(overlaid HW breakpoints)

4 protection sets

(separate HW

breakpoints)

4 protection sets

(separate HW

breakpoints)

4 protection sets

(separate HW

breakpoints)

Instruction set

16/32 bit instructions

16/32 bit instructions

16/32 bit instructions

16/32 bit instructions

16/32 bit instructions

Compatibility

TC1.2 compatible

TC1.3 compatible

TC1.3.1 compatible

TC1.6 compatible

TC1.6 compatible

Other features

n static branch predictor

n dynamic branch

predictor

n Enhanced branch

pre-diction (branch

history and target

buffers)

n Dual core support

n Safety support

n Dual core capable

n Power consumption

optimized

n Safety support

Status

Production (Audo-NG)

Production (AudoFuture)

Development for 90nm

Development for 65nm

Development for 65nm

6/25/2022

�

系统内部功能模块

�

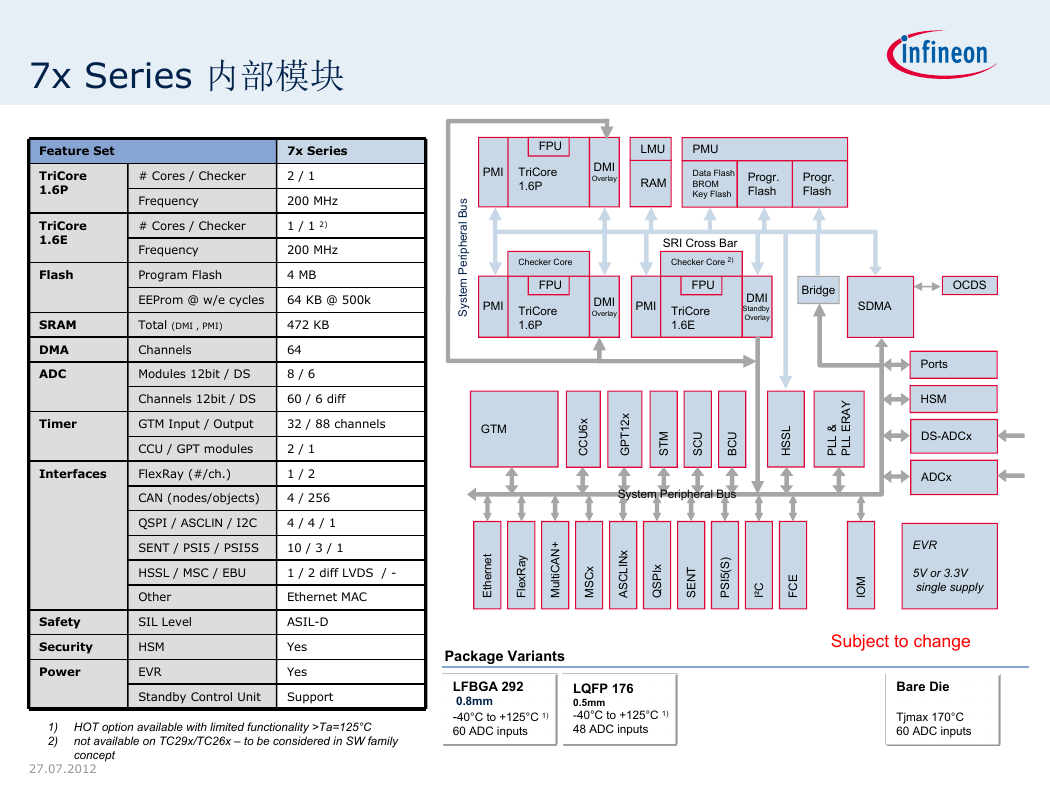

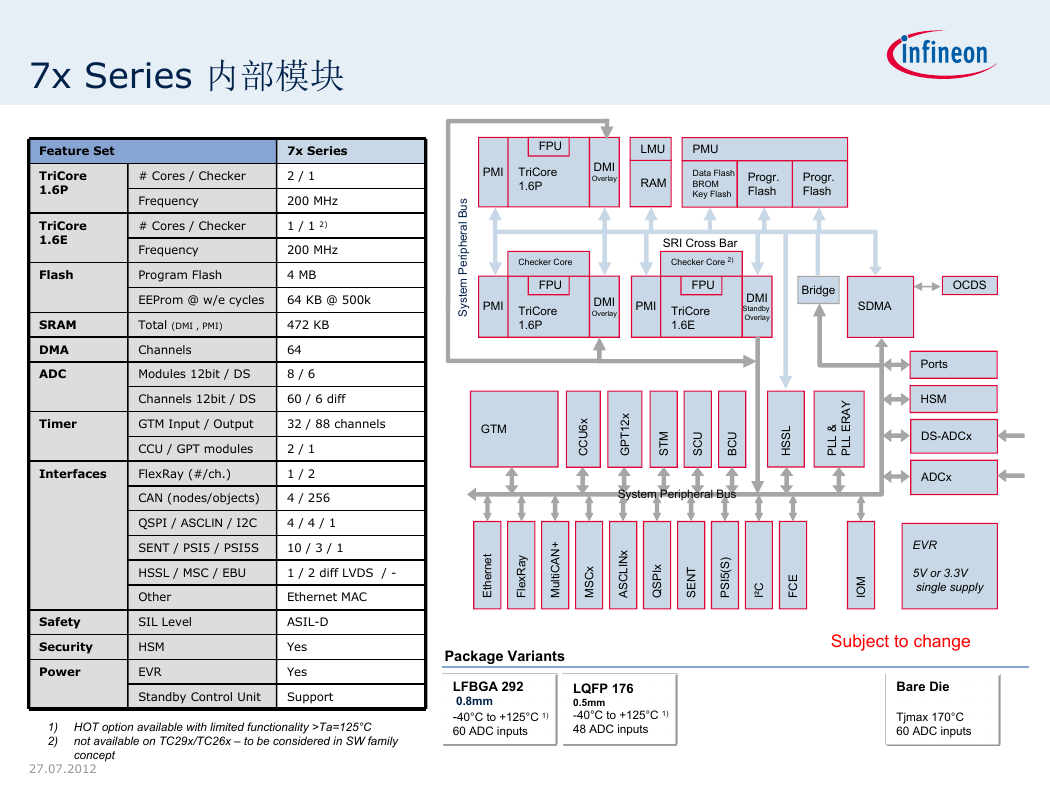

7x Series 内部模块

Feature Set

7x Series

# Cores / Checker

2 / 1

TriCore

1.6P

TriCore

1.6E

Frequency

# Cores / Checker

Frequency

200 MHz

1 / 1 2)

200 MHz

4 MB

Flash

Program Flash

SRAM

DMA

ADC

EEProm @ w/e cycles

64 KB @ 500k

Total (DMI , PMI)

Channels

Modules 12bit / DS

472 KB

64

8 / 6

Channels 12bit / DS

60 / 6 diff

Timer

GTM Input / Output

32 / 88 channels

CCU / GPT modules

Interfaces

FlexRay (#/ch.)

2 / 1

1 / 2

CAN (nodes/objects)

4 / 256

QSPI / ASCLIN / I2C

4 / 4 / 1

SENT / PSI5 / PSI5S

10 / 3 / 1

HSSL / MSC / EBU

1 / 2 diff LVDS / -

Safety

Security

Power

Other

SIL Level

HSM

EVR

Ethernet MAC

ASIL-D

Yes

Yes

Standby Control Unit

Support

1) HOT option available with limited functionality >Ta=125°C

2)

not available on TC29x/TC26x – to be considered in SW family

concept

27.07.2012

s

u

B

l

a

r

e

h

p

i

r

e

P

m

e

t

s

y

S

FPU

LMU

PMU

PMI

TriCore

1.6P

DMI

Overlay

RAM

Data Flash

BROM

Key Flash

Progr.

Flash

Progr.

Flash

Checker Core

FPU

TriCore

1.6P

PMI

DMI

Overlay

PMI

SRI Cross Bar

Checker Core 2)

FPU

TriCore

1.6E

DMI

Standby

Overlay

Bridge

SDMA

OCDS

GTM

x

6

U

C

C

x

2

1

T

P

G

M

T

S

U

C

S

U

C

B

L

S

S

H

System Peripheral Bus

Y

A

R

E

L

L

P

&

L

L

P

Ports

HSM

DS-ADCx

ADCx

+

N

A

C

i

t

l

u

M

y

a

R

x

e

F

l

I

x

N

L

C

S

A

x

C

S

M

x

I

P

S

Q

T

N

E

S

)

S

(

5

S

P

I

C

²

I

E

C

F

M

O

I

EVR

5V or 3.3V

single supply

t

e

n

r

e

h

E

t

Package Variants

LFBGA 292

0.8mm

-40°C to +125°C 1)

60 ADC inputs

LQFP 176

0.5mm

-40°C to +125°C 1)

48 ADC inputs

Subject to change

Bare Die

Tjmax 170°C

60 ADC inputs

�

内核及内存

6/25/2022

Copyright © Infineon Technologies AG 2013. All rights reserved.

Page 7

�

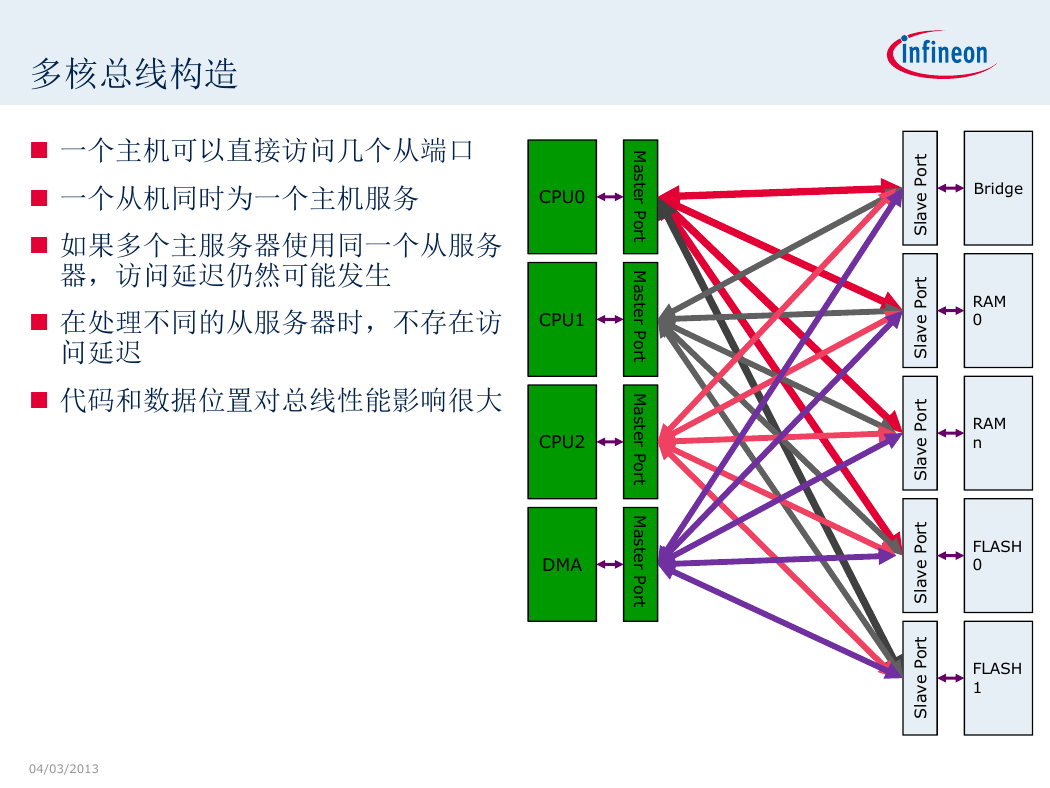

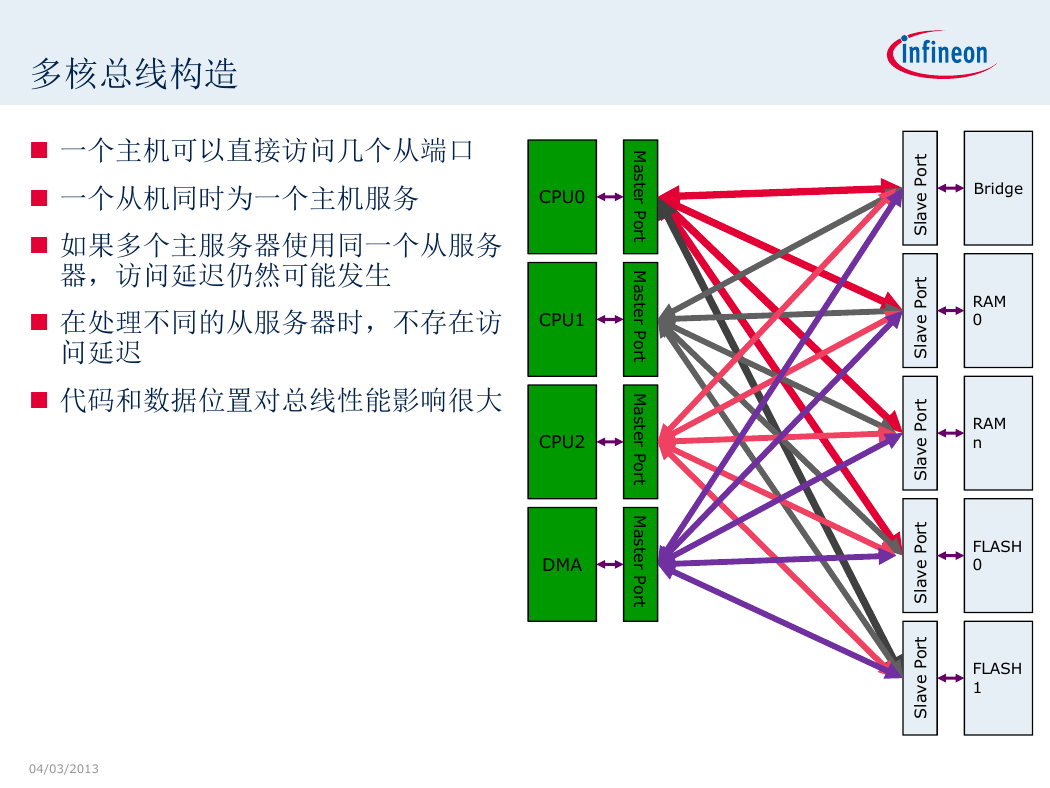

多核总线构造

n 一个主机可以直接访问几个从端口

n 一个从机同时为一个主机服务

CPU0

n 如果多个主服务器使用同一个从服务

器,访问延迟仍然可能发生

n 在处理不同的从服务器时,不存在访

CPU1

问延迟

n 代码和数据位置对总线性能影响很大

CPU2

DMA

M

a

s

t

e

r

P

o

r

t

M

a

s

t

e

r

P

o

r

t

M

a

s

t

e

r

P

o

r

t

M

a

s

t

e

r

P

o

r

t

04/03/2013

t

r

o

P

e

v

a

S

l

t

r

o

P

e

v

a

S

l

t

r

o

P

e

v

a

S

l

t

r

o

P

e

v

a

S

l

t

r

o

P

e

v

a

S

l

Bridge

RAM

0

RAM

n

FLASH

0

FLASH

1

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc