8

第卷 第 期

29

Vol.29

№

8

·工程应用技术与实现·

计 算 机 工 程

Computer Engineering

5

2003

年 月

May 2003

文章编号:——

10003428(2003)08 015602

—

文献标识码:A

中图分类号: TP302.2

FPGAPCI

基于的接口设计

胡和平,田宜波

华中科技大学计算机科学与技术学院,武汉

(430074)

摘要 : 介绍一种使用硬核逻辑进行简单高效的接口设计方法。该方法是在已固化硬核逻辑的中,设计用户逻辑。重点

叙述了中硬核逻辑的原理和结构,分析了时序设计要点。给出了设计实例和注意事项。

关键词: 总线;核;现场可编程逻辑阵列;仿真

PCIPCIPCIFPGAPCI

QL5030PCI

PCIPCI

PCI Interface Design Based on FPGA

(Department of Computer Science and Engineering, Huazhong University of Science and Technology, Wuhan 430074)

HU HepingTIAN Yibo

,

】

【

Abstract A method is introduced for the PCI design by using PCI hardcore logic. The design of PCI user logic is done with this method based on

FPGA where PCI hardcore logic has been embeded.This paper focuses on the principle and architecture of the PCI hardcore logic in QL5030, from

which the key point of time sequencing is analysed. In addition, a design example and some notes are introduced.

【

Peripheral component interconnect busPCI coreFPGASimulation

Key words

;;

;

】

1 PCI

总线及其接口概述

局部总线是高速PCI(Peripheral Component Interconnect)

32bit33MHz

132Mbyte/sCompact PCI64bit

同步总线,具有总线宽度,工作频率,最大传

输率为;而总线,具有总线宽

度,工作频率,最大传输率为。因此,

PCI

66MHz528 Mbyte/s

总线在高速数据通信方面应用前景很广。

PCIMASTER()TARGET(

总线设备分为主设备和从设

PCIPCIPCI

)PCIMASTERTARGET

备,因此,总线接口通信可分为

种方式。总线接口设计包括总线配置寄存器、 总

线逻辑接口、用户设备逻辑接口、数据缓冲区等设计。目前

总线接口设计多采用以下种方法:

PCI3(1)ASIC PCI(2)

;

FPGA + PCI soft IP(3)FPGA +PCI hard IP

和

两

;

。

作为一般应用工程师,多采用后面两种方式进行 接PCI

PCI

PCIPCI

口设计,而不必自己去设计复杂的接口逻辑。这样可以

缩短开发周期,甚至可以不必完全理解总线规范的细

节。而采用硬核逻辑设计接口方法将克服前两种设

计方式的缺点,使得设计更有效、更快。与专用接口芯PCI

片相似,公司将接口核逻辑固化在里。

设计者只需根据要求设计用户设备逻辑接口,并通过顶

层仿真验证接口以及用户设备逻辑设计的正确与否。

QuickLogicPCIFPGA

PCI

PCI

PCI

QL5030PCIT32PCI

本文以为例。介绍利用进行接口设

计的方法及注意事项,并给出具体实例设计。

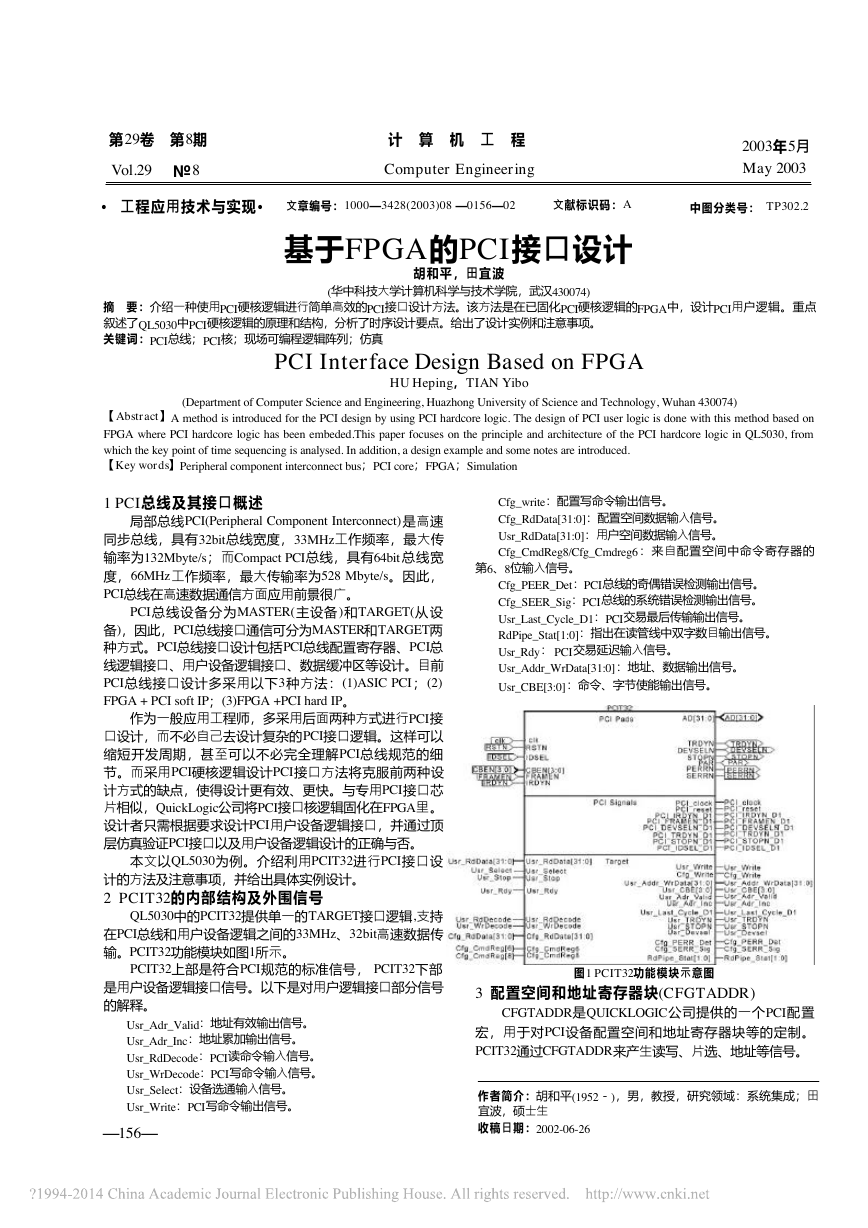

2 PCIT32

的内部结构及外围信号

中的提供单一的接口逻辑支持

,

QL5030PCIT32TARGET

PCI33MHz32bit

在总线和用户设备逻辑之间的、高速数据传

输。功能模块如图所示。

1

上部是符合规范的标准信号,下部

PCIT32

PCIT32

PCIT32PCI

是用户设备逻辑接口信号。以下是对用户逻辑接口部分信号

的解释。

:地址有效输出信号。

:地址累加输出信号。

:读命令输入信号。

:写命令输入信号。

Usr_Adr_Valid

Usr_Adr_Inc

Usr_RdDecodePCI

Usr_WrDecodePCI

Usr_Select

Usr_WritePCI

:设备选通输入信号。

:写命令输出信号。

— —156

:配置写命令输出信号。

Cfg_write

Cfg_RdData[31:0]

Usr_RdData[31:0]

Cfg_CmdReg8/Cfg_Cmdreg6

:配置空间数据输入信号。

:用户空间数据输入信号。

:来自配置空间中命令寄存器的

第 、位输入信号。

6 8

:总线的奇偶错误检测输出信号。

:总线的系统错误检测输出信号。

:交易最后传输输出信号。

:指出在读管线中双字数目输出信号。

Cfg_PEER_DetPCI

Cfg_SEER_SigPCI

Usr_Last_Cycle_D1PCI

RdPipe_Stat[1:0]

Usr_Rdy PCI

Usr_Addr_WrData[31:0]

Usr_CBE[3:0]

:交易延迟输入信号。

:地址、数据输出信号。

:命令、字节使能输出信号。

图功能模块示意图

配置空间和地址寄存器块

1 PCIT32

3

(CFGTADDR)

CFGTADDRQUICKLOGICPCI

是公司提供的一个配置

宏,用于对设备配置空间和地址寄存器块等的定制。

PCIT32CFGTADDR

通过来产生读写、片选、地址等信号。

PCI

作 者 简 介 :胡和平-,男,教授,研究领域:系统集成;田

宜波,硕士生

收 稿 日 期 :2002-06-26

(1952

)

�

CFGTADDR31PCI

由部分组成:第部分是配置空间 由

,

PCI

一组定义接口特点和状态寄存器组成;第部分是地址

寄存器和计数器,存储交易开始的起始地址,同时在每

次数据传输完成后,地址自动累加;第部分是命令译码逻

辑,将来自总线的命令映射成为用户读写命令等。

4

读写操作设计与分析

PCI

PCI

2

3

规范中定义了两种读写操作,即和 读

PCIMemoryI/O

QL5030 PCIT3232Memory

MemoryI/O

写。读写操作包括:位的猝发读

写,单周期读写,单周期读写,配置空间的读写

等。由于空间有限,通常配置映射多采用映射。

I/OMemory

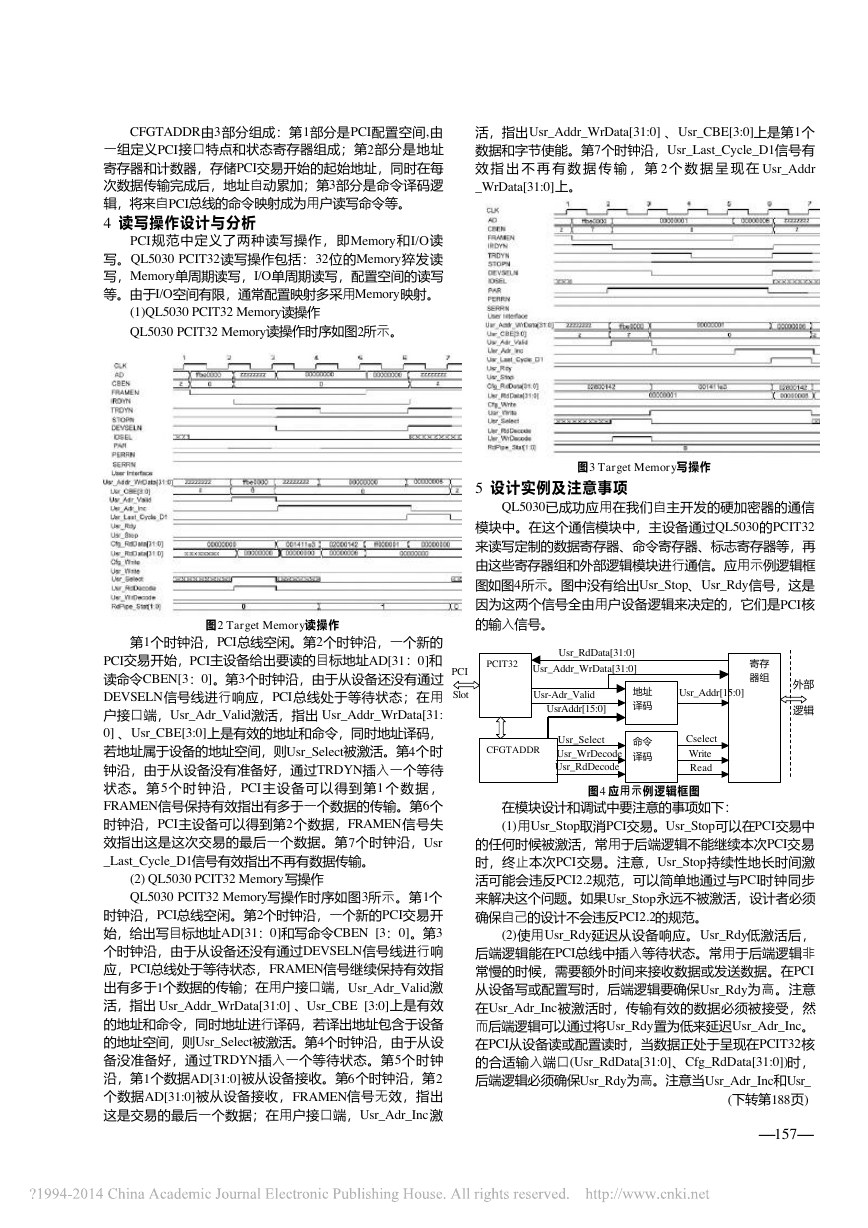

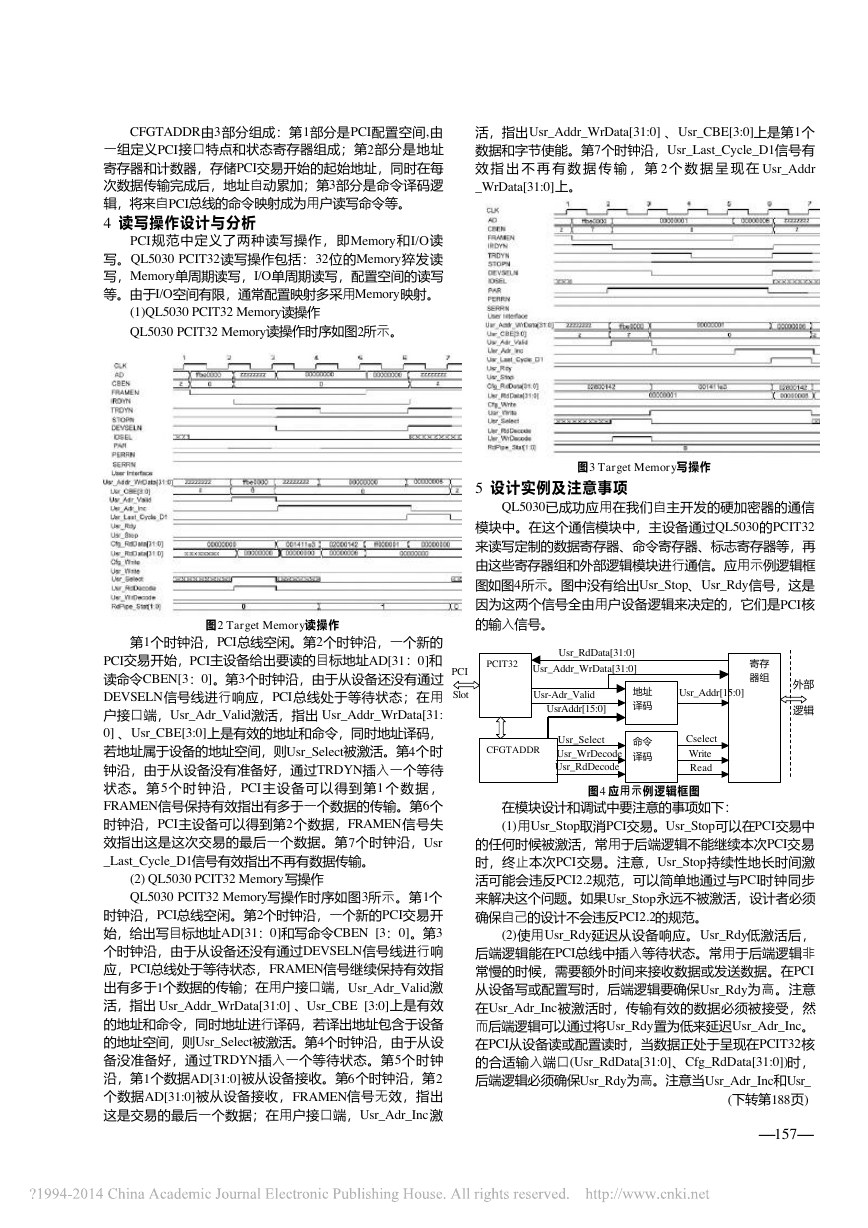

(1)QL5030 PCIT32 Memory

QL5030 PCIT32 Memory

读操作

读操作时序如图所示。

2

图读操作2 Target Memory

3

2

1PCI

Usr_Addr_WrData[31:

、上是有效的地址和命令,同时地址译码,

信号线进行响应,总线处于等待状态;在用

Usr_Adr_Valid

第个时钟沿,总线空闲。第个时钟沿,一个新的

交易开始,主设备给出要读的目标地址: 和

PCIPCIAD[310]

读命令:。第个时钟沿,由于从设备还没有通过

CBEN[30]

DEVSELNPCI

户接口端,激活,指出

0] Usr_CBE[3:0]

若地址属于设备的地址空间,则被激活。第个时

钟沿,由于从设备没有准备好,通过插入一个等待

状态。第个时钟沿,主设备可以得到第个 数 据 ,

FRAMEN

时钟沿,主设备可以得到第个数据,信号失

效指出这是这次交易的最后一个数据。第个时钟沿,

_Last_Cycle_D1

5PCI

信号保持有效指出有多于一个数据的传输。第 个

PCI2FRAMEN

7Usr

信号有效指出不再有数据传输。

Usr_Select

TRDYN

4

1

6

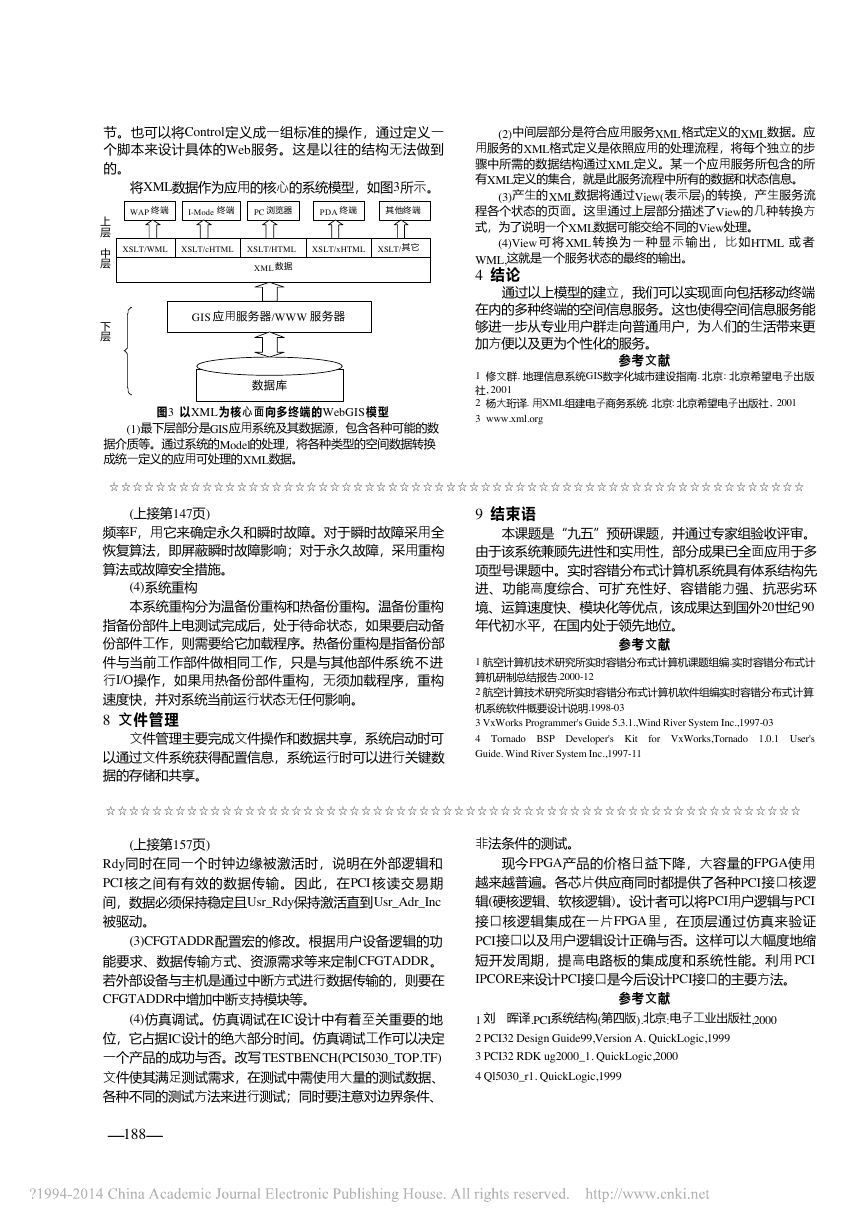

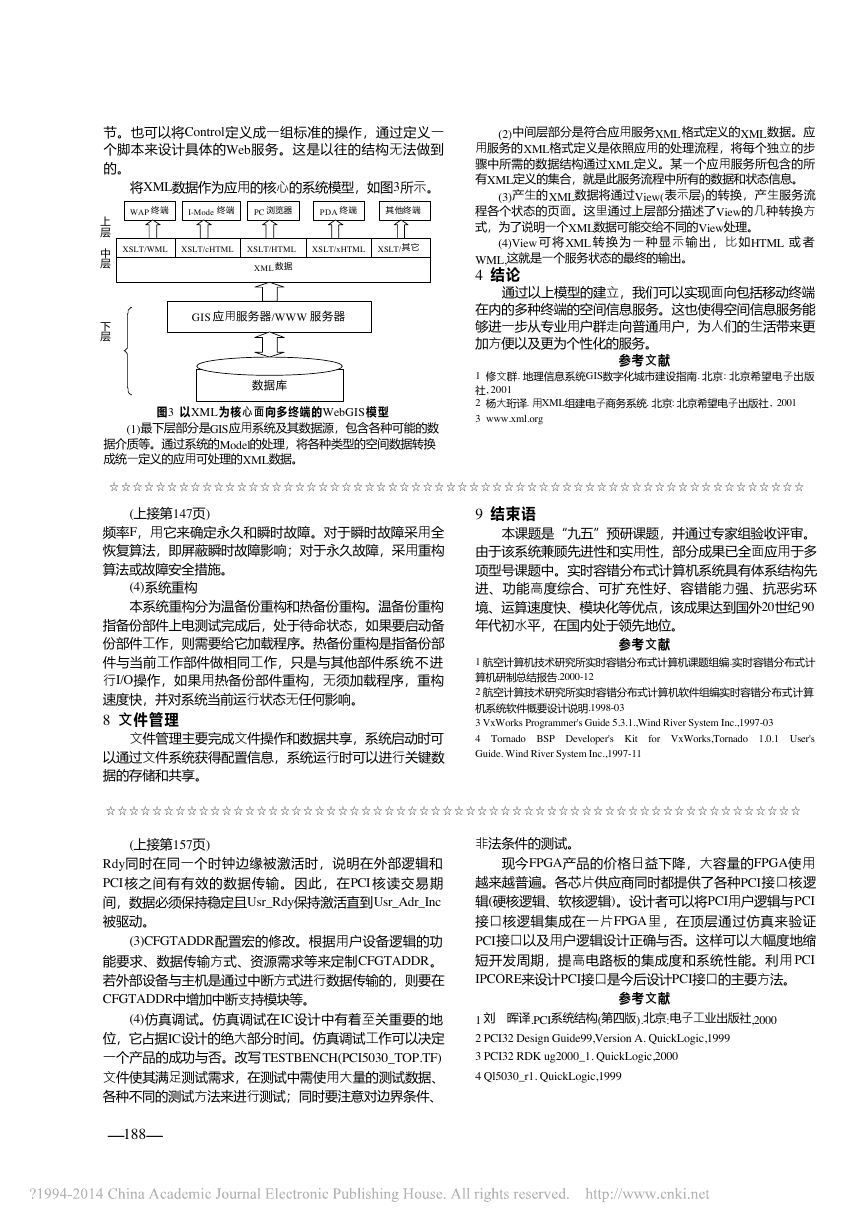

(2) QL5030 PCIT32 Memory

QL5030 PCIT32 Memory3

写操作

写操作时序如图所示。第 个

1

PCI2PCI

PCIFRAMEN

1Usr_Adr_Valid

Usr_Addr_WrData[31:0] Usr_CBE [3:0]

时钟沿,总线空闲。第个时钟沿,一个新的交易开

始,给出写目标地址:和写命令:。第

3

AD[310]CBEN [30]

个时钟沿,由于从设备还没有通过信号线进行响

DEVSELN

应,总线处于等待状态,信号继续保持有效指

出有多于个数据的传输;在用户接口端,

活,指出、上是有效

的地址和命令,同时地址进行译码,若译出地址包含于设备

的地址空间,则被激活。第个时钟沿,由于从设

备没准备好,通过插入一个等待状态。第个时钟

沿,第个数据被从设备接收。第个时钟沿,第

个数据被从设备接收,信号无效,指出

这是交易的最后一个数据;在用户接口端,

1AD[31:0]6

AD[31:0]FRAMEN

Usr_Select

TRDYN

Usr_Adr_Inc

激

激

5

2

4

Usr_Addr_WrData[31:0] Usr_CBE[3:0]

活,指出、上是第 个

数据和字节使能。第个时钟沿,信号有

效 指 出 不 再 有 数 据 传 输 ,第个 数 据 呈 现 在

_WrData[31:0]

7Usr_Last_Cycle_D1

2Usr_Addr

上。

1

图写操作3 Target Memory

5

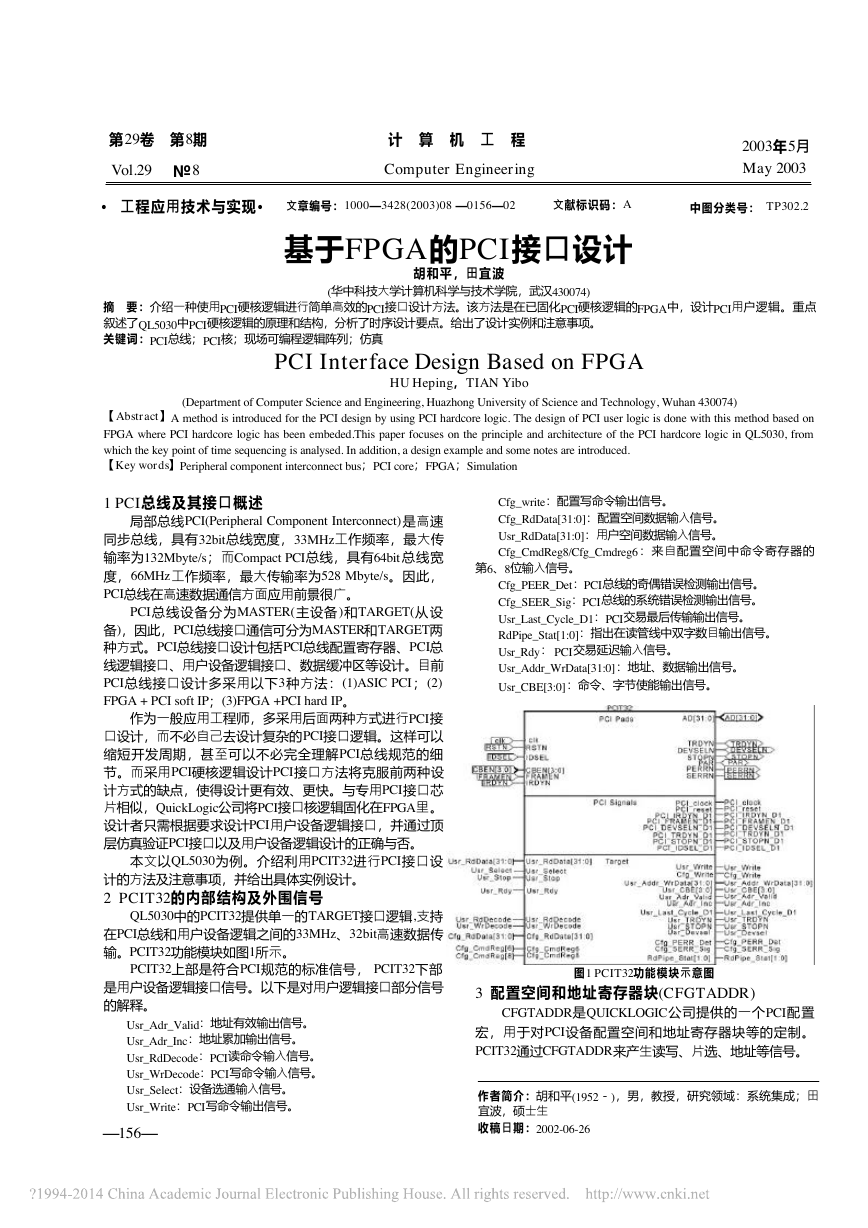

设计实例及注意事项

QL5030

已成功应用在我们自主开发的硬加密器的通信

的

QL5030PCIT32

模块中。在这个通信模块中,主设备通过

来读写定制的数据寄存器、命令寄存器、标志寄存器等,再

由这些寄存器组和外部逻辑模块进行通信。应用示例逻辑框

图如图所示。图中没有给出

因为这两个信号全由用户设备逻辑来决定的,它们是 核PCI

的输入信号。

4Usr_StopUsr_Rdy

、信号,这是

PCI

Slot

PCIT32

Usr_RdData[31:0]

Usr_Addr_WrData[31:0]

Usr-Adr_Valid

UsrAddr[15:0]

CFGTADDR

Usr_Select

Usr_WrDecode

Usr_RdDecode

地址

译码

命令

译码

Usr_Addr[15:0]

寄存

器组

外部

逻辑

Cselect

Write

Read

图应用示例逻辑框图

4

在模块设计和调试中要注意的事项如下:

(1)Usr_StopPCIUsr_StopPCI

用取消交易。可以在交易中

的任何时候被激活,常用于后端逻辑不能继续本次交易PCI

时,终止本次交易。注意,持续性地长时间激

活可能会违反规范,可以简单地通过与时钟同步

来解决这个问题。如果永远不被激活,设计者必须

确保自己的设计不会违反的规范。

PCIUsr_Stop

PCI2.2PCI

Usr_Stop

PCI2.2

(2)Usr_RdyUsr_Rdy

使用延迟从设备响应。低激活后,

PCI

Usr_Adr_Inc

后端逻辑能在总线中插入等待状态。常用于后端逻辑非

常慢的时候,需要额外时间来接收数据或发送数据。在PCI

从设备写或配置写时,后端逻辑要确保为高。注意

Usr_Rdy

在被激活时,传输有效的数据必须被接受,然

而后端逻辑可以通过将置为低来延迟

在从设备读或配置读时,当数据正处于呈现在

的合适输入端口

后端逻辑必须确保为高。注意当

(Usr_RdData[31:0]Cfg_RdData[31:0])

Usr_RdyUsr_Adr_Inc

PCIPCIT32

、时,

。

核

Usr_RdyUsr_Adr_IncUsr_

(188

和

下转第 页

)

— —157

�

Control

节。也可以将定义成一组标准的操作,通过定义一

个脚本来设计具体的服务。这是以往的结构无法做到

的。

Web

上

层

中

层

下

层

将数据作为应用的核心的系统模型,如图所示。

3

XML

WAP 终端

I-Mode 终端

PC 浏览器

PDA 终端

其他终端

XSLT/WML XSLT/cHTML XSLT/HTML

XSLT/xHTML XSLT/其它

XML 数据

GIS 应用服务器/WWW 服务器

数据库

图以为核心面向多终端的模 型

3 XMLWebGIS

(1)GIS

最下层部分是应用系统及其数据源,包含各种可能的数

(2)XMLXML

中间层部分是符合应用服务格式定义的数据。应

XML

用服务的格式定义是依照应用的处理流程,将每个独立的步

骤中所需的数据结构通过定义。某一个应用服务所包含的所

有定义的集合,就是此服务流程中所有的数据和状态信息。

XML

XML

(3)XMLView(

产生的数据将通过表示层的转换,产生服务流

)

程各个状态的页面。这里通过上层部分描述了的几种转换方

式,为了说明一个数据可能交给不同的处理。

View

XMLView

(4)ViewXMLHTML

可将转 换 为 一 种 显 示 输 出 , 比如或 者

这就是一个服务状态的最终的输出。

WML,

结论4

通过以上模型的建立,我们可以实现面向包括移动终端

在内的多种终端的空间信息服务。这也使得空间信息服务能

够进一步从专业用户群走向普通用户,为人们的生活带来更

加方便以及更为个性化的服务。

参考文献

修文群地理信息系统数字化城市建设指南北京北京希望电子出版

GIS.

:

杨大珩译用组建电子商务系统北京北京希望电子出版社

. XML.

, 2001

:

.

1

社, 2001

2

3 www.xml.org

据介质等。通过系统的的处理,将各种类型的空间数据转换

成统一定义的应用可处理的数据。XML

Model

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

上接第 页

(147 )

F

频率,用它来确定永久和瞬时故障。对于瞬时故障采用全

恢复算法,即屏蔽瞬时故障影响;对于永久故障,采用重构

算法或故障安全措施。

系统重构

(4)

本系统重构分为温备份重构和热备份重构。温备份重构

指备份部件上电测试完成后,处于待命状态,如果要启动备

份部件工作,则需要给它加载程序。热备份重构是指备份部

件与当前工作部件做相同工作,只是与其他部件系统不进

行操作,如果用热备份部件重构,无须加载程序,重构

速度快,并对系统当前运行状态无任何影响。

8

文件管理

I/O

/

文件管理主要完成文件操作和数据共享,系统启动时可

以通过文件系统获得配置信息,系统运行时可以进行关键数

据的存储和共享。

9

结束语

本课题是“九五”预研课题,并通过专家组验收评审。

由于该系统兼顾先进性和实用性,部分成果已全面应用于多

项型号课题中。实时容错分布式计算机系统具有体系结构先

进、功能高度综合、可扩充性好、容错能力强、抗恶劣环

境、运算速度快、模块化等优点,该成果达到国外世纪2090

年代初水平,在国内处于领先地位。

参考文献

航空计算技术研究所实时容错分布式计算机软件组编实时容错分布式计算

.

航空计算机技术研究所实时容错分布式计算机课题组编实时容错分布式计

.

1

算机研制总结报告.2000-12

2

机系统软件概要设计说明.1998-03

3 VxWorks Programmer's Guide 5.3.1.,Wind River System Inc.,1997-03

4 Tornado BSP Developer's Kit

Guide. Wind River System Inc.,1997-11

for VxWorks,Tornado 1.0.1 User's

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

上接第 页

(157 )

同时在同一个时钟边缘被激活时,说明在外部逻辑和

核之间有有效的数据传输。因此,在核读交易期

Rdy

PCIPCI

间,数据必须保持稳定且保持激活直到

被驱动。

Usr_RdyUsr_Adr_Inc

(3)CFGTADDR

配置宏的修改。根据用户设备逻辑的功

能要求、数据传输方式、资源需求等来定制

。

若外部设备与主机是通过中断方式进行数据传输的,则要在

CFGTADDR

中增加中断支持模块等。

CFGTADDR

IC

(4)IC

仿真调试。仿真调试在设计中有着至关重要的地

位,它占据设计的绝大部分时间。仿真调试工作可以决定

一个产品的成功与否。改写TESTBENCH(PCI5030_TOP.TF)

文件使其满足测试需求,在测试中需使用大量的测试数据、

各种不同的测试方法来进行测试;同时要注意对边界条件、

— —188

非法条件的测试。

现今产品的价格日益下降,大容量的使用

FPGAFPGA

()PCIPCI

越来越普遍。各芯片供应商同时都提供了各种接口核逻

PCI

辑硬核逻辑、软核逻辑。设计者可以将用户逻辑与

接口核逻辑集成在一片里,在顶层通过仿真来验证

接口以及用户逻辑设计正确与否。这样可以大幅度地缩

PCI

短开发周期,提高电路板的集成度和系统性能。利用 PCI

IPCOREPCIPCI

来设计接口是今后设计接口的主要方法。

FPGA

参考文献

.PCI().:,2000

刘晖译系统结构第四版北京电子工业出版社

1

2 PCI32 Design Guide99,Version A. QuickLogic,1999

3 PCI32 RDK ug2000_1. QuickLogic,2000

4 Ql5030_r1. QuickLogic,1999

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc