5

Description

4

DATE

BY

3

REV

C

D

1. Improved layout for the USB PHY.

2. Removed unused parts from the design.

3. Added current measurement function to the TWL4030.

4. Added filter caps to the VBUS rail input and output.

5.Changed U9 & U11 package to the QFN..

1. Added J12 and J13 to provide access to the RGB TTL signals on the LCD.

2. Added 5 filter caps.

3. Moved the USB Host port from Port1 to Port2.

4. Deleted R1.

5. Added 10K pulldown to USB reset signal.

6. Added 10K pulldown resistors as ID function to determine board type by reading these pins.

7. Added series resistor, R53, in the CLK line of the HSUSB clock line. May be removed after

testing.

1. Moved the McBSP3_DX signal to pin AB26.

2. Moved the McBSP3_DR signal to pin AB25.

3. Moved the McBSP3_CLKX signal to pin AD25.

4. Changes were to allow access to three PWM signals from OMAP3530.

C1

C2

8/14/08

GC

10/1/08

GC

1/1/09

GC

C

C2A

1. Changed R70 and R72 from 12K to 1.2K to lower the impedance due to noise issues.

2. Changed R71 and R73 from 12K to 1.2K to lower the impedance due to noise issues.

3/11/09

GC

PAGE NO.

2

CONTENTS

SCHEMATIC PAGE

1

1

2

3

4

5

6

7

8

9

10

COVER PAGE

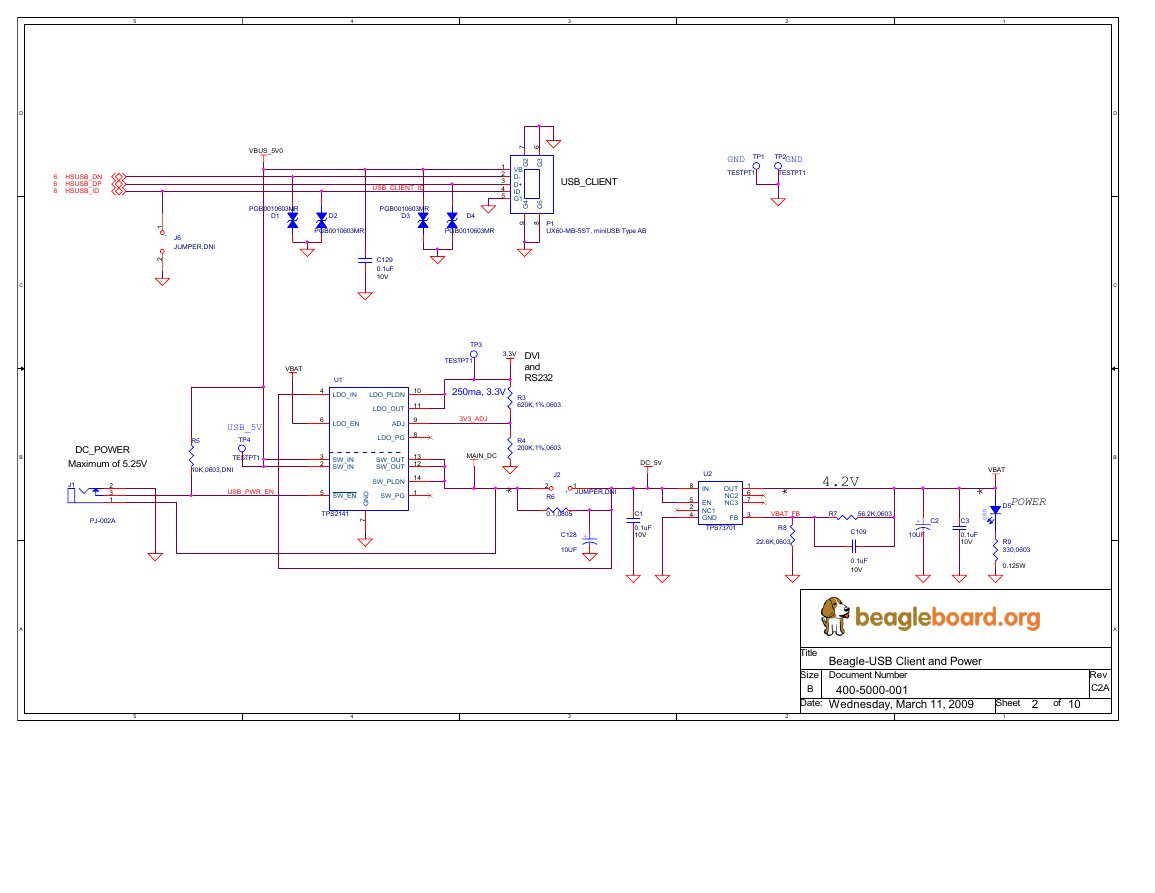

USB OTG CONNECTOR AND MAIN POWER

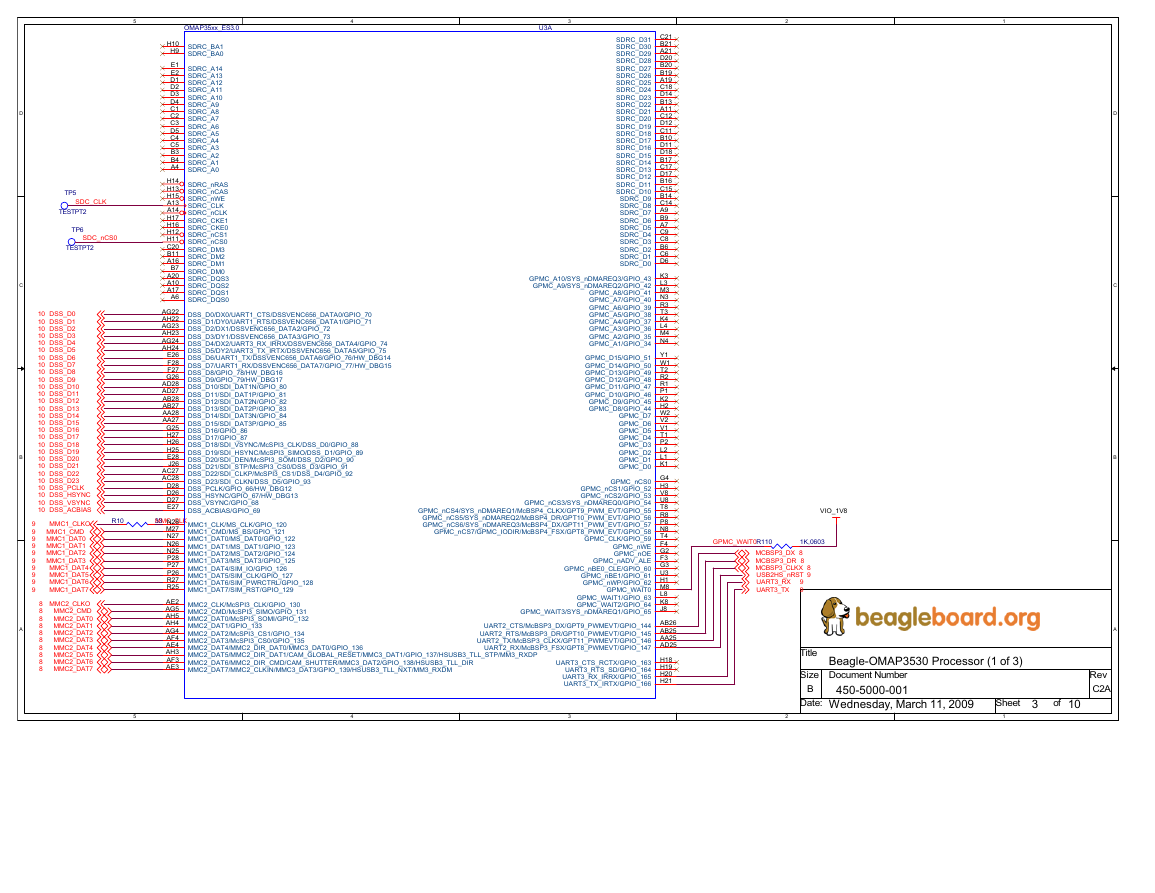

OMAP3 1 OF 3

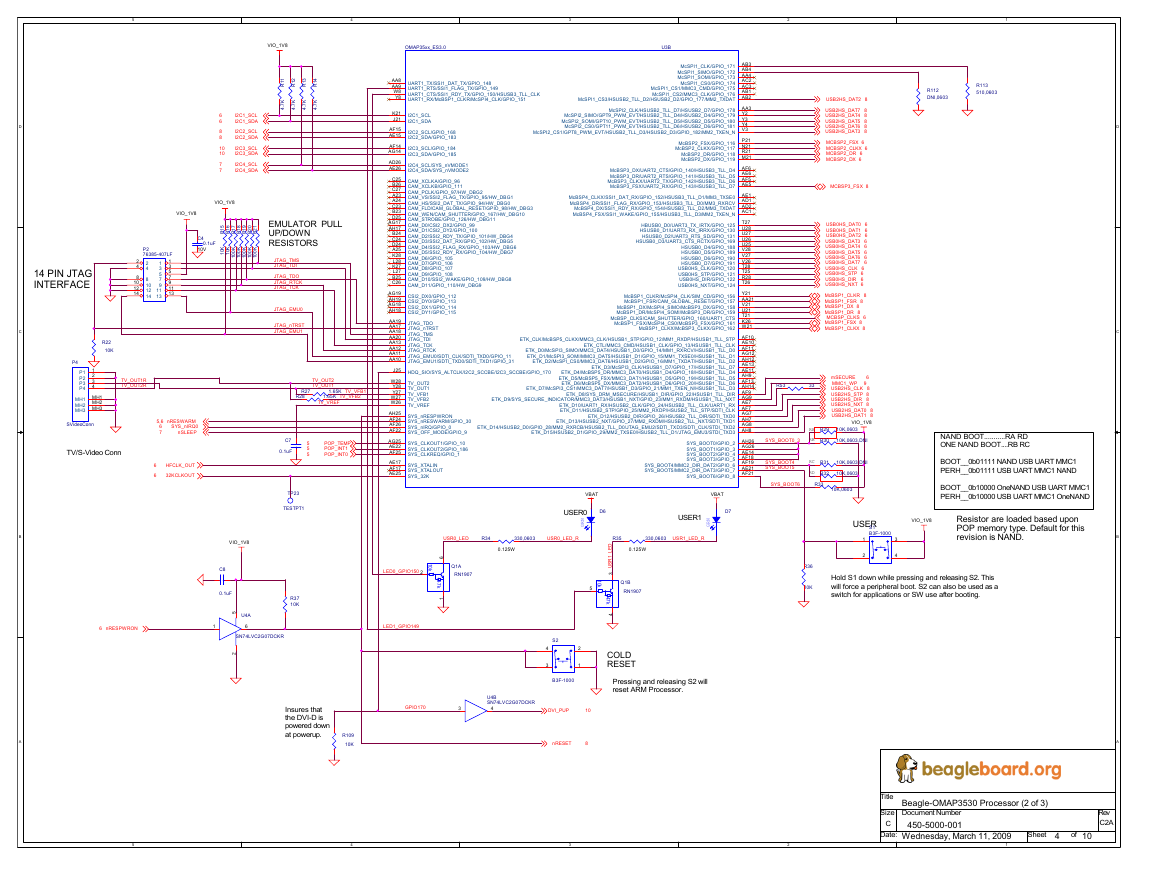

OMAP3 2 OF 3, JTAG, SWITCHES, LEDS, SVIDEO

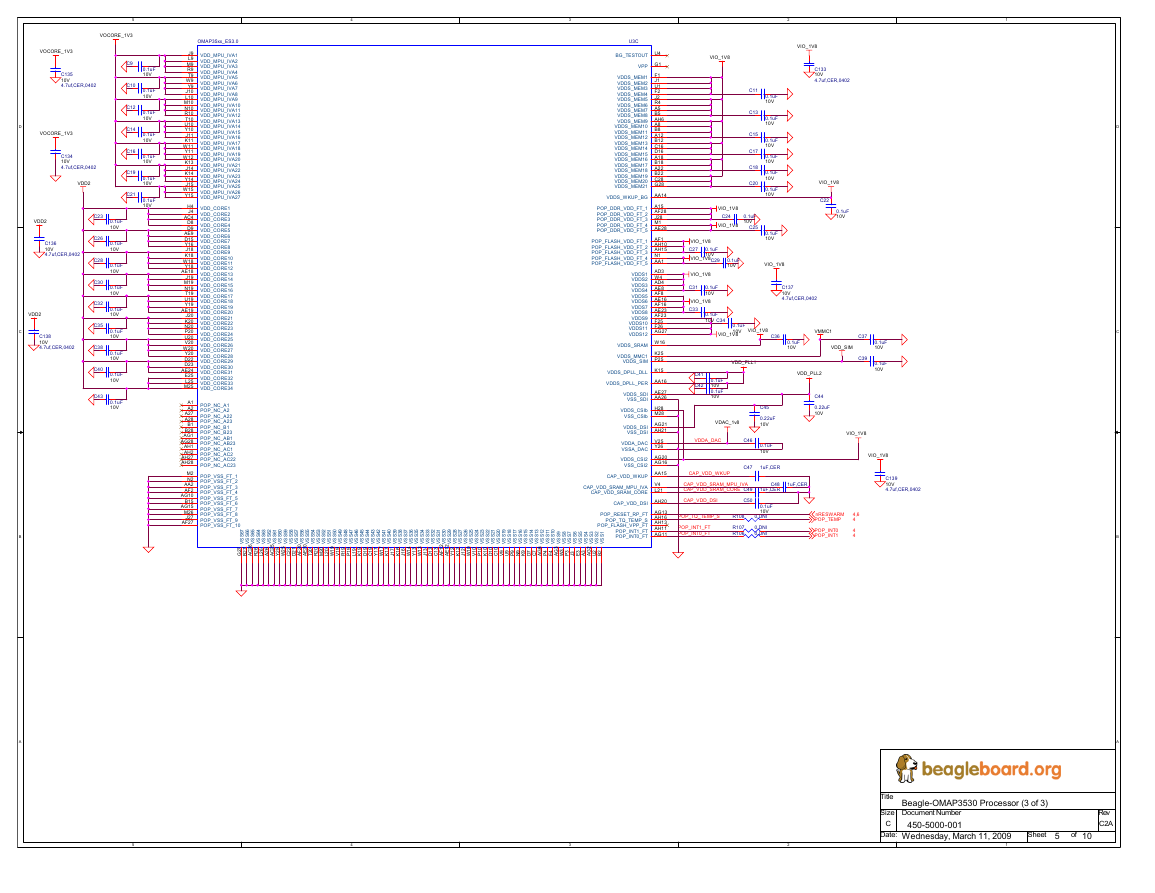

OMAP3 3 OF 3

TWL4030 1 of 2, AUDIO JACKS, LED, 26MHZ, 32KHZ

TWL4030 2 of 2

USB HOST AND EXPANSION

SD/MMC, SERIAL HEADER

DVI-D

This schematic is *NOT SUPPORTED* and DOES NOT constitute a reference design.

Only “community” support is allowed via resources at BeagleBoard.org/discuss.

THERE IS NO WARRANTY FOR THIS DESIGN , TO THE EXTENT PERMITTED BY APPLICABLE

LAW. EXCEPT WHEN OTHERWISE STATED IN WRITING THE COPYRIGHT HOLDERS AND/OR OTHER

PARTIES PROVIDE THE DESIGN “AS IS” WITHOUT WARRANTY OF ANY KIND, EITHER

EXPRESSED OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF

MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. THE ENTIRE RISK AS TO THE

QUALITY AND PERFORMANCE OF THE DESIGN IS WITH YOU. SHOULD THE DESIGN DESIGN

PROVE DEFECTIVE, YOU ASSUME THE COST OF ALL NECESSARY SERVICING, REPAIR OR

CORRECTION.

B

A

Title

5

4

3

2

Beagle-Cover Page

B

Size Document Number

450-5000-001

Wednesday, March 11, 2009

Date:

Rev

C2A

1

of

10

Sheet

1

D

C

B

A

�

5

4

3

2

1

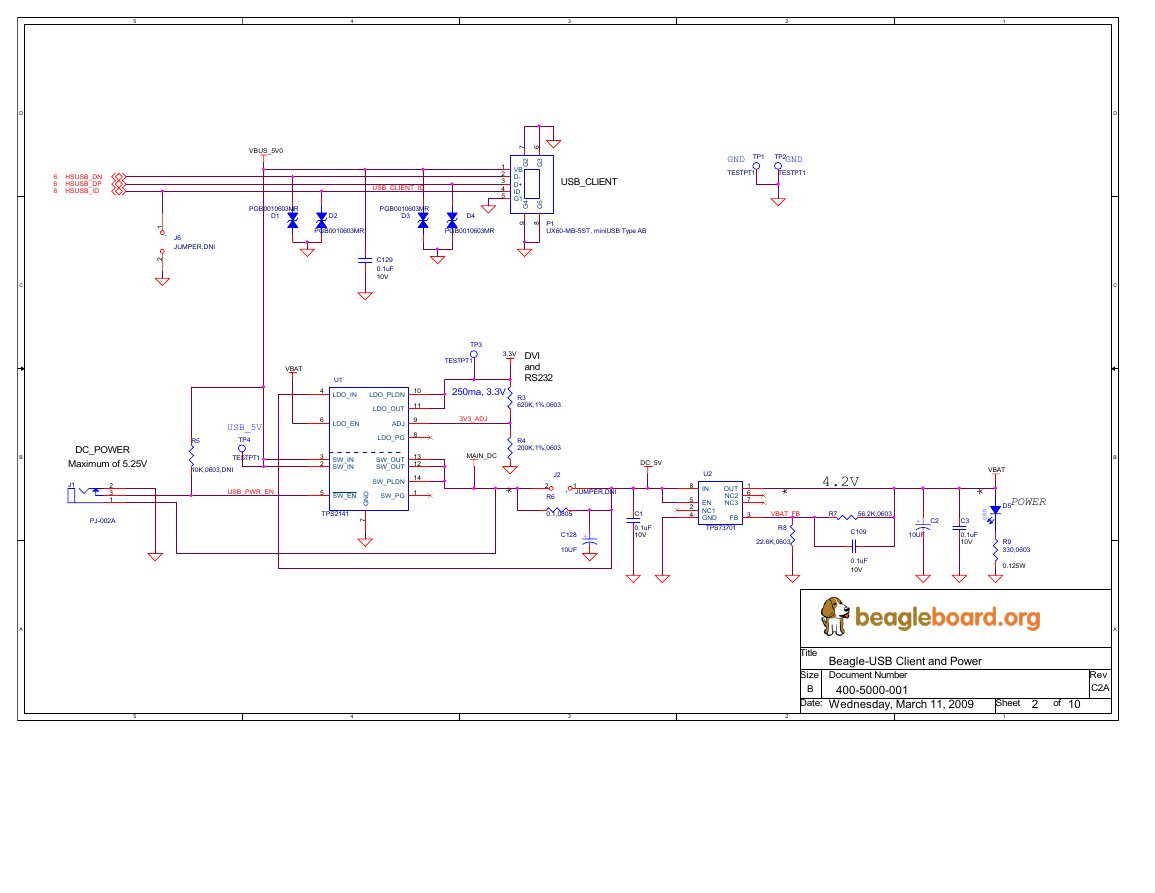

VBUS_5V0

7 6

6

6

6

HSUSB_DN

HSUSB_DP

HSUSB_ID

1

+ J6

JUMPER,DNI

2

USB_CLIENT_ID

PGB0010603MR

D1

D2

PGB0010603MR

D3

PGB0010603MR

C129

0.1uF

10V

1

2

3

4

5

2

G

VB

D-

D+

ID

G1

4

G

3

G

5

G

USB_CLIENT

D4

PGB0010603MR

89

P1

UX60-MB-5ST, miniUSB Type AB

TP1

GND

TESTPT1

TP2

GND

TESTPT1

VBAT

U1

R5

USB_5V

TP4

TESTPT1

10K,0603,DNI

USB_PWR_EN

4

6

3

2

5

LDO_IN

LDO_PLDN

LDO_OUT

LDO_EN

ADJ

LDO_PG

SW_OUT

SW_OUT

SW_PLDN

SW_PG

D

N

G

7

SW_IN

SW_IN

SW_EN

TPS2141

DC_POWER

Maximum of 5.25V

J1

2

3

1

PJ-002A

10

11

9

8

13

12

14

1

TP3

TESTPT1

3.3V

DVI

and

RS232

250ma, 3.3V

3V3_ADJ

MAIN_DC

R3

620K,1%,0603

R4

200K,1%,0603

*

J2

2

R6

1

JUMPER,DNI

+

0.1,0805

C128

+

10UF

DC_5V

C1

0.1uF

10V

8

5

2

4

U2

IN

OUT

NC2

NC3

EN

NC1

GND

FB

TPS73701

4.2V

*

VBAT_FB

R7

56.2K,0603

1

6

7

3

R8

22.6K,0603

C109

0.1uF

10V

+

C2

10UF

VBAT

*

N

R

G

C3

0.1uF

10V

POWER

D5

R9

330,0603

0.125W

D

C

B

A

D

C

B

A

5

4

3

2

Title

Beagle-USB Client and Power

B

Size Document Number

400-5000-001

Wednesday, March 11, 2009

Date:

Rev

C2A

Sheet

1

2

of

10

�

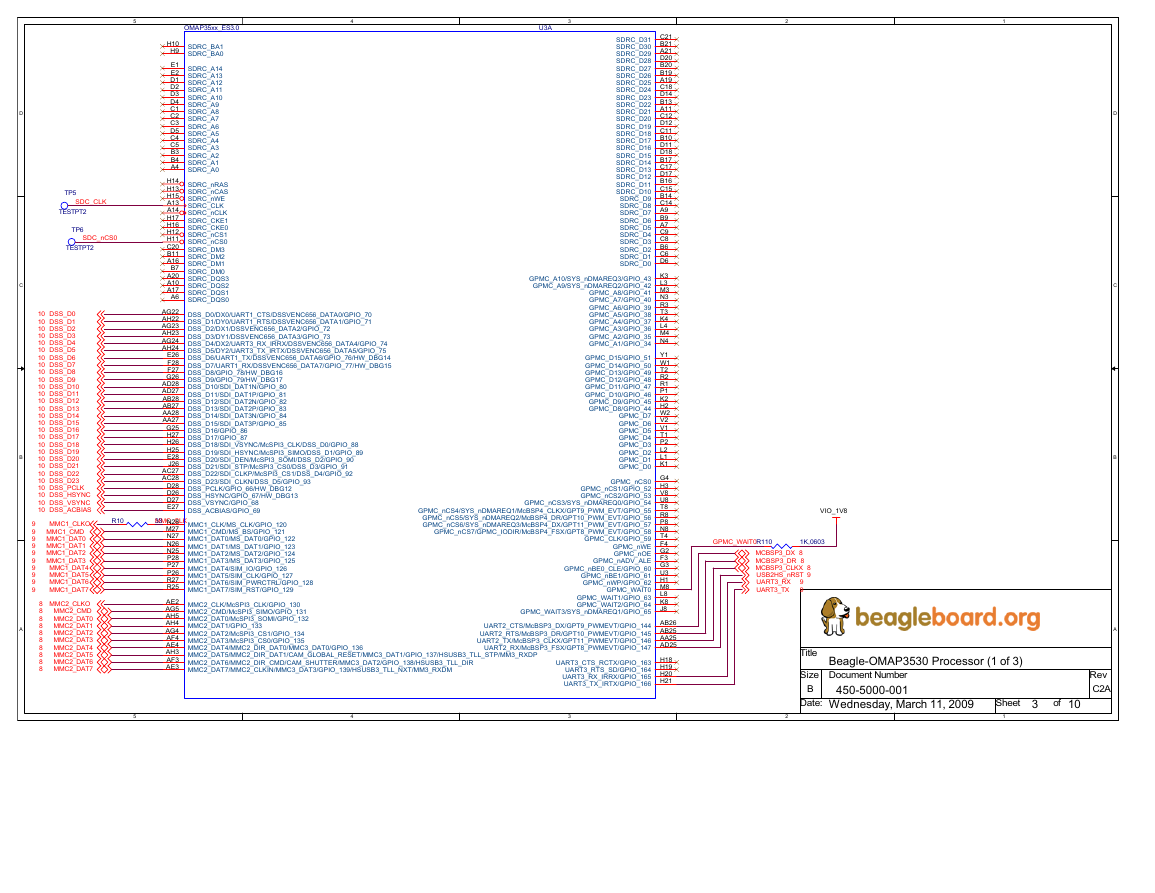

5

OMAP35xx_ES3.0

4

3

U3A

H10

H9

E1

E2

D1

D2

D3

D4

C1

C2

C3

D5

C4

C5

B3

B4

A4

H14

H13

H15

A13

A14

H17

H16

H12

H11

C20

B11

A16

B7

A20

A10

A17

A6

AG22

AH22

AG23

AH23

AG24

AH24

E26

F28

F27

G26

AD28

AD27

AB28

AB27

AA28

AA27

G25

H27

H26

H25

E28

J26

AC27

AC28

D28

D26

D27

E27

SDRC_BA1

SDRC_BA0

SDRC_A14

SDRC_A13

SDRC_A12

SDRC_A11

SDRC_A10

SDRC_A9

SDRC_A8

SDRC_A7

SDRC_A6

SDRC_A5

SDRC_A4

SDRC_A3

SDRC_A2

SDRC_A1

SDRC_A0

SDRC_nRAS

SDRC_nCAS

SDRC_nWE

SDRC_CLK

SDRC_nCLK

SDRC_CKE1

SDRC_CKE0

SDRC_nCS1

SDRC_nCS0

SDRC_DM3

SDRC_DM2

SDRC_DM1

SDRC_DM0

SDRC_DQS3

SDRC_DQS2

SDRC_DQS1

SDRC_DQS0

DSS_D0/DX0/UART1_CTS/DSSVENC656_DATA0/GPIO_70

DSS_D1/DY0/UART1_RTS/DSSVENC656_DATA1/GPIO_71

DSS_D2/DX1/DSSVENC656_DATA2/GPIO_72

DSS_D3/DY1/DSSVENC656_DATA3/GPIO_73

DSS_D4/DX2/UART3_RX_IRRX/DSSVENC656_DATA4/GPIO_74

DSS_D5/DY2/UART3_TX_IRTX/DSSVENC656_DATA5/GPIO_75

DSS_D6/UART1_TX/DSSVENC656_DATA6/GPIO_76/HW_DBG14

DSS_D7/UART1_RX/DSSVENC656_DATA7/GPIO_77/HW_DBG15

DSS_D8/GPIO_78/HW_DBG16

DSS_D9/GPIO_79/HW_DBG17

DSS_D10/SDI_DAT1N/GPIO_80

DSS_D11/SDI_DAT1P/GPIO_81

DSS_D12/SDI_DAT2N/GPIO_82

DSS_D13/SDI_DAT2P/GPIO_83

DSS_D14/SDI_DAT3N/GPIO_84

DSS_D15/SDI_DAT3P/GPIO_85

DSS_D16/GPIO_86

DSS_D17/GPIO_87

DSS_D18/SDI_VSYNC/McSPI3_CLK/DSS_D0/GPIO_88

DSS_D19/SDI_HSYNC/McSPI3_SIMO/DSS_D1/GPIO_89

DSS_D20/SDI_DEN/McSPI3_SOMI/DSS_D2/GPIO_90

DSS_D21/SDI_STP/McSPI3_CS0/DSS_D3/GPIO_91

DSS_D22/SDI_CLKP/McSPI3_CS1/DSS_D4/GPIO_92

DSS_D23/SDI_CLKN/DSS_D5/GPIO_93

DSS_PCLK/GPIO_66/HW_DBG12

DSS_HSYNC/GPIO_67/HW_DBG13

DSS_VSYNC/GPIO_68

DSS_ACBIAS/GPIO_69

D

C

B

A

TP5

SDC_CLK

TESTPT2

TP6

SDC_nCS0

TESTPT2

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

DSS_D0

DSS_D1

DSS_D2

DSS_D3

DSS_D4

DSS_D5

DSS_D6

DSS_D7

DSS_D8

DSS_D9

DSS_D10

DSS_D11

DSS_D12

DSS_D13

DSS_D14

DSS_D15

DSS_D16

DSS_D17

DSS_D18

DSS_D19

DSS_D20

DSS_D21

DSS_D22

DSS_D23

DSS_PCLK

DSS_HSYNC

DSS_VSYNC

DSS_ACBIAS

9

9

9

9

9

9

9

9

9

9

MMC1_CLKO

MMC1_CMD

MMC1_DAT0

MMC1_DAT1

MMC1_DAT2

MMC1_DAT3

MMC1_DAT4

MMC1_DAT5

MMC1_DAT6

MMC1_DAT7

8

8

8

8

8

8

8

8

8

8

MMC2_CLKO

MMC2_CMD

MMC2_DAT0

MMC2_DAT1

MMC2_DAT2

MMC2_DAT3

MMC2_DAT4

MMC2_DAT5

MMC2_DAT6

MMC2_DAT7

SDRC_D31

SDRC_D30

SDRC_D29

SDRC_D28

SDRC_D27

SDRC_D26

SDRC_D25

SDRC_D24

SDRC_D23

SDRC_D22

SDRC_D21

SDRC_D20

SDRC_D19

SDRC_D18

SDRC_D17

SDRC_D16

SDRC_D15

SDRC_D14

SDRC_D13

SDRC_D12

SDRC_D11

SDRC_D10

SDRC_D9

SDRC_D8

SDRC_D7

SDRC_D6

SDRC_D5

SDRC_D4

SDRC_D3

SDRC_D2

SDRC_D1

SDRC_D0

GPMC_A10/SYS_nDMAREQ3/GPIO_43

GPMC_A9/SYS_nDMAREQ2/GPIO_42

GPMC_A8/GPIO_41

GPMC_A7/GPIO_40

GPMC_A6/GPIO_39

GPMC_A5/GPIO_38

GPMC_A4/GPIO_37

GPMC_A3/GPIO_36

GPMC_A2/GPIO_35

GPMC_A1/GPIO_34

GPMC_D15/GPIO_51

GPMC_D14/GPIO_50

GPMC_D13/GPIO_49

GPMC_D12/GPIO_48

GPMC_D11/GPIO_47

GPMC_D10/GPIO_46

GPMC_D9/GPIO_45

GPMC_D8/GPIO_44

GPMC_D7

GPMC_D6

GPMC_D5

GPMC_D4

GPMC_D3

GPMC_D2

GPMC_D1

GPMC_D0

C21

B21

A21

D20

B20

B19

A19

C18

D14

B13

A11

C12

D12

C11

B10

D11

D18

B17

C17

D17

B16

C15

B14

C14

A9

B9

A7

C9

C8

B6

C6

D6

K3

L3

M3

N3

R3

T3

K4

L4

M4

N4

Y1

W1

T2

R2

R1

P1

K2

H2

W2

V2

V1

T1

P2

L2

L1

K1

G4

H3

V8

U8

T8

R8

P8

N8

T4

F4

G2

F3

G3

U3

H1

M8

L8

K8

J8

AB26

AB25

AA25

AD25

H18

H19

H20

H21

2

1

VIO_1V8

D

C

B

A

Rev

C2A

R10

MMC_CLK

33

N28

M27

N27

N26

N25

P28

P27

P26

R27

R25

MMC1_CLK/MS_CLK/GPIO_120

MMC1_CMD/MS_BS/GPIO_121

MMC1_DAT0/MS_DAT0/GPIO_122

MMC1_DAT1/MS_DAT1/GPIO_123

MMC1_DAT2/MS_DAT2/GPIO_124

MMC1_DAT3/MS_DAT3/GPIO_125

MMC1_DAT4/SIM_IO/GPIO_126

MMC1_DAT5/SIM_CLK/GPIO_127

MMC1_DAT6/SIM_PWRCTRL/GPIO_128

MMC1_DAT7/SIM_RST/GPIO_129

AE2

AG5

AH5

AH4

AG4

AF4

AE4

AH3

AF3

AE3

MMC2_CLK/McSPI3_CLK/GPIO_130

MMC2_CMD/McSPI3_SIMO/GPIO_131

MMC2_DAT0/McSPI3_SOMI/GPIO_132

MMC2_DAT1/GPIO_133

MMC2_DAT2/McSPI3_CS1/GPIO_134

MMC2_DAT3/McSPI3_CS0/GPIO_135

MMC2_DAT4/MMC2_DIR_DAT0/MMC3_DAT0/GPIO_136

MMC2_DAT5/MMC2_DIR_DAT1/CAM_GLOBAL_RESET/MMC3_DAT1/GPIO_137/HSUSB3_TLL_STP/MM3_RXDP

MMC2_DAT6/MMC2_DIR_CMD/CAM_SHUTTER/MMC3_DAT2/GPIO_138/HSUSB3_TLL_DIR

MMC2_DAT7/MMC2_CLKIN/MMC3_DAT3/GPIO_139/HSUSB3_TLL_NXT/MM3_RXDM

GPMC_nCS0

GPMC_nCS1/GPIO_52

GPMC_nCS2/GPIO_53

GPMC_nCS3/SYS_nDMAREQ0/GPIO_54

GPMC_nCS4/SYS_nDMAREQ1/McBSP4_CLKX/GPT9_PWM_EVT/GPIO_55

GPMC_nCS5/SYS_nDMAREQ2/McBSP4_DR/GPT10_PWM_EVT/GPIO_56

GPMC_nCS6/SYS_nDMAREQ3/McBSP4_DX/GPT11_PWM_EVT/GPIO_57

GPMC_nCS7/GPMC_IODIR/McBSP4_FSX/GPT8_PWM_EVT/GPIO_58

GPMC_CLK/GPIO_59

GPMC_nWE

GPMC_nOE

GPMC_nADV_ALE

GPMC_nBE0_CLE/GPIO_60

GPMC_nBE1/GPIO_61

GPMC_nWP/GPIO_62

GPMC_WAIT0

GPMC_WAIT1/GPIO_63

GPMC_WAIT2/GPIO_64

GPMC_WAIT3/SYS_nDMAREQ1/GPIO_65

UART2_CTS/McBSP3_DX/GPT9_PWMEVT/GPIO_144

UART2_RTS/McBSP3_DR/GPT10_PWMEVT/GPIO_145

UART2_TX/McBSP3_CLKX/GPT11_PWMEVT/GPIO_146

UART2_RX/McBSP3_FSX/GPT8_PWMEVT/GPIO_147

UART3_CTS_RCTX/GPIO_163

UART3_RTS_SD/GPIO_164

UART3_RX_IRRX/GPIO_165

UART3_TX_IRTX/GPIO_166

GPMC_WAIT0

1K,0603

R110

MCBSP3_DX 8

MCBSP3_DR 8

MCBSP3_CLKX 8

USB2HS_nRST 9

UART3_RX

UART3_TX

9

9

Title

5

4

3

2

Beagle-OMAP3530 Processor (1 of 3)

B

Size Document Number

450-5000-001

Wednesday, March 11, 2009

Date:

Sheet

1

3

of

10

�

5

4

3

2

1

VIO_1V8

OMAP35xx_ES3.0

U3B

6

6

8

8

10

10

7

7

I2C1_SCL

I2C1_SDA

I2C2_SCL

I2C2_SDA

I2C3_SCL

I2C3_SDA

I2C4_SCL

I2C4_SDA

VIO_1V8

VIO_1V8

C4

10V

0.1uF

5

1

R

6

1

R

7

1

R

8

1

R

9

1

R

0

2

R

1

2

R

K

0

1

K

0

1

K

0

0

1

K

0

0

1

K

0

0

1

K

0

0

1

K

0

0

1

14 PIN JTAG

INTERFACE

2

4

8

10

12

14

P2

76385-407LF

1

2

3

4

5

7

9

11

13

1

3

5

7

9

11

13

8

10

12

14

R22

10K

P4

P1

P2

P3

P4

MH1

MH2

MH3

1

2

3

4

MH1

MH2

MH3

SVideoConn

TV_OUT1R

TV_OUT2R

TV/S-Video Conn

5,6

6

7

nRESWARM

SYS_nIRQ0

nSLEEP

6

6

HFCLK_OUT

32KCLKOUT

6

nRESPWRON

C7

0.1uF

5

5

5

POP_TEMP

POP_INT1

POP_INT0

TP23

TESTPT1

R37

10K

VIO_1V8

C8

0.1uF

5

U4A

1

6

SN74LVC2G07DCKR

2

D

C

B

A

UART1_TX/SSI1_DAT_TX/GPIO_148

UART1_RTS/SSI1_FLAG_TX/GPIO_149

UART1_CTS/SSI1_RDY_TX/GPIO_150/HSUSB3_TLL_CLK

UART1_RX/McBSP1_CLKR/McSPI4_CLK/GPIO_151

McSPI1_CLK/GPIO_171

McSPI1_SIMO/GPIO_172

McSPI1_SOMI/GPIO_173

McSPI1_CS0/GPIO_174

McSPI1_CS1/MMC3_CMD/GPIO_175

McSPI1_CS2/MMC3_CLK/GPIO_176

McSPI1_CS3/HSUSB2_TLL_D2/HSUSB2_D2/GPIO_177/MM2_TXDAT

McSPI2_CLK/HSUSB2_TLL_D7/HSUSB2_D7/GPIO_178

McSPI2_SIMO/GPT9_PWM_EVT/HSUSB2_TLL_D4/HSUSB2_D4/GPIO_179

McSPI2_SOMI/GPT10_PWM_EVT/HSUSB2_TLL_D5/HSUSB2_D5/GPIO_180

McSPI2_CS0/GPT11_PWM_EVT/HSUSB2_TLL_D6/HSUSB2_D6/GPIO_181

McSPI2_CS1/GPT8_PWM_EVT/HSUSB2_TLL_D3/HSUSB2_D3/GPIO_182/MM2_TXEN_N

1

1

R

2

1

R

3

1

R

4

1

R

K

7

.

4

K

7

.

4

K

7

.

4

K

7

.

4

EMULATOR PULL

UP/DOWN

RESISTORS

JTAG_TMS

JTAG_TDI

JTAG_TDO

JTAG_RTCK

JTAG_TCK

JTAG_EMU0

JTAG_nTRST

JTAG_EMU1

R27

R28

TV_OUT2

TV_OUT1

TV_VREF

1.65K

TV_VFB1

1.65K

TV_VFB2

AA8

AA9

W8

Y8

K21

J21

AF15

AE15

AF14

AG14

AD26

AE26

C25

B26

C27

A23

A24

C23

B23

D25

AG17

AH17

B24

C24

D24

A25

K28

L28

K27

L27

B25

C26

AG19

AH19

AG18

AH18

AA19

AA17

AA18

AA20

AA13

AA12

AA11

AA10

J25

W28

Y28

Y27

W27

W26

AH25

AF24

AF26

AF22

AG25

AE22

AF25

AE17

AF17

AE25

I2C1_SCL

I2C1_SDA

I2C2_SCL/GPIO_168

I2C2_SDA/GPIO_183

I2C3_SCL/GPIO_184

I2C3_SDA/GPIO_185

I2C4_SCL/SYS_nVMODE1

I2C4_SDA/SYS_nVMODE2

CAM_XCLKA/GPIO_96

CAM_XCLKB/GPIO_111

CAM_PCLK/GPIO_97/HW_DBG2

CAM_VS/SSI2_FLAG_TX/GPIO_95/HW_DBG1

CAM_HS/SSI2_DAT_TX/GPIO_94/HW_DBG0

CAM_FLD/CAM_GLOBAL_RESET/GPIO_98/HW_DBG3

CAM_WEN/CAM_SHUTTER/GPIO_167/HW_DBG10

CAM_STROBE/GPIO_126/HW_DBG11

CAM_D0/CSI2_DX2/GPIO_99

CAM_D1/CSI2_DY2/GPIO_100

CAM_D2/SSI2_RDY_TX/GPIO_101/HW_DBG4

CAM_D3/SSI2_DAT_RX/GPIO_102/HW_DBG5

CAM_D4/SSI2_FLAG_RX/GPIO_103/HW_DBG6

CAM_D5/SSI2_RDY_RX/GPIO_104/HW_DBG7

CAM_D6/GPIO_105

CAM_D7/GPIO_106

CAM_D8/GPIO_107

CAM_D9/GPIO_108

CAM_D10/SSI2_WAKE/GPIO_109/HW_DBG8

CAM_D11/GPIO_110/HW_DBG9

CSI2_DX0/GPIO_112

CSI2_DY0/GPIO_113

CSI2_DX1/GPIO_114

CSI2_DY1/GPIO_115

JTAG_TDO

JTAG_nTRST

JTAG_TMS

JTAG_TDI

JTAG_TCK

JTAG_RTCK

JTAG_EMU0/SDTI_CLK/SDTI_TXD0/GPIO_11

JTAG_EMU1/SDTI_TXD0/SDTI_TXD1/GPIO_31

HDQ_SIO/SYS_ALTCLK/I2C2_SCCBE/I2C3_SCCBE/GPIO_170

TV_OUT2

TV_OUT1

TV_VFB1

TV_VFB2

TV_VREF

SYS_nRESPWRON

SYS_nRESWARM/GPIO_30

SYS_nIRQ/GPIO_0

SYS_OFF_MODE/GPIO_9

SYS_CLKOUT1/GPIO_10

SYS_CLKOUT2/GPIO_186

SYS_CLKREQ/GPIO_1

SYS_XTALIN

SYS_XTALOUT

SYS_32K

McBSP2_FSX/GPIO_116

McBSP2_CLKX/GPIO_117

McBSP2_DR/GPIO_118

McBSP2_DX/GPIO_119

McBSP3_DX/UART2_CTS/GPIO_140/HSUSB3_TLL_D4

McBSP3_DR/UART2_RTS/GPIO_141/HSUSB3_TLL_D5

McBSP3_CLKX/UART2_TX/GPIO_142/HSUSB3_TLL_D6

McBSP3_FSX/UART2_RX/GPIO_143/HSUSB3_TLL_D7

McBSP4_CLKX/SSI1_DAT_RX/GPIO_152/HSUSB3_TLL_D1/MM3_TXSE0

McBSP4_DR/SSI1_FLAG_RX/GPIO_153/HSUSB3_TLL_D0/MM3_RXRCV

McBSP4_DX/SSI1_RDY_RX/GPIO_154/HSUSB3_TLL_D2/MM3_TXDAT

McBSP4_FSX/SSI1_WAKE/GPIO_155/HSUSB3_TLL_D3/MM2_TXEN_N

HBUSB0_D0/UART3_TX_IRTX/GPIO_125

HSUSB0_D1/UART3_RX_IRRX/GPIO_130

HSUSB0_D2/UART3_RTS_SD/GPIO_131

HSUSB0_D3/UART3_CTS_RCTX/GPIO_169

HSUSB0_D4/GPIO_188

HSUSB0_D5/GPIO_189

HSUSB0_D6/GPIO_190

HSUSB0_D7/GPIO_191

USB0HS_CLK/GPIO_120

USB0HS_STP/GPIO_121

USB0HS_DIR/GPIO_122

USB0HS_NXT/GPIO_124

McBSP1_CLKR/McSPI4_CLK/SIM_CD/GPIO_156

McBSP1_FSR/CAM_GLOBAL_RESET/GPIO_157

McBSP1_DX/McSPI4_SIMO/McBSP3_DX/GPIO_158

McBSP1_DR/McSPI4_SOMI/McBSP3_DR/GPIO_159

McBSP_CLKS/CAM_SHUTTER/GPIO_160/UART1_CTS

McBSP1_FSX/McSPI4_CS0/McBSP3_FSX/GPIO_161

McBSP1_CLKX/McBSP3_CLKX/GPIO_162

ETK_CLK/McBSP5_CLKX/MMC3_CLK/HSUSB1_STP/GPIO_12/MM1_RXDP/HSUSB1_TLL_STP

ETK_CTL/MMC3_CMD/HSUSB1_CLK/GPIO_13/HSUSB1_TLL_CLK

ETK_D0/McSPI3_SIMO/MMC3_DAT4/HSUSB1_D0/GPIO_14/MM1_RXRCV/HSUSB1_TLL_D0

ETK_D1/McSPI3_SOMI/MMC3_DAT5/HSUSB1_D1/GPIO_15/MM1_TXSE0/HSUSB1_TLL_D1

ETK_D2/McSPI_CS0/MMC3_DAT6/HSUSB1_D2/GPIO_16/MM1_TXDAT/HSUSB1_TLL_D2

ETK_D3/McSPI3_CLK/HSUSB1_D7/GPIO_17/HSUSB1_TLL_D7

ETK_D4/McBSP5_DR/MMC3_DAT0/HSUSB1_D4/GPIO_18/HSUSB1_TLL_D4

ETK_D5/McBSP5_FSX/MMC3_DAT1/HSUSB1_D5/GPIO_19/HSUSB1_TLL_D5

ETK_D6/McBSP5_DX/MMC3_DAT2/HSUSB1_D6/GPIO_20/HSUSB1_TLL_D6

ETK_D7/McSPI3_CS1/MMC3_DAT7/HSUSB1_D3/GPIO_21/MM1_TXEN_N/HSUSB1_TLL_D3

ETK_D8/SYS_DRM_MSECURE/HSUSB1_DIR/GPIO_22/HSUSB1_TLL_DIR

ETK_D9/SYS_SECURE_INDICATOR/MMC3_DAT3/HSUSB1_NXT/GPIO_23/MM1_RXDM/HSUSB1_TLL_NXT

ETK_D10/UART1_RX/HSUSB2_CLK/GPIO_24/HSUSB2_TLL_CLK/UART1_RX

ETK_D11/HSUSB2_STP/GPIO_25/MM2_RXDP/HSUSB2_TLL_STP/SDTI_CLK

ETK_D12/HSUSB2_DIR/GPIO_26/HSUSB2_TLL_DIR/SDTI_TXD0

ETK_D13/HSUSB2_NXT/GPIO_27/MM2_RXDM/HSUSB2_TLL_NXT/SDTI_TXD1

ETK_D14/HSUSB2_D0/GPIO_28/MM2_RXRCB/HSUSB2_TLL_D0/JTAG_EMU2/SDTI_TXD3/SDTI_CLK/STDI_TXD2

ETK_D15/HSUSB2_D1/GPIO_29/MM2_TXSE0/HSUSB2_TLL_D1/JTAG_EMU3/STDI_TXD3

SYS_BOOT0/GPIO_2

SYS_BOOT1/GPIO_3

SYS_BOOT2/GPIO_4

SYS_BOOT3/GPIO_5

SYS_BOOT4/MMC2_DIR_DAT2/GPIO_6

SYS_BOOT5/MMC2_DIR_DAT3/GPIO_7

SYS_BOOT6/GPIO_8

VBAT

D7

USER1

N

R

G

VBAT

USER0

D6

N

R

G

USR0_LED

R34

330,0603

USR0_LED_R

R35

330,0603

USR1_LED_R

0.125W

LED0_GPIO150

2

Q1A

RN1907

6

1

0

k

4

7

k

1

LED1_GPIO149

0.125W

Q1B

RN1907

D

E

L

_

1

R

S

U

3

4

7

k

4

1

0

k

5

S2

4

3

2

1

B3F-1000

Insures that

the DVI-D is

powered down

at powerup.

R109

10K

GPIO170

3

U4B

SN74LVC2G07DCKR

4

DVI_PUP

10

nRESET

8

AB3

AB4

AA4

AC2

AC3

AB1

AB2

AA3

Y2

Y3

Y4

V3

P21

N21

R21

M21

AF6

AE6

AF5

AE5

AE1

AD1

AD2

AC1

T27

U28

U27

U26

U25

V28

V27

V26

T28

T25

R28

T26

Y21

AA21

V21

U21

T21

K26

W21

AF10

AE10

AF11

AG12

AH12

AE13

AE11

AH9

AF13

AH14

AF9

AG9

AE7

AF7

AG7

AH7

AG8

AH8

AH26

AG26

AE14

AF18

AF19

AE21

AF21

R112

DNI,0603

R113

510,0603

USB2HS_DAT2 8

USB2HS_DAT7 8

USB2HS_DAT4 8

USB2HS_DAT5 8

USB2HS_DAT6 8

USB2HS_DAT3 8

MCBSP2_FSX 6

MCBSP2_CLKX 6

MCBSP2_DR 6

MCBSP2_DX 6

MCBSP3_FSX 8

USB0HS_DAT0 6

USB0HS_DAT1 6

USB0HS_DAT2 6

USB0HS_DAT3 6

USB0HS_DAT4 6

USB0HS_DAT5 6

USB0HS_DAT6 6

USB0HS_DAT7 6

USB0HS_CLK 6

USB0HS_STP 6

USB0HS_DIR 6

USB0HS_NXT 6

McBSP1_CLKR 8

McBSP1_FSR 8

McBSP1_DX 8

McBSP1_DR 8

MCBSP_CLKS 6

McBSP1_FSX 8

McBSP1_CLKX 8

R53

33

SYS_BOOT0_3

SYS_BOOT4

SYS_BOOT5

RA

RB

RC

RD

R29

R30

R31

R32

6

9

mSECURE

MMC1_WP

USB2HS_CLK 8

USB2HS_STP 8

USB2HS_DIR 8

USB2HS_NXT 8

USB2HS_DAT0 8

USB2HS_DAT1 8

VIO_1V8

10K,0603

10K,0603,DNI

10K,0603,DNI

10K,0603

SYS_BOOT6

R33

10K,0603

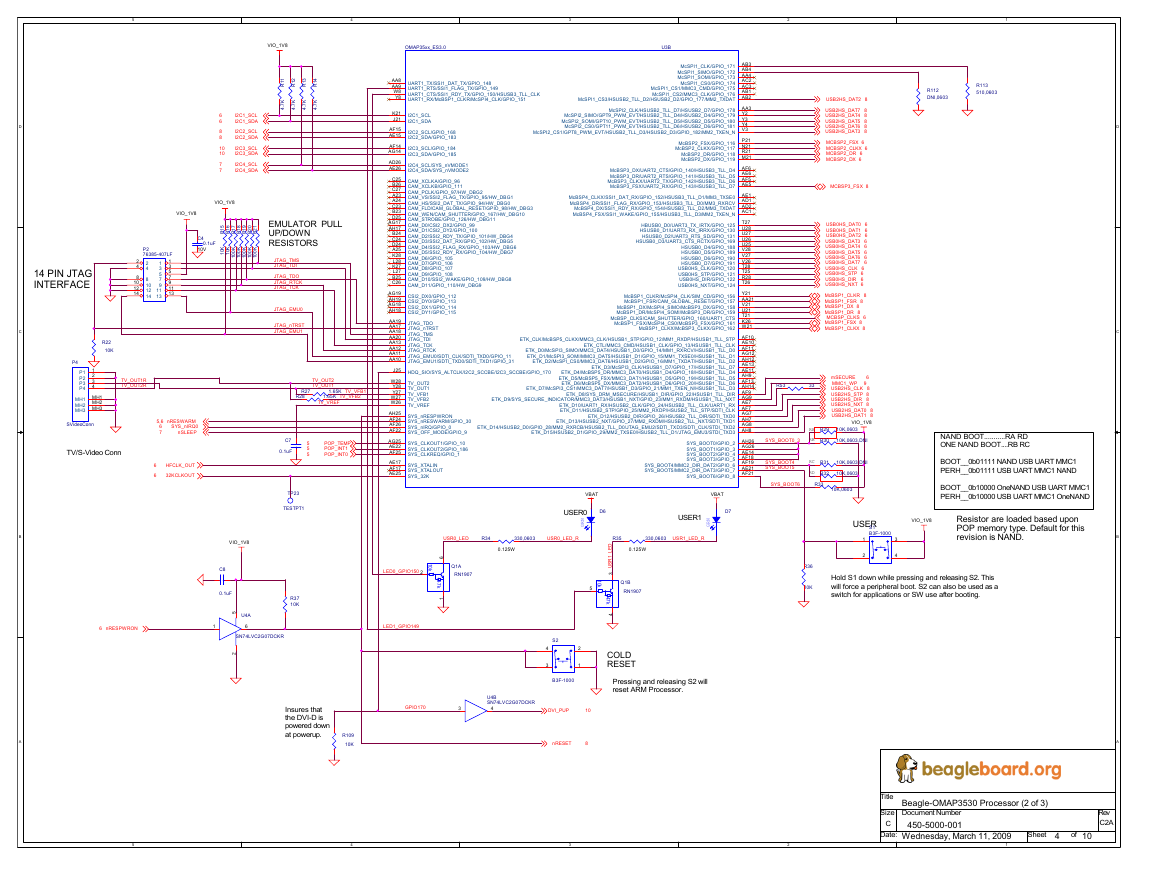

NAND BOOT...........RA RD

ONE NAND BOOT....RB RC

BOOT__0b01111 NAND USB UART MMC1

PERH__0b01111 USB UART MMC1 NAND

BOOT__0b10000 OneNAND USB UART MMC1

PERH__0b10000 USB UART MMC1 OneNAND

VIO_1V8

Resistor are loaded based upon

POP memory type. Default for this

revision is NAND.

USER

S1

B3F-1000

1

2

3

4

R36

10K

Hold S1 down while pressing and releasing S2. This

will force a peripheral boot. S2 can also be used as a

switch for applications or SW use after booting.

COLD

RESET

Pressing and releasing S2 will

reset ARM Processor.

Title

Beagle-OMAP3530 Processor (2 of 3)

C

Size Document Number

450-5000-001

Wednesday, March 11, 2009

Date:

Sheet

4

of

10

5

4

3

2

1

D

C

B

A

Rev

C2A

�

VIO_1V8

2

VIO_1V8

C133

10V

4.7uf,CER,0402

1

4

3

U3C

BG_TESTOUT

VPP

VDDS_MEM1

VDDS_MEM2

VDDS_MEM3

VDDS_MEM4

VDDS_MEM5

VDDS_MEM6

VDDS_MEM7

VDDS_MEM8

VDDS_MEM9

VDDS_MEM10

VDDS_MEM11

VDDS_MEM12

VDDS_MEM13

VDDS_MEM14

VDDS_MEM15

VDDS_MEM16

VDDS_MEM17

VDDS_MEM18

VDDS_MEM19

VDDS_MEM20

VDDS_MEM21

VDDS_WKUP_BG

POP_DDR_VDD_FT_1

POP_DDR_VDD_FT_2

POP_DDR_VDD_FT_3

POP_DDR_VDD_FT_4

POP_DDR_VDD_FT_5

POP_FLASH_VDD_FT_1

POP_FLASH_VDD_FT_2

POP_FLASH_VDD_FT_3

POP_FLASH_VDD_FT_4

POP_FLASH_VDD_FT_5

VDDS1

VDDS2

VDDS3

VDDS4

VDDS5

VDDS6

VDDS7

VDDS8

VDDS9

VDDS10

VDDS11

VDDS12

VDDS_SRAM

VDDS_MMC1

VDDS_SIM

VDDS_DPLL_DLL

VDDS_DPLL_PER

VDDS_SDI

VSS_SDI

VDDS_CSIb

VSS_CSIb

VDDS_DSI

VSS_DSI

VDDA_DAC

VSSA_DAC

VDDS_CSI2

VSS_CSI2

CAP_VDD_WKUP

CAP_VDD_SRAM_MPU_IVA

CAP_VDD_SRAM_CORE

CAP_VDD_DSI

U4

G1

F1

J1

U1

F2

J2

R4

A5

B5

AH6

A8

B8

A12

B12

C16

D16

A18

B18

A22

B22

C28

G28

AA14

A15

AF28

J28

M1

AE28

AF1

AH10

AH15

N1

AA1

AD3

W4

AD4

AE8

AF8

AE16

AF16

AE23

AF23

F25

F26

AG27

W16

K25

P25

K15

AA16

AE27

AA26

H28

M28

AG21

AH21

V25

Y26

AG20

AG16

AA15

V4

L21

AH20

AG13

AH16

AH13

AH11

AG11

C11

C13

C15

C17

C18

C20

VIO_1V8

C24

VIO_1V8

0.1uF

10V

C25

0.1uF

10V

0.1uF

10V

0.1uF

10V

0.1uF

10V

0.1uF

10V

0.1uF

10V

0.1uF

10V

VIO_1V8

C22

0.1uF

10V

VIO_1V8

C27

VIO_1V8

0.1uF

10V

C29

VIO_1V8

C31

0.1uF

10V

VIO_1V8

C33

0.1uF

10V

C34

0.1uF

10V

VIO_1V8

C137

10V

4.7uf,CER,0402

0.1uF

10V

VIO_1V8

VIO_1V8

C36

VMMC1

0.1uF

10V

VDD_SIM

C37

C39

0.1uF

10V

0.1uF

10V

VDD_PLL1

C41

C42

0.1uF

10V

0.1uF

10V

VDAC_1v8

VDDA_DAC

C46

C45

0.22uF

10V

0.1uF

10V

VDD_PLL2

C44

0.22uF

10V

7

6

S

S

V

6

6

S

S

V

5

6

S

S

V

4

6

S

S

V

3

6

S

S

V

2

6

S

S

V

1

6

S

S

V

0

6

S

S

V

9

5

S

S

V

8

5

S

S

V

7

5

S

S

V

6

5

S

S

V

5

5

S

S

V

4

5

S

S

V

3

5

S

S

V

2

5

S

S

V

1

5

S

S

V

0

5

S

S

V

9

4

S

S

V

8

4

S

S

V

7

4

S

S

V

6

4

S

S

V

5

4

S

S

V

4

4

S

S

V

3

4

S

S

V

2

4

S

S

V

1

4

S

S

V

0

4

S

S

V

9

3

S

S

V

8

3

S

S

V

7

3

S

S

V

6

3

S

S

V

5

3

S

S

V

4

3

S

S

V

3

3

S

S

V

2

3

S

S

V

1

3

S

S

V

0

3

S

S

V

9

2

S

S

V

8

2

S

S

V

7

2

S

S

V

6

2

S

S

V

5

2

S

S

V

4

2

S

S

V

3

2

S

S

V

2

2

S

S

V

1

2

S

S

V

0

2

S

S

V

9

1

S

S

V

8

1

S

S

V

7

1

S

S

V

6

1

S

S

V

5

1

S

S

V

4

1

S

S

V

3

1

S

S

V

2

1

S

S

V

1

1

S

S

V

0

1

S

S

V

9

S

S

V

8

S

S

V

7

S

S

V

6

S

S

V

5

S

S

V

4

S

S

V

3

S

S

V

2

S

S

V

1

S

S

V

7

2

G

7

2

B

6

2

C

A

6

2

R

6

2

L

6

2

A

5

2

C

A

5

2

Y

5

2

W

2

2

C

1

2

D

0

2

F

A

0

2

E

A

0

2

T

0

2

R

0

2

M

0

2

L

9

1

W

9

1

V

9

1

R

9

1

P

9

1

L

9

1

K

9

1

D

9

1

C

7

1

Y

7

1

W

7

1

K

7

1

J

6

1

K

6

1

J

4

1

W

3

1

Y

3

1

W

3

1

J

3

1

D

3

1

C

2

1

F

A

2

1

E

A

2

1

Y

2

1

K

2

1

J

0

1

W

0

1

V

0

1

P

0

1

K

0

1

D

0

1

C

9

V

9

U

9

P

9

N

9

K

7

D

7

C

4

P

4

E

3

P

3

J

3

E

3

A

6

G

A

3

G

A

3

W

2

G

A

2

U

2

B

CAP_VDD_WKUP

C47

1uF,CER

CAP_VDD_SRAM_MPU_IVA

CAP_VDD_SRAM_CORE

C49

C48

1uF,CER

1uF,CER

CAP_VDD_DSI

C50

POP_TQ_TEMP_S

POP_INT1_FT

POP_INT0_FT

R108

R107

R106

0.1uF

10V

0,DNI

0,DNI

0,DNI

POP_RESET_RP_FT

POP_TQ_TEMP_S

POP_FLASH_VPP_FT

POP_INT1_FT

POP_INT0_FT

VIO_1V8

VIO_1V8

C139

10V

4.7uf,CER,0402

VOCORE_1V3

C135

10V

4.7uf,CER,0402

D

VOCORE_1V3

C134

10V

4.7uf,CER,0402

VDD2

5

VOCORE_1V3

C9

C10

C12

C14

C16

C19

C21

0.1uF

10V

0.1uF

10V

0.1uF

10V

0.1uF

10V

0.1uF

10V

0.1uF

10V

0.1uF

10V

VDD2

C136

10V

4.7uf,CER,0402

VDD2

C

C138

10V

4.7uf,CER,0402

C23

C26

C28

C30

C32

C35

C38

C40

C43

0.1uF

10V

0.1uF

10V

0.1uF

10V

0.1uF

10V

0.1uF

10V

0.1uF

10V

0.1uF

10V

0.1uF

10V

0.1uF

10V

OMAP35xx_ES3.0

VDD_MPU_IVA1

VDD_MPU_IVA2

VDD_MPU_IVA3

VDD_MPU_IVA4

VDD_MPU_IVA5

VDD_MPU_IVA6

VDD_MPU_IVA7

VDD_MPU_IVA8

VDD_MPU_IVA9

VDD_MPU_IVA10

VDD_MPU_IVA11

VDD_MPU_IVA12

VDD_MPU_IVA13

VDD_MPU_IVA14

VDD_MPU_IVA15

VDD_MPU_IVA16

VDD_MPU_IVA17

VDD_MPU_IVA18

VDD_MPU_IVA19

VDD_MPU_IVA20

VDD_MPU_IVA21

VDD_MPU_IVA22

VDD_MPU_IVA23

VDD_MPU_IVA24

VDD_MPU_IVA25

VDD_MPU_IVA26

VDD_MPU_IVA27

VDD_CORE1

VDD_CORE2

VDD_CORE3

VDD_CORE4

VDD_CORE5

VDD_CORE6

VDD_CORE7

VDD_CORE8

VDD_CORE9

VDD_CORE10

VDD_CORE11

VDD_CORE12

VDD_CORE13

VDD_CORE14

VDD_CORE15

VDD_CORE16

VDD_CORE17

VDD_CORE18

VDD_CORE19

VDD_CORE20

VDD_CORE21

VDD_CORE22

VDD_CORE23

VDD_CORE24

VDD_CORE25

VDD_CORE26

VDD_CORE27

VDD_CORE28

VDD_CORE29

VDD_CORE30

VDD_CORE31

VDD_CORE32

VDD_CORE33

VDD_CORE34

POP_NC_A1

POP_NC_A2

POP_NC_A22

POP_NC_A23

POP_NC_B1

POP_NC_B23

POP_NC_AB1

POP_NC_AB23

POP_NC_AC1

POP_NC_AC2

POP_NC_AC22

POP_NC_AC23

POP_VSS_FT_1

POP_VSS_FT_2

POP_VSS_FT_3

POP_VSS_FT_4

POP_VSS_FT_5

POP_VSS_FT_6

POP_VSS_FT_7

POP_VSS_FT_8

POP_VSS_FT_9

POP_VSS_FT_10

J9

L9

M9

R9

T9

W9

Y9

J10

L10

M10

N10

R10

T10

U10

Y10

J11

K11

W11

Y11

W12

K13

J14

K14

Y14

J15

W15

Y15

H4

J4

AC4

D8

D9

AE9

D15

Y16

J18

K18

W18

Y18

AE18

J19

M19

N19

T19

U19

Y19

AE19

J20

K20

N20

P20

U20

V20

W20

Y20

D22

D23

AE24

E25

L25

M25

A1

A2

A27

A28

B1

B28

AG1

AG28

AH1

AH2

AH27

AH28

M2

N2

AA2

AF2

AG10

B15

AG15

M26

J27

AF27

B

A

D

C

B

A

Rev

C2A

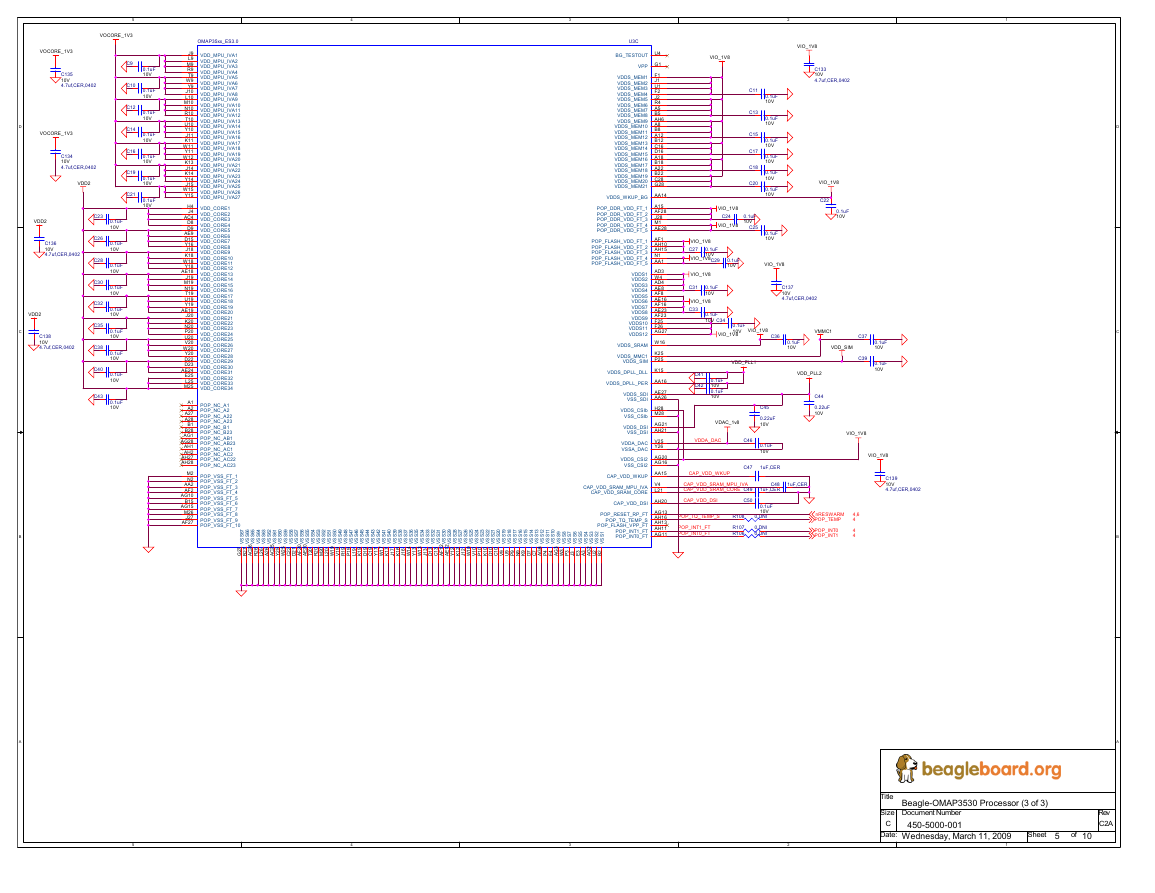

nRESWARM

POP_TEMP

POP_INT0

POP_INT1

4,6

4

4

4

Title

Beagle-OMAP3530 Processor (3 of 3)

C

Size Document Number

450-5000-001

Wednesday, March 11, 2009

Date:

Sheet

5

of

10

5

4

3

2

1

�

TP19

TESTPT1

R38

5

HFCLK_26MHz

HFCLK_OUT

4

VIO_1V8

4

MCBSP_CLKS

33

HFCLKOUT

R39

R40

10K

33

CLK_REQ

CLK256FS

4

4

4

4

USB0HS_CLK

USB0HS_STP

USB0HS_DIR

USB0HS_NXT

4

4

4

4

4

4

4

4

USB0HS_DAT0

USB0HS_DAT1

USB0HS_DAT2

USB0HS_DAT3

USB0HS_DAT4

USB0HS_DAT5

USB0HS_DAT6

USB0HS_DAT7

VBUS_5V0

R43

T2_VBUS

0,0603

VBAT

C127

2

2

2

HSUSB_DP

HSUSB_DN

HSUSB_ID

10V

4.7uf,CER,0402

4

4

4

I2C1_SDA

I2C1_SCL

SYS_nIRQ0

VIO_1V8

nRESWARM

nRESPWRON

4,5

4

R45

PWRON

4.7K

R47

4.7K

2

C55

T2_VREF

1

1uF,CER

VBAT

VIO_1V8

R61

10K

4,5

mSECURE

4

4

4

4

MCBSP2_CLKX

MCBSP2_FSX

MCBSP2_DX

MCBSP2_DR

D

C

B

C68

22PF

T2_XOUT

1

Y2

32KHz,FX135

2

C69

22PF

T2_XIN

A

4

32KCLKOUT

VBAT

D12

GRN

LTST-C150CKT

8

nEN_USB_PWR

100PF

C70

PMU_STAT

PMU_STAT

5

R48

330,0603

T2_LED_B

A14

R12

C6

D7

G10

D13

L15

L14

L13

M13

K14

K13

J14

J13

G14

G13

F14

F13

R8

T10

T11

R11

D4

D5

F10

F9

A11

B13

A13

N16

C13

K11

J11

H8

R1

T2

T15

R16

C5

C3

L3

K6

K4

K3

B16

A15

A1

A16

T1

T16

P15

P16

N10

G15

F15

G11

F16

4

HFCLKIN

HFCLKOUT

CLKEN

CLKEN2

CLKREQ

CLK256FS

UCLK

STP/GPIO.9

DIR/GPIO.10

NXT/GPIO.11

CLOCKS

IO_1P8

ULPI

DATA0/UART4.TXD

DATA1/UART4.RXD

DATA2/UART4.RTSI

DATA3/UART4.CTSO/GPIO.12

DATA4/GPIO.14

DATA5/GPIO.3

DATA6/GPIO.4

DATA7/GPIO.5

PCM BT

BT.PCM.VDX/GPIO.17/DIG.MIC.CLK1

BT.PCM.VDR/GPIO.16/DIG.MIC.CLK0

IO_1P8

TDM

IO_1P8

TEST

32kHz

IO_1P8

LED

I2S.CLK

I2S.SYNC

I2S.DIN

I2S.DOUT

JTAG.TCK/BERCLK

JTAG.TDI/BERDATA

TEST

TESTV2

TESTV1

TEST.RESET

32KXOUT

32KXIN

32KCLKOUT

LEDB/VIBRA.M

LEDA/VIBRA.P

LEDSYNC/GPIO.13

LEDGND

4

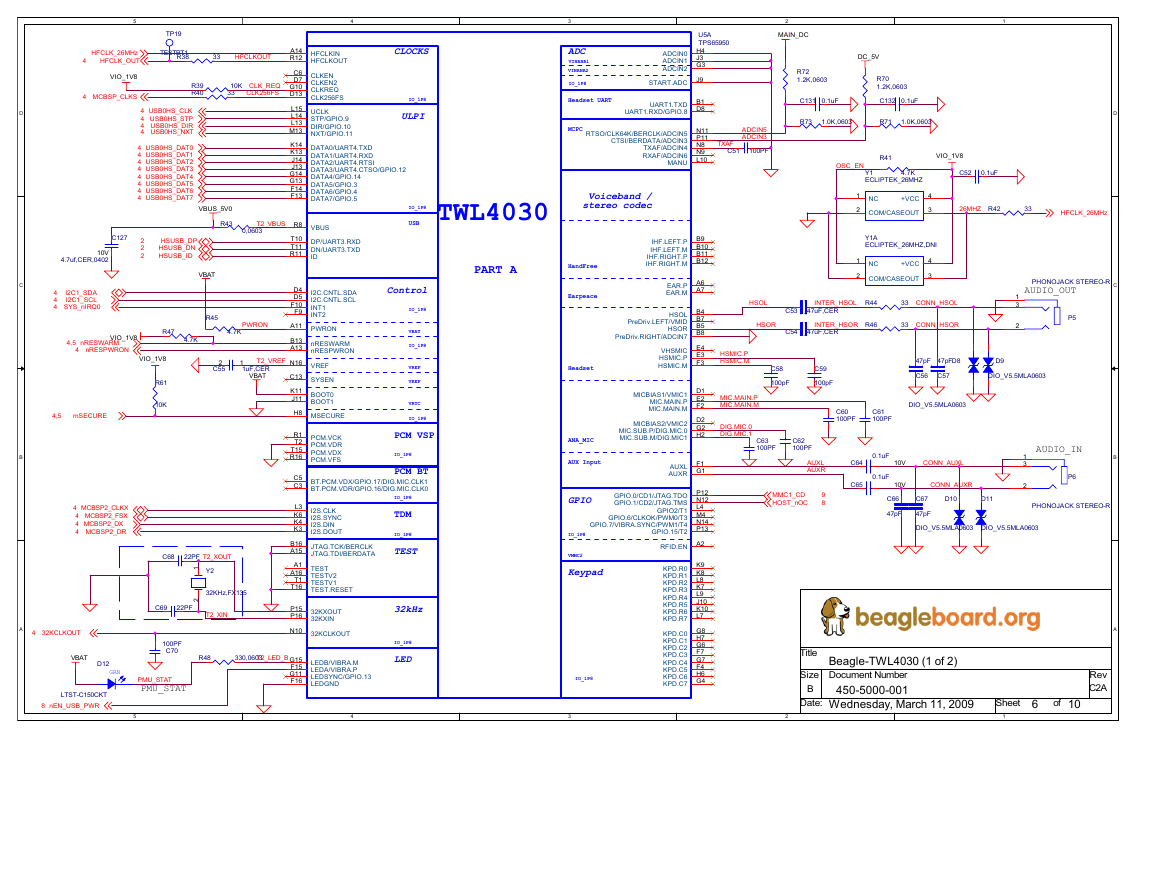

IO_1P8

USB

TWL4030

Voiceband /

stereo codec

VBUS

DP/UART3.RXD

DN/UART3.TXD

ID

I2C.CNTL.SDA

I2C.CNTL.SCL

INT1

INT2

PWRON

nRESWARM

nRESPWRON

VREF

SYSEN

BOOT0

BOOT1

MSECURE

PCM.VCK

PCM.VDR

PCM.VDX

PCM.VFS

PART A

Control

IO_1P8

VBAT

IO_1P8

VREF

VREF

VRTC

IO_1P8

PCM VSP

IO_1P8

HandFree

Earpeace

Headset

ANA_MIC

AUX Input

3

ADC

VINANA1

VINANA2

IO_1P8

ADCIN0

ADCIN1

ADCIN2

START.ADC

Headset UART

UART1.TXD

UART1.RXD/GPIO.8

MCPC

RTSO/CLK64K/BERCLK/ADCIN5

CTSI/BERDATA/ADCIN3

TXAF/ADCIN4

RXAF/ADCIN6

MANU

U5A

TPS65950

H4

J3

G3

J9

B1

D8

N11

P11

N8

N9

L10

ADCIN5

ADCIN3

100PF

TXAF

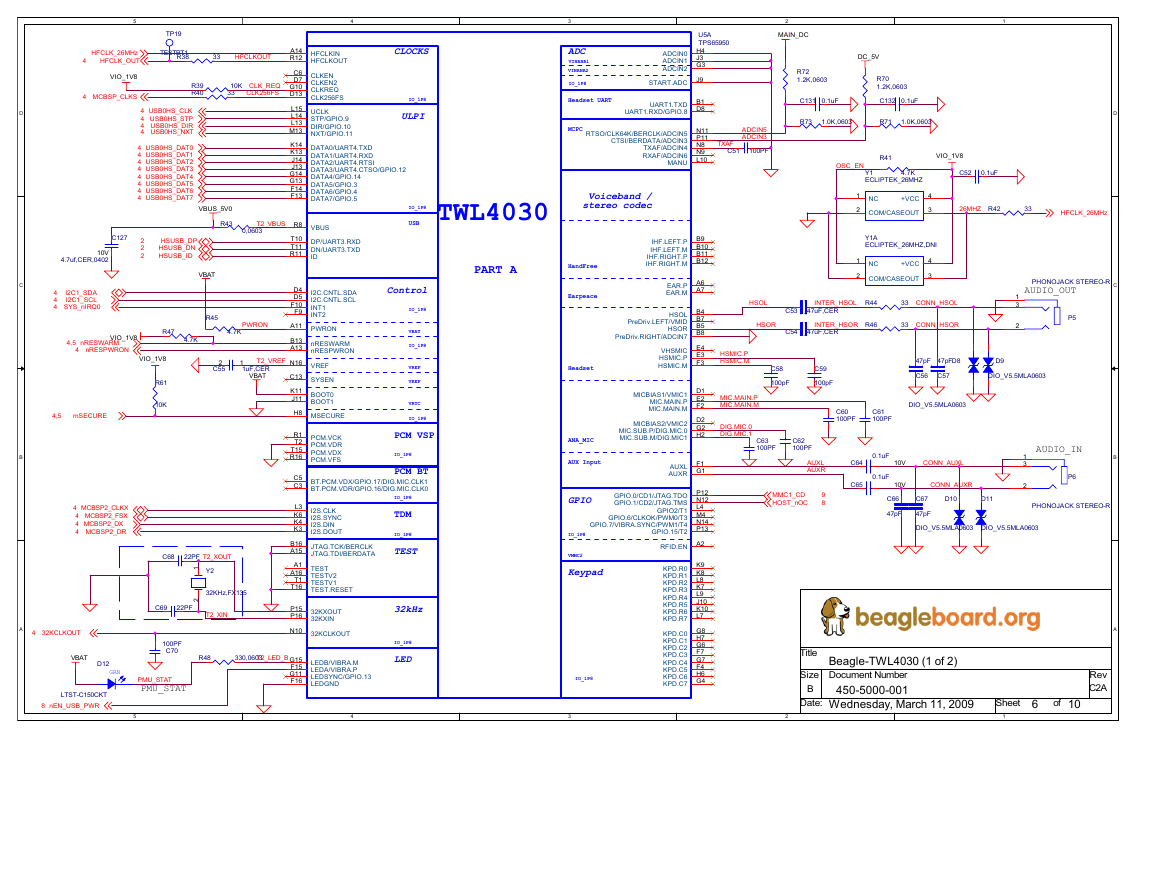

C51

2

MAIN_DC

1

R72

1.2K,0603

DC_5V

R70

1.2K,0603

C131 0.1uF

C132 0.1uF

R73

1.0K,0603

R71

1.0K,0603

D

R41

VIO_1V8

OSC_EN

1

2

1

2

Y1

ECLIPTEK_26MHZ

4.7K

NC

+VCC

COM/CASE

OUT

4

3

Y1A

ECLIPTEK_26MHZ,DNI

NC

+VCC

COM/CASE

OUT

4

3

C52

0.1uF

26MHZ

R42

33

HFCLK_26MHz

PHONOJACK STEREO-R

AUDIO_OUT

C

P5

1

3

2

HSOL

HSOR

INTER_HSOL

47uF,CER

INTER_HSOR

47uF,CER

R44

R46

C53

C54

33

CONN_HSOL

33

CONN_HSOR

HSMIC.P

HSMIC.M

MIC.MAIN.P

MIC.MAIN.M

C58

100pF

C59

100pF

DIG.MIC.0

DIG.MIC.1

C63

100PF

C62

100PF

AUXL

AUXR

MMC1_CD

HOST_nOC

9

8

47pF

47pF

D8

D9

C56

C57

DIO_V5.5MLA0603

C60

100PF

C61

100PF

DIO_V5.5MLA0603

0.1uF

0.1uF

C64

C65

10V

CONN_AUXL

10V

CONN_AUXR

AUDIO_IN

P6

1

3

2

C66

47pF

C67

47pF

D10

D11

PHONOJACK STEREO-R

DIO_V5.5MLA0603

DIO_V5.5MLA0603

B

A

Title

Beagle-TWL4030 (1 of 2)

B

Size Document Number

450-5000-001

Wednesday, March 11, 2009

Date:

2

Rev

C2A

Sheet

1

6

of

10

IHF.LEFT.P

IHF.LEFT.M

IHF.RIGHT.P

IHF.RIGHT.M

B9

B10

B11

B12

EAR.P

EAR.M

HSOL

PreDriv.LEFT/VMID

HSOR

PreDriv.RIGHT/ADCIN7

VHSMIC

HSMIC.P

HSMIC.M

MICBIAS1/VMIC1

MIC.MAIN.P

MIC.MAIN.M

MICBIAS2/VMIC2

MIC.SUB.P/DIG.MIC.0

MIC.SUB.M/DIG.MIC1

AUXL

AUXR

A6

A7

B4

B7

B5

B8

E4

E3

F3

D1

E2

F2

D2

G2

H2

F1

G1

P12

N12

L4

M4

N14

P13

A2

K9

K8

L8

K7

L9

J10

K10

L7

G8

H7

G6

F7

G7

F4

H6

G4

RFID.EN

KPD.R0

KPD.R1

KPD.R2

KPD.R3

KPD.R4

KPD.R5

KPD.R6

KPD.R7

KPD.C0

KPD.C1

KPD.C2

KPD.C3

KPD.C4

KPD.C5

KPD.C6

KPD.C7

GPIO

GPIO.0/CD1/JTAG.TDO

GPIO.1/CD2/JTAG.TMS

GPIO2/T1

GPIO.6/CLKOK/PWM0/T3

GPIO.7/VIBRA.SYNC/PWM1/T4

GPIO.15/T2

IO_1P8

VMMC2

Keypad

IO_1P8

3

�

D

C

B

A

5

4

3

2

1

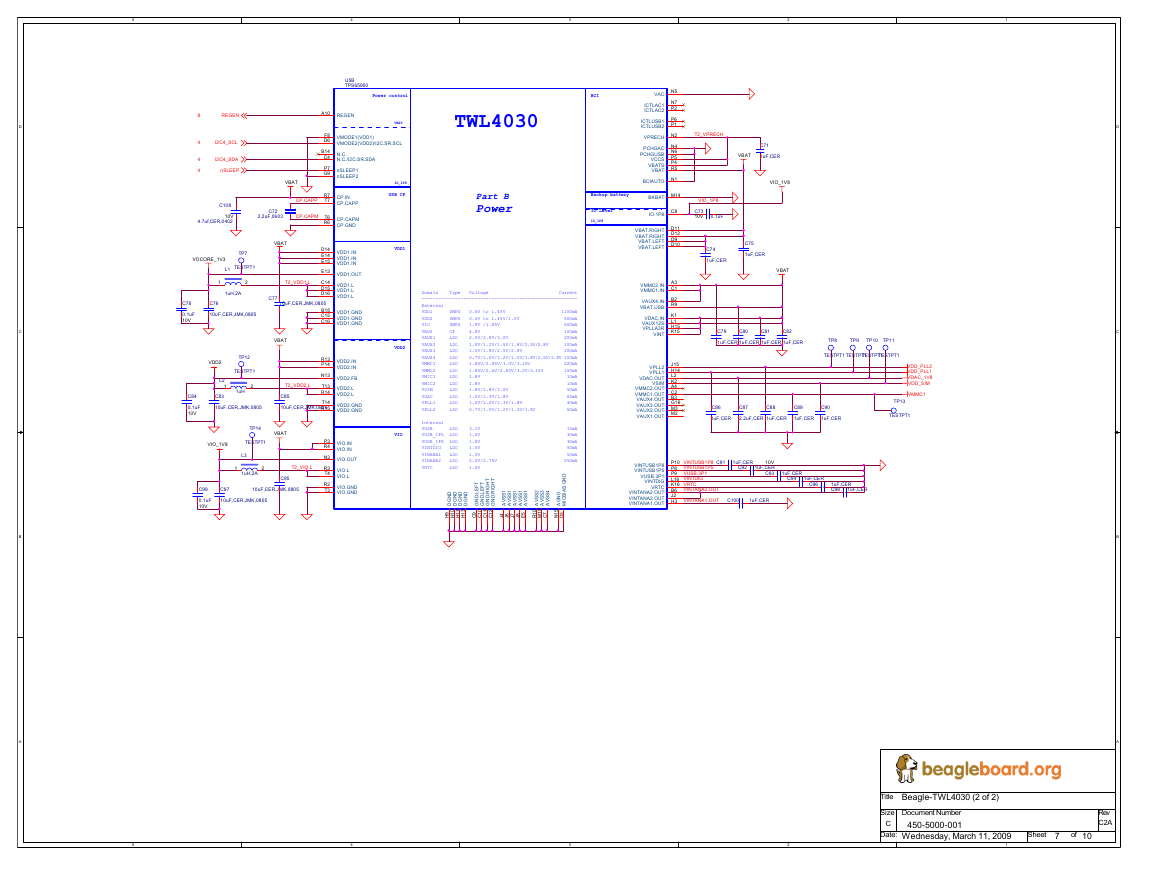

U5B

TPS65950

A10

REGEN

VBAT

VMODE1(VDD1)

VMODE2(VDD2)/I2C.SR.SCL

N.C.

N.C./I2C.SR.SDA

Power control

BCI

TWL4030

Part B

Power

Backup battery

IO Level

IO_1P8

8

4

4

4

REGEN

I2C4_SCL

I2C4_SDA

nSLEEP

C108

10V

4.7uf,CER,0402

VBAT

C72

2.2uF,0603

CP.CAPP

CP.CAPM

VOCORE_1V3

TP7

VBAT

TESTPT1

L1

1

2

1uH,2A

C76

10uF,CER,JMK,0805

C77

C78

0.1uF

10V

T2_VDD1.L

10uF,CER,JMK,0805

B15

C15

C16

TP12

TESTPT1

2

1uH

VDD2

L2

1

C83

10uF,CER,JMK,0805

C84

0.1uF

10V

VBAT

T2_VDD2.L

C85

T14

10uF,CER,JMK,0805

R15

F8

D6

B14

C4

P7

G9

R7

T7

T6

R6

D14

E14

E15

E13

C14

D15

D16

R13

P14

N13

T13

R14

nSLEEP1

nSLEEP2

CP.IN

CP.CAPP

CP.CAPM

CP.GND

VDD1.IN

VDD1.IN

VDD1.IN

VDD1.OUT

VDD1.L

VDD1.L

VDD1.L

VDD1.GND

VDD1.GND

VDD1.GND

VDD2.IN

VDD2.IN

VDD2.FB

VDD2.L

VDD2.L

VDD2.GND

VDD2.GND

TP14

VBAT

VIO_1V8

TESTPT1

L3

1

2

1uH,2A

T2_VIO.L

C95

C99

0.1uF

10V

C97

10uF,CER,JMK,0805

10uF,CER,JMK,0805

P3

R4

N3

R3

T4

R2

T3

VIO.IN

VIO.IN

VIO.OUT

VIO.L

VIO.L

VIO.GND

VIO.GND

IO_1P8

USB CP

VDD1

VDD2

VIO

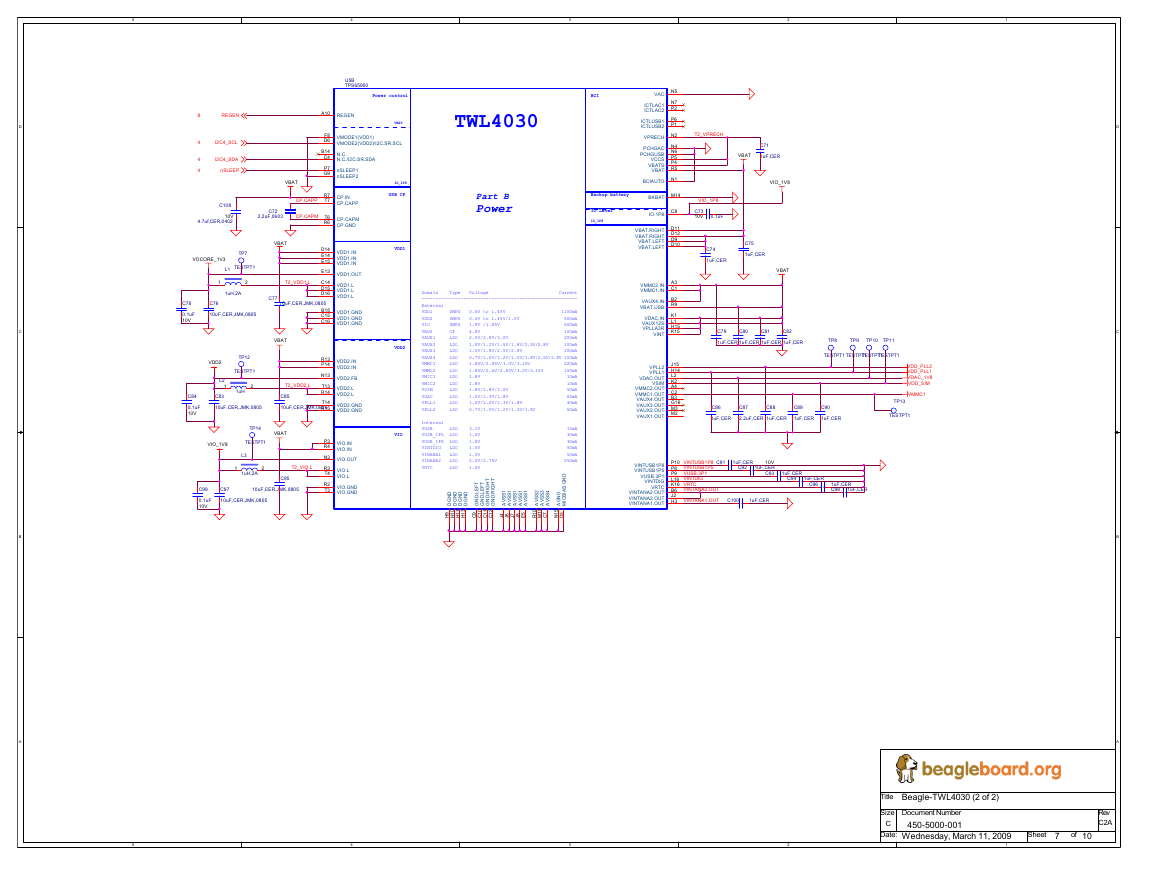

Domain Type Voltage Current

---------------------------------------------------------

External

VDD1 SMPS 0.6V to 1.45V 1100mA

VDD2 SMPS 0.6V to 1.45V/1.5V 600mA

VIO SMPS 1.8V /1.85V 600mA

VBUS CP 4.8V 100mA

VAUX1 LDO 2.5V/2.8V/3.0V 200mA

VAUX2 LDO 1.0V/1.2V/1.5V/1.8V/2.5V/2.8V 100mA

VAUX3 LDO 1.5V/1.8V/2.5V/2.8V 200mA

VAUX4 LDO 0.7V/1.0V/1.2V/1.5V/1.8V/2.5V/2.8V 100mA

VMMC1 LDO 1.85V/2.85V/3.0V/3.15V 220mA

VMMC2 LDO 1.85V/2.6V/2.85V/3.0V/3.15V 100mA

VMIC1 LDO 1.8V 10mA

VMIC2 LDO 1.8V 10mA

VSIM LDO 1.8V/2.8V/3.0V 50mA

VDAC LDO 1.2V/1.3V/1.8V 65mA

VPLL1 LDO 1.0V/1.2V/1.3V/1.8V 40mA

VPLL2 LDO 0.7V/1.0V/1.2V/1.3V/1.8V 60mA

Internal

VUSB LDO 3.1V 15mA

VUSB_1P5 LDO 1.5V 30mA

VUSB_1P8 LDO 1.8V 30mA

VINTDIG LDO 1.5V 50mA

VINANA1 LDO 1.5V 50mA

VINANA2 LDO 2.5V/2.75V 250mA

VRTC LDO 1.5V

T

F

E

L

D

N

G

T

F

E

L

D

N

G

.

.

I

I

T

H

G

R

D

N

G

T

H

G

R

D

N

G

.

.

D

N

G

D

D

N

G

D

D

N

G

D

D

N

G

D

0

1

H

1

1

H

3

1

H

9

H

0

1

C

1

1

C

2

1

C

9

C

1

S

S

V

A

1

S

S

V

A

1

S

S

V

A

1

S

S

V

A

1

S

S

V

A

2

S

S

V

A

3

S

S

V

A

4

S

S

V

A

4

J

6

J

7

J

8

J

5

E

0

1

R

5

1

M

7

C

.

D

N

G

S

A

B

C

M

I

I

D

N

G

A

5

1

N

3

D

VAC

ICTLAC1

ICTLAC2

ICTLUSB1

ICTLUSB2

VPRECH

PCHGAC

PCHGUSB

VCCS

VBATS

VBAT

BCIAUTO

BKBAT

IO.1P8

VBAT.RIGHT

VBAT.RIGHT

VBAT.LEFT

VBAT.LEFT

VMMC2.IN

VMMC1.IN

VAUX4.IN

VBAT.USB

VDAC.IN

VAUX12S

VPLLA3R

VINT

VPLL2

VPLL1

VDAC.OUT

VSIM

VMMC2.OUT

VMMC1.OUT

VAUX4.OUT

VAUX3.OUT

VAUX2.OUT

VAUX1.OUT

N5

N7

P2

P6

P1

N2

N4

N6

P5

P4

R5

N1

M14

C8

D11

D12

D9

D10

A3

C1

B2

R9

K1

L1

H15

K15

J15

H14

L2

K2

A4

C2

B3

G16

M3

M2

C71

VBAT

1uF,CER

VIO_1V8

T2_VPRECH

VIO_1P8

C73

10V

0.1uF

C74

1uF,CER

C75

1uF,CER

VBAT

C79

C80

C81

C82

1uF,CER

1uF,CER

1uF,CER

1uF,CER

TP8

TP9

TP10

TP11

TESTPT1

TESTPT1

TESTPT1

TESTPT1

C86

C87

C88

C89

C90

1uF,CER

2.2uF,CER

1uF,CER

1uF,CER

1uF,CER

VINTUSB1P8

VINTUSB1P5

VUSB.3P1

VINTDIG

VRTC

VINTANA2.OUT

VINTANA2.OUT

VINTANA1.OUT

P10

P8

P9

L16

K16

B6

J2

H3

1uF,CER

C92

10V

1uF,CER

C93

C91

VINTUSB1P8

VINTUSB1P5

VUSB.3P1

VINTDIG

VRTC

VINTANA2.OUT

VINTANA1.OUT

C100

1uF,CER

1uF,CER

C94

1uF,CER

C96

1uF,CER

C98

1uF,CER

D

C

B

A

Rev

C2A

Sheet

7

of

10

VDD_PLL2

VDD_PLL1

VDAC_1V8

VDD_SIM

VMMC1

TP13

TESTPT1

Title

Beagle-TWL4030 (2 of 2)

C

Size Document Number

450-5000-001

Wednesday, March 11, 2009

Date:

5

4

3

2

1

�

D

C

B

A

5

4

3

2

1

VIO_1V8

USB HOST INTERFACE

DC_5V

VBAT

R49

10K

TP20

TESTPT1

2

3

4

1

U6

IN

OUT

IN

OUT

EN OUT

GND

OC

PAD

8

7

6

5

9

TPS2061 (DGN)

6

nEN_USB_PWR

HOST_nOC

6

U7

STP

DIR

NXT

CLKOUT

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

VBUS

DM

DP

ID

RBIAS

VDD3.3

VDD1.8

VBAT

GND

RESETB

REFCLK

USB3322 (CSP)

A3

A4

B5

A5

B4

C5

C4

D5

D4

E5

E4

D3

B2

A2

4

4

4

USB2HS_STP

USB2HS_DIR

USB2HS_NXT

4

4

4

4

4

4

4

4

USB2HS_DAT0

USB2HS_DAT1

USB2HS_DAT2

USB2HS_DAT3

USB2HS_DAT4

USB2HS_DAT5

USB2HS_DAT6

USB2HS_DAT7

4

USB2HS_nRST

USB2HS_CLK

4

1

1

1

R

K

0

1

C2

D1

E1

B1

A1

D2

B3

C1

C3

USB33_VBUS

R50

10K,0603

USB33_ID

USB33_RBIAS

R52

R51

8.064k

0

USB33_VDD3.3

VIO_1V8

C103

C102

0.1uF

10V

10V

4.7uf,CER,0402

10V

4.7uf,CER,0402

C105

C104

0.1uF

10V

VBAT

C107

0.1uF

10V

C106

10V

4.7uf,CER,0402

+ C101

100uf, 6.3V

16V

Power Control

HOST_VBUS

HOST_D-

HOST_D+

P7

USB-A Conn. - 87520-xx1xx

1

2

3

4

VBUS

D-

D+

GND

SHIELD

SHIELD

5

6

Host Connector

Expansion

Connector

DC_5V

J3

VIO_1V8

2

4

6

8

10

12

14

16

18

20

22

24

26

28

1

3

5

7

9

11

13

15

17

19

21

23

25

27

HEADER 14X2,DNI

MMC2_DAT7 3

MMC2_DAT6 3

MMC2_DAT5 3

MMC2_DAT4 3

MMC2_DAT3 3

MMC2_DAT2 3

MMC2_DAT1 3

MMC2_DAT0 3

MMC2_CMD 3

MMC2_CLKO 3

I2C2_SDA

4

7

REGEN

Title

Beagle-USB Host and Expansion Connector.

4

4

4

4

4

4

4

4

4

4

4

MCBSP3_DX

MCBSP3_CLKX

MCBSP3_FSX

MCBSP3_DR

McBSP1_DX

McBSP1_CLKX

McBSP1_FSX

McBSP1_DR

McBSP1_CLKR

McBSP1_FSR

I2C2_SCL

4

nRESET

5

4

3

2

B

Size Document Number

450-5000-001

Wednesday, March 11, 2009

Date:

Rev

C2A

Sheet

1

8

of

10

D

C

B

A

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc