62 else //表示按下,跳转下一个状态

63 begin

64 data_flag <=1'b0;

65 state <=s1;

66 end

67 end

68 s1:begin

69 if(row ==4'b1111) //如果是抖动跳转0状态

70 begin

71 cnt <=19'b0;

72 state <=s0;

73 end

74 else

75 begin

76 if(cnt

99 end

100 else

101 begin

102 col <=col;

103 end

104 end

105 end

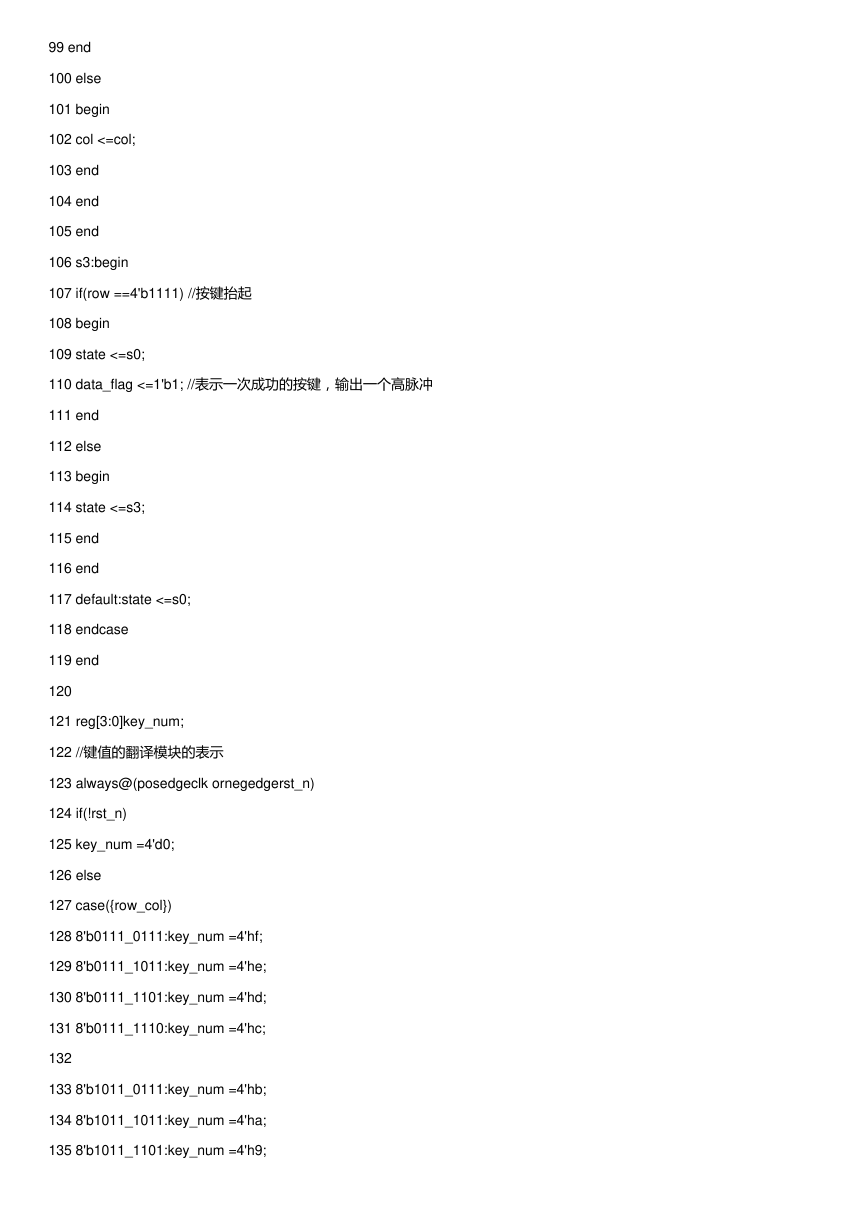

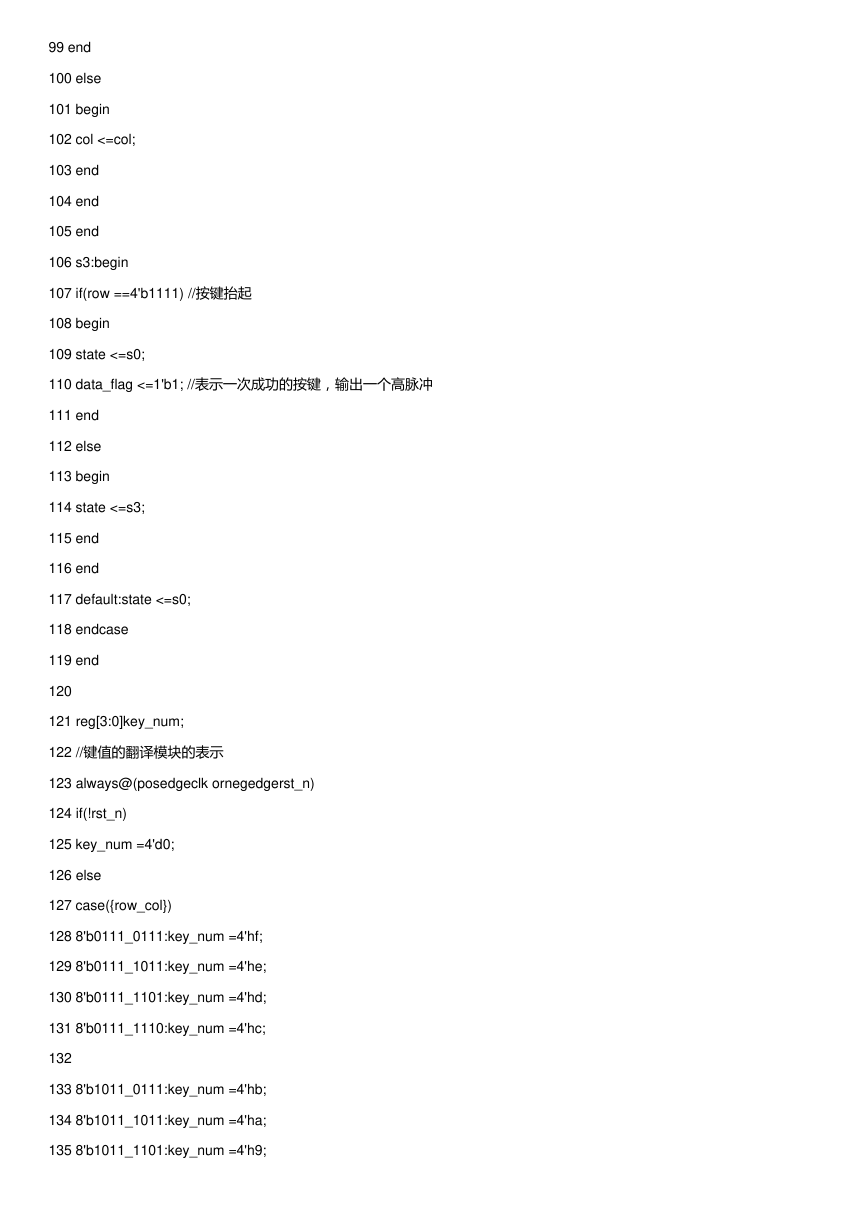

106 s3:begin

107 if(row ==4'b1111) //按键抬起

108 begin

109 state <=s0;

110 data_flag <=1'b1; //表示一次成功的按键,输出一个高脉冲

111 end

112 else

113 begin

114 state <=s3;

115 end

116 end

117 default:state <=s0;

118 endcase

119 end

120

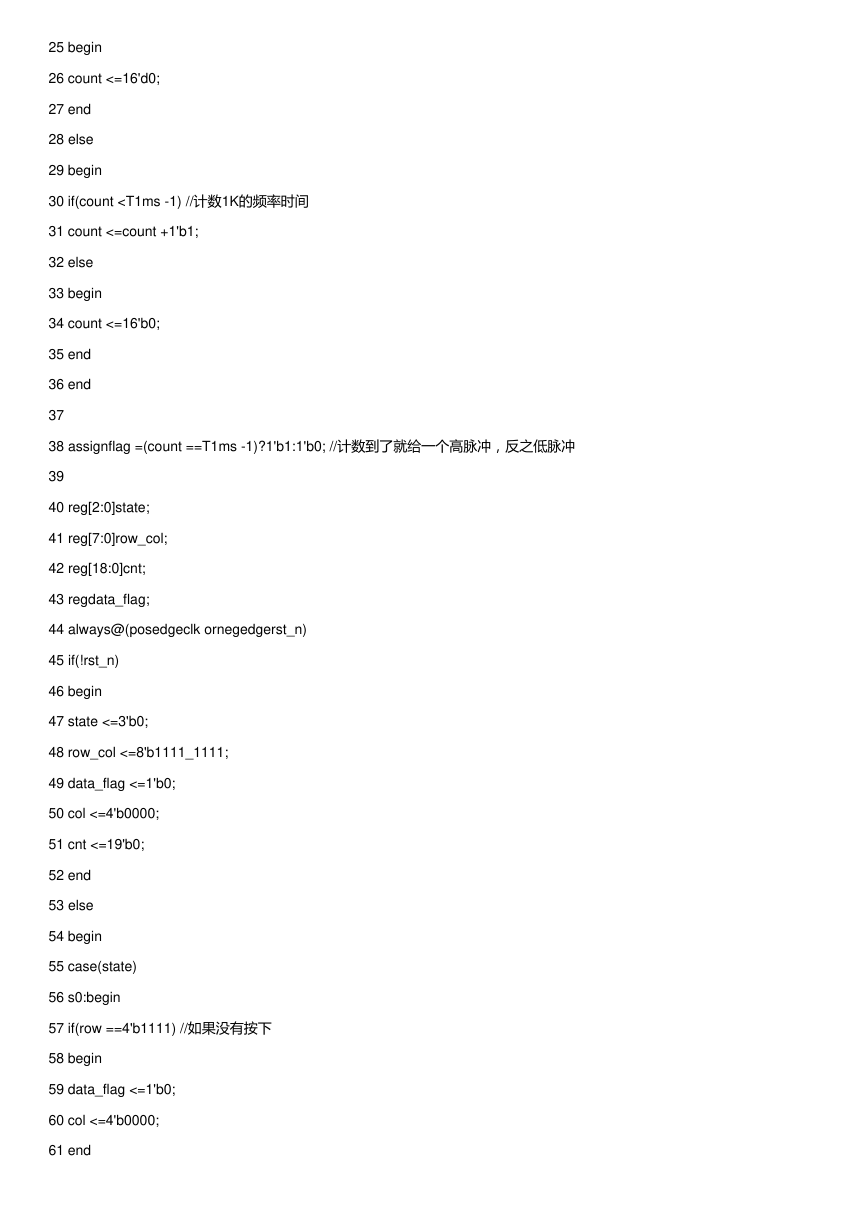

121 reg[3:0]key_num;

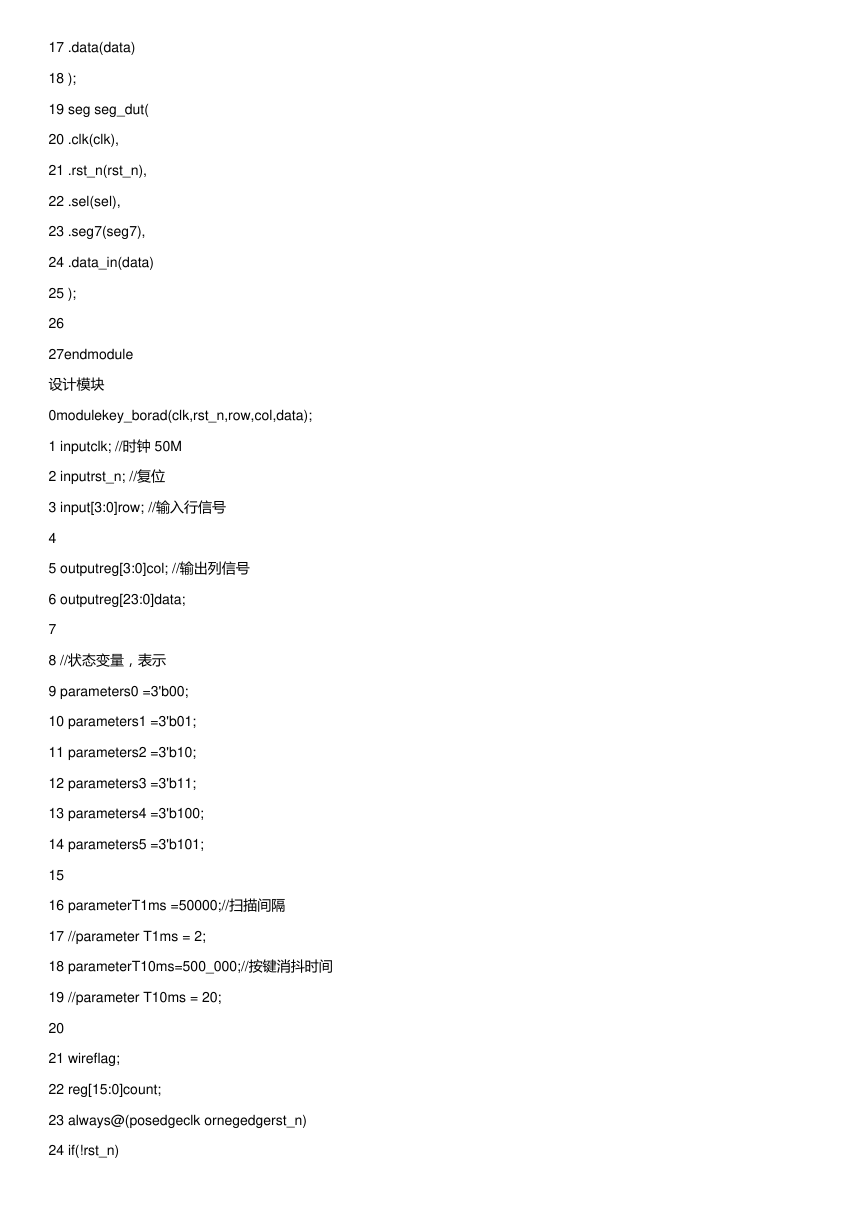

122 //键值的翻译模块的表示

123 always@(posedgeclk ornegedgerst_n)

124 if(!rst_n)

125 key_num =4'd0;

126 else

127 case({row_col})

128 8'b0111_0111:key_num =4'hf;

129 8'b0111_1011:key_num =4'he;

130 8'b0111_1101:key_num =4'hd;

131 8'b0111_1110:key_num =4'hc;

132

133 8'b1011_0111:key_num =4'hb;

134 8'b1011_1011:key_num =4'ha;

135 8'b1011_1101:key_num =4'h9;

�

136 8'b1011_1110:key_num =4'h8;

137

138 8'b1101_0111:key_num =4'h7;

139 8'b1101_1011:key_num =4'h6;

140 8'b1101_1101:key_num =4'h5;

141 8'b1101_1110:key_num =4'h4;

142

143 8'b1110_0111:key_num =4'h3;

144 8'b1110_1011:key_num =4'h2;

145 8'b1110_1101:key_num =4'h1;

146 8'b1110_1110:key_num =4'h0;

147 default:;

148 endcase

149

150

151

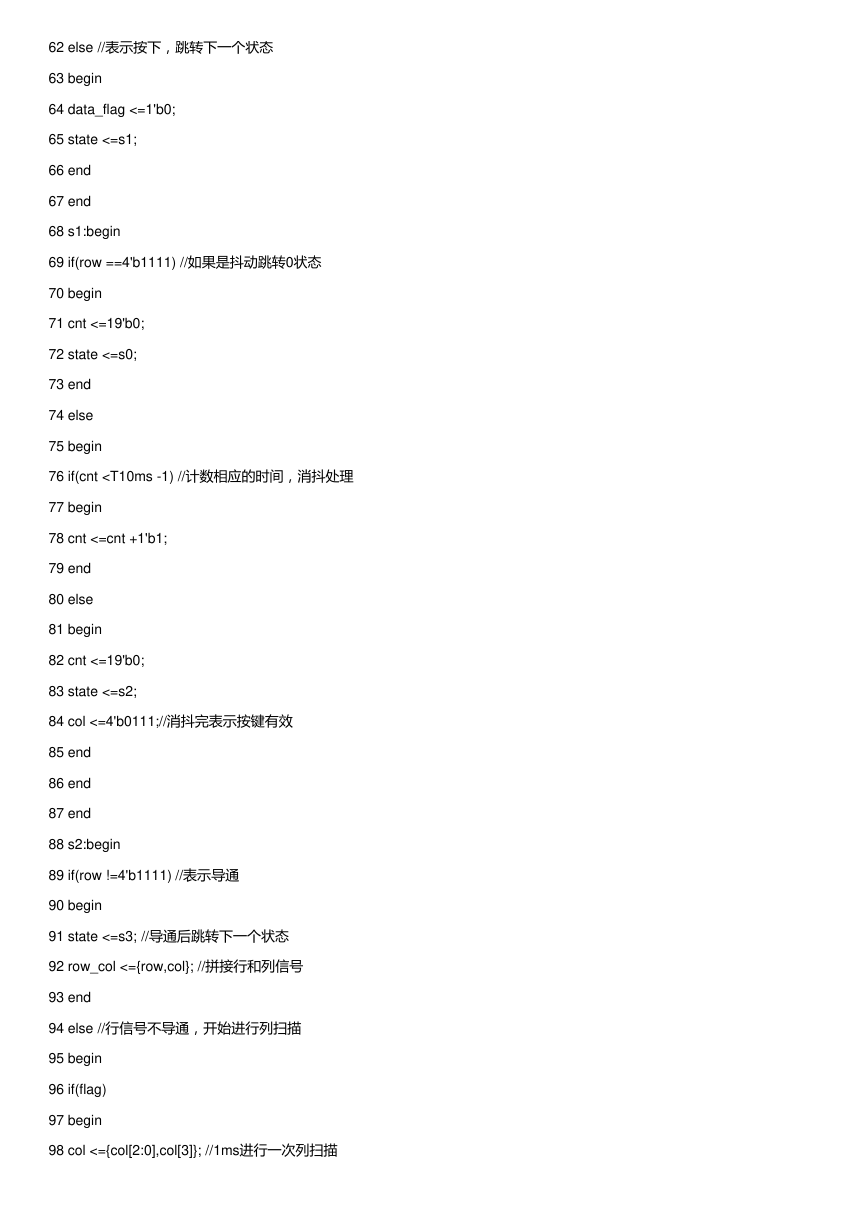

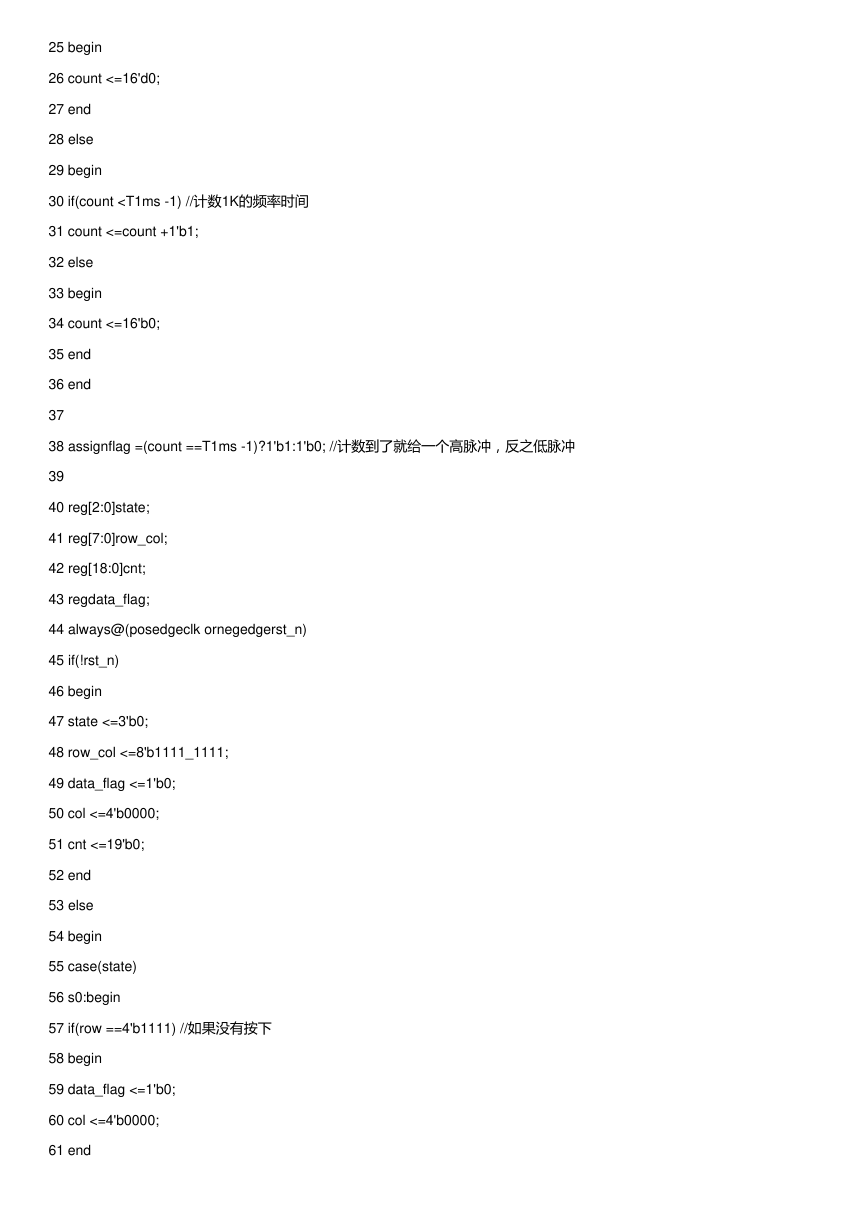

152 //计算模块的表示

153 reg[2:0]state_s;//状态变量

154 reg[23:0]num1,num2,data_in,data_t; //信号变量

155 reg[3:0]flag_s;//运算符

156 always@(posedgeclk ornegedgerst_n)

157 begin

158 if(!rst_n)

159 begin

160 data <=24'b0;

161 state_s <=s0;

162 num1 <=24'b0;

163 num2 <=24'b0;

164 data_t <=24'b0;

165 flag_s <=4'b0;

166 data_in <=24'b0;

167 end

168 else

169 begin

170 case(state_s)

171 s0:begin

172 if(data_flag) //如果有一次按下

�

173 begin

174 if(key_num <4'd9)//键值小于9便是有效

175 begin

176 num1 <=num1*10+key_num;//BCD码转为2进制

177 data <={data[19:0],key_num};//数码管移位

178 end

179 if(key_num >4'd9&&key_num <4'd14)//10 -- 13 表示运算符

180 begin

181 data <=24'b0;

182 state_s <=s1;

183 flag_s <=key_num;

184 end

185 else//否则无效信号

186 state_s <=s0;

187 end

188 end

189 s1:begin

190 if(data_flag)//如果有一次按下

191 begin

192 if(key_num <4'd9)//键值小于9便是有效

193 begin

194 num2 <=10*num2 +key_num;//BCD码转为2进制

195 data <={data[19:0],key_num};//数码管移位

196 end

197 if(key_num >4'd9&&key_num <4'd14)//10 -- 13 表示运算符

198 begin

199 state_s <=s1;

200 end

201 if(key_num ==15)//表示等于

202 begin

203 state_s <=s2;

204 end

205 end

206 end

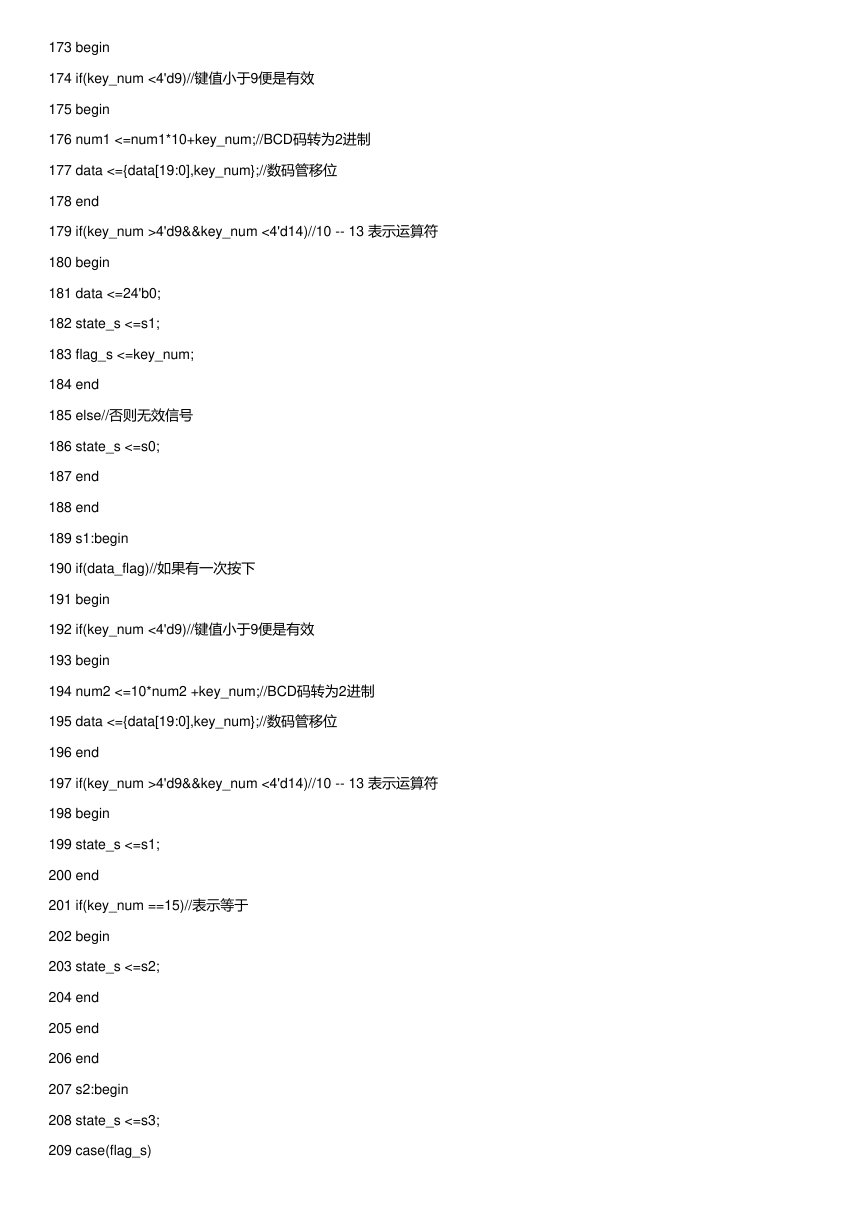

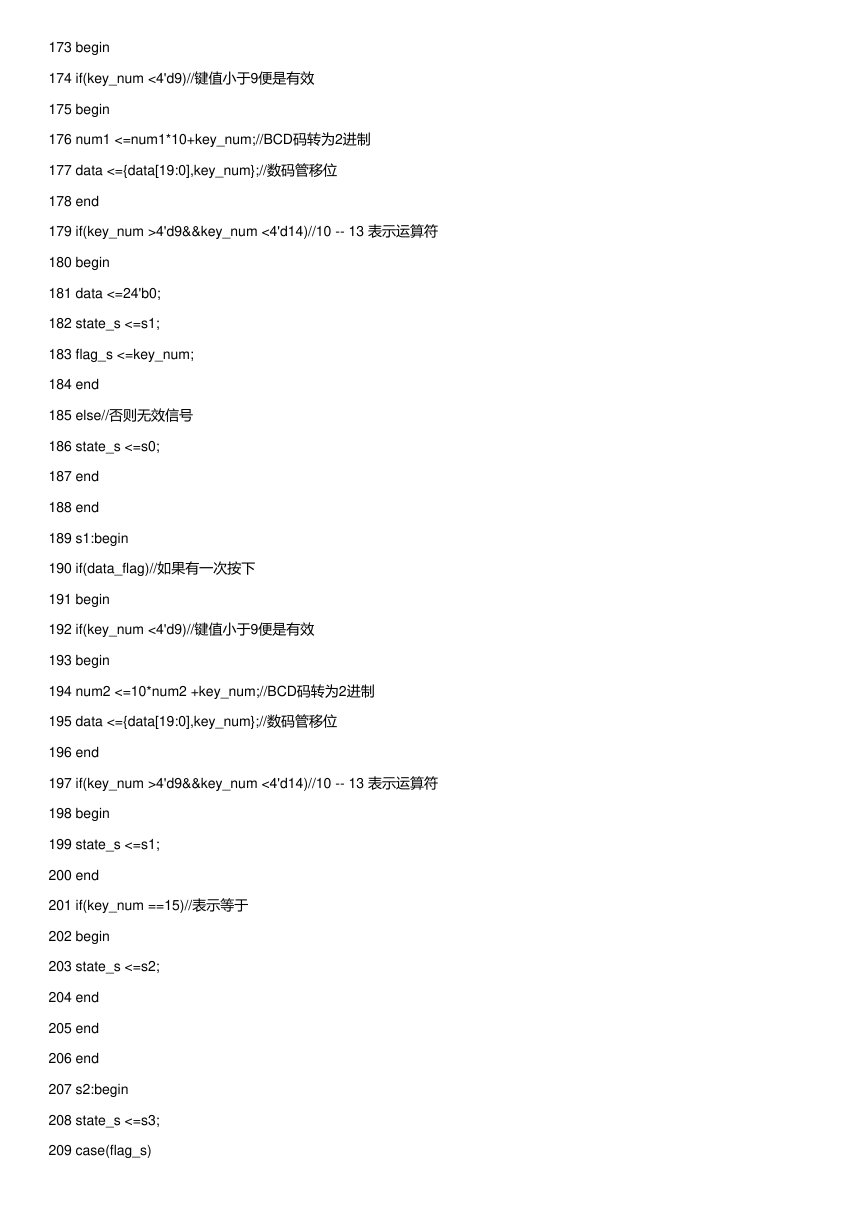

207 s2:begin

208 state_s <=s3;

209 case(flag_s)

�

210

211 4'd10:begin//加运算

212 data_in <=num1 +num2;

213 state_s <=s3;

214 end

215

216 4'd13:begin//乘运算

217 data_in <=num1 *num2;

218 state_s <=s3;

219 end

220 endcase

221 end

222 s3:begin//二进制转为BCD码显示到对应的数码管上

223 data[3:0]=data_in %10;

224 data[7:4]=data_in /10%10;

225 data[11:8]=data_in /100%10;

226 data[15:12]=data_in /1000%10;

227 data[19:16]=data_in /10000%10;

228 data[23:20]=data_in /100000;

229 state_s <=s0;

230 data_in <=24'b0;

231 end

232 default:state_s <=s0;

233 endcase

234 end

235 end

236

237

258endmodule

测试模块

0`timescale1ns/1ps

1

2modulecalc_tb();

3 regclk;

4 regrst_n;

5 reg[4:0]pressnum;

6 wire[3:0]row;

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc