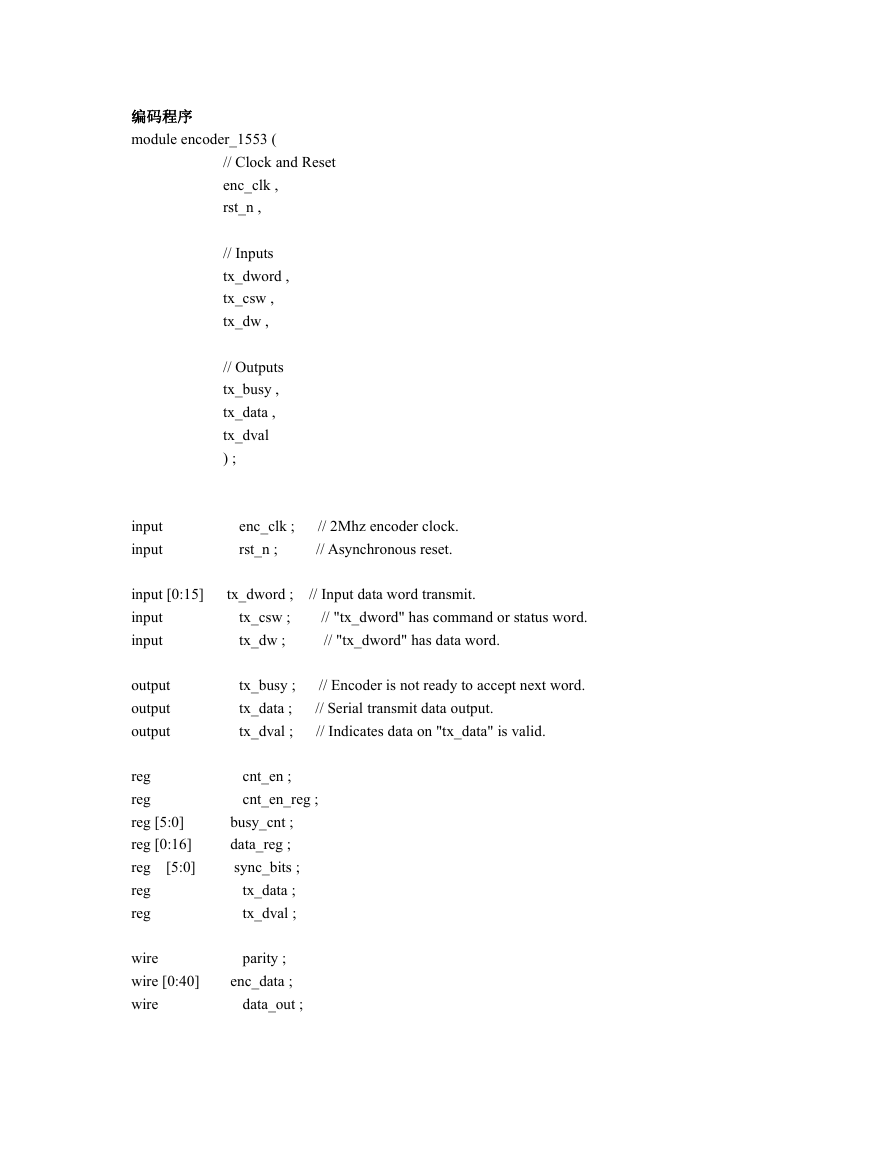

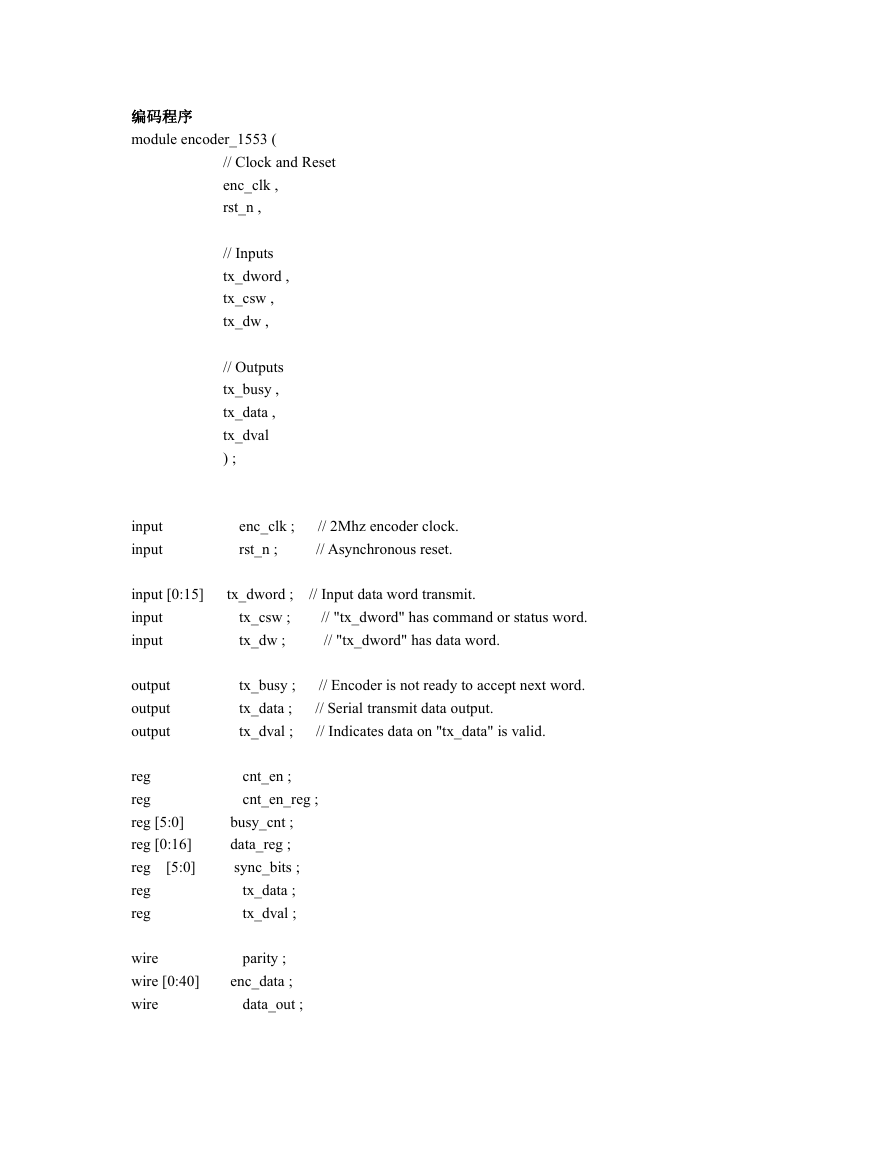

编码程序

module encoder_1553 (

// Clock and Reset

enc_clk ,

rst_n ,

// Inputs

tx_dword ,

tx_csw ,

tx_dw ,

// Outputs

tx_busy ,

tx_data ,

tx_dval

) ;

input

input

enc_clk ;

rst_n ;

// 2Mhz encoder clock.

// Asynchronous reset.

input [0:15]

input

input

tx_dword ;

tx_csw ;

tx_dw ;

// Input data word transmit.

// "tx_dword" has command or status word.

// "tx_dword" has data word.

output

output

output

reg

reg

reg [5:0]

reg [0:16]

reg

[5:0]

reg

reg

tx_busy ;

tx_data ;

tx_dval ;

// Encoder is not ready to accept next word.

// Serial transmit data output.

// Indicates data on "tx_data" is valid.

cnt_en ;

cnt_en_reg ;

busy_cnt ;

data_reg ;

sync_bits ;

tx_data ;

tx_dval ;

wire

wire [0:40]

wire

parity ;

enc_data ;

data_out ;

�

// Count number of clocks required to encode and serialize

// the input data.

always @(posedge enc_clk or negedge rst_n) begin

if (!rst_n)

cnt_en <= 1'b0 ;

else if (tx_csw || tx_dw )

cnt_en <= 1'b1 ;

else if (busy_cnt == 'd38)

cnt_en <= 1'b0 ;

else

cnt_en <= cnt_en ;

end

always @(posedge enc_clk or negedge rst_n) begin

if (!rst_n)

cnt_en_reg <= 1'b0 ;

else

cnt_en_reg <= cnt_en ;

end

always @(posedge enc_clk or negedge rst_n) begin

if (!rst_n)

busy_cnt <= 'd0 ;

else if (cnt_en)

busy_cnt <= busy_cnt + 1 ;

else

busy_cnt <= 'd0 ;

end

// Generate busy signal for the user interface.

assign tx_busy = cnt_en ;

// Generate parity for the given 16 bit word data.

assign parity = ^(tx_dword) ;

// Register input data word along with generated parity.

always @(posedge enc_clk or negedge rst_n) begin

if (!rst_n)

data_reg <= 17'h0000 ;

else if ((tx_csw || tx_dw) && !cnt_en)

data_reg <= {tx_dword, parity} ;

�

else if (!cnt_en )

data_reg <= 17'h0000 ;

else

data_reg <= data_reg ;

end

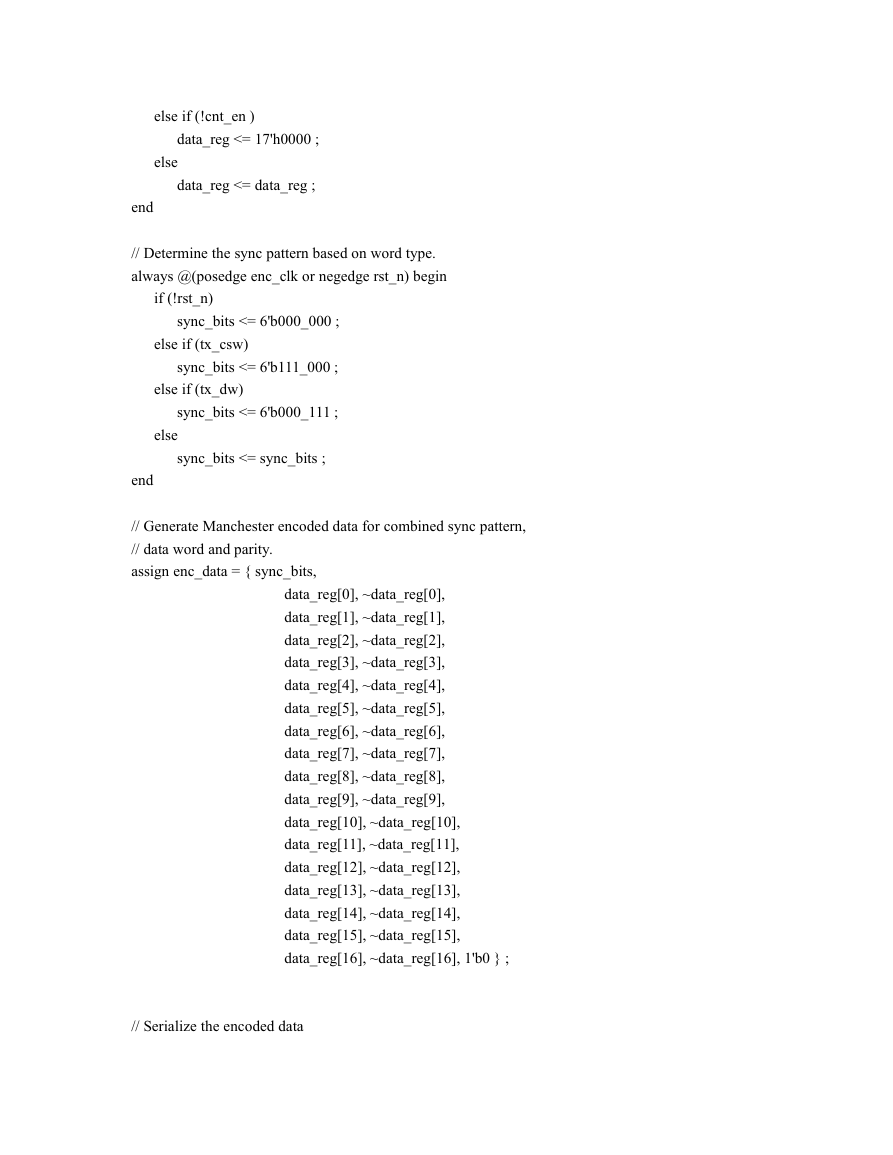

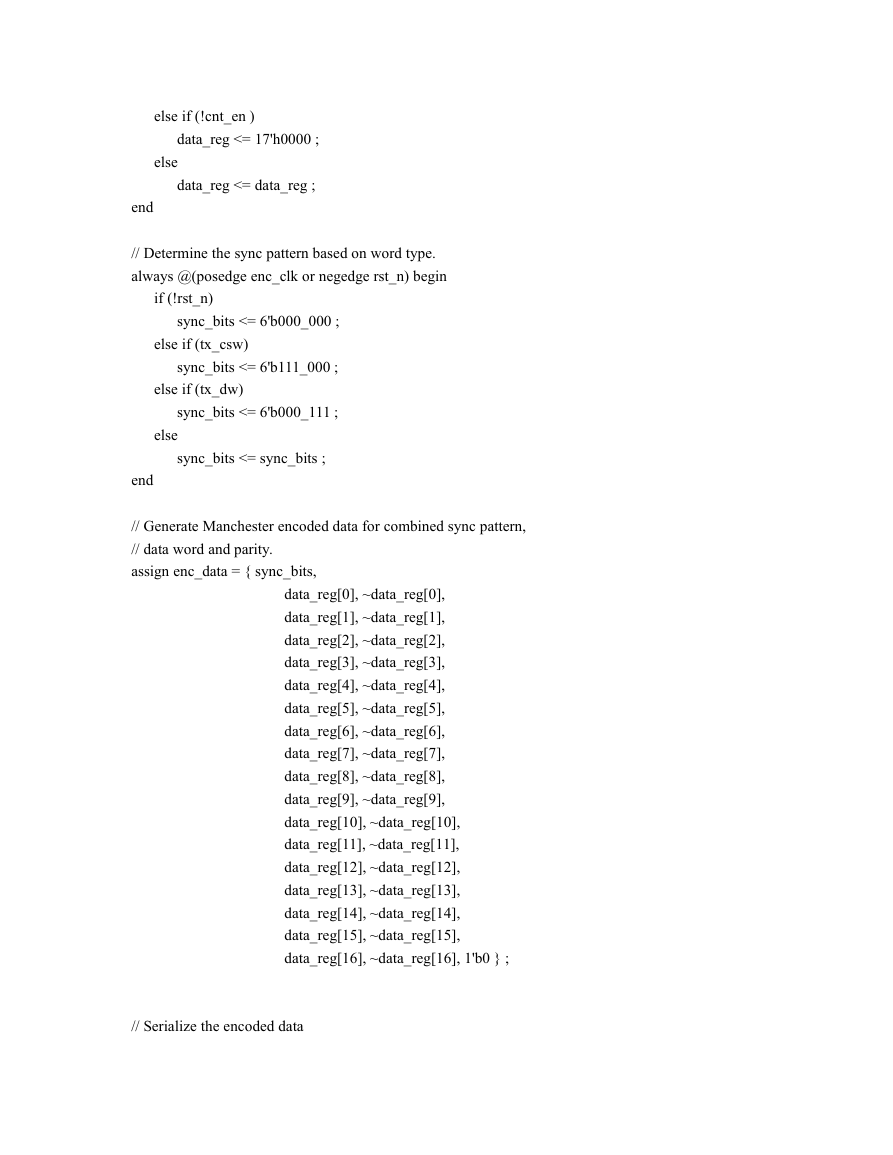

// Determine the sync pattern based on word type.

always @(posedge enc_clk or negedge rst_n) begin

if (!rst_n)

sync_bits <= 6'b000_000 ;

else if (tx_csw)

sync_bits <= 6'b111_000 ;

else if (tx_dw)

sync_bits <= 6'b000_111 ;

else

sync_bits <= sync_bits ;

end

// Generate Manchester encoded data for combined sync pattern,

// data word and parity.

assign enc_data = { sync_bits,

data_reg[0], ~data_reg[0],

data_reg[1], ~data_reg[1],

data_reg[2], ~data_reg[2],

data_reg[3], ~data_reg[3],

data_reg[4], ~data_reg[4],

data_reg[5], ~data_reg[5],

data_reg[6], ~data_reg[6],

data_reg[7], ~data_reg[7],

data_reg[8], ~data_reg[8],

data_reg[9], ~data_reg[9],

data_reg[10], ~data_reg[10],

data_reg[11], ~data_reg[11],

data_reg[12], ~data_reg[12],

data_reg[13], ~data_reg[13],

data_reg[14], ~data_reg[14],

data_reg[15], ~data_reg[15],

data_reg[16], ~data_reg[16], 1'b0 } ;

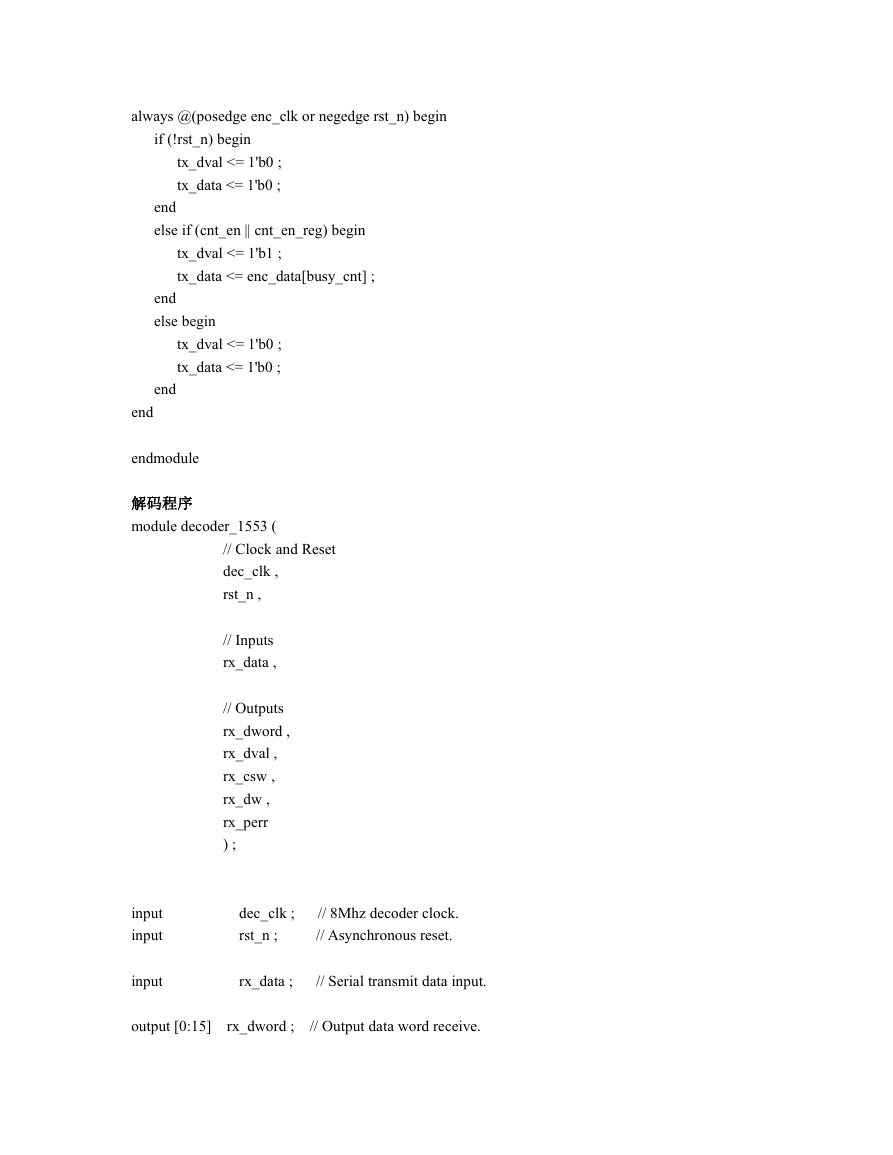

// Serialize the encoded data

�

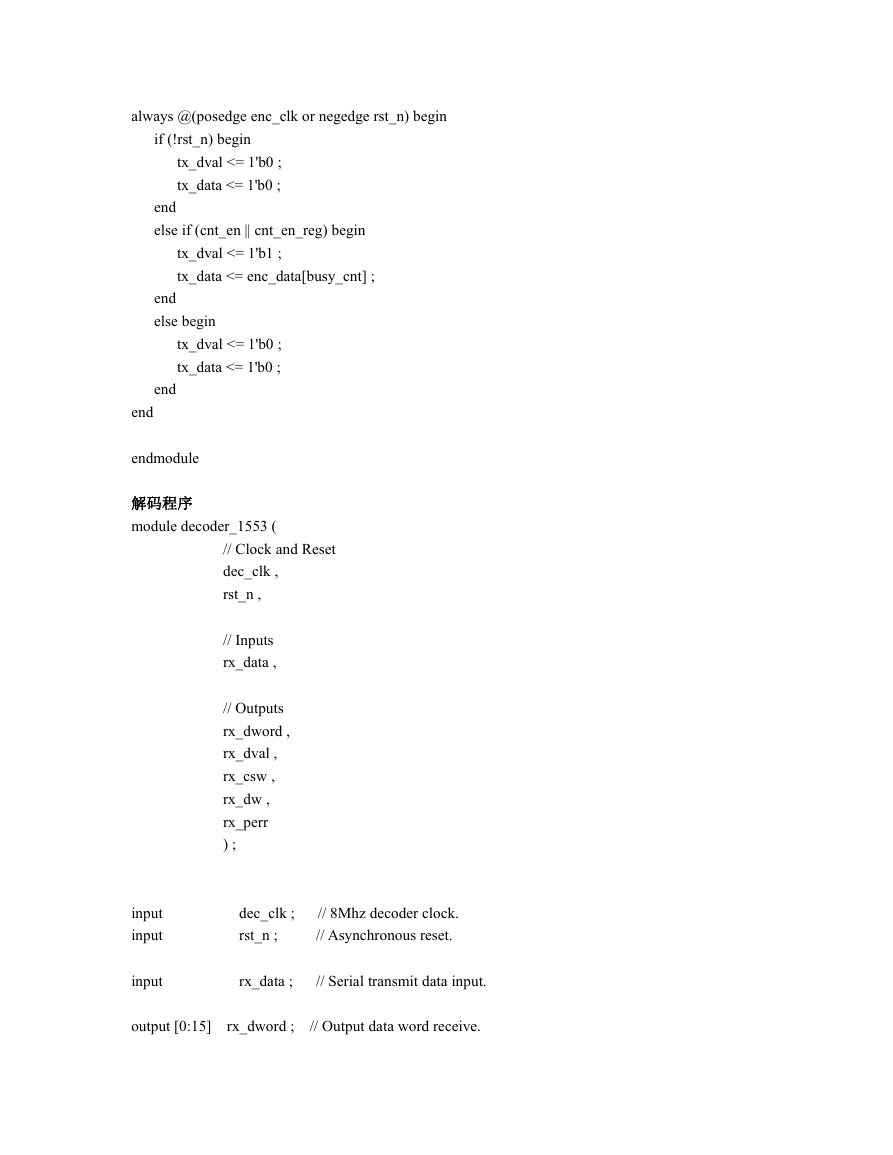

always @(posedge enc_clk or negedge rst_n) begin

if (!rst_n) begin

tx_dval <= 1'b0 ;

tx_data <= 1'b0 ;

end

else if (cnt_en || cnt_en_reg) begin

tx_dval <= 1'b1 ;

tx_data <= enc_data[busy_cnt] ;

end

else begin

tx_dval <= 1'b0 ;

tx_data <= 1'b0 ;

end

end

endmodule

解码程序

module decoder_1553 (

// Clock and Reset

dec_clk ,

rst_n ,

// Inputs

rx_data ,

// Outputs

rx_dword ,

rx_dval ,

rx_csw ,

rx_dw ,

rx_perr

) ;

input

input

input

dec_clk ;

rst_n ;

// 8Mhz decoder clock.

// Asynchronous reset.

rx_data ;

// Serial transmit data input.

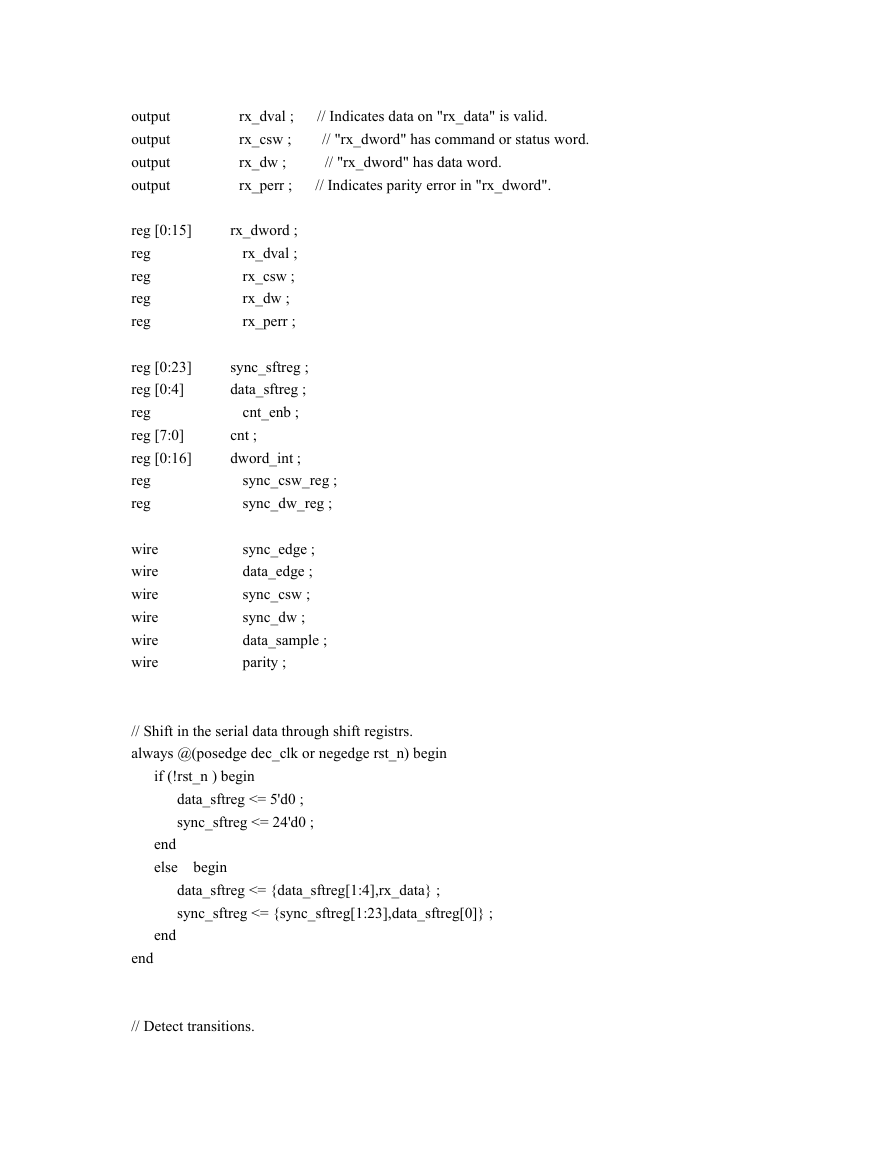

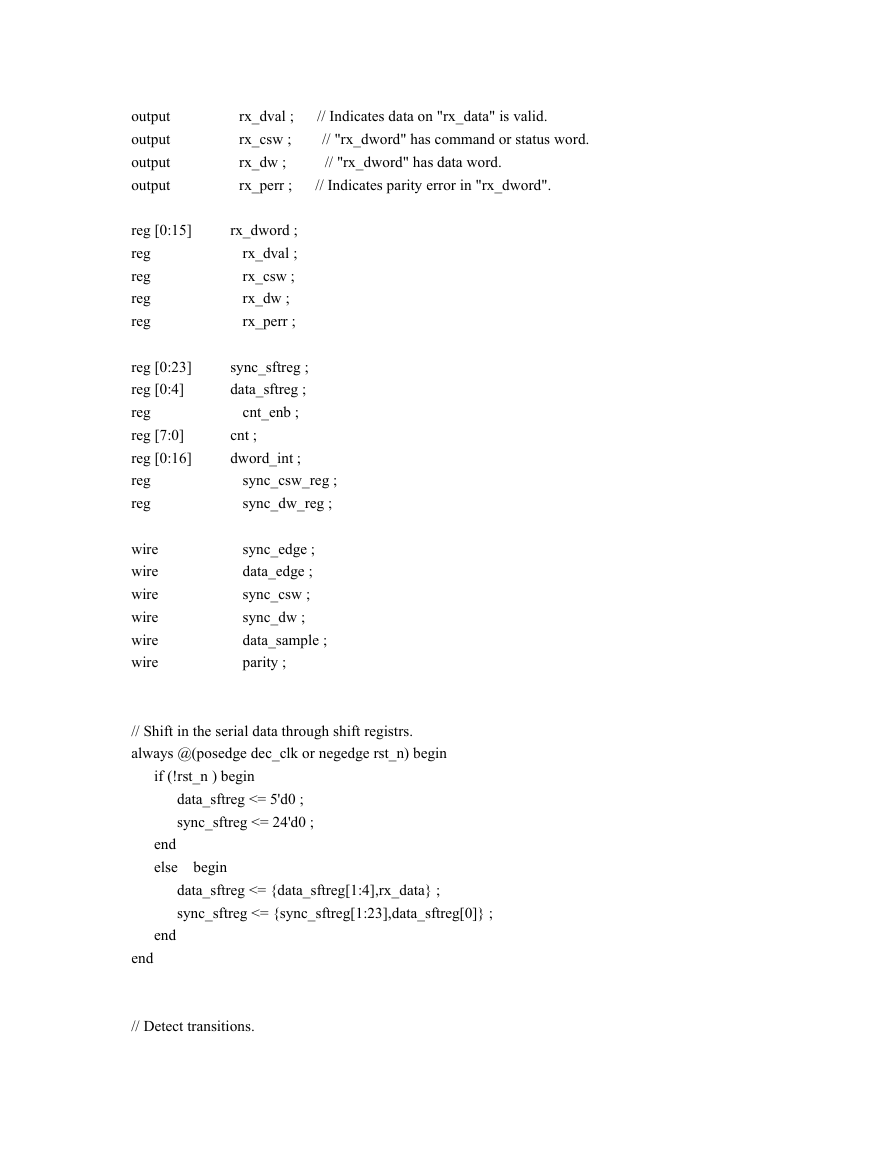

output [0:15]

rx_dword ;

// Output data word receive.

�

output

output

output

output

reg [0:15]

reg

reg

reg

reg

reg [0:23]

reg [0:4]

reg

reg [7:0]

reg [0:16]

reg

reg

wire

wire

wire

wire

wire

wire

rx_dval ;

rx_csw ;

rx_dw ;

rx_perr ;

// Indicates data on "rx_data" is valid.

// "rx_dword" has command or status word.

// "rx_dword" has data word.

// Indicates parity error in "rx_dword".

rx_dword ;

rx_dval ;

rx_csw ;

rx_dw ;

rx_perr ;

sync_sftreg ;

data_sftreg ;

cnt_enb ;

cnt ;

dword_int ;

sync_csw_reg ;

sync_dw_reg ;

sync_edge ;

data_edge ;

sync_csw ;

sync_dw ;

data_sample ;

parity ;

// Shift in the serial data through shift registrs.

always @(posedge dec_clk or negedge rst_n) begin

if (!rst_n ) begin

data_sftreg <= 5'd0 ;

sync_sftreg <= 24'd0 ;

end

else

begin

data_sftreg <= {data_sftreg[1:4],rx_data} ;

sync_sftreg <= {sync_sftreg[1:23],data_sftreg[0]} ;

end

end

// Detect transitions.

�

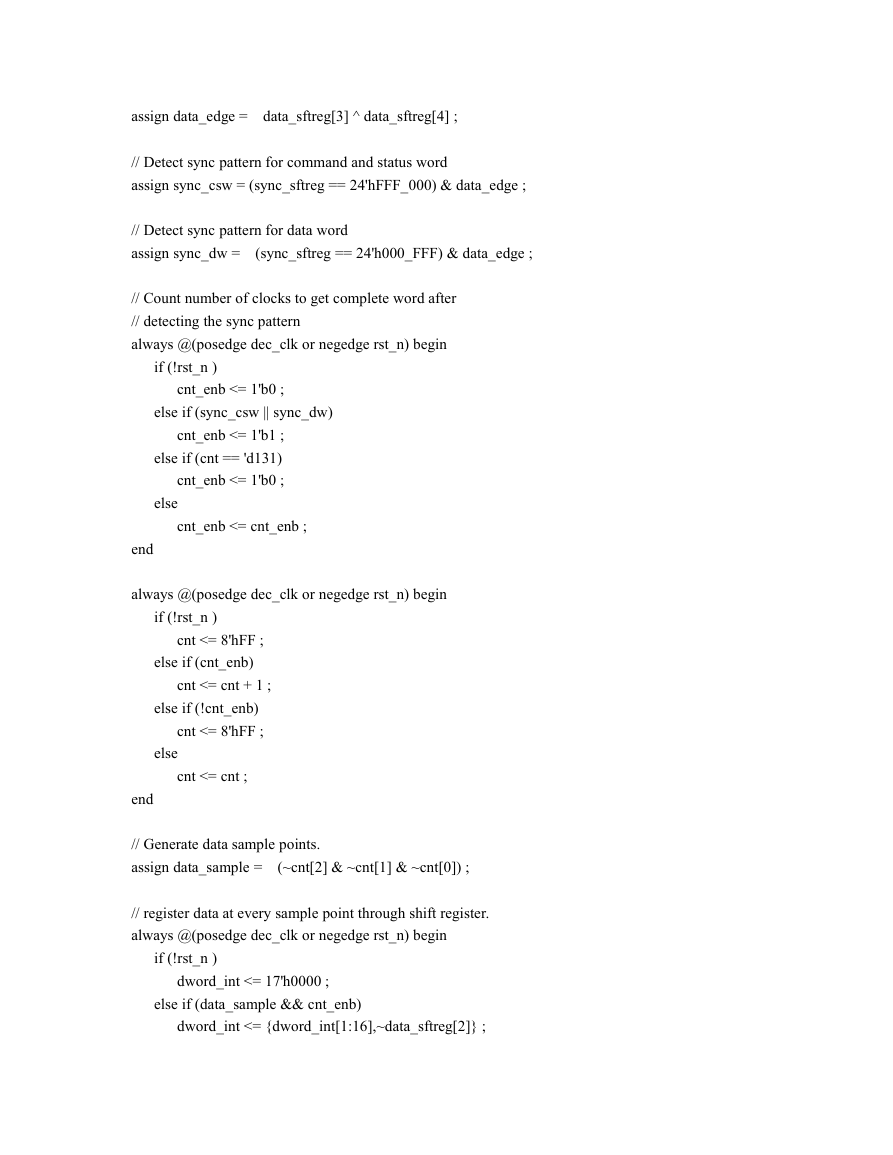

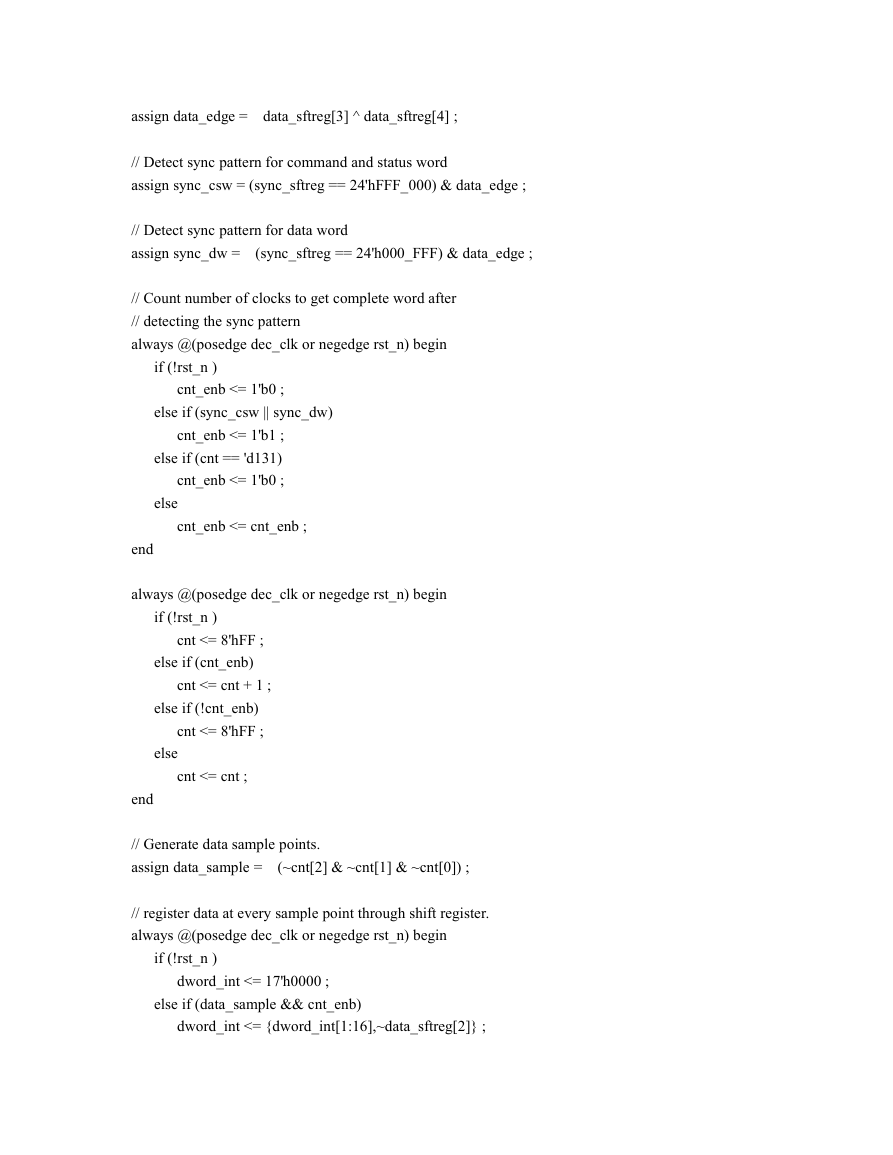

assign data_edge = data_sftreg[3] ^ data_sftreg[4] ;

// Detect sync pattern for command and status word

assign sync_csw = (sync_sftreg == 24'hFFF_000) & data_edge ;

// Detect sync pattern for data word

assign sync_dw = (sync_sftreg == 24'h000_FFF) & data_edge ;

// Count number of clocks to get complete word after

// detecting the sync pattern

always @(posedge dec_clk or negedge rst_n) begin

if (!rst_n )

cnt_enb <= 1'b0 ;

else if (sync_csw || sync_dw)

cnt_enb <= 1'b1 ;

else if (cnt == 'd131)

cnt_enb <= 1'b0 ;

else

cnt_enb <= cnt_enb ;

end

always @(posedge dec_clk or negedge rst_n) begin

if (!rst_n )

cnt <= 8'hFF ;

else if (cnt_enb)

cnt <= cnt + 1 ;

else if (!cnt_enb)

cnt <= 8'hFF ;

else

cnt <= cnt ;

end

// Generate data sample points.

assign data_sample = (~cnt[2] & ~cnt[1] & ~cnt[0]) ;

// register data at every sample point through shift register.

always @(posedge dec_clk or negedge rst_n) begin

if (!rst_n )

dword_int <= 17'h0000 ;

else if (data_sample && cnt_enb)

dword_int <= {dword_int[1:16],~data_sftreg[2]} ;

�

else if (!cnt_enb)

dword_int <= 17'h0000 ;

else

dword_int <= dword_int ;

end

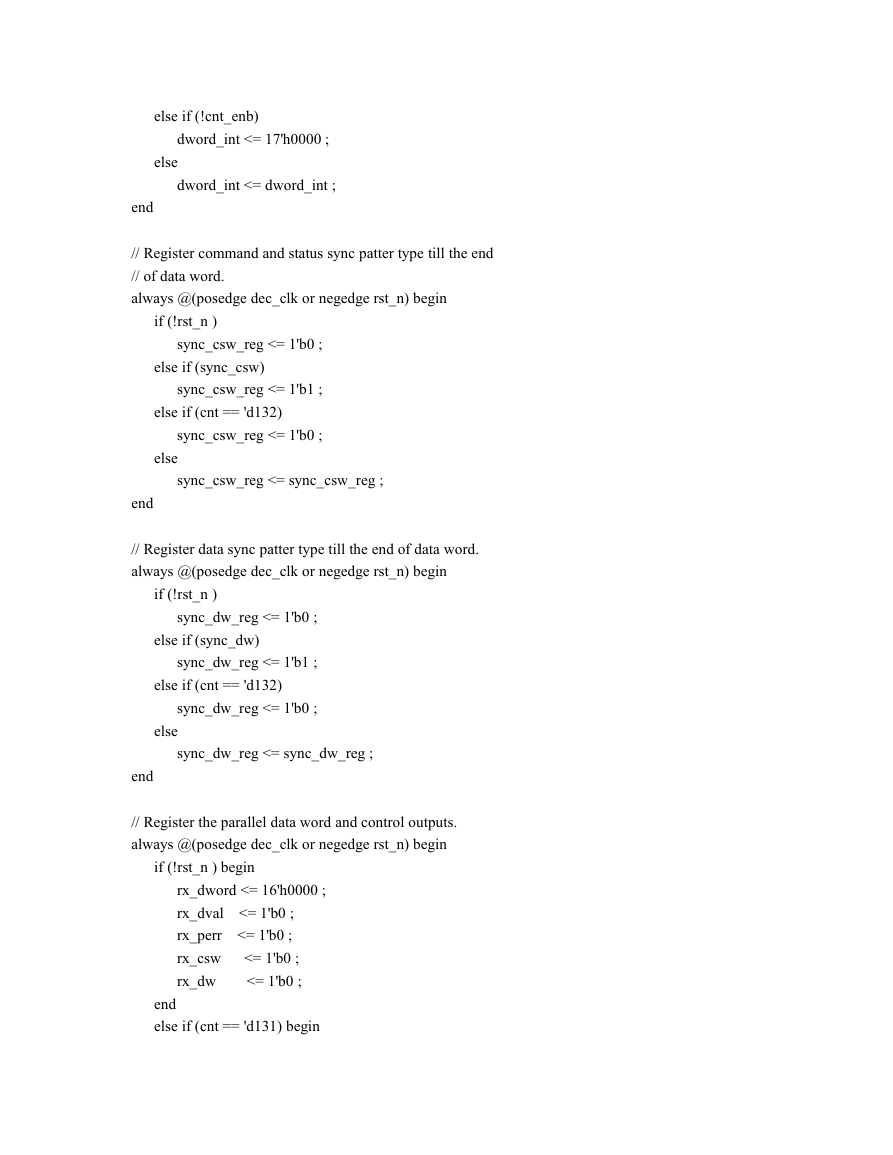

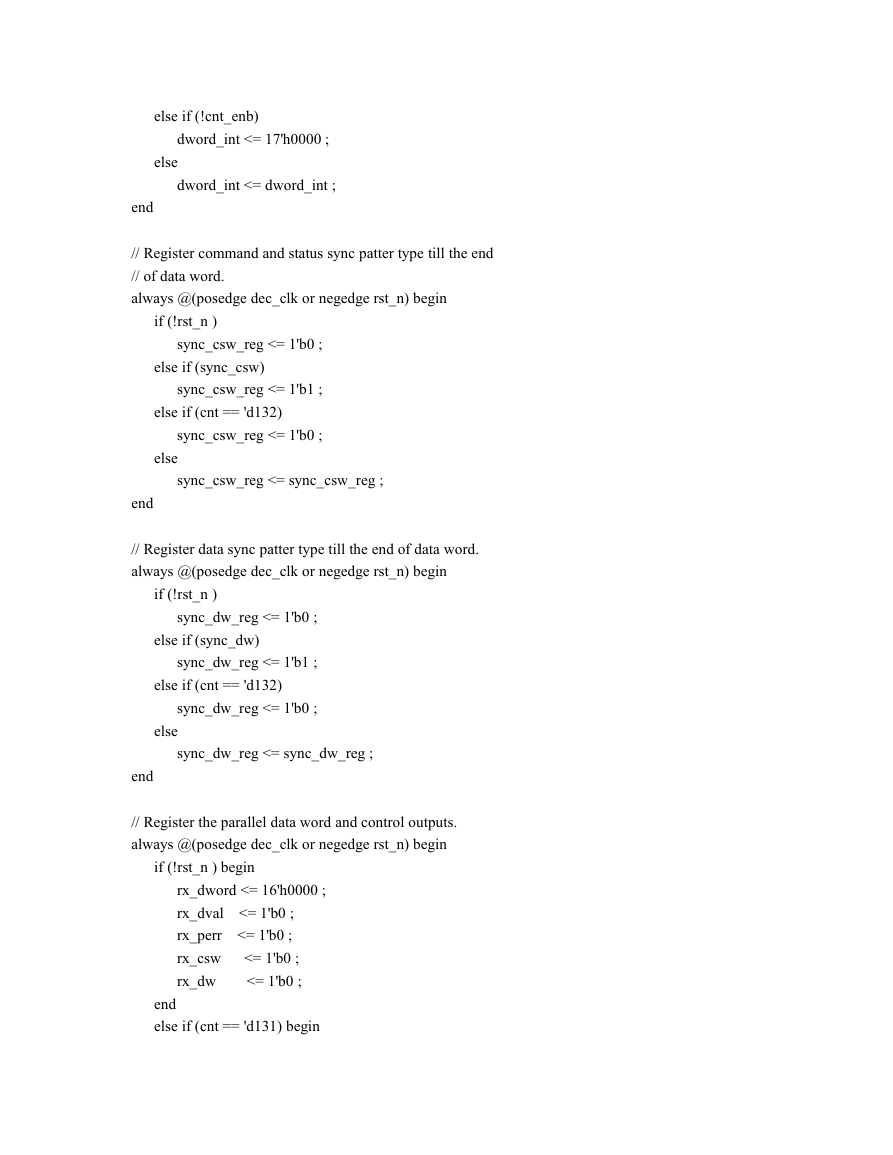

// Register command and status sync patter type till the end

// of data word.

always @(posedge dec_clk or negedge rst_n) begin

if (!rst_n )

sync_csw_reg <= 1'b0 ;

else if (sync_csw)

sync_csw_reg <= 1'b1 ;

else if (cnt == 'd132)

sync_csw_reg <= 1'b0 ;

else

sync_csw_reg <= sync_csw_reg ;

end

// Register data sync patter type till the end of data word.

always @(posedge dec_clk or negedge rst_n) begin

if (!rst_n )

sync_dw_reg <= 1'b0 ;

else if (sync_dw)

sync_dw_reg <= 1'b1 ;

else if (cnt == 'd132)

sync_dw_reg <= 1'b0 ;

else

sync_dw_reg <= sync_dw_reg ;

end

// Register the parallel data word and control outputs.

always @(posedge dec_clk or negedge rst_n) begin

if (!rst_n ) begin

rx_dword <= 16'h0000 ;

rx_dval <= 1'b0 ;

rx_perr <= 1'b0 ;

<= 1'b0 ;

rx_csw

rx_dw

<= 1'b0 ;

end

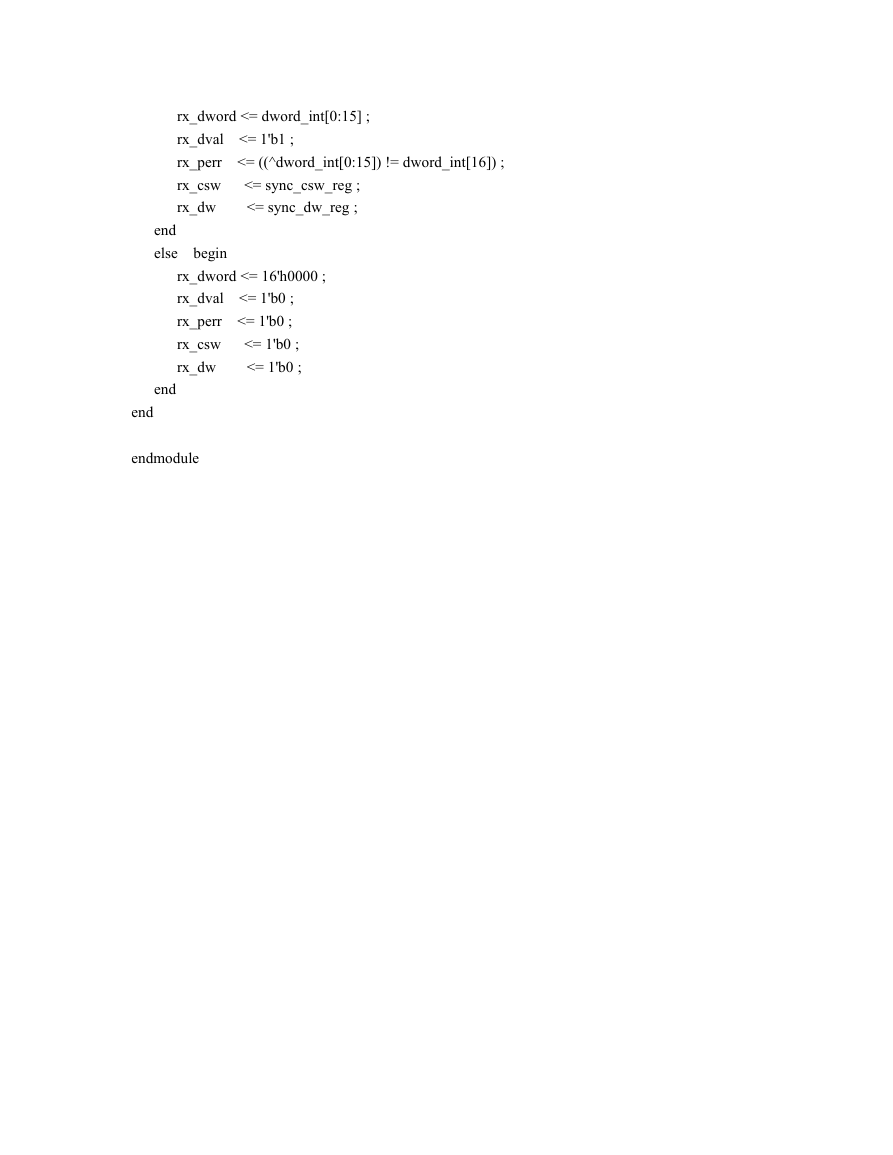

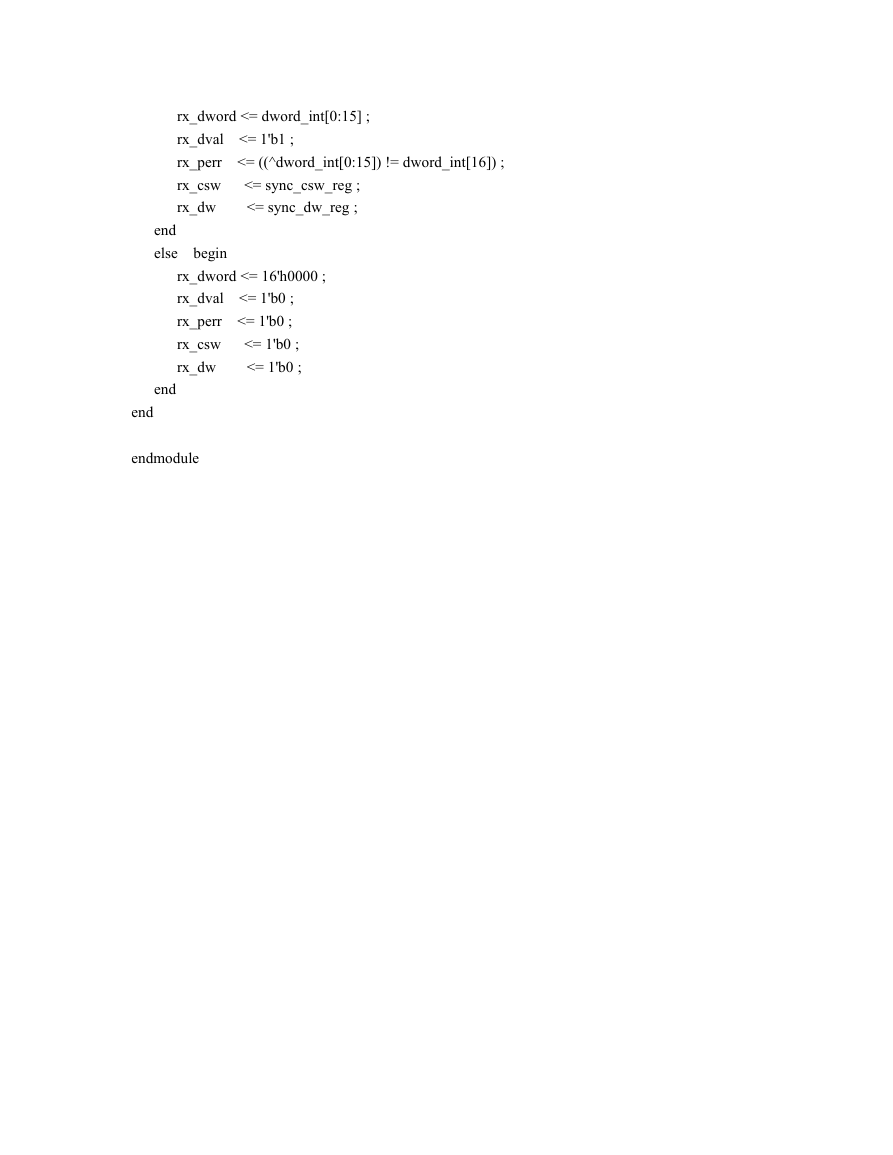

else if (cnt == 'd131) begin

�

rx_dword <= dword_int[0:15] ;

rx_dval <= 1'b1 ;

rx_perr <= ((^dword_int[0:15]) != dword_int[16]) ;

rx_csw

rx_dw

<= sync_csw_reg ;

<= sync_dw_reg ;

end

else

begin

rx_dword <= 16'h0000 ;

rx_dval <= 1'b0 ;

rx_perr <= 1'b0 ;

<= 1'b0 ;

rx_csw

rx_dw

<= 1'b0 ;

end

end

endmodule

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc