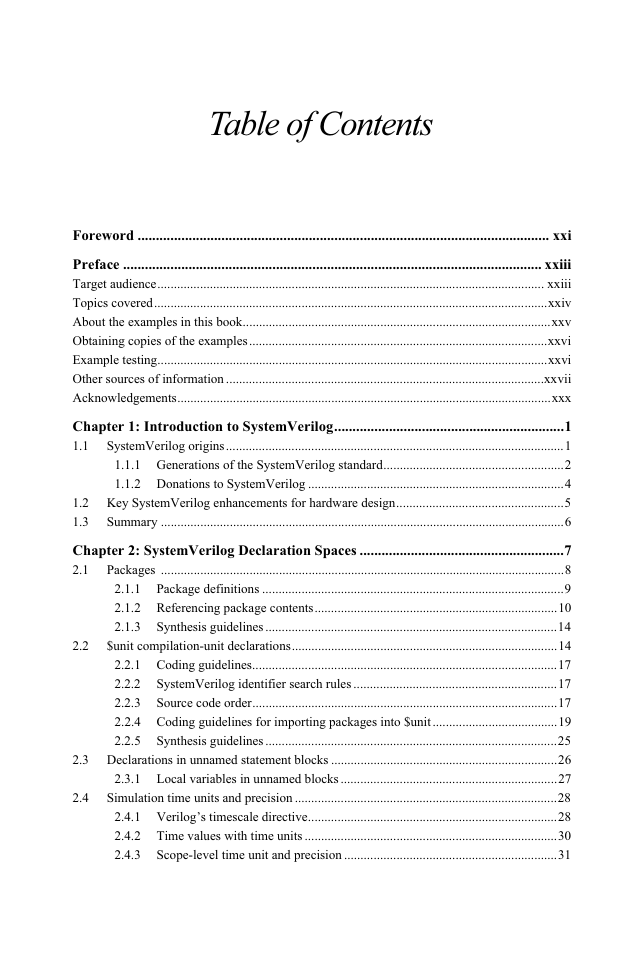

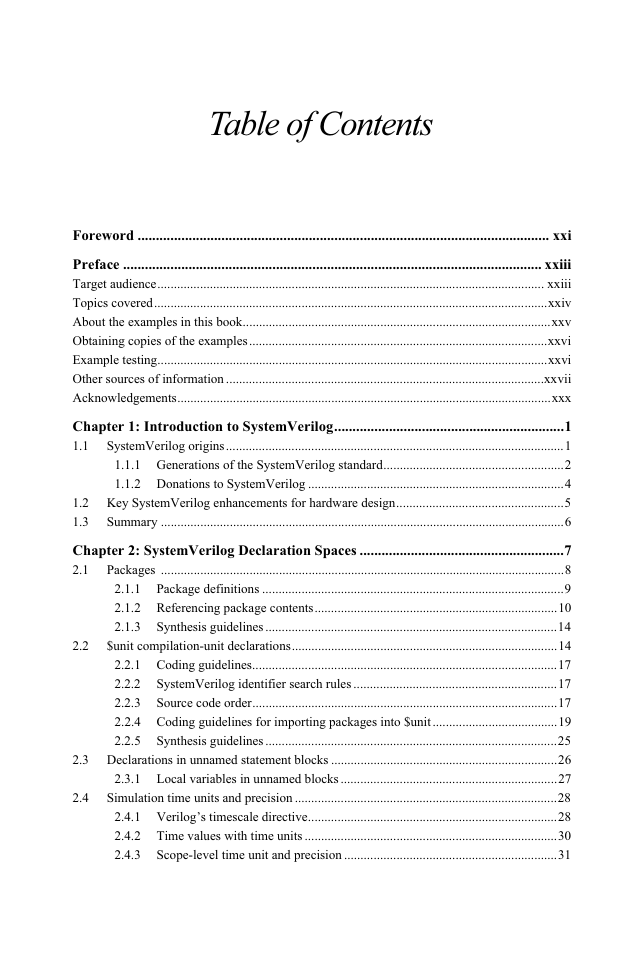

Contents

chapter 1 introduction to systemverilog

1.1 SystemVerilog origins

1.2 Key enhancements for hardware design

1.3 summary

chapter 2 declaration spaces

2.1 package

2.2 $unit compilation

2.3 declarations in unnamed statement blocks

2.4 sumulation time units and precision

2.5 summary

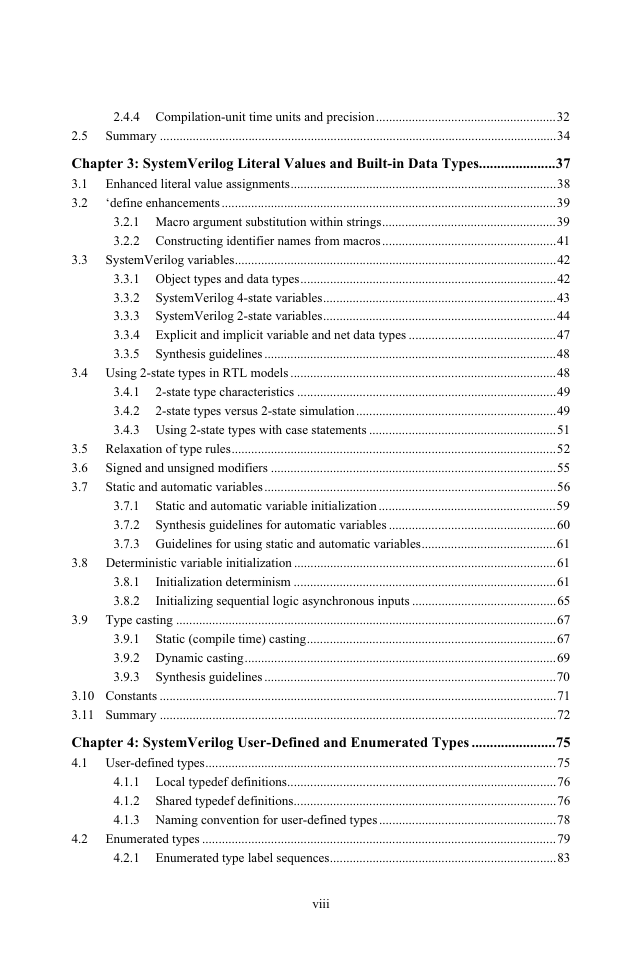

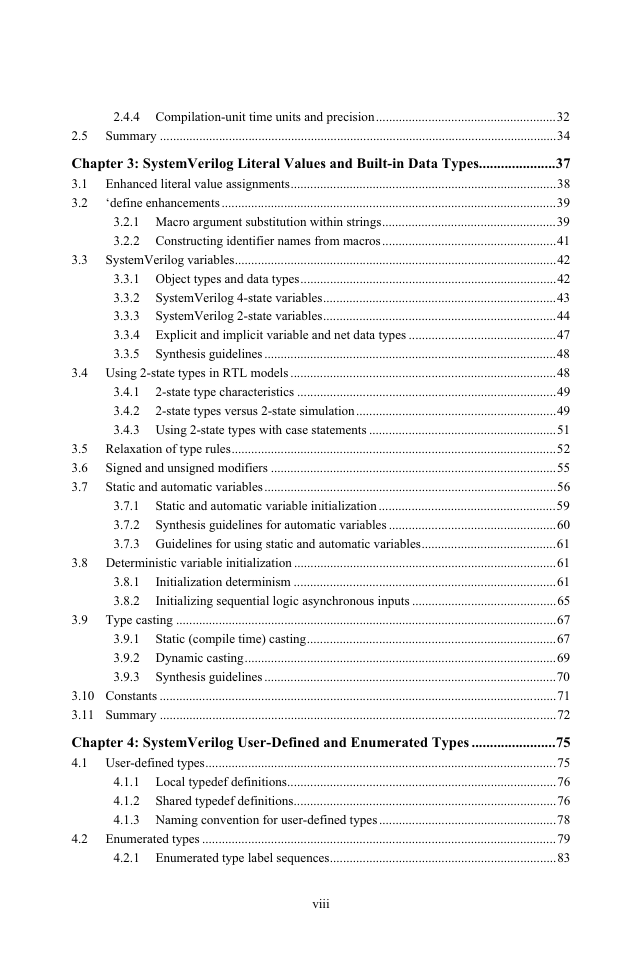

chapter 3 liteeral values and built-in data types

3.1 enhanced literal value assignments

3.2 `define enhancements

3.3 systemverilog variables

3.4 using 2-state types in RTL models

3.5 relaxation of type rules

3.6 signed and unsigned modifiers

3.7 static and automatic variables

3.8 deterministic variable initialization

3.9 type casting

3.10 Constants

3.11 summary

chapter 4 user defined and enumerated types

4.1 user defined types

4.2 enumerated types

4.3 summary

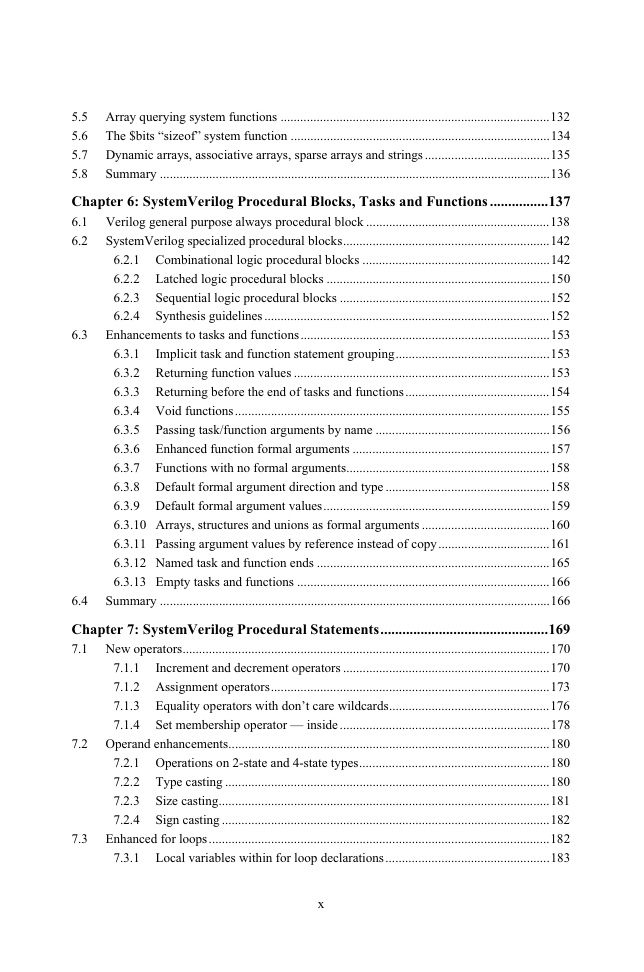

chapter 5 arrays, structres and unions

5.1 structures

5.2 unions

5.3 arrays

5.4 the foreach array looping construct

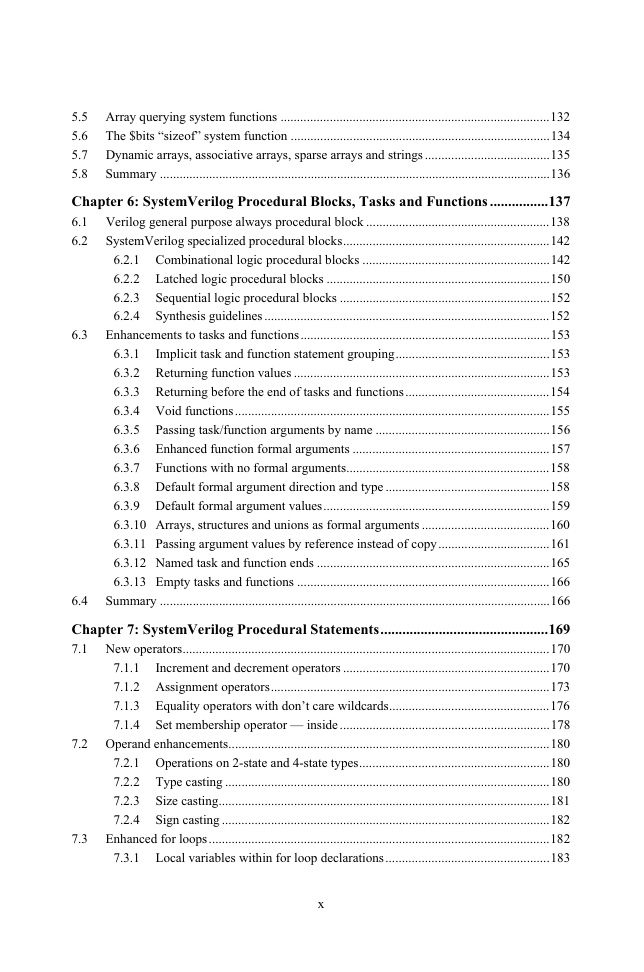

5.5 array querying system functions

5.6 the $bits "sizeof" system function

5.7 synamic arrays, associative arrays, sparse arrays and strings

5.8 summary

chapter 6 procedural blocks, tasks and functions

6.1 verilog general purpose always procedural block

6.2 specialized procedural blocks

6.3 enhancements to tasks and functions

6.4 summary

Ch7 Procedural Statements

7.1 new operators

7.2 operand enhancements

7.3 enhanced for loops

7.4 bottom testing do...while loop

7.5 the foreach array looping construct

7.6 new jump statements - break, continue, return

7.7 enhanced block names

7.8 statement labels

7.9 enhanced case statements

7.10 enhanced if...else decisions

7.11 summary

chapter 8 modeling finit state machines with systemverilog

8.1 modeling state machines with enumerated types

8.2 using 2-state types in FSM models

8.3 summary

chapter 9 design hierarchy

9.1 module prototypes

9.2 named ending statements

9.3 nested(local) module declarations

9.4 simplified netlists of module instances

9.5 net aliasing

9.6 passing values through module ports

9.7 reference ports

9.8 enhanced port declarations

9.9 parameterized types

9.10 summary

chapter 10 interfaces

10.1 interface concepts

10.2 interface declarations

10.3 using interfaces as module ports

10.4 instantiating and connecting interfaces

10.5 referencing signals within an interface

10.6 interface modports

10.7 using tasks and functions in interfaces

10.8 using procedural blocks in interfaces

10.9 reconfigurable interfaces

10.10 verification with interfaces

10.11 summary

chapter 11 a complete design modeled with systemverilog

11.1 ATM example

11.2 data abstraction

11.3 interface encapsulation

11.4 design top level: squat

11.5 receivers and transmitters

11.6 testbench

11.7 summary

chapter 12 behavioral and transaction level modeling

12.1 behavioral modeling

12.2 what is a transaction

12.3 transaction level modeling in systemverilog

12.4 transaction level models via interfaces

12.5 bus arbitration

12.6 transactors, adapters, and bus functional models

12.7 more complex transactions

12.8 summary

appendix a the systemverilog formal definition

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc