三 电子密码锁设计的设计与实现

摘要

本文介绍了一种基于 AT89S52 单片机的电子密码锁的设计方法。该设计以

AT89S52 单片机为硬件核心,结合 4×4 矩阵键盘电路、 LCD 显示电路、密码

存储电路、开锁电路和声音报警电路等外围电路。利用单片机灵活的编程方法和

丰富的 I/O 端口,该系统能实现密码的输入、清除、比较,密码正确开锁,密码

错误次数超次报警,用户修改密码等功能。

关键词: 单片机;电子密码锁;矩阵键盘;声音报警

�

1 电子密码锁的背景及意义

随着社会科技的进步,锁已发展到了密码锁、磁性锁、电子锁、激光锁、声

控锁等等。在传统钥匙的基础上,加了一组或多组密码,不同声音,不同磁场,

不同声波,不同光束光波,不同图像。(如指纹、眼底视网膜等)来控制锁的开

启。从而大大提高了锁的安全性,使不法之徒无从下手,人们也就能对自身财产

安全有了更多的保障。当今安全信息系统应用越来越广泛,特别在保护机密、维

护隐私和财产保护方面起到重大作用,而基于电子密码锁的安全系统是其中的组

成部分,因此研究它具有重大的现实意义。

电子锁可以在日常生活和现代办公中,住宅与办公室的安全防范、单位的文

件档案、财务报表以及一些个人资料的保存等多种场合使用。大大提高了主人物

资的安全性,安全可以代替老式机械锁。目前使用的密码锁种类繁多,各具特色。

本文从经济实用的角度出发,采用 AT89C2052 单片机,研制了一款具有防盗自动

报警功能的电子密码锁。该密码锁设计方法合理,简单易行,成本低,符合住宅、

办公室用锁要求,具有一定的推广价值。

(1)系统设置 4 位密码,密码通过键盘输入,若密码正确,则将锁打开。

(2)密码由用户自己设定,在开锁状态下,用户可自行修改密码。

(3)具有自动报警功能。自动报警分现场报警和远程报警两种。现场报警由

扬声器发出报警声。

(4)两种情况下可报警:一是密码输入错误 3 次,则报警;二是非正常开门,

如破门而入的情况,可通过系统的红外监视装置监测,同时报警,保证了系统的

安全性。系统工作时,用户通过按键输入 4 位密码,单片机将输入密码与设定密

码进行比较,若密码正确,则发出开锁信号,将门打开,系统不报警;若密码不

正确,则有相应的指示灯闪动,并要求重新输入密码,重新输入密码的次数不能

超过 3 次,若 3 次输入的密码都不正确,则发出报警信号。

2 设计原理与设计方案

2.1 设计原理

系统的设计包括硬件和软件两大部分。

系统的硬件设计部分主要由以下几个模块组成:

单片机最小系统:该部分主要是使单片机能稳定工作,来控制整个系统实现

密码锁的功能。

�

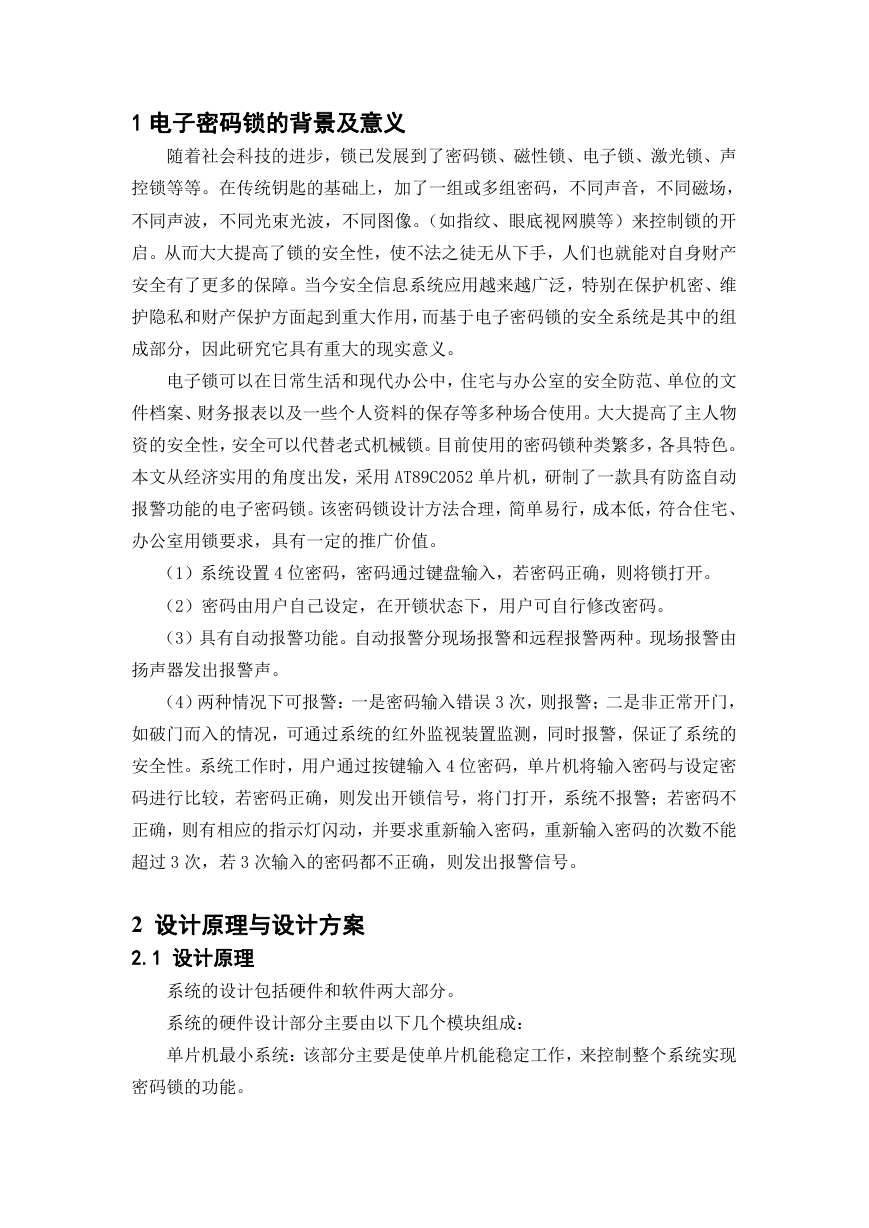

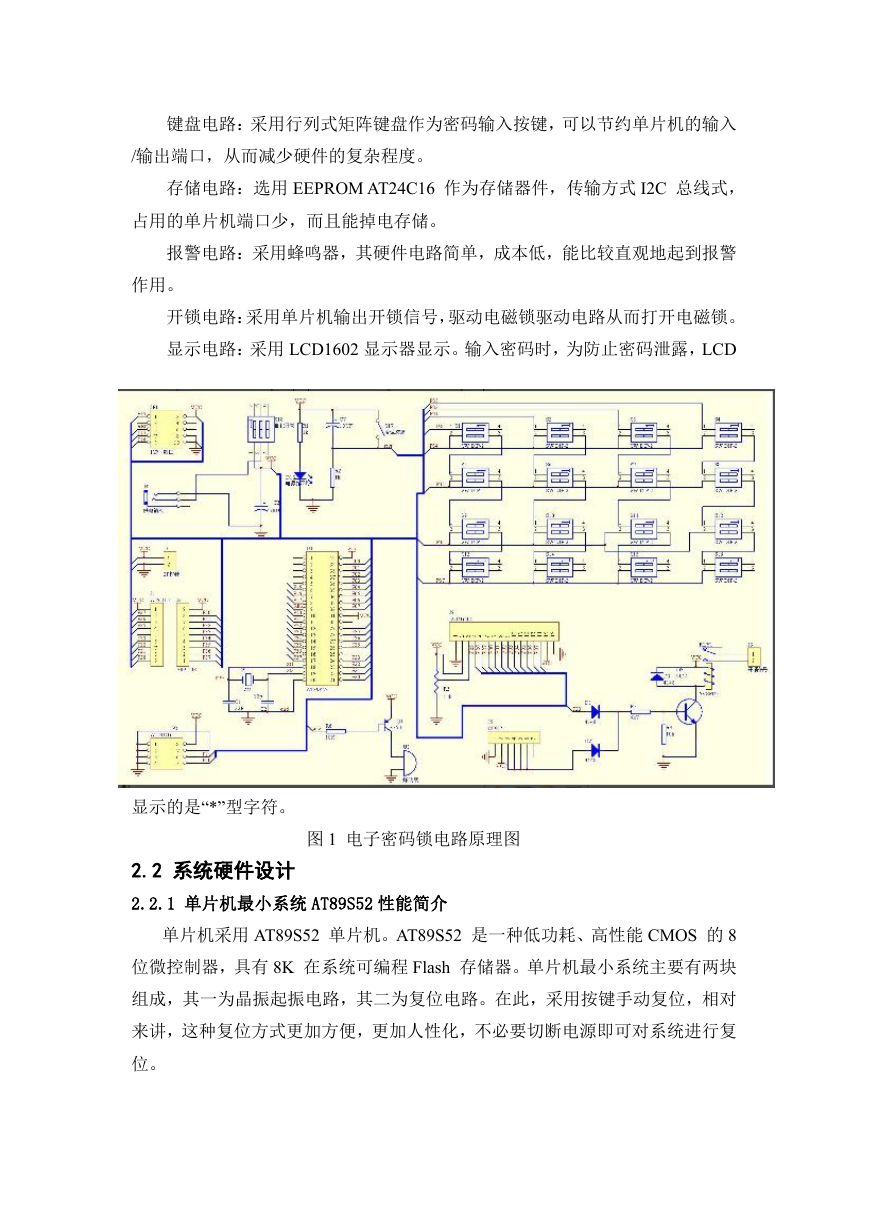

键盘电路:采用行列式矩阵键盘作为密码输入按键,可以节约单片机的输入

/输出端口,从而减少硬件的复杂程度。

存储电路:选用 EEPROM AT24C16 作为存储器件,传输方式 I2C 总线式,

占用的单片机端口少,而且能掉电存储。

报警电路:采用蜂鸣器,其硬件电路简单,成本低,能比较直观地起到报警

作用。

开锁电路:采用单片机输出开锁信号,驱动电磁锁驱动电路从而打开电磁锁。

显示电路:采用 LCD1602 显示器显示。输入密码时,为防止密码泄露,LCD

显示的是“*”型字符。

2.2 系统硬件设计

图 1 电子密码锁电路原理图

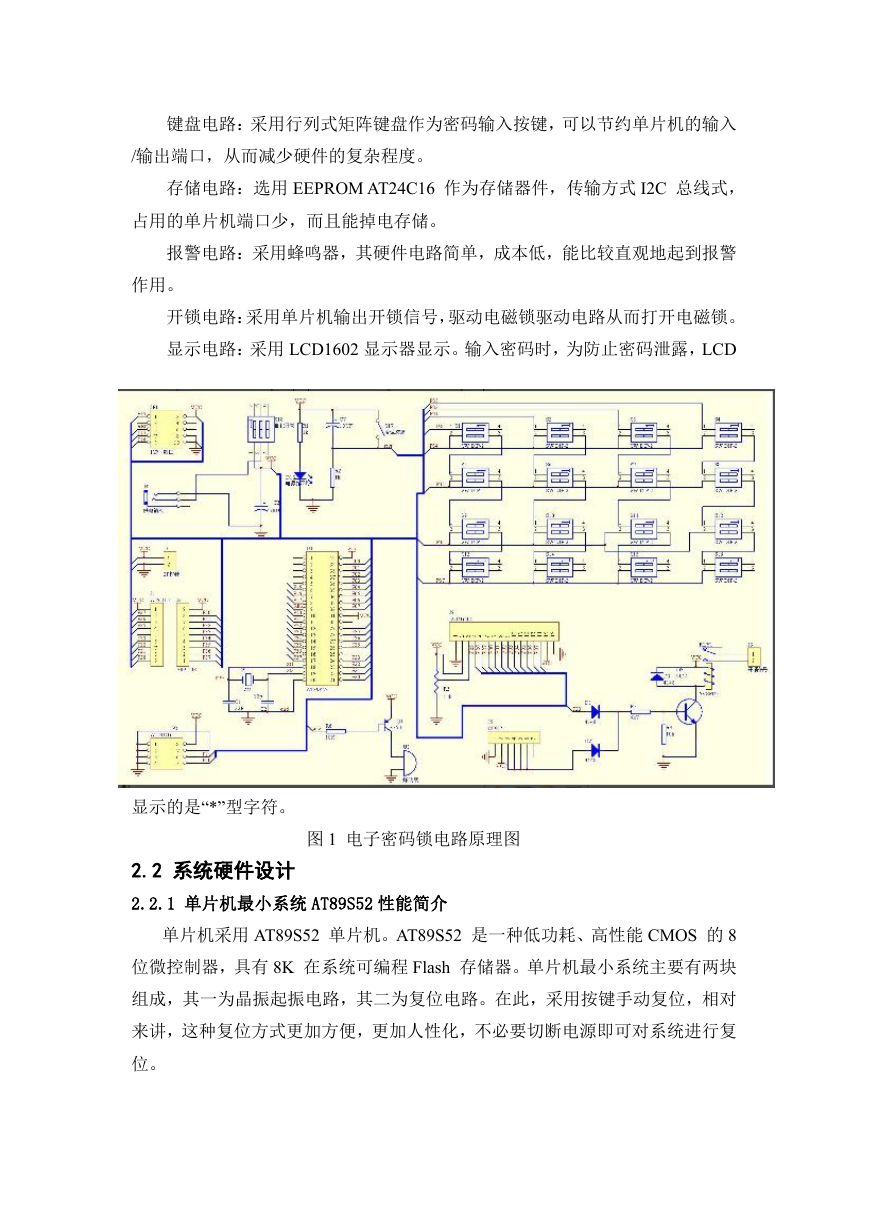

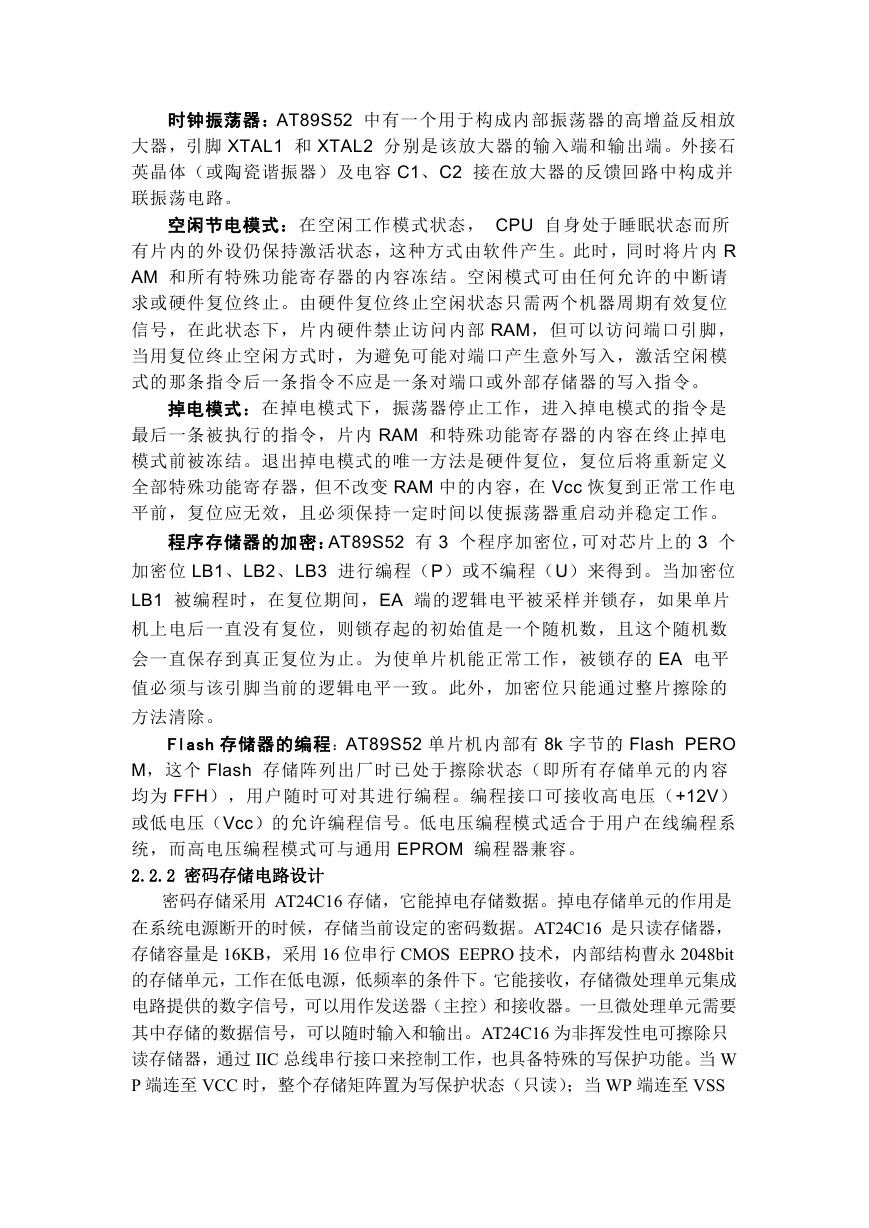

2.2.1 单片机最小系统 AT89S52 性能简介

单片机采用 AT89S52 单片机。AT89S52 是一种低功耗、高性能 CMOS 的 8

位微控制器,具有 8K 在系统可编程 Flash 存储器。单片机最小系统主要有两块

组成,其一为晶振起振电路,其二为复位电路。在此,采用按键手动复位,相对

来讲,这种复位方式更加方便,更加人性化,不必要切断电源即可对系统进行复

位。

�

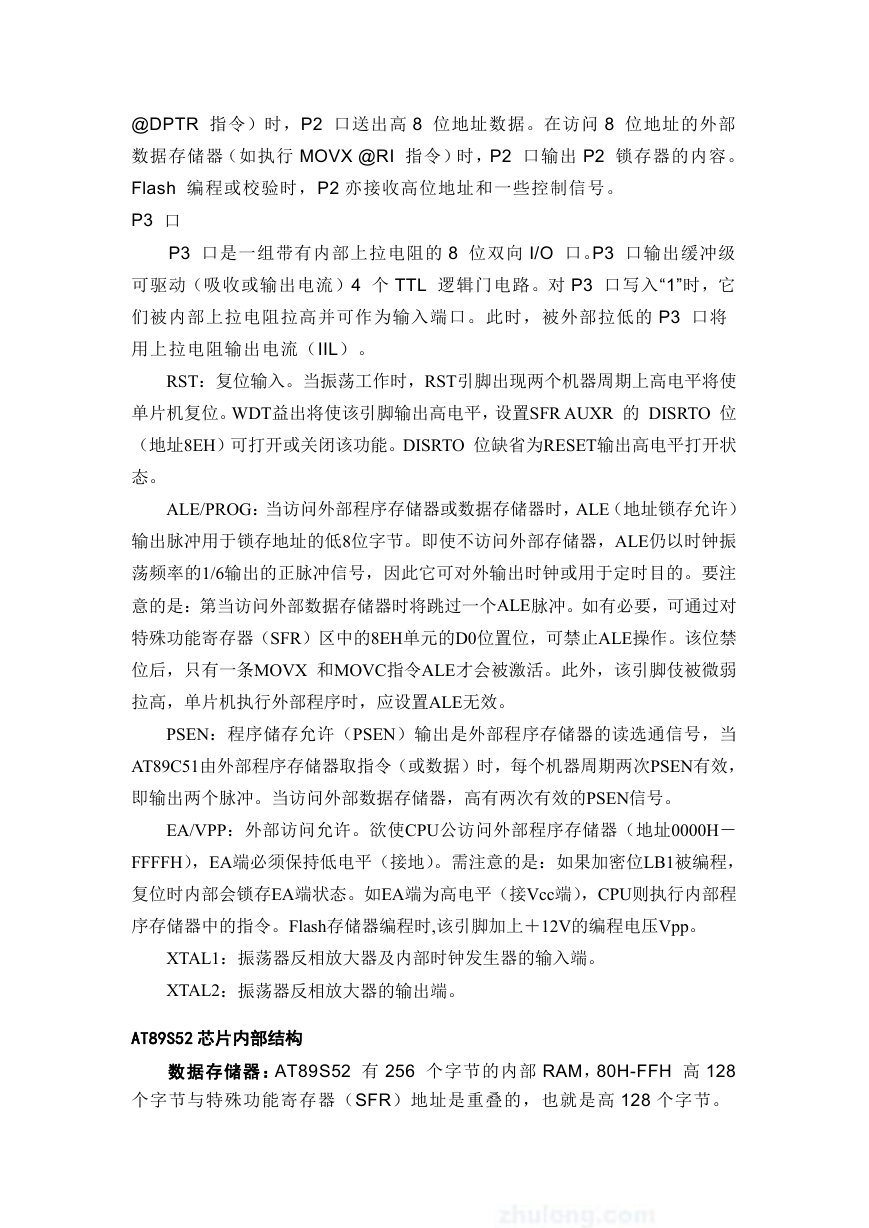

AT89S52 具有如下特点:AT89S52 有 40 个引脚,32 个外部双向输入/

输出(I/O)端口,同时内含 2 个外中断口,3 个 16 位可编程定时计数器,2

个全双工串行通信口,2 个读写口线,AT89C52 可以按照常规方法进行编

程,但不可以在线编程(S 系列的才支持在线编程)。其将通用的微处理器和

Flash 存储器结合在一起,特别是可反复擦写的 Flash 存储器可有效地降低

开发成本。AT89S52 有 PDIP、PQFP/TQFP 及 PLCC 等三种封装形式,以适应

不同产品的需求。

图 2 AT89S52 芯片引脚图

其主要功能特性:

兼容 MCS51 指令系统 · 8k 可反复擦写(>1000 次)Flash ROM

· 32 个双向 I/O 口 · 256x8bit 内部 RAM

· 3 个 16 位可编程定时/计数器中断 · 时钟频率 0-24MHz

· 2 个串行中断 · 可编程 UART 串行通道

· 2 个外部中断源 · 共 6 个中断源

· 2 个读写中断口线 · 3 级加密位

· 低功耗空闲和掉电模式 · 软件设置睡眠和唤醒功能

AT89S52 提供以下标准功能:功能包括 8K 字节 Flash 闪速存储器,256 字

节内部 RAM,对会聚主 IC 内部寄存器、数据 RAM 及外部接口等功能部件

的初始化,会聚调整控制,会聚测试图控制,红外遥控信号 IR 的接收解码

及与主板 CPU 通信等。

AT89S52 主要管脚有:XTAL1(19 脚)和 XTAL2(18 脚)为振荡器

输入输出端口,外接 12MHz 晶振。RST/Vpd(9 脚)为复位输入端口,

外接电阻电容组成的复位电路。VCC(40 脚)和 VSS(20 脚)为供电端

�

口,分别接+5V 电源的正负端。P0~P3 为可编程通用 I/O 脚,其功能用途

由软件定义,在本设计中,P0 端口(32~39 脚)被定义为 N1 功能控制

端口,分别与 N1 的相应功能管脚相连接,13 脚定义为 IR 输入端,10 脚

和 11 脚定义为 I2C 总线控制端口,分别连接 N1 的 SDAS(18 脚)和 SCLS

(19 脚)端口,12 脚、27 脚及 28 脚定义为握手信号功能端口,连接主

板 CPU 的相应功能端,用于当前制式的检测及会聚调整状态进入的控制功

能。

AT89S52 引脚功能说明

VCC:电源电压

GND:地

P1 口

P1 是一个带内部上拉电阻的 8 位双向 I/O 口, P1 的输出缓冲级可

驱动(吸收或输出电流)4 个 TTL 逻辑门电路。对端口写“1”,通过内部的

上拉电阻把端口拉到高电平,此时可作输入口。作输入口使用时,因为内

部存在上拉电阻,某个引脚被外部信号拉低时会输出一个电流(IIL)。与

AT89C51 不同之处是,P1.0 和 P1.1 还可分别作为定时/计数器 2 的外部

计数输入(P1.0/T2)和输入(P1.1/T2EX)参见表 1。

Flash 编程和程序校验期间,P1 接收低 8 位地址。

表.P1.0 和 P1.1 的第二功能

见表 1

引脚号

功能特性

引脚号

功能特性

P1.0

T2 时钟输出 P1.1

T2EX(定时/

计数器 2)

P2 口

P2 是一个带有内部上拉电阻的 8 位双向 I/O 口,P2 的输出缓冲级可

驱动(吸收或输出电流)4 个 TTL 逻辑门电路。对端口 P2 写“1”,通过内

部的上拉电阻把端口拉到高电平,此时可作输入口,作输入口使用时,因

为内部存在上拉电阻,某个引脚被外部信号拉低时会输出一个电流(IIL)。在

访问外部程序存储器或 16 位地址的外部数据存储器(例如执行 MOVX

�

@DPTR 指令)时,P2 口送出高 8 位地址数据。在访问 8 位地址的外部

数据存储器(如执行 MOVX @RI 指令)时,P2 口输出 P2 锁存器的内容。

Flash 编程或校验时,P2 亦接收高位地址和一些控制信号。

P3 口

P3 口是一组带有内部上拉电阻的 8 位双向 I/O 口。P3 口输出缓冲级

可驱动(吸收或输出电流)4 个 TTL 逻辑门电路。对 P3 口写入“1”时,它

们被内部上拉电阻拉高并可作为输入端口。此时,被外部拉低的 P3 口将

用上拉电阻输出电流(IIL)。

RST:复位输入。当振荡工作时,RST引脚出现两个机器周期上高电平将使

单片机复位。WDT益出将使该引脚输出高电平,设置SFR AUXR 的 DISRTO 位

(地址8EH)可打开或关闭该功能。DISRTO 位缺省为RESET输出高电平打开状

态。

ALE/PROG:当访问外部程序存储器或数据存储器时,ALE(地址锁存允许)

输出脉冲用于锁存地址的低8位字节。即使不访问外部存储器,ALE仍以时钟振

荡频率的1/6输出的正脉冲信号,因此它可对外输出时钟或用于定时目的。要注

意的是:第当访问外部数据存储器时将跳过一个ALE脉冲。如有必要,可通过对

特殊功能寄存器(SFR)区中的8EH单元的D0位置位,可禁止ALE操作。该位禁

位后,只有一条MOVX 和MOVC指令ALE才会被激活。此外,该引脚伎被微弱

拉高,单片机执行外部程序时,应设置ALE无效。

PSEN:程序储存允许(PSEN)输出是外部程序存储器的读选通信号,当

AT89C51由外部程序存储器取指令(或数据)时,每个机器周期两次PSEN有效,

即输出两个脉冲。当访问外部数据存储器,高有两次有效的PSEN信号。

EA/VPP:外部访问允许。欲使CPU公访问外部程序存储器(地址0000H-

FFFFH),EA端必须保持低电平(接地)。需注意的是:如果加密位LB1被编程,

复位时内部会锁存EA端状态。如EA端为高电平(接Vcc端),CPU则执行内部程

序存储器中的指令。Flash存储器编程时,该引脚加上+12V的编程电压Vpp。

XTAL1:振荡器反相放大器及内部时钟发生器的输入端。

XTAL2:振荡器反相放大器的输出端。

AT89S52 芯片内部结构

数据存储器:AT89S52 有 256 个字节的内部 RAM,80H-FFH 高 128

个字节与特殊功能寄存器(SFR)地址是重叠的,也就是高 128 个字节。

�

定时器 2:定时器 2 是一个 16 位定时/计数器。它既可当定时器使用,

也可作为外部事件计数器使用,其工作方式由特殊功能寄存器 T2CON(如

表 3)的 C/T2 位选择。定时器 2 有三种工作方式:捕获方式,自动重装

载(向上或向下计数)方式和波特率发生器方式,工作方式由 T2CON 的

控制位来选择。

在计数工作方式时,当 T2 引脚上外部输入信号产生由 1 至 0 的下降

沿时,寄存器的值加 1,在这种工作方式下,每个机器周期的 5SP2 期间,

对外部输入进行采样。若在第一个机器周期中采到的值为 1,而在下一个机

器周期中采到的值为 0,则在紧跟着的下一个周期的 S3P1 期间寄存器加 1。

由于识别 1 至 0 的跳变需要 2 个机器周期(24 个振荡周期),因此,最

高计数速率为振荡频率的 1/24。为确保采样的正确性,要求输入的电平在

变化前至少保持一个完整周期的时间,以保证输入信号至少被采样一次。

自动重装载(向上或向下计数器)方式:当定时器 2 工作于 16 位自动

重装载方式时,能对其编程为向上或向下计数方式,这个功能可通过特殊

功能寄存器 T2CON 来选择。复位时,DCEN 位置“0”,定时器 2 默认设置

为向上计数。当 DCEN 置位时,定时器 2 既可向上计数也可向下计数,这

取决于 T2EX 引脚的值。

当 DCEN=0 时,定时器 2 自动设置为向上计数,在这种方式下,

T2CON 中的 EXEN2 控制位有两种选择,若 EXEN2=0,定时器 2 为向上

计数至 0FFFFH 溢出,置位 TF2 激活中断,同时把 16 位计数寄存器

RCAP2H 和 RCAP2L 重装载,RCAP2H 和 RCAP2L 的值可由软件预置。

若 EXEN2=1,定时器 2 的 16 位重装载由溢出或外部输入端 T2EX 从 1 至

0 的下降沿触发。这个脉冲使 EXF2 置位,如果中断允许,同样产生中断

定时器 2 的中断入口地址是:002BH ——0032H 。

当 DCEN=1 时,允许定时器 2 向上或向下计数。这种方式下,T2EX

引脚控制计数器方向。T2EX 引脚为逻辑“1”时,定时器向上计数,当计数

0FFFFH 向上溢出时,置位 TF2,同时把 16 位计数寄存器 RCAP2H 和

RCAP2L 重装载到 TH2 和 TL2 中。T2EX 引脚为逻辑“0”时,定时器 2 向

下计数,当 TH2 和 TL2 中的数值等于 RCAP2H 和 RCAP2L 中的值时,

计数溢出,置位 TF2,同时将 0FFFFH 数值重新装入定时寄存器中。当定

时/计数器 2 向上溢出或向下溢出时,置位 EXF2 位。

�

时钟振荡器:AT89S52 中有一个用于构成内部振荡器的高增益反相放

大器,引脚 XTAL1 和 XTAL2 分别是该放大器的输入端和输出端。外接石

英晶体(或陶瓷谐振器)及电容 C1、C2 接在放大器的反馈回路中构成并

联振荡电路。

空闲节电模式:在空闲工作模式状态, CPU 自身处于睡眠状态而所

有片内的外设仍保持激活状态,这种方式由软件产生。此时,同时将片内 R

AM 和所有特殊功能寄存器的内容冻结。空闲模式可由任何允许的中断请

求或硬件复位终止。由硬件复位终止空闲状态只需两个机器周期有效复位

信号,在此状态下,片内硬件禁止访问内部 RAM,但可以访问端口引脚,

当用复位终止空闲方式时,为避免可能对端口产生意外写入,激活空闲模

式的那条指令后一条指令不应是一条对端口或外部存储器的写入指令。

掉电模式:在掉电模式下,振荡器停止工作,进入掉电模式的指令是

最后一条被执行的指令,片内 RAM 和特殊功能寄存器的内容在终止掉电

模式前被冻结。退出掉电模式的唯一方法是硬件复位,复位后将重新定义

全部特殊功能寄存器,但不改变 RAM 中的内容,在 Vcc 恢复到正常工作电

平前,复位应无效,且必须保持一定时间以使振荡器重启动并稳定工作。

程序存储器的加密:AT89S52 有 3 个程序加密位,可对芯片上的 3 个

加密位 LB1、LB2、LB3 进行编程(P)或不编程(U)来得到。当加密位

LB1 被编程时,在复位期间,EA 端的逻辑电平被采样并锁存,如果单片

机上电后一直没有复位,则锁存起的初始值是一个随机数,且这个随机数

会一直保存到真正复位为止。为使单片机能正常工作,被锁存的 EA 电平

值必须与该引脚当前的逻辑电平一致。此外,加密位只能通过整片擦除的

方法清除。

Flash 存储器的编程:AT89S52 单片机内部有 8k 字节的 Flash PERO

M,这个 Flash 存储阵列出厂时已处于擦除状态(即所有存储单元的内容

均为 FFH),用户随时可对其进行编程。编程接口可接收高电压(+12V)

或低电压(Vcc)的允许编程信号。低电压编程模式适合于用户在线编程系

统,而高电压编程模式可与通用 EPROM 编程器兼容。

2.2.2 密码存储电路设计

密码存储采用 AT24C16 存储,它能掉电存储数据。掉电存储单元的作用是

在系统电源断开的时候,存储当前设定的密码数据。AT24C16 是只读存储器,

存储容量是 16KB,采用 16 位串行 CMOS EEPRO 技术,内部结构曹永 2048bit

的存储单元,工作在低电源,低频率的条件下。它能接收,存储微处理单元集成

电路提供的数字信号,可以用作发送器(主控)和接收器。一旦微处理单元需要

其中存储的数据信号,可以随时输入和输出。AT24C16 为非挥发性电可擦除只

读存储器,通过 IIC 总线串行接口来控制工作,也具备特殊的写保护功能。当 W

P 端连至 VCC 时,整个存储矩阵置为写保护状态(只读);当 WP 端连至 VSS

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc