FPGA 设计思想与验证方法视频教程实验精讲手册

本系列共 20 个实验精讲手册全部由山东大学研友袁卓整理,特此感谢

大家好,这里小梅哥将我们精心录制和编辑的 FPGA 学习系列教程——《小

梅哥 FPGA 设计思想与验证方法视频教程》分享给大家。教程充分考虑 0 基础朋

友的实际情况,手把手带领学习者分析思路、编写代码、仿真验证、板级调试。

教语法,学仿真,一步一步,直到最后设计若干较为综合的逻辑系统。

1

教程以我们自主开发的芯路恒 FPGA 学习板为实验平台,通过若干基础和综

合的系统设计讲解,一步一步掌握 FPGA 设计与验证的思想和方法。

注意,购买了开发板的客户,在进行本实验时,记得使用我们提供的引脚分

配表中的引脚分配,不要跟着视频中的引脚分配进行分配,尤其是使用和我们配

套视频中不一样的硬件平台时。在本文档中针对每个实验也都提供了相应的硬件

分配表。

�

FPGA 设计思想与验证方法视频教程实验精讲手册 ............................................. 1

一、FPGA 设计流程介绍 .............................................................................. 3

二、组合逻辑电路设计之译码器 .................................................................18

三、时序逻辑电路设计之计数器 .................................................................24

四、IP 核应用之计数器 ................................................................................33

五、BCD 计数器设计与应用 ........................................................................47

六、阻塞赋值与非阻塞赋值原理分析 ..........................................................60

七、状态机设计实例 ....................................................................................68

八、独立按键消抖实验 A .............................................................................77

九、独立按键消抖实验 B .............................................................................94

十、8 位 7 段数码管驱动实验 .................................................................... 103

十一、串口发送模块设计与验证 ............................................................... 118

十二、串口接收模块设计与验证 ............................................................... 136

十三 A、嵌入式 RAM 使用之双端口 RAM ............................................... 153

十三 B、搭建串口收发与存储双口 RAM 简易应用系统 ........................... 164

十四、嵌入式 RAM 使用之 ROM .............................................................. 171

十五、嵌入式块 RAM 使用之 FIFO ........................................................... 185

十六、PLL 锁相环介绍与简单应用............................................................ 200

十七、线性序列机与串行接口 DAC 驱动设计 .......................................... 214

十八、线性序列机与 TLV5144 驱动设计 ................................................... 236

十九、HT6221 红外遥控解码 ..................................................................... 257

�

一、FPGA 设计流程介绍

本集是视频教程第一讲,主要通过一个实例简单演示 FPGA 开发的基本流

程。本人也是自学过两年 FPGA,并参加了国内某专业的 FPGA 培训机构 100 天

就业培训,并最终留任授课 3 个月。因此十分清楚了解各位学习者在刚开始学习

FPGA 时的各种苦闷。因此希望通过这样一个视频教程,把较为科学的 FPGA 学

习方法和思想传递给大家。

如果大家所认为的 FPGA 开发流程就是编码、下载、调试,那么你就该好好

的看下这个视频教程了,因为我也正是被这种错误的学习方式耽误了好久好久,

直到参加了培训学习才知道,仿真验证才是 FPGA 开发的重中之重,现在的我进

行 FPGA 开发,板级调试时间占不到整个开发过程的 5%,并不是我不重视板级

调试,而是因为通过完整的理论验证之后,下载到板级上基本不会出现任何问题。

科学的学习方法尤为重要,希望大家一定要注意这一点。我也曾在工作中遇到很

多人,就算是我手把手的教他仿真、写 testbench,他也不愿意弄的情况,因此我

只想在这里说,不仿真,永远无法掌握 FPGA 时序设计的要点,做设计永远是事

倍功半。

课程目标

1. 了解并学会 FPGA 开发设计的整体流程

2. 设计一个二选一选择器并进行功能仿真、时序仿真以及板级验证

实验平台

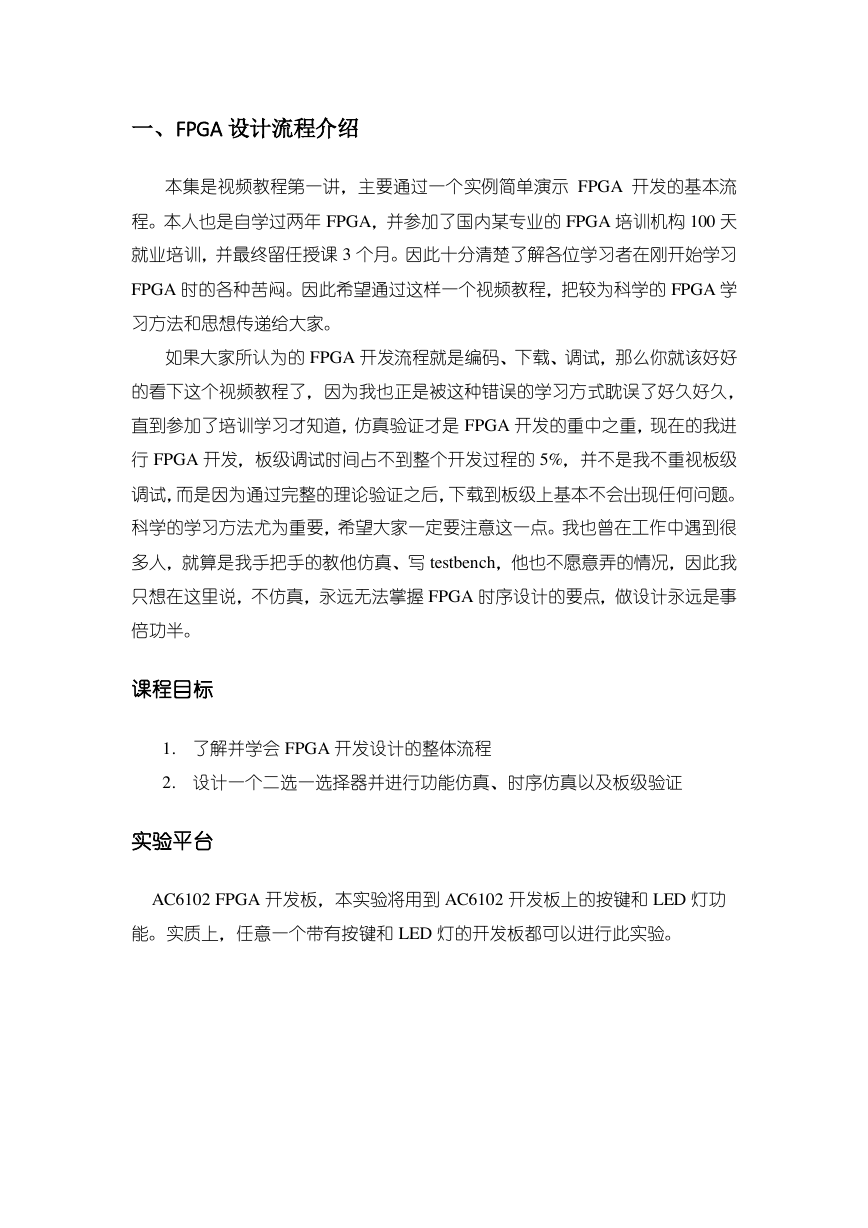

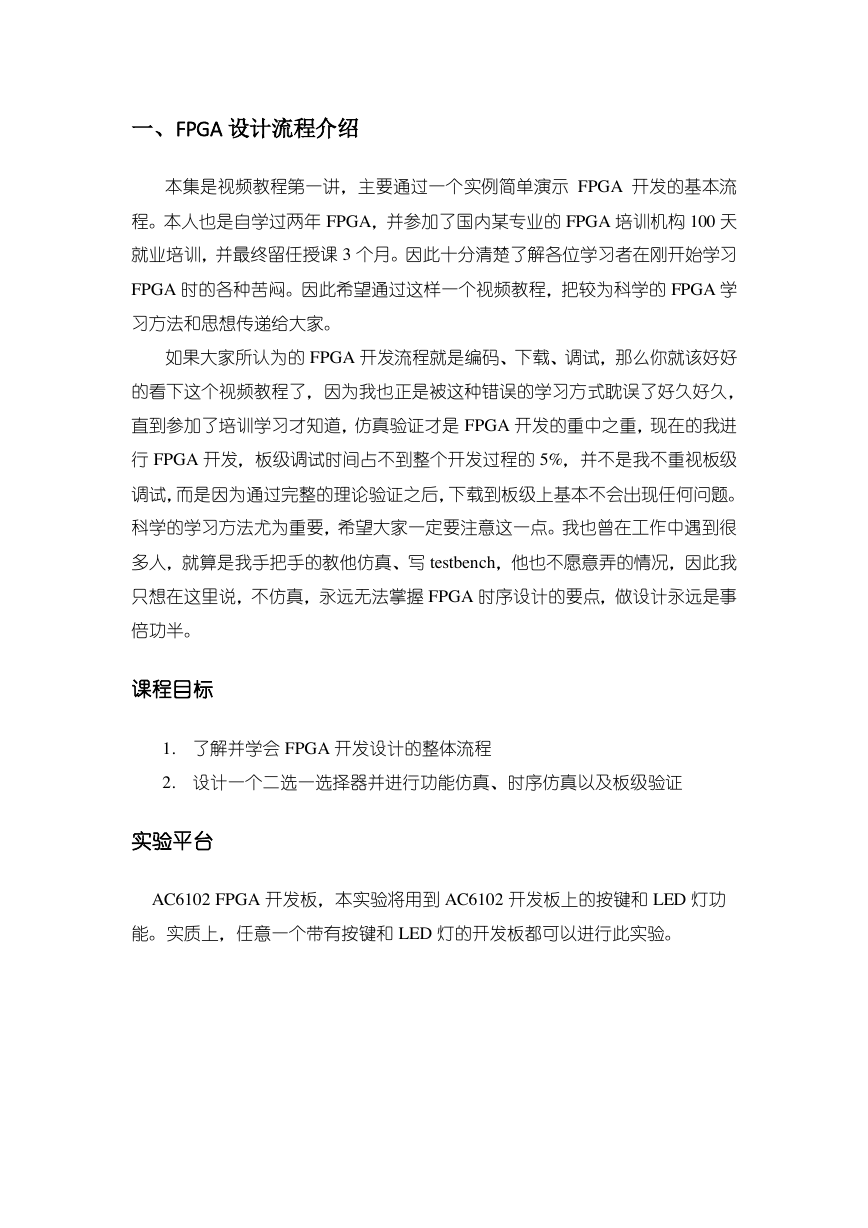

AC6102 FPGA 开发板,本实验将用到 AC6102 开发板上的按键和 LED 灯功

能。实质上,任意一个带有按键和 LED 灯的开发板都可以进行此实验。

�

实验内容

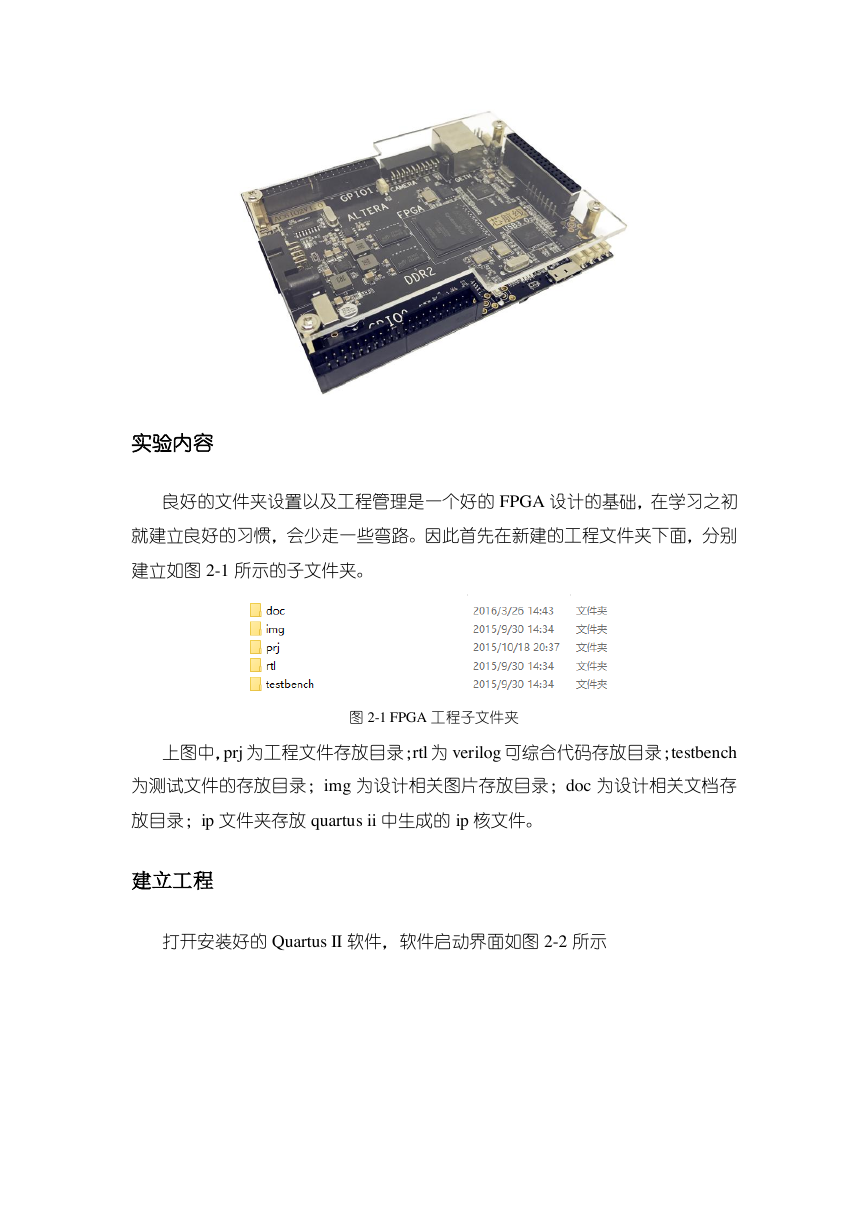

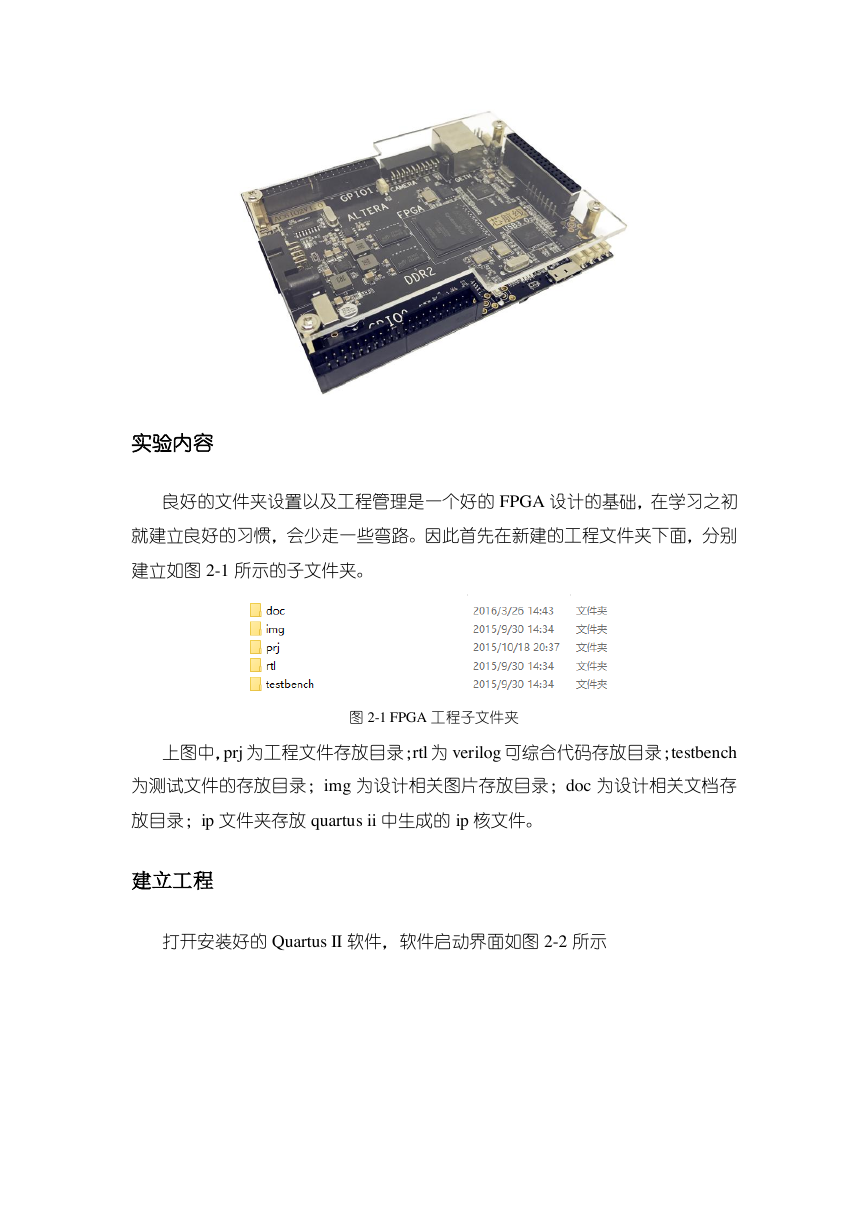

良好的文件夹设置以及工程管理是一个好的 FPGA 设计的基础,在学习之初

就建立良好的习惯,会少走一些弯路。因此首先在新建的工程文件夹下面,分别

建立如图 2-1 所示的子文件夹。

图 2-1 FPGA 工程子文件夹

上图中,prj 为工程文件存放目录;rtl 为 verilog 可综合代码存放目录;testbench

为测试文件的存放目录;img 为设计相关图片存放目录;doc 为设计相关文档存

放目录;ip 文件夹存放 quartus ii 中生成的 ip 核文件。

建立工程

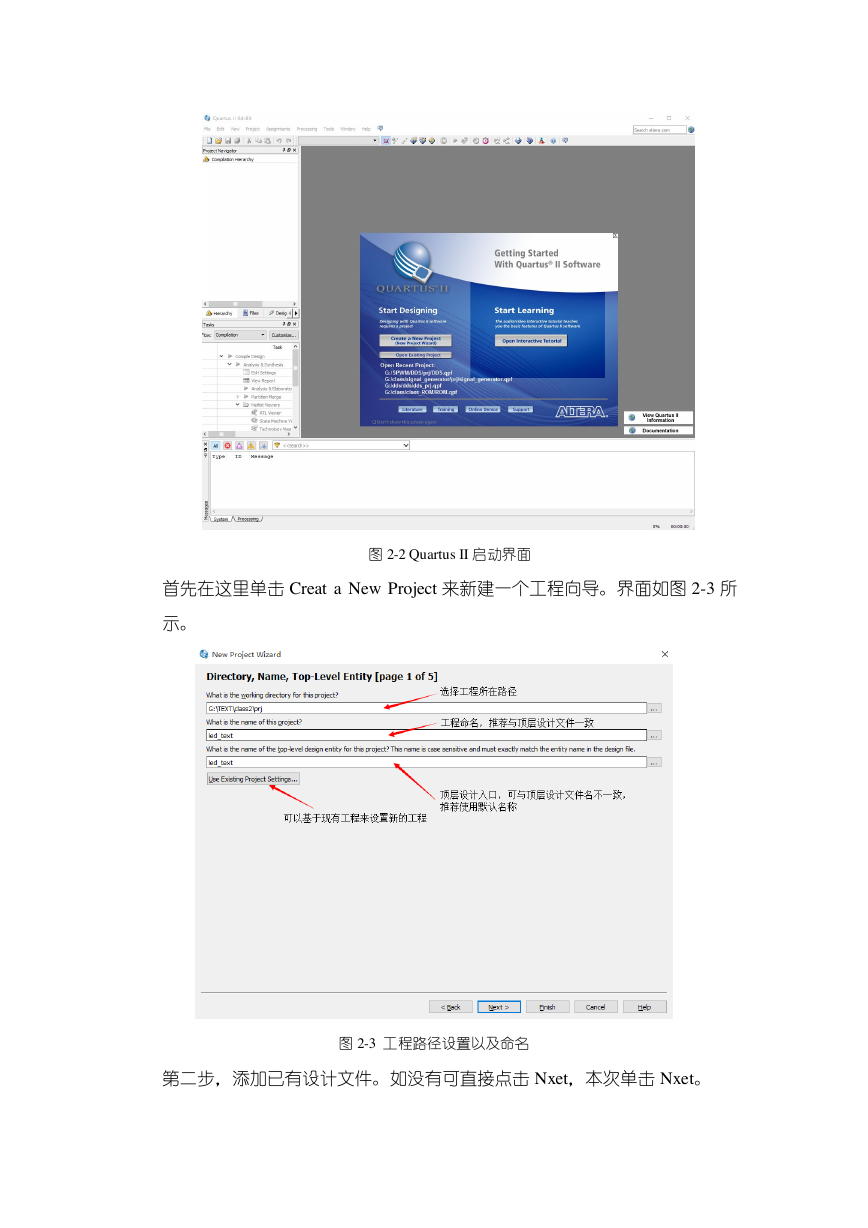

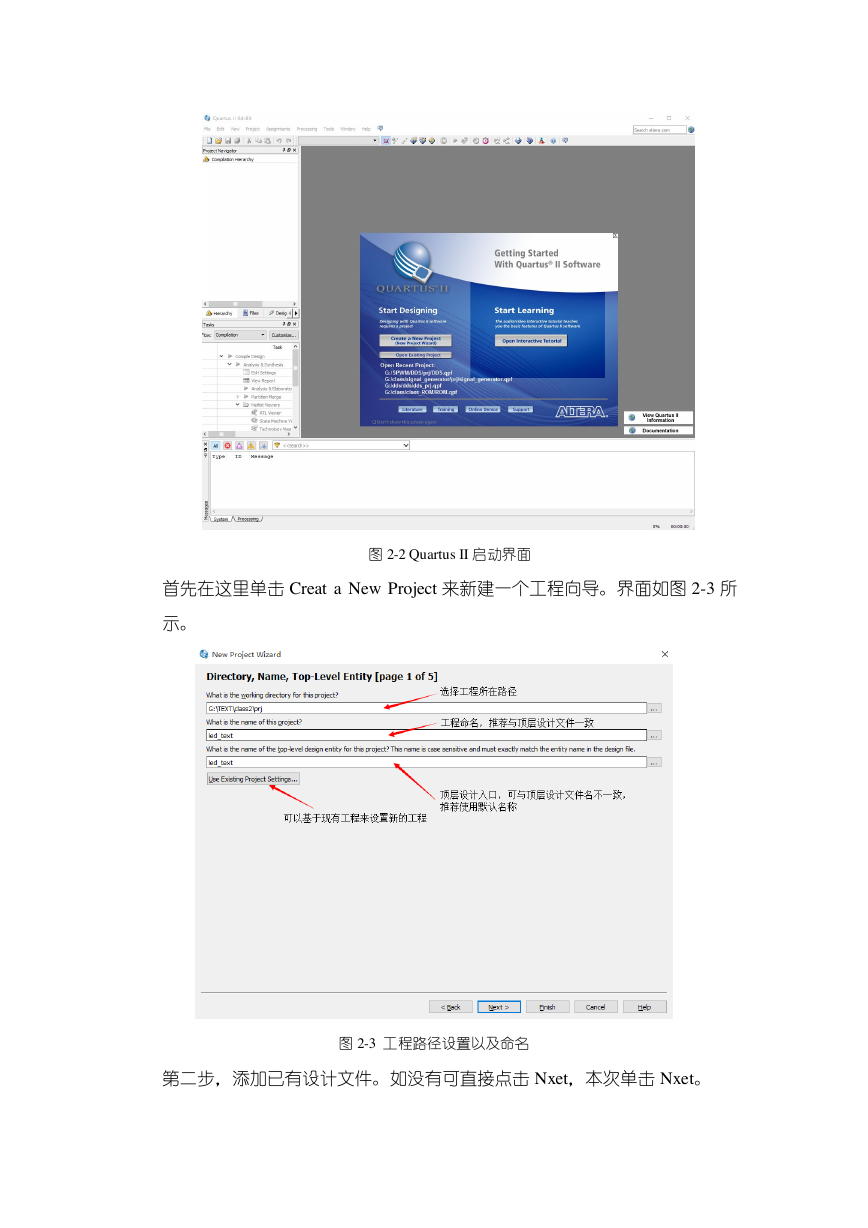

打开安装好的 Quartus II 软件,软件启动界面如图 2-2 所示

�

图 2-2 Quartus II 启动界面

首先在这里单击 Creat a New Project 来新建一个工程向导。界面如图 2-3 所

示。

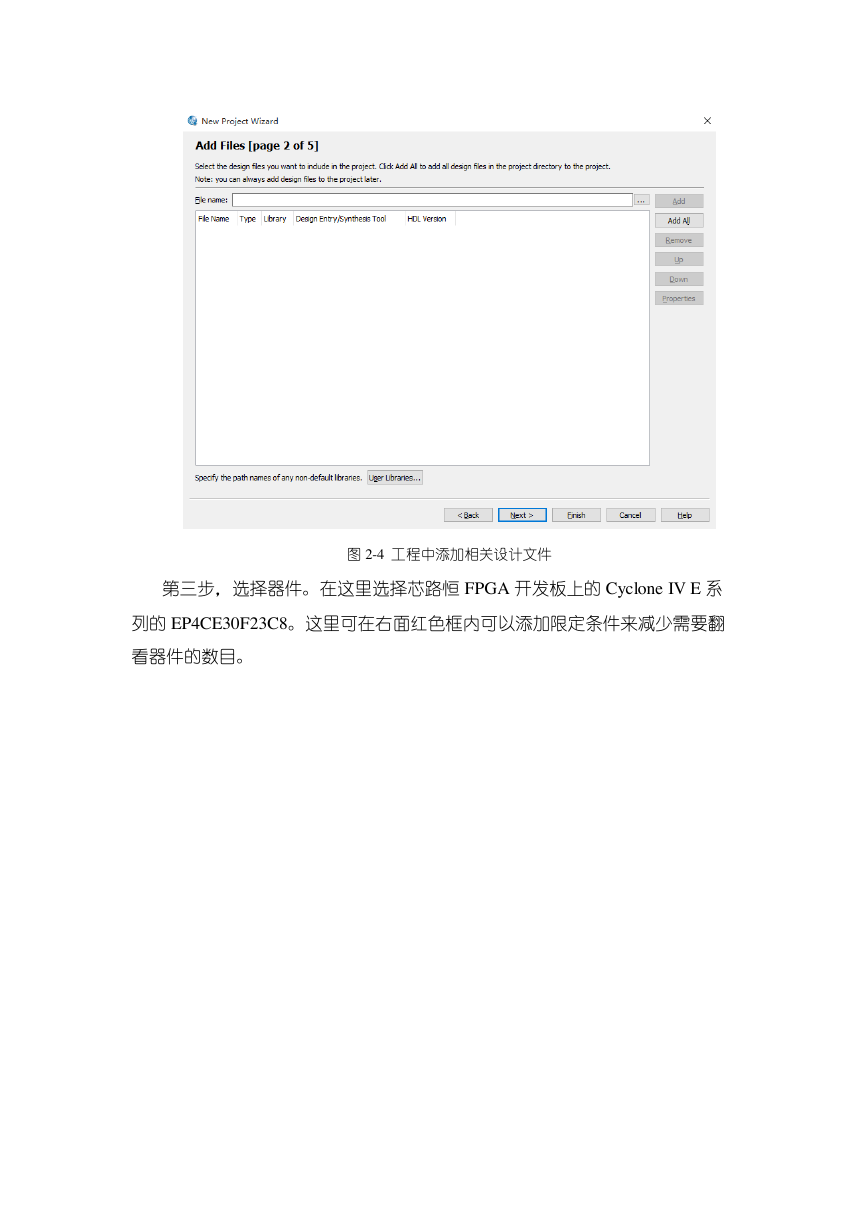

图 2-3 工程路径设置以及命名

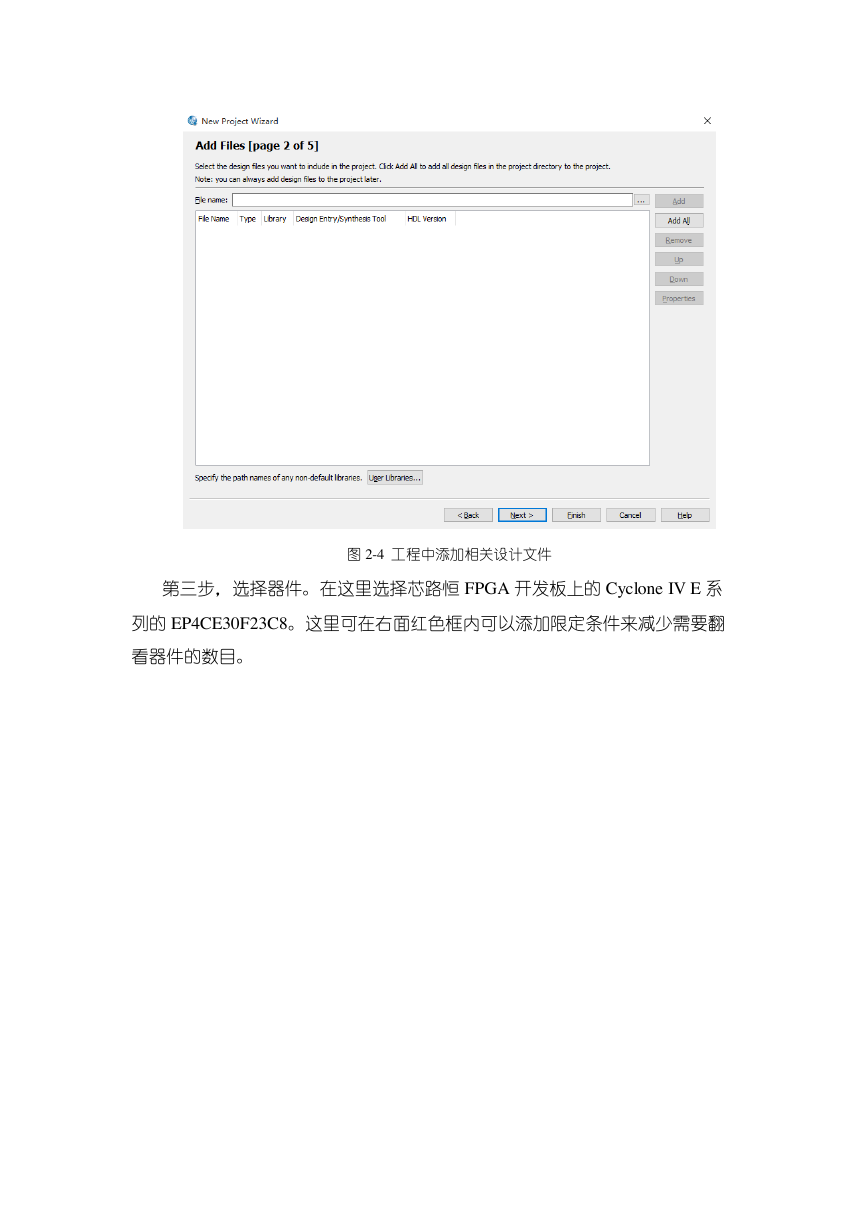

第二步,添加已有设计文件。如没有可直接点击 Nxet,本次单击 Nxet。

�

图 2-4 工程中添加相关设计文件

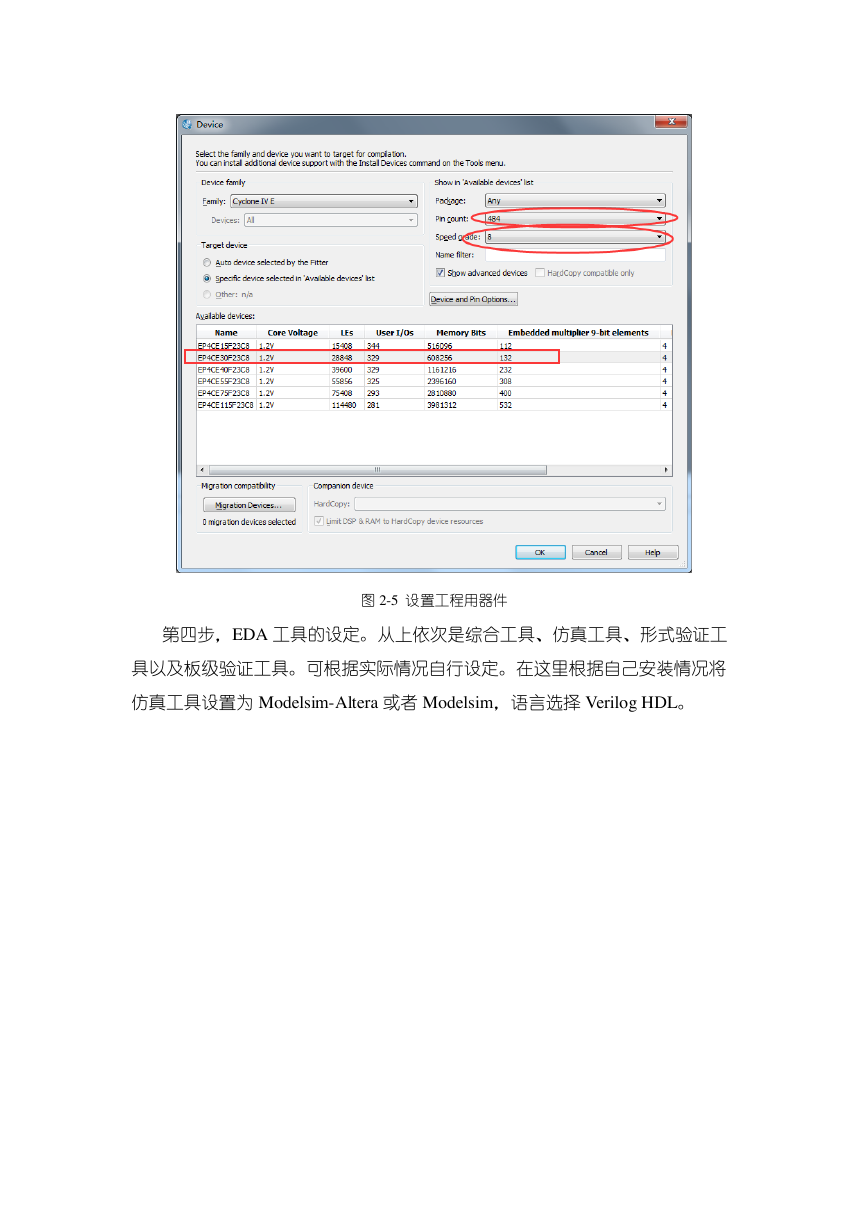

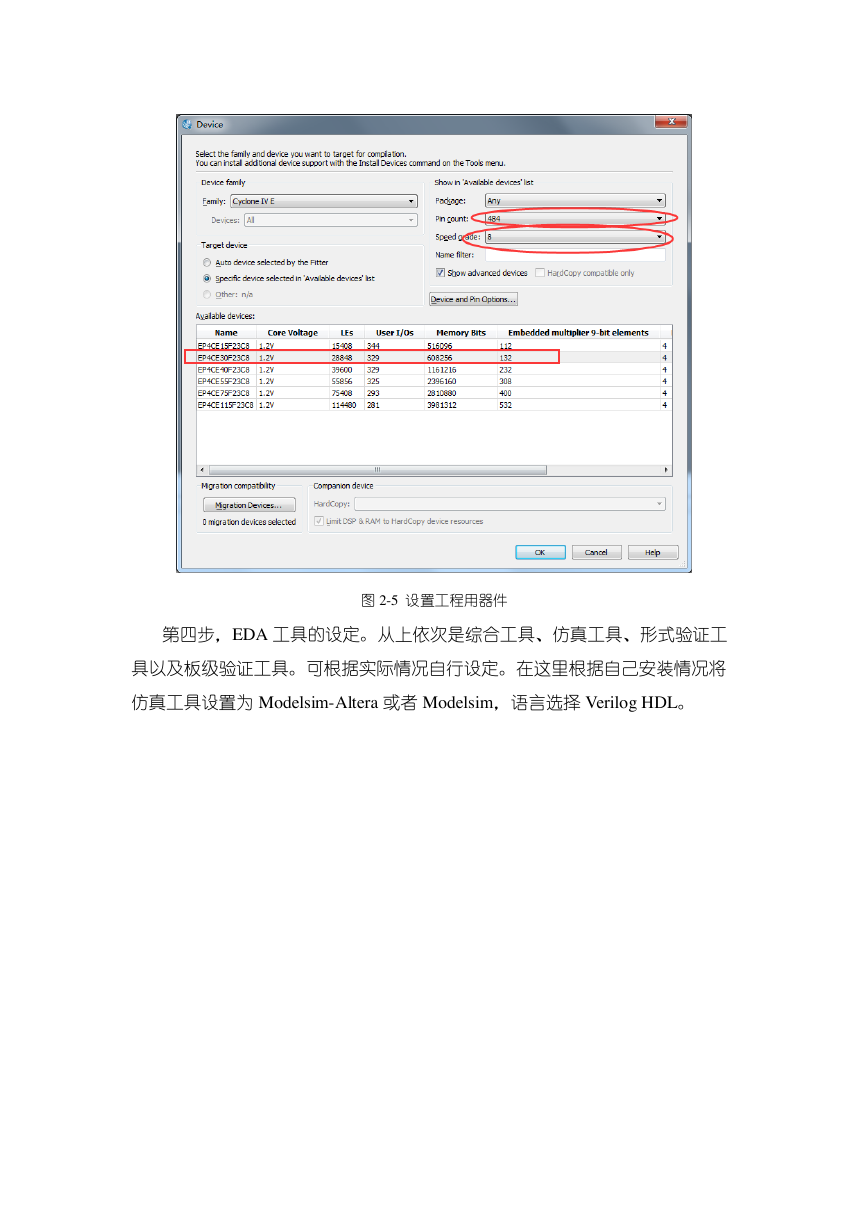

第三步,选择器件。在这里选择芯路恒 FPGA 开发板上的 Cyclone IV E 系

列的 EP4CE30F23C8。这里可在右面红色框内可以添加限定条件来减少需要翻

看器件的数目。

�

图 2-5 设置工程用器件

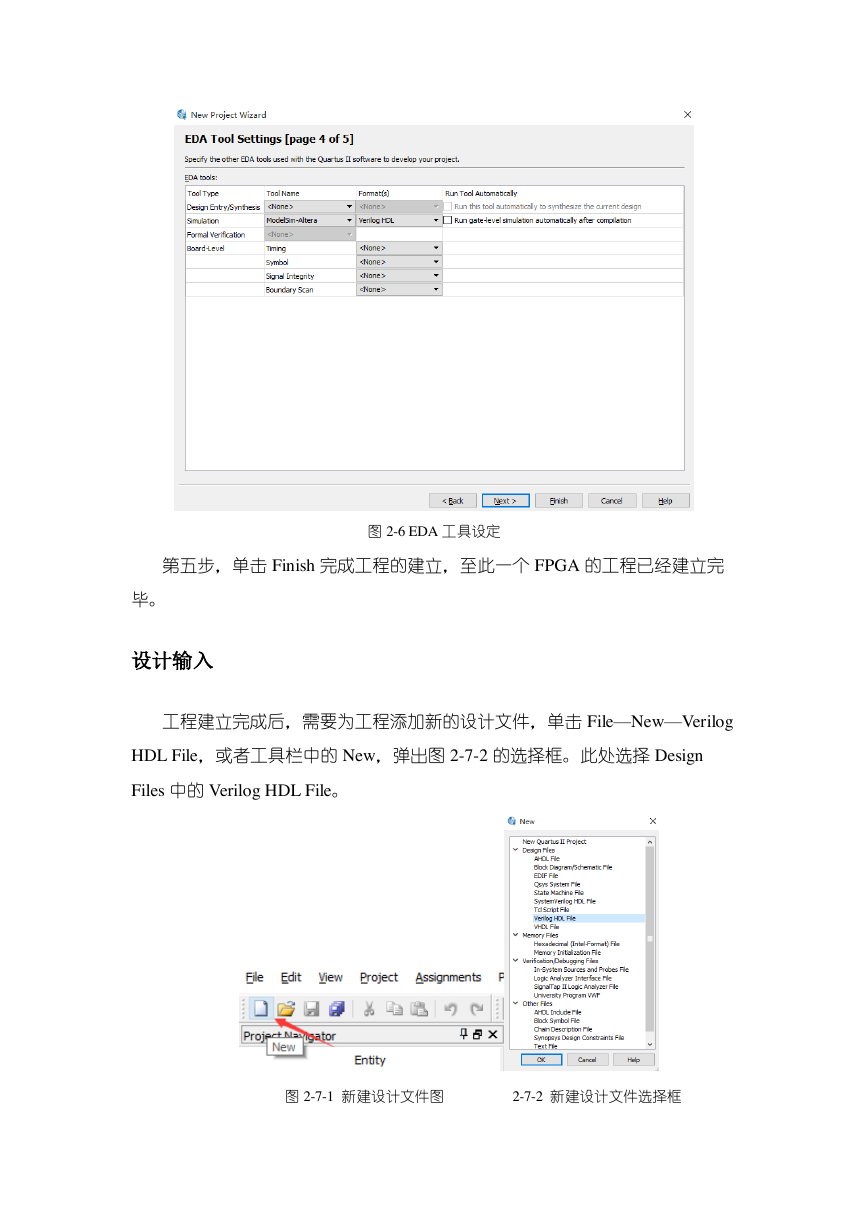

第四步,EDA 工具的设定。从上依次是综合工具、仿真工具、形式验证工

具以及板级验证工具。可根据实际情况自行设定。在这里根据自己安装情况将

仿真工具设置为 Modelsim-Altera 或者 Modelsim,语言选择 Verilog HDL。

�

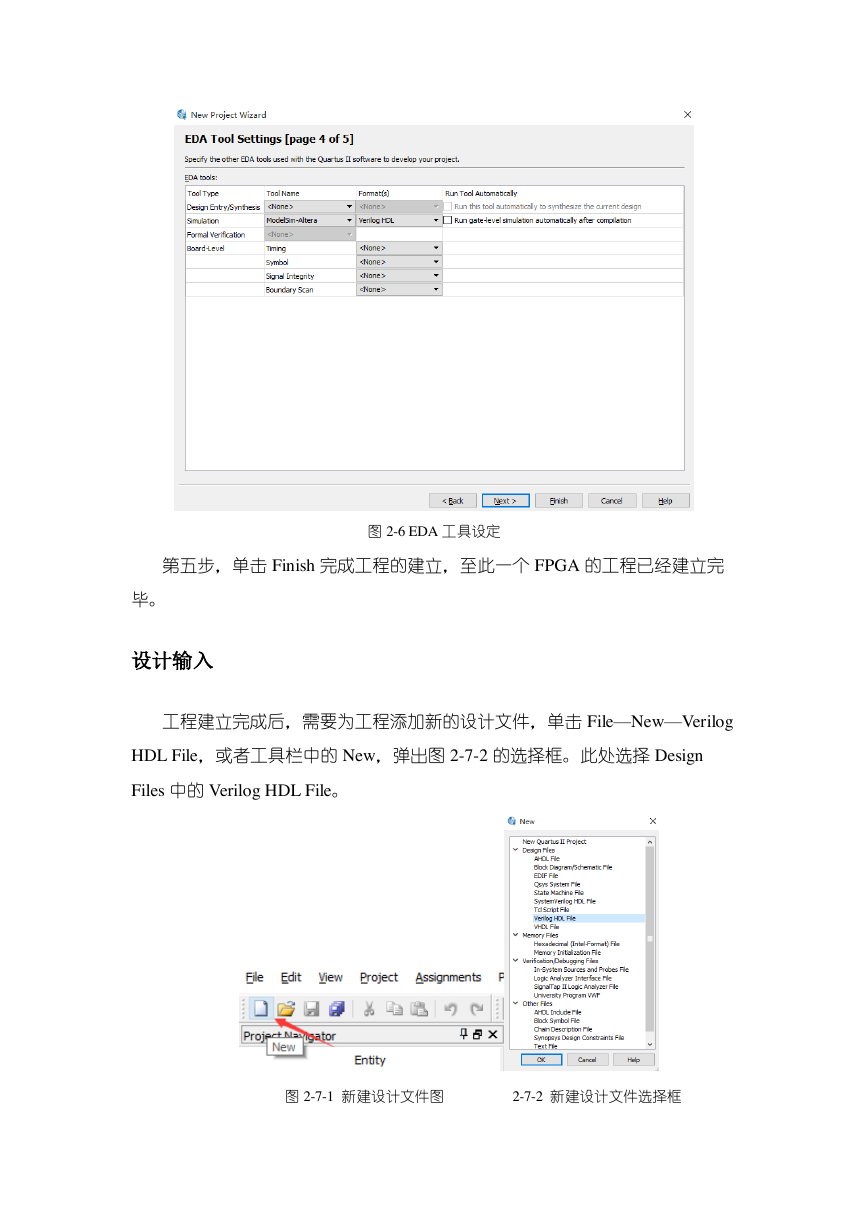

图 2-6 EDA 工具设定

第五步,单击 Finish 完成工程的建立,至此一个 FPGA 的工程已经建立完

毕。

设计输入

工程建立完成后,需要为工程添加新的设计文件,单击 File—New—Verilog

HDL File,或者工具栏中的 New,弹出图 2-7-2 的选择框。此处选择 Design

Files 中的 Verilog HDL File。

图 2-7-1 新建设计文件图 2-7-2 新建设计文件选择框

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc