集成电路版图设计复习

一、名词解释

1.版图设计:根据逻辑与电路功能和性能要求以及工艺水平要求,来设计光刻用的掩

膜版图,是集成电路设计的最终输出。

2.布图规划:根据模块所包含的器件数估计其面积,再根据该模块与其他模块的连接

关系以及上一层模块或芯片的形状,估计该模块的形状和相对位置

3.几何设计规则:可看作光刻掩模版的制备要求,这些规则在生产阶段为电路设计师

和工艺工程师提供了一种必要的信息联系。与版图规则相联系的主要目标是获得具有最

佳成品率的电路,而几何尺寸则尽可能地小,同时又不影响器件电路的可靠性。

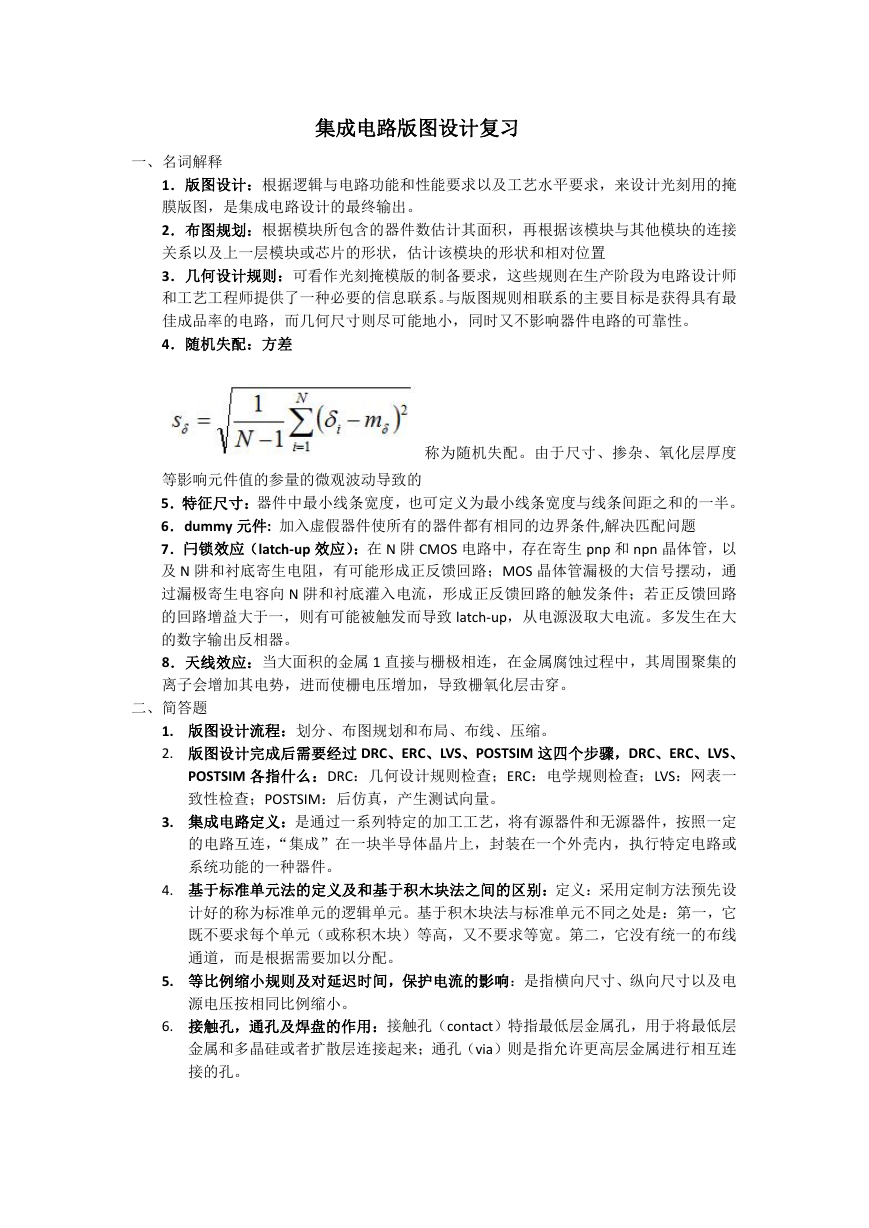

4.随机失配:方差

称为随机失配。由于尺寸、掺杂、氧化层厚度

等影响元件值的参量的微观波动导致的

5.特征尺寸:器件中最小线条宽度,也可定义为最小线条宽度与线条间距之和的一半。

6.dummy 元件: 加入虚假器件使所有的器件都有相同的边界条件,解决匹配问题

7.闩锁效应(latch-up 效应):在 N 阱 CMOS 电路中,存在寄生 pnp 和 npn 晶体管,以

及 N 阱和衬底寄生电阻,有可能形成正反馈回路;MOS 晶体管漏极的大信号摆动,通

过漏极寄生电容向 N 阱和衬底灌入电流,形成正反馈回路的触发条件;若正反馈回路

的回路增益大于一,则有可能被触发而导致 latch-up,从电源汲取大电流。多发生在大

的数字输出反相器。

8.天线效应:当大面积的金属 1 直接与栅极相连,在金属腐蚀过程中,其周围聚集的

离子会增加其电势,进而使栅电压增加,导致栅氧化层击穿。

二、简答题

1. 版图设计流程:划分、布图规划和布局、布线、压缩。

2. 版图设计完成后需要经过 DRC、ERC、LVS、POSTSIM 这四个步骤,DRC、ERC、LVS、

POSTSIM 各指什么:DRC:几何设计规则检查;ERC:电学规则检查;LVS:网表一

致性检查;POSTSIM:后仿真,产生测试向量。

3. 集成电路定义:是通过一系列特定的加工工艺,将有源器件和无源器件,按照一定

的电路互连,“集成”在一块半导体晶片上,封装在一个外壳内,执行特定电路或

系统功能的一种器件。

4. 基于标准单元法的定义及和基于积木块法之间的区别:定义:采用定制方法预先设

计好的称为标准单元的逻辑单元。基于积木块法与标准单元不同之处是:第一,它

既不要求每个单元(或称积木块)等高,又不要求等宽。第二,它没有统一的布线

通道,而是根据需要加以分配。

5. 等比例缩小规则及对延迟时间,保护电流的影响:是指横向尺寸、纵向尺寸以及电

源电压按相同比例缩小。

6. 接触孔,通孔及焊盘的作用:接触孔(contact)特指最低层金属孔,用于将最低层

金属和多晶硅或者扩散层连接起来;通孔(via)则是指允许更高层金属进行相互连

接的孔。

�

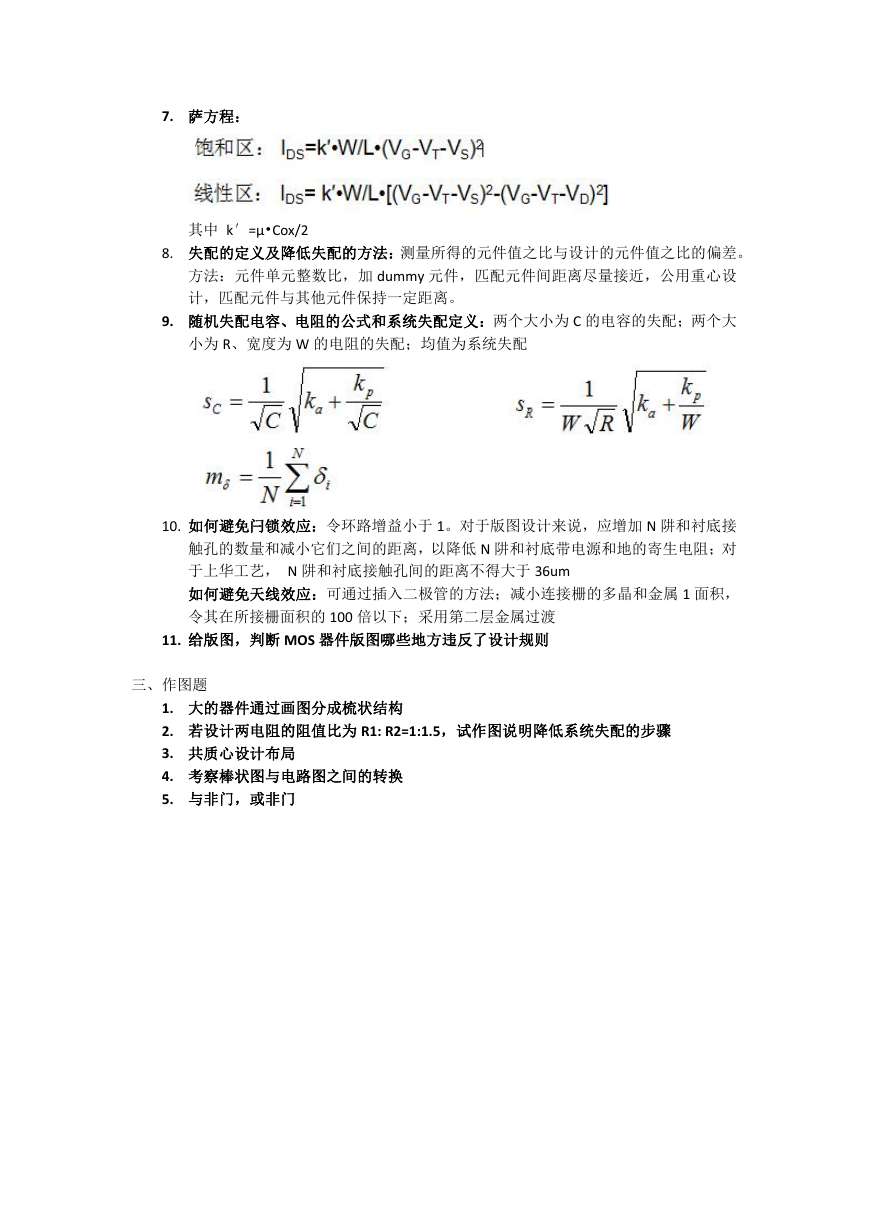

7. 萨方程:

其中 k′=µ•Cox/2

8. 失配的定义及降低失配的方法:测量所得的元件值之比与设计的元件值之比的偏差。

方法:元件单元整数比,加 dummy 元件,匹配元件间距离尽量接近,公用重心设

计,匹配元件与其他元件保持一定距离。

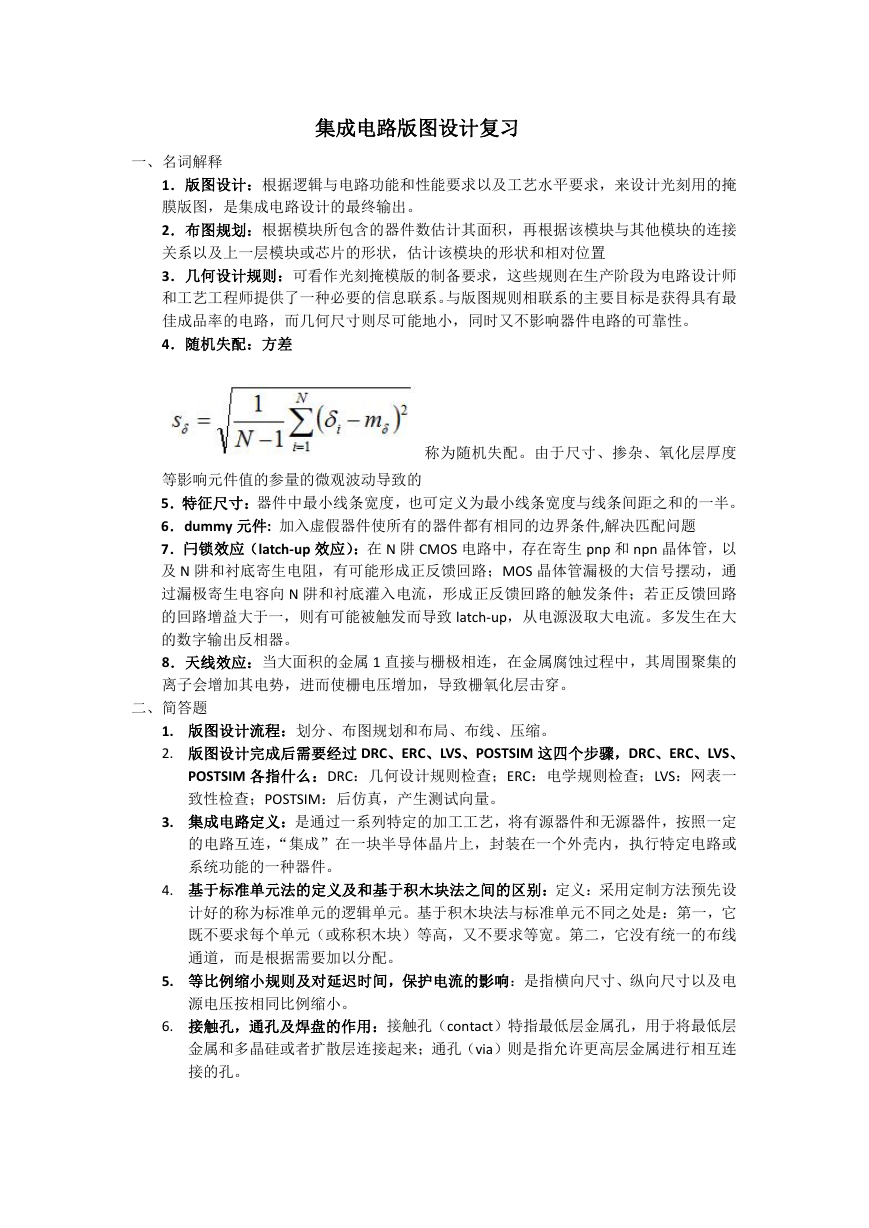

9. 随机失配电容、电阻的公式和系统失配定义:两个大小为 C 的电容的失配;两个大

小为 R、宽度为 W 的电阻的失配;均值为系统失配

10. 如何避免闩锁效应:令环路增益小于 1。对于版图设计来说,应增加 N 阱和衬底接

触孔的数量和减小它们之间的距离,以降低 N 阱和衬底带电源和地的寄生电阻;对

于上华工艺, N 阱和衬底接触孔间的距离不得大于 36um

如何避免天线效应:可通过插入二极管的方法;减小连接栅的多晶和金属 1 面积,

令其在所接栅面积的 100 倍以下;采用第二层金属过渡

11. 给版图,判断 MOS 器件版图哪些地方违反了设计规则

三、作图题

1. 大的器件通过画图分成梳状结构

2. 若设计两电阻的阻值比为 R1: R2=1:1.5,试作图说明降低系统失配的步骤

3. 共质心设计布局

4. 考察棒状图与电路图之间的转换

5. 与非门,或非门

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc