中国科技论文在线

http://www.paper.edu.cn

基于 FPGA 的多功能扫频信号源的设计

刘颢阳,李绍胜**

(北京邮电大学信息与通信工程学院,北京 100876)

摘要:扫频信号源是扫频仪主要功能部件,对其实现方法进行研究有重要意义。本文给出了

一种由 FPGA 与 DAC 组合的扫频信号源设计方案。信号源主要采用 DDS 技术实现,本设

计使用并行 NCO 和并串转换的方式实现了在较低频率时钟驱动下生成较高频率信号的目

的,提高了信号源的输出频率范围。该方案具有多功能、成本低、体积小、使用灵活等特点。

关键词:DDS; FPGA; 并串转换

中图分类号:TN741

The design of multi-function sweep signal source based on

FPGA

LIU Haoyang, LI Shaosheng

Telecommnications, Beijing 100876)

(School of Information and Communication Engineering, Beijing University of Posts and

Abstract: The frequency sweep signal source is the main functional components of sweeper. It is

significant to study the way to realize it. This paper describes a design of sweep signal source,

which uses a combination of FPGA and DAC. The signal source using DSS technology. The

design uses parallel NCOs and parallel to serial conversion method to achieve the goal of

generator higher frequency signal waveform by a lower frequency clock. This increases the signal

source output frequency range. The design has the features of multi-functional, low cost, small

size, using flexible.

Key words: DDS; FPGA; parallel to serial conversion

0 引言

频率特性是电子部件、电路或系统设备的一项重要技术指标,扫频仪是用于测量系统频

率特性的测量仪器,其在通信、信号处理等领域具有广泛的应用。扫频信号源是扫频仪的主

要功能部件,作用是产生测量用的正弦扫频信号,其扫频范围可调,输出信号的幅度等幅。

传统的扫频信号源多是基于压控振荡器(VCO)、锁相环等技术。随着对所测量的频

率和精度的要求不断提高,传统的扫频信号源暴露出转换频率时间长、频率精度不高、硬件

庞大等问题,已经渐渐不能满足需求。

随着现代电子技术的飞速发展,目前 DA 转换器速率已高达 1GSPS 以上,而现场可编

程门阵列(FPGA)的规模达到了百万门级,工作速度达到数百兆赫兹,内嵌 RAM、乘法

器和快速进位链等部件使其运算能力相当可观[1]。在这种情况下,出现了以直接数字频率合

成(DDS)技术为核心的数字扫频信号源。与其他频率合成方法相比,直接数字频率合成具

有合成频率准确、分辨率高、频率转换时间短、全数字控制灵活等优点。本设计中的扫频信

号源采用直接数字频率合成方法,除 DA 转换功能外,均在单片 FPGA 上实现,可根据使用

者的需要,设置输出扫频信号的频率、信号幅度,还可用于输出带调制的频率信号在内的多

种信号。

作者简介:刘颢阳(1985-),男,在读研究生,主要研究方向:嵌入式开发

通信联系人:李绍胜,(1966-),男,副教授,主要研究方向:软件无线电. E-mail: lss@bupt.edu.cn

- 1 -

5

10

15

20

25

30

35

40

�

中国科技论文在线

1 DDS 技术原理

http://www.paper.edu.cn

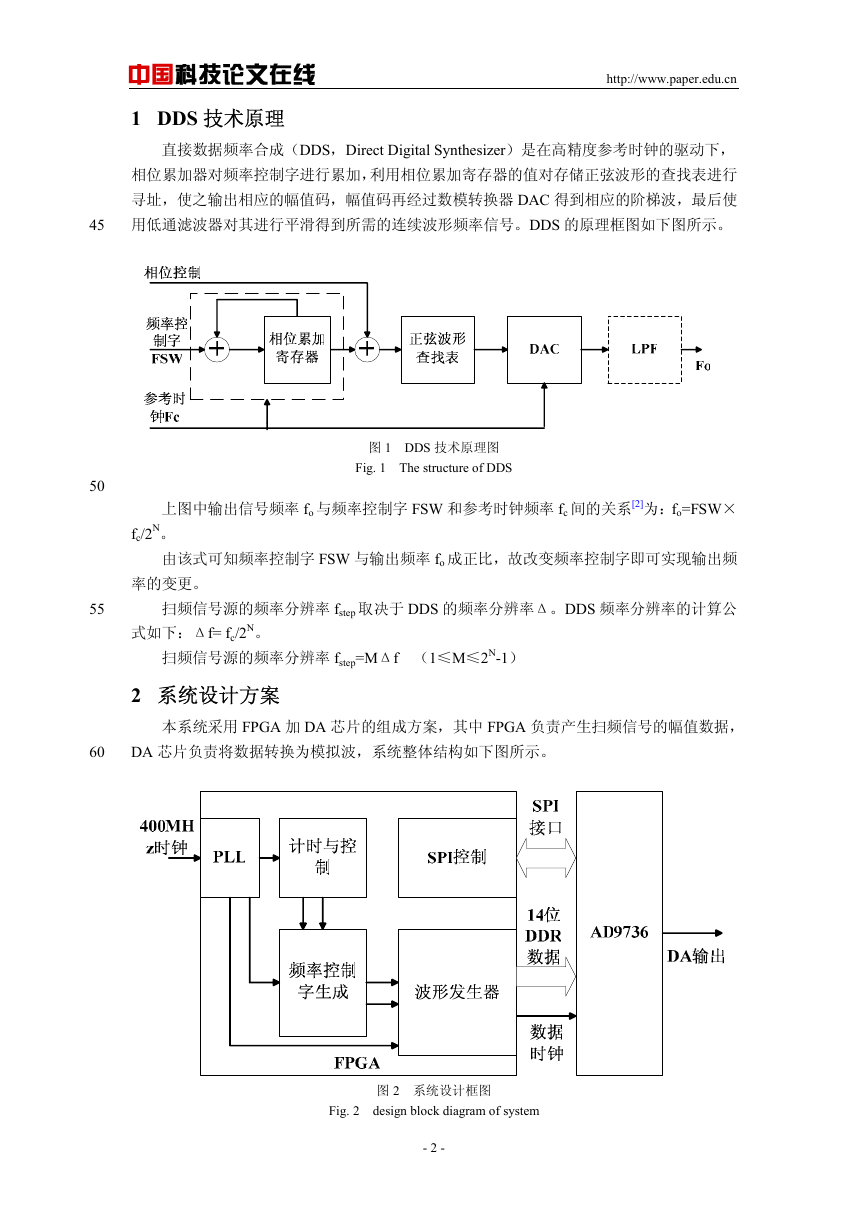

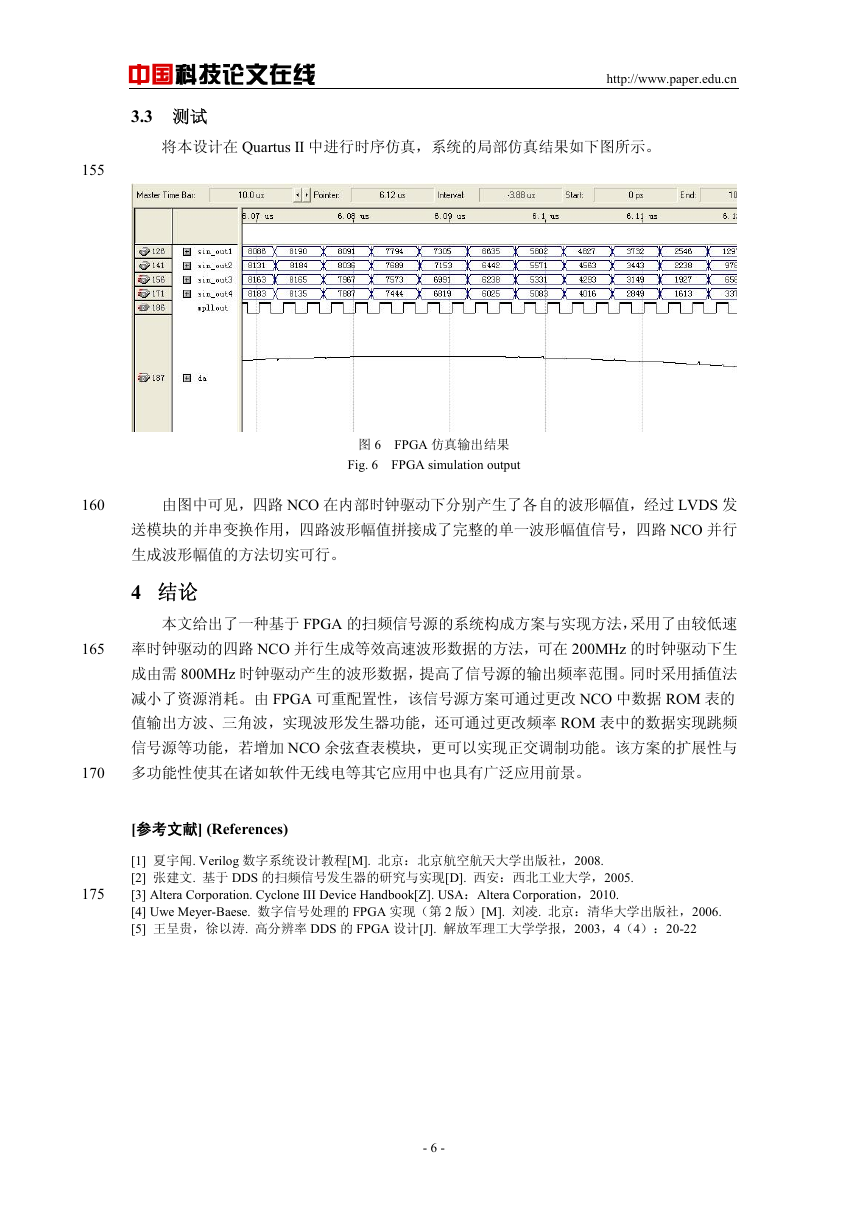

直接数据频率合成(DDS,Direct Digital Synthesizer)是在高精度参考时钟的驱动下,

相位累加器对频率控制字进行累加,利用相位累加寄存器的值对存储正弦波形的查找表进行

寻址,使之输出相应的幅值码,幅值码再经过数模转换器 DAC 得到相应的阶梯波,最后使

用低通滤波器对其进行平滑得到所需的连续波形频率信号。DDS 的原理框图如下图所示。

45

50

图 1 DDS 技术原理图

Fig. 1 The structure of DDS

上图中输出信号频率 fo 与频率控制字 FSW 和参考时钟频率 fc 间的关系[2]为:fo=FSW×

fc/2N。

由该式可知频率控制字 FSW 与输出频率 fo 成正比,故改变频率控制字即可实现输出频

率的变更。

55

扫频信号源的频率分辨率 fstep 取决于 DDS 的频率分辨率Δ。DDS 频率分辨率的计算公

式如下:Δf= fc/2N。

扫频信号源的频率分辨率 fstep=MΔf (1≤M≤2N-1)

2 系统设计方案

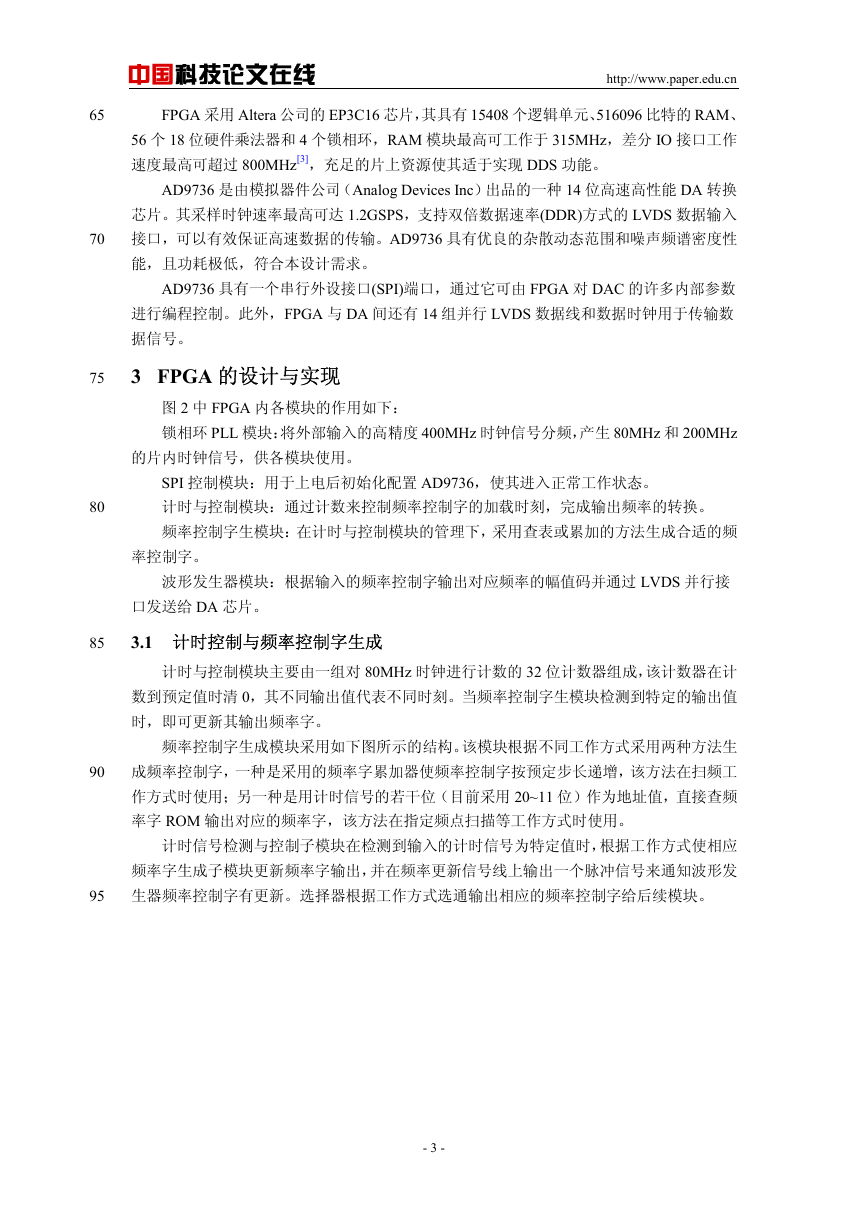

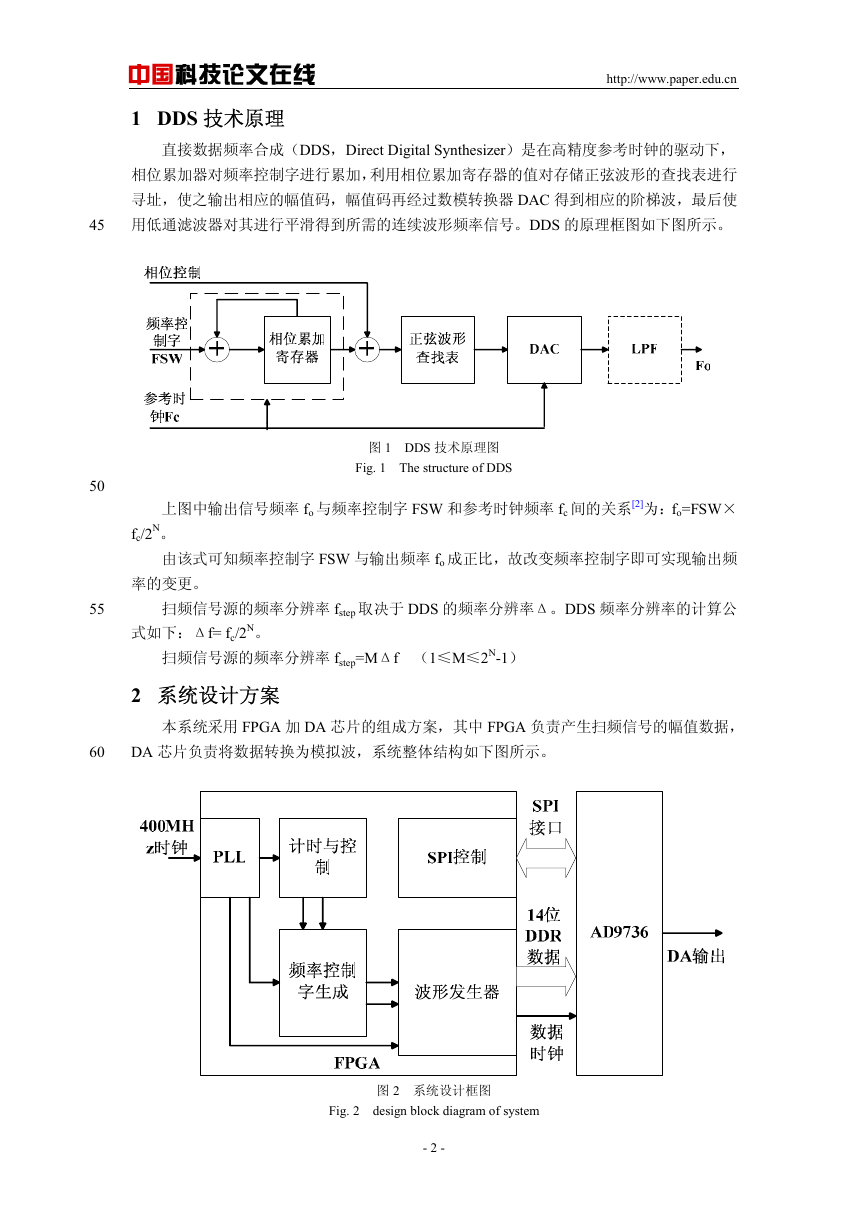

本系统采用 FPGA 加 DA 芯片的组成方案,其中 FPGA 负责产生扫频信号的幅值数据,

60

DA 芯片负责将数据转换为模拟波,系统整体结构如下图所示。

图 2 系统设计框图

Fig. 2 design block diagram of system

- 2 -

�

中国科技论文在线

http://www.paper.edu.cn

65

70

75

80

FPGA 采用 Altera 公司的 EP3C16 芯片,其具有 15408 个逻辑单元、516096 比特的 RAM、

56 个 18 位硬件乘法器和 4 个锁相环,RAM 模块最高可工作于 315MHz,差分 IO 接口工作

速度最高可超过 800MHz[3],充足的片上资源使其适于实现 DDS 功能。

AD9736 是由模拟器件公司(Analog Devices Inc)出品的一种 14 位高速高性能 DA 转换

芯片。其采样时钟速率最高可达 1.2GSPS,支持双倍数据速率(DDR)方式的 LVDS 数据输入

接口,可以有效保证高速数据的传输。AD9736 具有优良的杂散动态范围和噪声频谱密度性

能,且功耗极低,符合本设计需求。

AD9736 具有一个串行外设接口(SPI)端口,通过它可由 FPGA 对 DAC 的许多内部参数

进行编程控制。此外,FPGA 与 DA 间还有 14 组并行 LVDS 数据线和数据时钟用于传输数

据信号。

3 FPGA 的设计与实现

图 2 中 FPGA 内各模块的作用如下:

锁相环 PLL 模块:将外部输入的高精度 400MHz 时钟信号分频,产生 80MHz 和 200MHz

的片内时钟信号,供各模块使用。

SPI 控制模块:用于上电后初始化配置 AD9736,使其进入正常工作状态。

计时与控制模块:通过计数来控制频率控制字的加载时刻,完成输出频率的转换。

频率控制字生模块:在计时与控制模块的管理下,采用查表或累加的方法生成合适的频

率控制字。

波形发生器模块:根据输入的频率控制字输出对应频率的幅值码并通过 LVDS 并行接

口发送给 DA 芯片。

3.1 计时控制与频率控制字生成

85

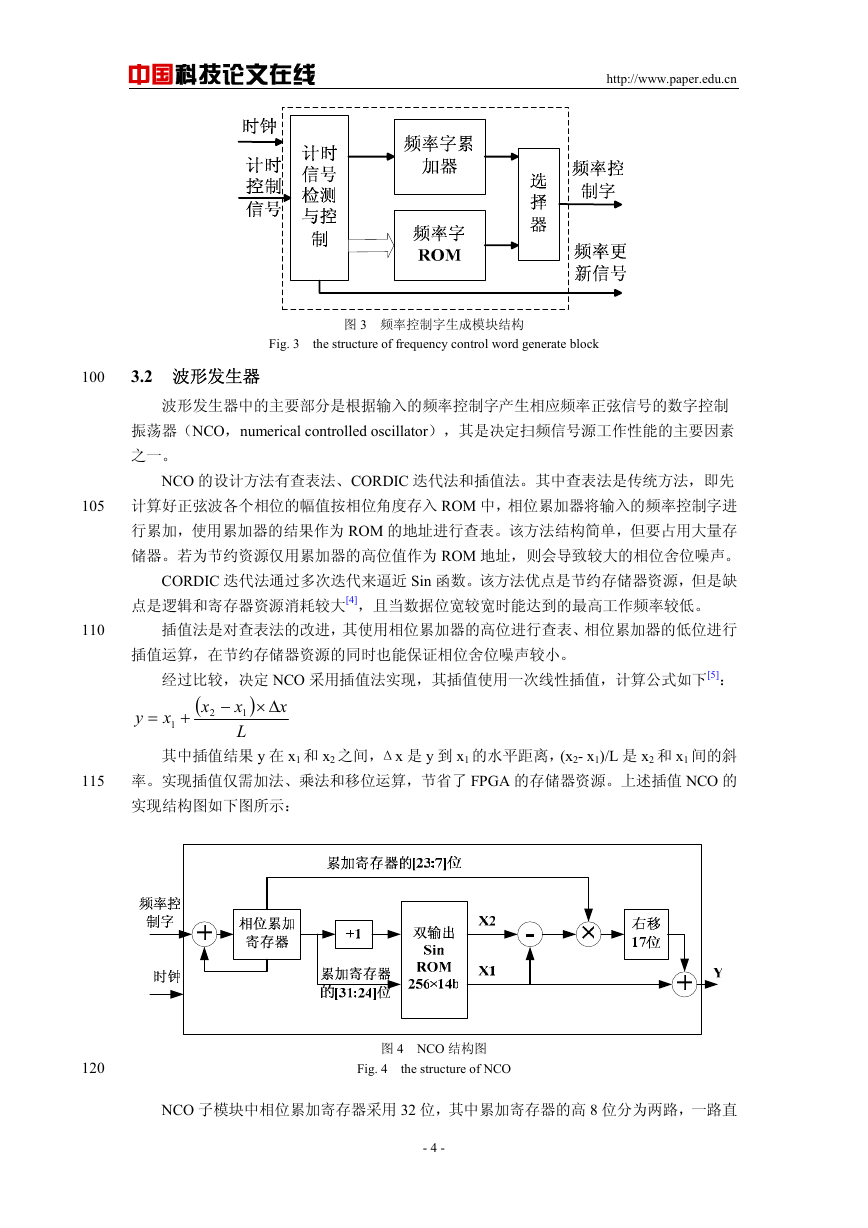

计时与控制模块主要由一组对 80MHz 时钟进行计数的 32 位计数器组成,该计数器在计

数到预定值时清 0,其不同输出值代表不同时刻。当频率控制字生模块检测到特定的输出值

时,即可更新其输出频率字。

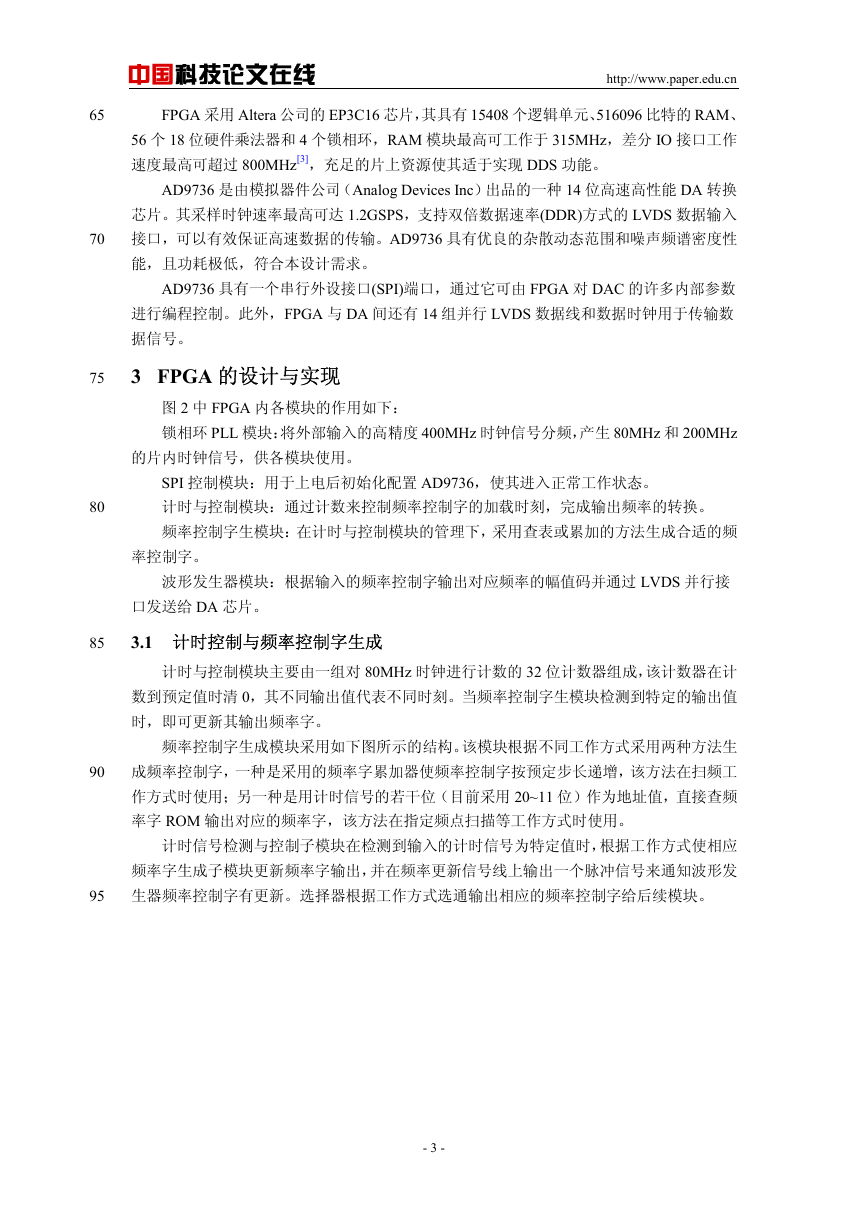

频率控制字生成模块采用如下图所示的结构。该模块根据不同工作方式采用两种方法生

90

成频率控制字,一种是采用的频率字累加器使频率控制字按预定步长递增,该方法在扫频工

作方式时使用;另一种是用计时信号的若干位(目前采用 20~11 位)作为地址值,直接查频

率字 ROM 输出对应的频率字,该方法在指定频点扫描等工作方式时使用。

计时信号检测与控制子模块在检测到输入的计时信号为特定值时,根据工作方式使相应

频率字生成子模块更新频率字输出,并在频率更新信号线上输出一个脉冲信号来通知波形发

生器频率控制字有更新。选择器根据工作方式选通输出相应的频率控制字给后续模块。

95

- 3 -

�

中国科技论文在线

http://www.paper.edu.cn

图 3 频率控制字生成模块结构

Fig. 3 the structure of frequency control word generate block

100

3.2 波形发生器

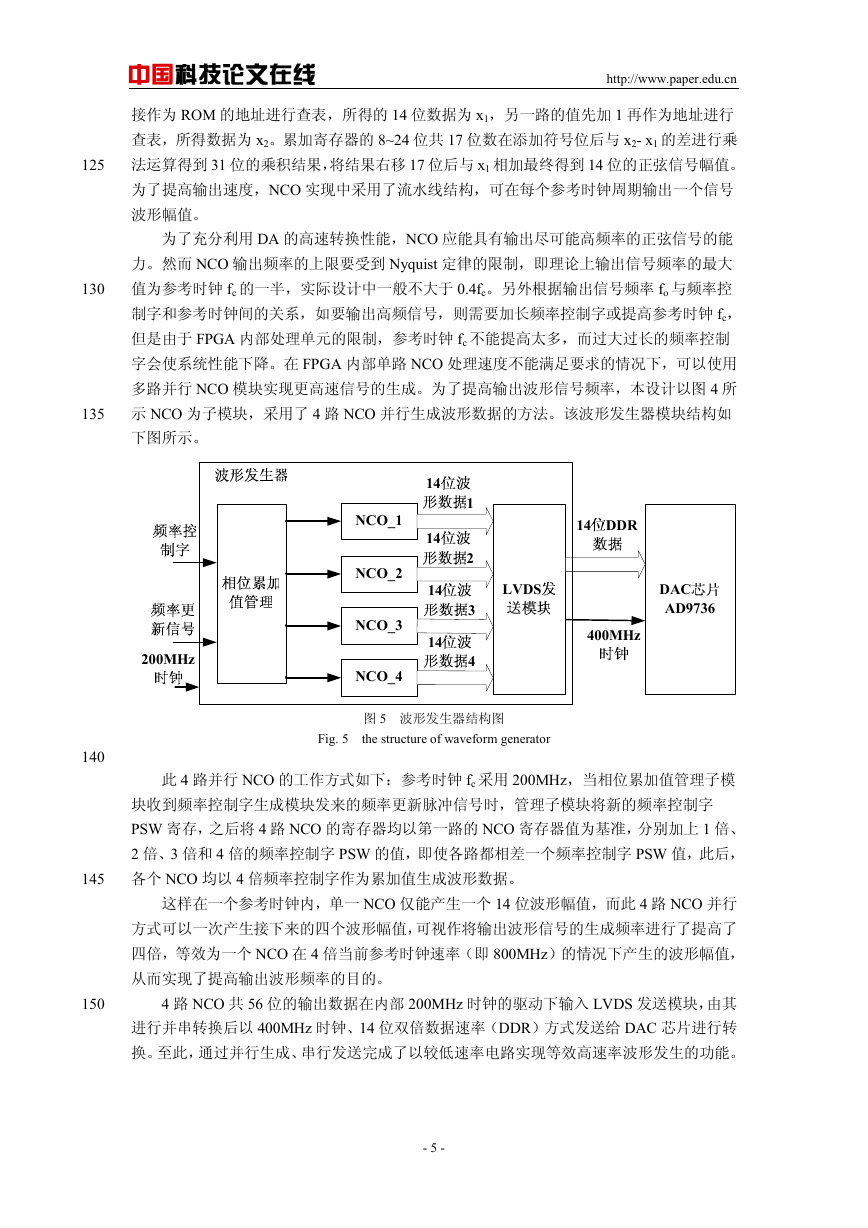

波形发生器中的主要部分是根据输入的频率控制字产生相应频率正弦信号的数字控制

振荡器(NCO,numerical controlled oscillator),其是决定扫频信号源工作性能的主要因素

之一。

NCO 的设计方法有查表法、CORDIC 迭代法和插值法。其中查表法是传统方法,即先

计算好正弦波各个相位的幅值按相位角度存入 ROM 中,相位累加器将输入的频率控制字进

行累加,使用累加器的结果作为 ROM 的地址进行查表。该方法结构简单,但要占用大量存

储器。若为节约资源仅用累加器的高位值作为 ROM 地址,则会导致较大的相位舍位噪声。

CORDIC 迭代法通过多次迭代来逼近 Sin 函数。该方法优点是节约存储器资源,但是缺

点是逻辑和寄存器资源消耗较大[4],且当数据位宽较宽时能达到的最高工作频率较低。

插值法是对查表法的改进,其使用相位累加器的高位进行查表、相位累加器的低位进行

插值运算,在节约存储器资源的同时也能保证相位舍位噪声较小。

经过比较,决定 NCO 采用插值法实现,其插值使用一次线性插值,计算公式如下[5]:

y

=

x

1

+

)

∆×

x

(

x

2

−

x

1

L

其中插值结果 y 在 x1 和 x2 之间,Δx 是 y 到 x1 的水平距离,(x2- x1)/L 是 x2 和 x1 间的斜

率。实现插值仅需加法、乘法和移位运算,节省了 FPGA 的存储器资源。上述插值 NCO 的

实现结构图如下图所示:

图 4 NCO 结构图

Fig. 4 the structure of NCO

NCO 子模块中相位累加寄存器采用 32 位,其中累加寄存器的高 8 位分为两路,一路直

- 4 -

105

110

115

120

�

中国科技论文在线

http://www.paper.edu.cn

接作为 ROM 的地址进行查表,所得的 14 位数据为 x1,另一路的值先加 1 再作为地址进行

查表,所得数据为 x2。累加寄存器的 8~24 位共 17 位数在添加符号位后与 x2- x1 的差进行乘

法运算得到 31 位的乘积结果,将结果右移 17 位后与 x1 相加最终得到 14 位的正弦信号幅值。

为了提高输出速度,NCO 实现中采用了流水线结构,可在每个参考时钟周期输出一个信号

波形幅值。

为了充分利用 DA 的高速转换性能,NCO 应能具有输出尽可能高频率的正弦信号的能

力。然而 NCO 输出频率的上限要受到 Nyquist 定律的限制,即理论上输出信号频率的最大

值为参考时钟 fc 的一半,实际设计中一般不大于 0.4fc。另外根据输出信号频率 fo 与频率控

制字和参考时钟间的关系,如要输出高频信号,则需要加长频率控制字或提高参考时钟 fc,

但是由于 FPGA 内部处理单元的限制,参考时钟 fc 不能提高太多,而过大过长的频率控制

字会使系统性能下降。在 FPGA 内部单路 NCO 处理速度不能满足要求的情况下,可以使用

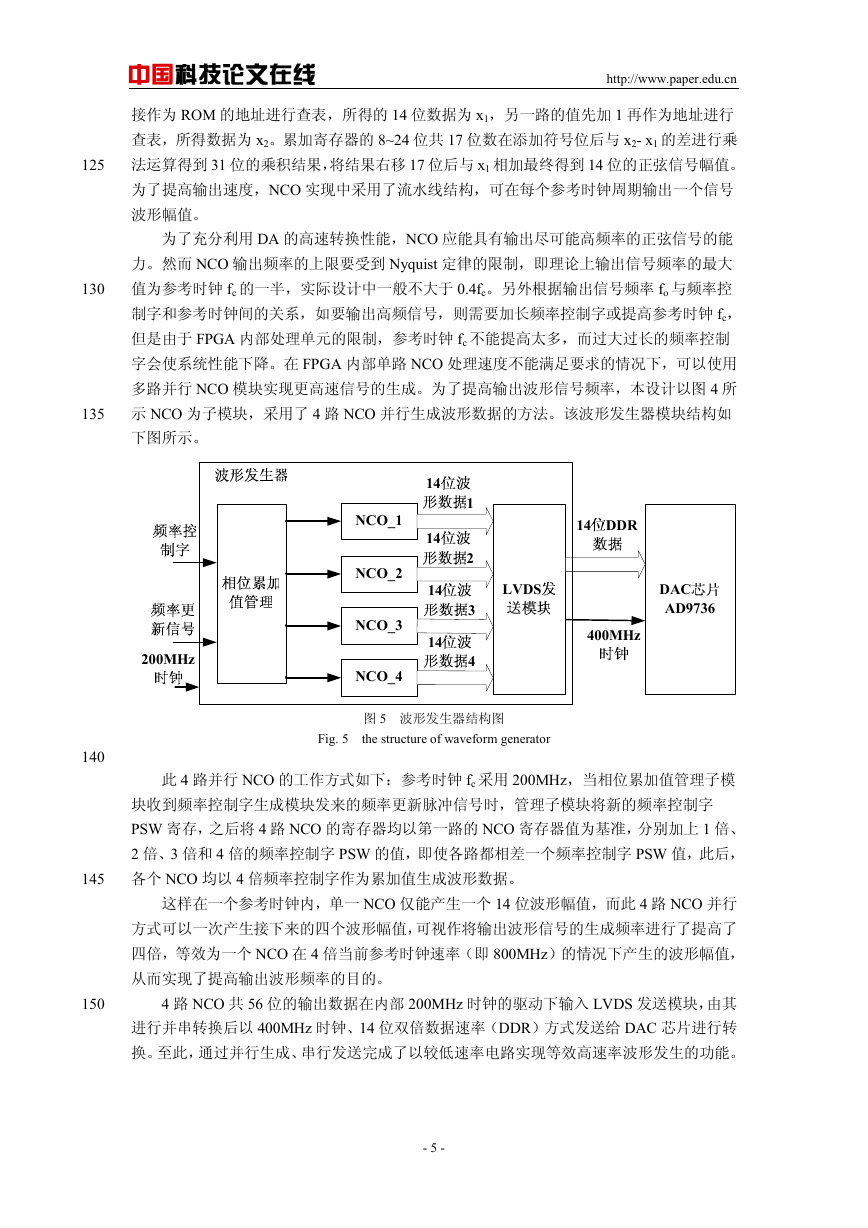

多路并行 NCO 模块实现更高速信号的生成。为了提高输出波形信号频率,本设计以图 4 所

示 NCO 为子模块,采用了 4 路 NCO 并行生成波形数据的方法。该波形发生器模块结构如

下图所示。

14

14

14

14

1

2

3

4

NCO_1

NCO_2

NCO_3

NCO_4

14 DDR

LVDS

DAC

AD9736

400MHz

200MHz

图 5 波形发生器结构图

Fig. 5 the structure of waveform generator

此 4 路并行 NCO 的工作方式如下:参考时钟 fc 采用 200MHz,当相位累加值管理子模

块收到频率控制字生成模块发来的频率更新脉冲信号时,管理子模块将新的频率控制字

PSW 寄存,之后将 4 路 NCO 的寄存器均以第一路的 NCO 寄存器值为基准,分别加上 1 倍、

2 倍、3 倍和 4 倍的频率控制字 PSW 的值,即使各路都相差一个频率控制字 PSW 值,此后,

各个 NCO 均以 4 倍频率控制字作为累加值生成波形数据。

这样在一个参考时钟内,单一 NCO 仅能产生一个 14 位波形幅值,而此 4 路 NCO 并行

方式可以一次产生接下来的四个波形幅值,可视作将输出波形信号的生成频率进行了提高了

四倍,等效为一个 NCO 在 4 倍当前参考时钟速率(即 800MHz)的情况下产生的波形幅值,

从而实现了提高输出波形频率的目的。

4 路 NCO 共 56 位的输出数据在内部 200MHz 时钟的驱动下输入 LVDS 发送模块,由其

进行并串转换后以 400MHz 时钟、14 位双倍数据速率(DDR)方式发送给 DAC 芯片进行转

换。至此,通过并行生成、串行发送完成了以较低速率电路实现等效高速率波形发生的功能。

125

130

135

140

145

150

- 5 -

�

中国科技论文在线

3.3 测试

http://www.paper.edu.cn

155

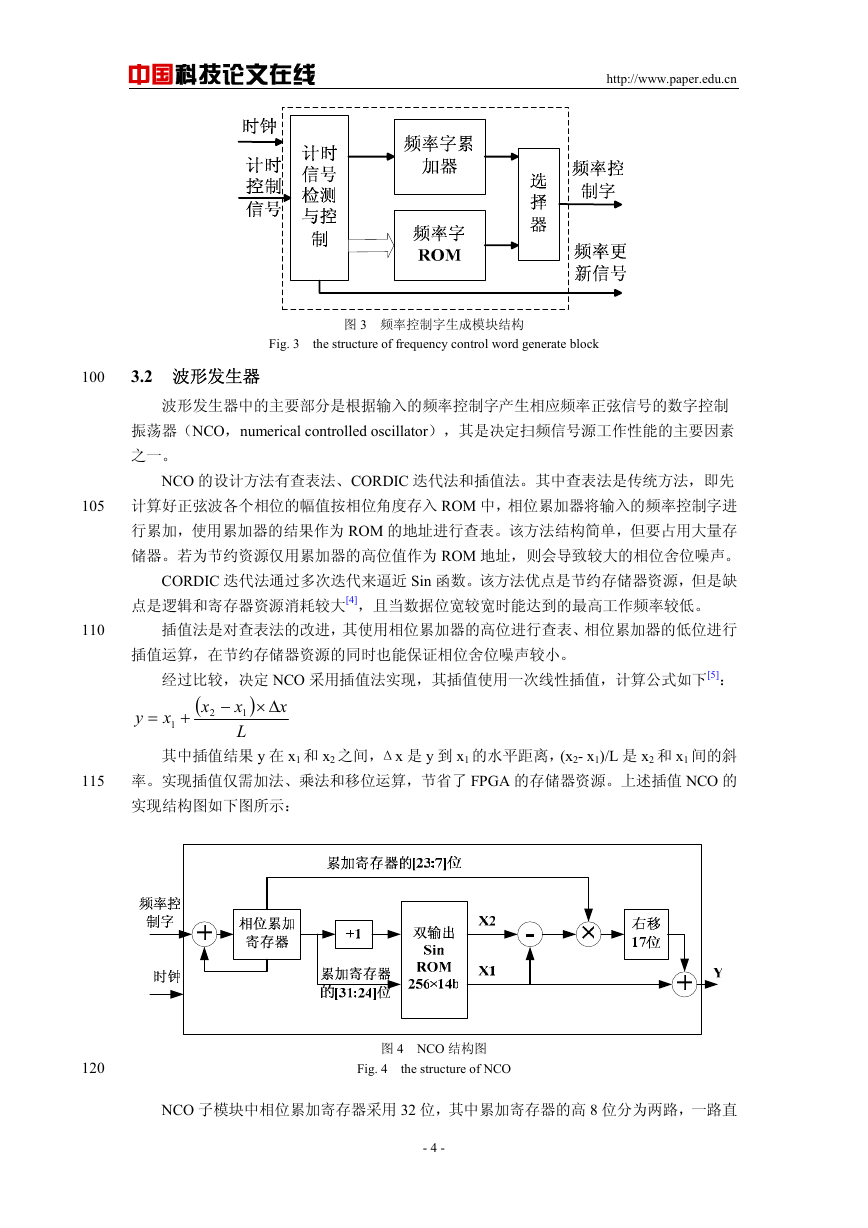

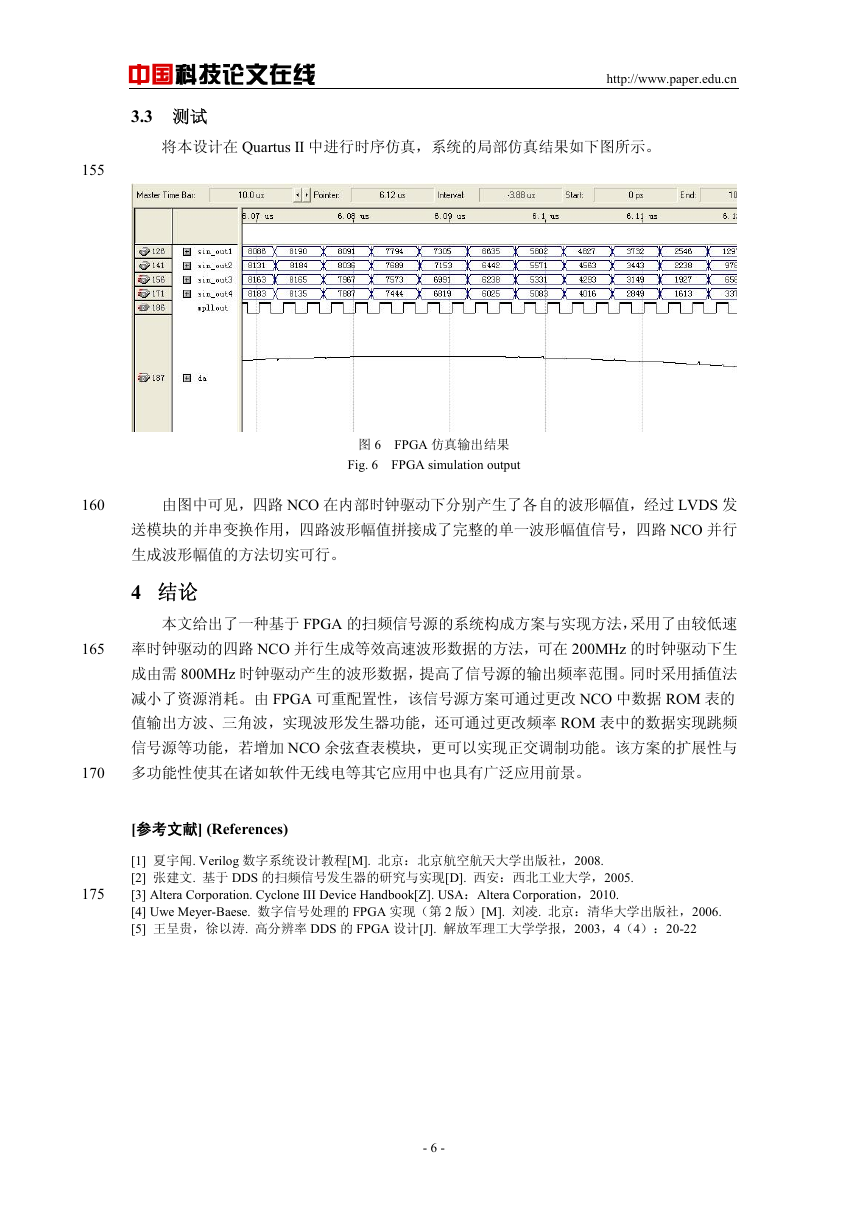

将本设计在 Quartus II 中进行时序仿真,系统的局部仿真结果如下图所示。

图 6 FPGA 仿真输出结果

Fig. 6 FPGA simulation output

160

165

170

175

由图中可见,四路 NCO 在内部时钟驱动下分别产生了各自的波形幅值,经过 LVDS 发

送模块的并串变换作用,四路波形幅值拼接成了完整的单一波形幅值信号,四路 NCO 并行

生成波形幅值的方法切实可行。

4 结论

本文给出了一种基于 FPGA 的扫频信号源的系统构成方案与实现方法,采用了由较低速

率时钟驱动的四路 NCO 并行生成等效高速波形数据的方法,可在 200MHz 的时钟驱动下生

成由需 800MHz 时钟驱动产生的波形数据,提高了信号源的输出频率范围。同时采用插值法

减小了资源消耗。由 FPGA 可重配置性,该信号源方案可通过更改 NCO 中数据 ROM 表的

值输出方波、三角波,实现波形发生器功能,还可通过更改频率 ROM 表中的数据实现跳频

信号源等功能,若增加 NCO 余弦查表模块,更可以实现正交调制功能。该方案的扩展性与

多功能性使其在诸如软件无线电等其它应用中也具有广泛应用前景。

[参考文献] (References)

[1] 夏宇闻. Verilog 数字系统设计教程[M]. 北京:北京航空航天大学出版社,2008.

[2] 张建文. 基于 DDS 的扫频信号发生器的研究与实现[D]. 西安:西北工业大学,2005.

[3] Altera Corporation. Cyclone III Device Handbook[Z]. USA:Altera Corporation,2010.

[4] Uwe Meyer-Baese. 数字信号处理的 FPGA 实现(第 2 版)[M]. 刘凌. 北京:清华大学出版社,2006.

[5] 王呈贵,徐以涛. 高分辨率 DDS 的 FPGA 设计[J]. 解放军理工大学学报,2003,4(4):20-22

- 6 -

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc