SATA协议分析及其FPGA实现摘要并行总线PATA从设计至今已快20年历史,如今它的缺陷已经严重阻碍了系统性能的进一步提高,己被串行ATA(serialATA)即SATA总线所取代。SATA作为新一代磁盘接口总线,采用点对点方式进行数据传输,内置数据/命令校验单元,支持热插拔,具有150MB/s(SATA1.0)或300MB/s(SATA2.0)的传输速度。目前SATA已在存储领域广泛应用,但国内尚无独立研发的面向FPGA的SATAIPCORE,在这样的条件下设计面向FPGA应用的SATAIPCORE具有重要的意义。本论文对协议进行了详细的分析,建立了SATAIPCORE的层次结构,将设备端SATAIPCORE划分成应用层、传输层、链路层和物理层;介绍了实现该IPCORE所选择的开发工具、开发语言和所选用的芯片;在此基础上着重阐述协议IPCORE的设计,并对各个部分的设计予以分别阐述,并编码实现;最后进行综合和测试。采用FPGA集成硬核RocketIOMGT(RocketIOMulti—GigabitTransceiver)实现了1.5Gbps的串行传输链路;设计满足协议需求、适合FPGA设计的并行结构,实现了多状态机的协同工作:在高速设计中,使用了流水线方法进行并行设计,以提高速度,考虑到系统不同部分复杂度的不同,设计采用部分流水线结构;采用在线逻辑分析仪Chipscopepro与SATA总线分析仪进行片上调试与测试,使得调试工作方便快捷、测试数据准确;严格按照SATA1.0a协议实现了SATA设备端IPCORE的设计。最终测试数据表明,本论文设计的基于FPGA的SATAIPCORE满足协议需求。设计中的SATAIPCORE具有使用方便、集成度高、成本低等优点,在固态电子硬盘SSD(Solid.StateDisk)开发中应用本设计,将使开发变得方便快捷,更能够适应市场需求。关键词:串行ATA:现场可编程门阵列;吉比特收发器;IP核�

硕十学位论文AbstractTheParallelA1、AProtocolhasalreadybeenusedondiskinterf.aceforthepaSttwent)ryears.Nowadaystheprotocol’sdmwbacklimitsthesystem’spe面肿a11ce,andwillbereplacedbytheSerialArA(SATA).Asahighspeedyserialbus,SATAincludesthepointt0pointn.狮sf-ermode,embeddeddataandcoⅡⅡnandscheckingunit,supponhotplug.Theband嘶dthis150MBpersecond(SATAVerSion1.0a)or300MBpersecond(SAI'Aversion2.O).TheproductsbaSedonSATAareused掣eatlynoW,mostofwhichareprovidedbytheothercountries.AndnoSA队IPCOREf.orFPGAisdeVelopedindependentlyinchina.Soit’ssignificanttodesignaSAlAIPCORE.ThispaperfirstlyanalyzestheSAlrAprotocol,锄ddeVelopsthelayermodelofSAl’Aadapter.111e1ayermodelcontajnsapplication1ayer,tI彻sponlayer,linklayeraIldphysicallayer.ToaccompliShtllePCORE,“introducesthedesiglllanguage,desigIltoolsaIldselectedchip.A耐itexplainedmewholeIPCOREindetail,w11ichincludesallthemodulesseparately.AtlaSt,itfinished出lmestepsincludiI培codec,synthesisaIldtest.111emesisdesig璐the1.5Gbpsdi脏rentialserialsigIlaIco皿nunicationch籼elbasedonRocketIOMGT.Anditaccomplishesmultiplestatemachinecooperationdesignusingparallelstmcture.Toimpr0Vetllespeed,itutilizesmepipeline锄ddesi驴parallelinllighspeedydesign.ConsideringtIlef.aCtthatdifI’erentpartshaVedifrerentcomplexity,tlledesignusesdi虢rentpipelines.ByCmpscopepr0龇ldSATAbus锄alyzers,thedebuggingprocessbecomef弧terandmoreaccurate.ItachievestheSATAIPCOREbaSedontheSAlA1.0aprotoc01.Fimllytlletestdataindicatesmatmedes咖ml舢stheprotocol’srequirements.TheSATAIPCOI也islli曲lyintegrated锄dlowcost.ItenablesthedeVelopmentofsolid-s龇diskmoreconvenient.KeyWords:SerialA队;FieldProgr{umnableGateAJTay;ROCl

湖南大学学位论文原创性声明本人郑重声明:所呈交的论文是本人在导师的指导下独立进行研究所取得的研究成果。除了文中特别加以标注引用的内容外,本论文不包含任何其他个人或集体已经发表或撰写的成果作品。对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式标明。本人完全意识到本声明的法律后果由本人承担。作者签名:铯杰、学位论文版权使用授权书本学位论文作者完全了解学校有关保留、使用学位论文的规定,同意学校保留并向国家有关部门或机构送交论文的复印件和电子版,允许论文被查阅和借阅。本人授权湖南大学可以将本学位论文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本学位论文。本学位论文属于l、保密口,在年解密后适用本授权书。2、不保密团。(请在以上相应方框内打“√”)作者签名:导师签名:蒙私i溶黜烨多醐:渐伽引日�

硕卜学位论文第1章绪论随着Xilinx、Altera这些公司大力推动FPGA的市场化,以及可编程片上系统概念的提出,围绕着面向FPGA平台的IPCOER设计成为了当今的热门;串行ATA协议的公布使得硬盘行业发生了巨大的改革,各大公司不断加大这方面的设计投入。本章首先介绍了本文的研究背景、意义,以及国内外的相关研究状况,然后概括了本文的主要工作和论文组织安排。1.1课题背景和意义计算机存储技术在计算机发展中始终是一个关键技术。其技术特性决定了计算机的数据存储性能,进而决定了计算机的整体性能以及应用环境。从根本上来说,无论是现在还是将来,存储技术都将制约着计算机技术的应用与发展【ll,尤其在高速数据存储领域。近年来随着各种高速数据传输的广泛应用,高性能存储技术之争也愈演愈烈。如今,串行技术已成为计算机总线的主导技术,无论是系统总线、芯片互联与磁盘接口,还是诸如USB、IEEEl394等外部总线,无一例外都引入了串行技术提高性能,SATA(SerialAdvancedTechnologyAttachment)即为新一代串行磁盘接口总线。在过去的十几年,PATA(ParallelAdvancedTechnologyAttachment)总线取得了非常大的成功,它的并行总线执行机制现在看来依然具有很高的性能,但其带宽却早已显出疲态【21。新一代串行存储总线SATA带着强捍的生命力应运而生,SATA1.0传输速率为150MB/s,现在正在研究开发的SATA3.0传输速率更达到了600MB/s【31。SATA总线采用点对点连接拓扑,每个通道独立工作,不必共享接口带宽,并使用了嵌入式时钟信号,增加了32位CRC错误校验,具备了比以往更强的检错能力。目前在PC芯片组中,SATA接口已基本取代了传统的PATA磁盘接口,在阵列存储领域,SATARAID扩展卡也应用广泛。但是,现在市场上的SATA芯片基本上都是由国外的少数大厂商设计制造的,国内的SATA相关产品也都是在国外厂商提供的芯片上进行二次开发而成的。但是近两年由于存储领域的革命性变革,即存储介质采用FLASH成为可能,伴随固态电子硬盘SSD(SolidStateDisk)即将取代传统机械磁盘的趋势,国内外众多公司都加大了研发力度,引发了向存储领域进军的热潮。笔者有幸参与了严格按照SATA1.0a规范设计的固态电子硬盘开发,主要负责工作是SATA协议的FPGA设计。设计中的SATAIPCORE具有使用方便、集成度高、成本低等优点,�

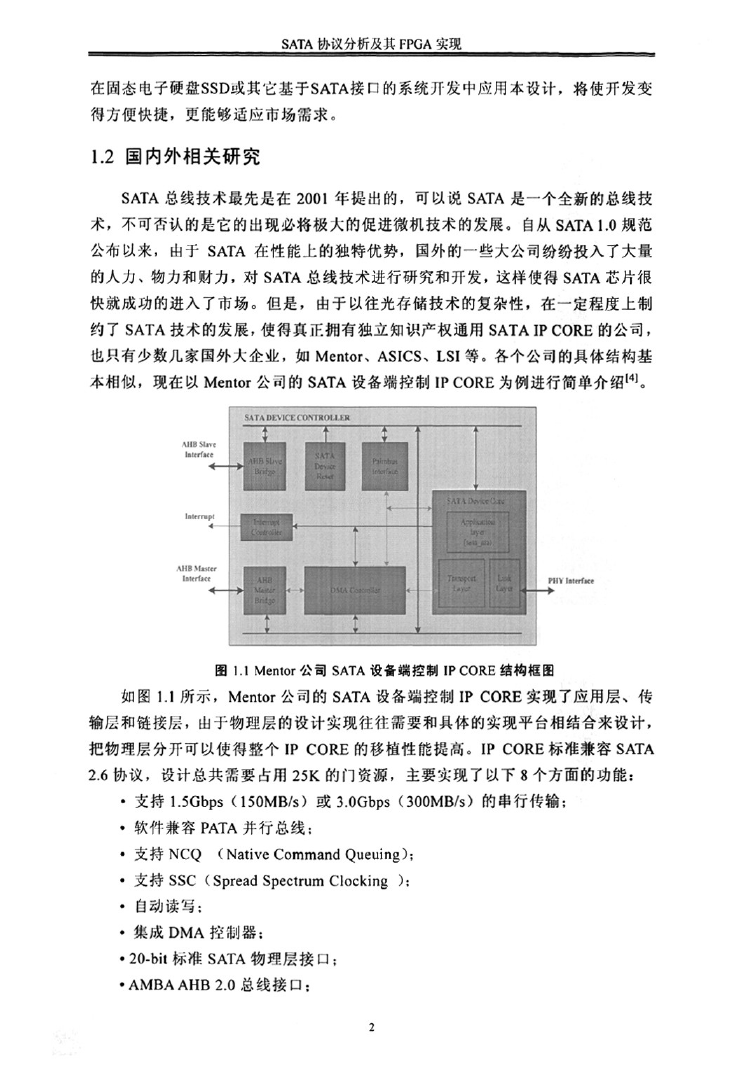

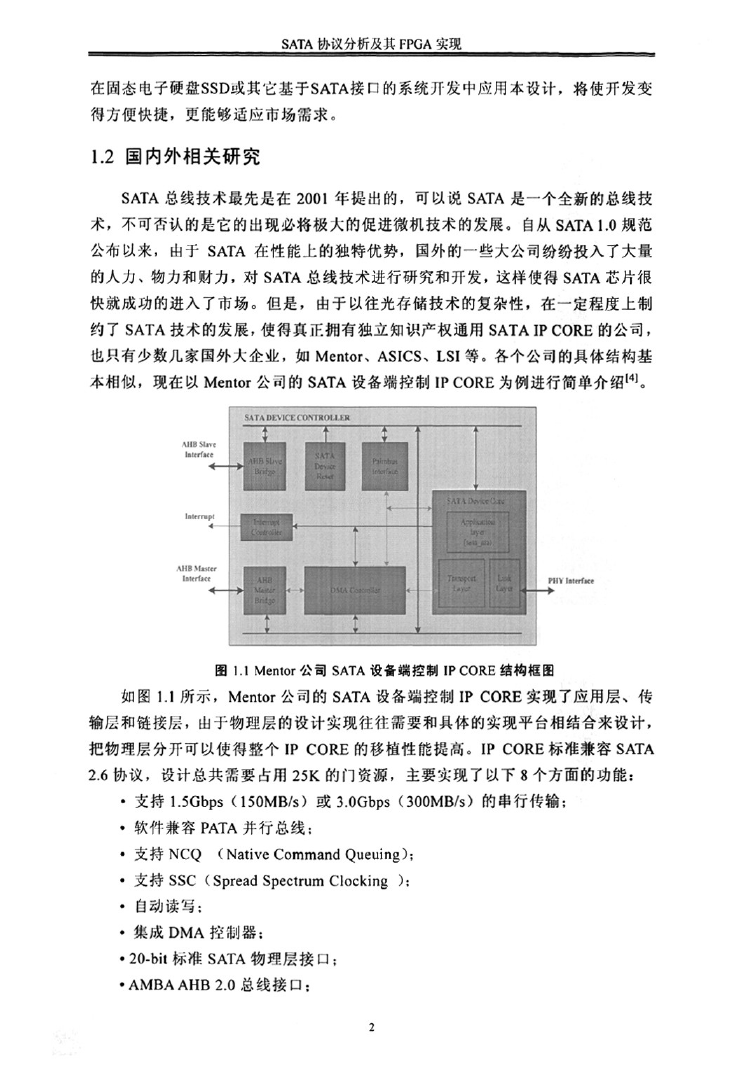

sATA协议分析成其FPGA实现在固卷电子硬盘ssD或其它基于sAlA接n的系统丌发中应用本设计,将使丌发变褂方便快捷.更能够通应市场需求。1.2国内外相关研究sAlA总线技术最先是在2001年提出的,可以i兑sA’rA是一个全新的总线技术,不可沓认的是它的出现必将极人的促进微机技术的发展。自从sAlAlO规范公柿咀束,由于sATA在性能上的独特优势,国外的一些大公司纷纷投入了大量的人力、物力和财力,对sAlIA总线技术进行研究和开发,这样使得sAlA芯片很快就成功的进入了市场。但是.由于以往光存储技术的复杂性,在一定程度上制约了sATA技术的发展,使得真正拥有独立知识产权通用sA丁AIPcORE的公司.也H有少数几家同外大企业,如Mentor、ASIcS、LSI等。各个公司的具体结构基奉相似.现在以Mentor公司的sAlA设备端控制IPcORE为倒进行简单介绍…。圈¨Menlor公司sAT^设备端控糍lPcORE结构框田如图11所示,Mentor公司的sAlA设备端控制IPcORE实现了应用层、传输层和链接增.由于物理层的设计实现往往需要和具体的,实现平台相结合来设计,把物理层分开可以使得整个lPc0RE的移植性能提高。IPcORE标准兼容s^TA26协议,设计总共需要占用25K的门资源,主要实现了以下8个方面的功能:·支持l5Gbps(150MB,s)或30Gbps(300MB/s)的串行传输:·软件燕容Ⅳ汀A并行总线:·支持NcQ(NativecommandQueui“g);·支持ssc(spreadspectrumcIocki“g):·D动读写:·集成DMA控制器;·20_bit标准sAl’A物珲层接u;·AMBAAHB20总线接口:�

硕十学位论文近两年来固态电子硬盘SSD成为磁盘发展趋势,引发了众多公司对存储领域进军的热潮,国内一些公司由于在这方面起步比较晚,目前还没有比较成熟的商用SATAIPCORE,各方面的技术都处在一个研究开发阶段。国内正在进行SAlrA产品的公司主要有忆正、朗科、源科等。1.3课题主要工作本课题的主要工作如下:(1)了解过去和当今计算机存储领域的发展状况,分析比较了PATA及SATA总线,说明了SATA总线体系的优点和发展趋势;(2)研究了千兆高速串行通信设计,采用XilinxRocketIOMGT实现SATA物理层高速串行链接;(3)研究了SATA协议架构。在深入分析协议各层功能与状态变迁的前提下,对各模块进行了设计与验证;(4)应用本设计,采用MicroBlaze对命令执行解析,以NANDFLASH作为数据储存,验证设计SATAIPCORE的正确性。最终将设计应用于固态电子硬盘SSD产品开发中;本论文有以下一些创新思想:(1)针对协议中不同协议层的要求,在满足速度的情况下减少资源的使用,使得速度和面积得以平衡;(2)在系统中的高速部分,采用部分流水线结构与并行结构;(3)采用在线逻辑分析仪Chipscope与SATA总线分析仪进行片上调试与测试,使得调试工作方便快捷、测试数据准确。1.4论文组织安排本文共分为五章:第一章:绪论。介绍课题背景与意义、国内外相关研究状况、课题主要工作及论文组织情况。第二章:SATA1.Oa协议研究分析。主要结合硬盘接口技术的发展现状及趋势,分析比较了ATA及SATA总线,说明了SATA作为一种新型硬盘接口类型,相比较于PATA的特点和优势,并深入地研究了SATA的基本结构框架,对协议各层的工作原理及状态变迁作了详细分析。第三章:SATA协议设计。介绍SAlrAIPCORE的具体设计实现,是本文的主要内容。进行了系统的总体结构设计,分析了设计流程和方法,并严格按照SATA协议基本结构框架,分层详细介绍SATA协议的各主要模块的FPGA设计,主要�

SATA协议分析及其FPGA实现包括高速串行链路的实现、物理层00B状态机、链路层和传输层协议的状态机逻辑实现,以及应用层的命令解析流程。第四章:综合与测试。主要介绍了综合和测试工作。综合部分主要包括约束、结果分析等。测试部分主要包括测试平台、高速串行链路的测试与数据传输测试。数据传输测试采用MicroBlaze执行命令处理,以FLASH作为存储介质,对设计进行整体功能验证。最后,本文还对工作做了总结,给出了进一步的改进方案以及研究方向,并附上致谢、参考文献及攻读硕士学位期间发表的学术论文情况。4�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc