DC 学习----第一章 基本概念

作者:未知 时间:2010-08-15 15:02:50 来自:网络转载

1.1 启动文件

启动文件用来指定综合工具所需要的一些初始化信息。DC 使用名为“.synopsys_dc.setup”的启动文

件,启动时,DC 会以下述顺序搜索并装载相应目录下的启动文件:

1)、DC 的安装目录;

2)、用户的 home 目录;

3)、当前启动目录。

注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置。

下面是一个 DC 启动文件的实例,它包含了几乎所有重要的设置,下文将结合该实例解释启动文件中各

项设置的具体含义。

例 1-1(一个 DC 启动文件):

search_path= search_path + {“.”, synopsys_root + “/dw/sim_ver” }

search_path= search_path + { “~/risc32/synthesis/libraries” }

target_library={ tcb773stc.db }

synthetic_library={dw_foundation.sldb}

link_library = { “*”, dw_foundation.sldb, tcb773stc.db }

symbol_library = { tcb773s.sdb }

synlib_wait_for_design_license = {"DesignWare-Foundation"}

alias rt “report_timing”

designer= XXXXX

company= “ASIC Lab, Fudan Univ.”

search_path 指定了综合工具的搜索路径。

target_library 为综合的目标库,它一般是由生产线提供的工艺相关的库。

synthetic_library 是综合库,它包含了一些可综合的与工艺无关的 IP。dw_foundation.sldb 是

Synopsys 提供的名为 Design Ware 的综合库,它包含了基本的算术运算逻辑、控制逻辑、可综合存储器等

IP,在综合是调用这些 IP 有助于提高电路性能和减少综合时间。

link_library 是链接库,它是 DC 在解释综合后网表时用来参考的库。一般情况下,它和目标库相同;

当使用综合库时,需要将该综合库加入链接库列表中。

symbol_library 为指定的符号库。

synlib_wait_for_design_license 用来获得 DesignWare-Foudation 的许可(license)。

alias 语句与 UNIX 相似,它定义了命令的简称。

最后的 designer 和 company 项则表明了设计者和所在公司。

另外,在启动文件中用符号 “/*” 和 “*/” 进行注释。

1.2 设计实体

在 DC 中,总共有 8 种设计实体:

设计(Design):一种能完成一定逻辑功能的电路。设计中可以包含下一层的子设计。

单元(Cell):设计中包含的子设计的实例。

参考(Reference):单元的参考对象,即单元是参考的实例。

端口(Port):设计的基本输入输出口。

管脚(Pin):单元的输入输出口。

连线(Net):端口间及管脚间的互连信号。

时钟(Clock):作为时钟信号源的管脚或端口。

�

库(Library):直接与工艺相关的一组单元的集合。

1.3 寻找设计实体

在 DC 中使用 find 命令寻找设计实体,其语法为:

find

<实体类型>

<名称列表>

-hierarchy

<实体类型>:上节所述的 8 种类型

<名称列表>:用来匹配的关键词,其中可带 “*” 统配符

-hierarchy:指令 DC 搜索所有设计层次

例 1-2(find 命令的使用):

find (cell, *U*)

find (net, “*”)

find (design, {A_*, B_*} -hierarchy)

另外,使用 all_inputs()和 all_outputs()可以得到设计所有的输入端口和输出端口。

1.4 编译器指示语句

有时,可以利用 HDL 描述中的一些特定的注释语句来控制综合工具的工作,从而弥补仿真环境和综合

环境之间的差异,这些注释语句称为编译器指示语句(Compiler Directives)。

1.4.1 Verilog 编译器指示语句

1) translate_off/ translate_on

这组语句用来指示 DC 停止翻译 “//synopsys translate_off”之后的 Verilog 描述,直至出现

“//synopsys translate_on”。当 Verilog 代码钟含有供仿真用的不可综合语句时,这项功能能使代码方

便地在仿真工具与综合工具之间移植。

例 1-3(translate_off/ translate_on 指示语句的使用):

//synopsys translate_off

/*仅供仿真用语句

……

*/

//synopsys translate_on

/*可综合语句

……

*/

2) parallel_case/ full_case

DC 可能使用带优先级的结构来综合 Verilog 的 case 语句,为避免这种情况,可以使用“//synopsys

parallel_case”指示 DC 将 case 语句综合为并行的多路选择器结构。

例 1-4(parallel_case 指示语句的使用):

always @ (state)

begin

case (state) //synopsys parallel_case

2’b00: new_state = 2’b01;

2’b01: new_state = 2’b10;

2’b10: new_state = 2’b00;

default: new_state = 2’b00;

�

endcase

end

另外,Verilog 允许 case 语句不覆盖所有可能情况,当这样的代码由 DC 综合时将产生锁存器。为避

免这种情况,可以使用 “//synopsys full_case”指示 DC 所有可能已完全覆盖。

例 1-5(full_case 指示语句的使用):

always @ (sel or a1 or a2)

begin

case (sel) //synopsys full_case

2’b00: z = a1;

2’b01: z = a2;

2’b10: z = a1 & a2;

endcase

end

1.4.2 VHDL 编译器指示语句

1) translate_off/ translate_on

作用同 Verilog,注意需要使用符合 VHDL 语法的注释:

--synopsys translate_off

--synopsys translate_on

也可以使用:

--pragma translate_off

--pragma translate_on

需要注意的是,在 VHDL 中使用了以上编译指示语句后,DC 仍会对 translate_off/on 之间的描述进行

语法检查,若想避免这一点,可以改变以下变量的值:

hdlin_translate_off_skip_text = true

2) synthesis_off/ synthesis_on

其作用和语法均类似于 translate_off 和 translate_on,只是它的作用不受上述变量控制。

DC 学习---第二章 设计入口

作者:未知 时间:2010-08-15 15:04:19 来自:网络转载

2.1 软件的启动

在 UNIX 下执行 dc_shell 即可启动 DC 的命令行界面,执行 design_analyzer& 即可启动相应的图形界

面。启动以后的图形界面如图 2-1 所示。

�

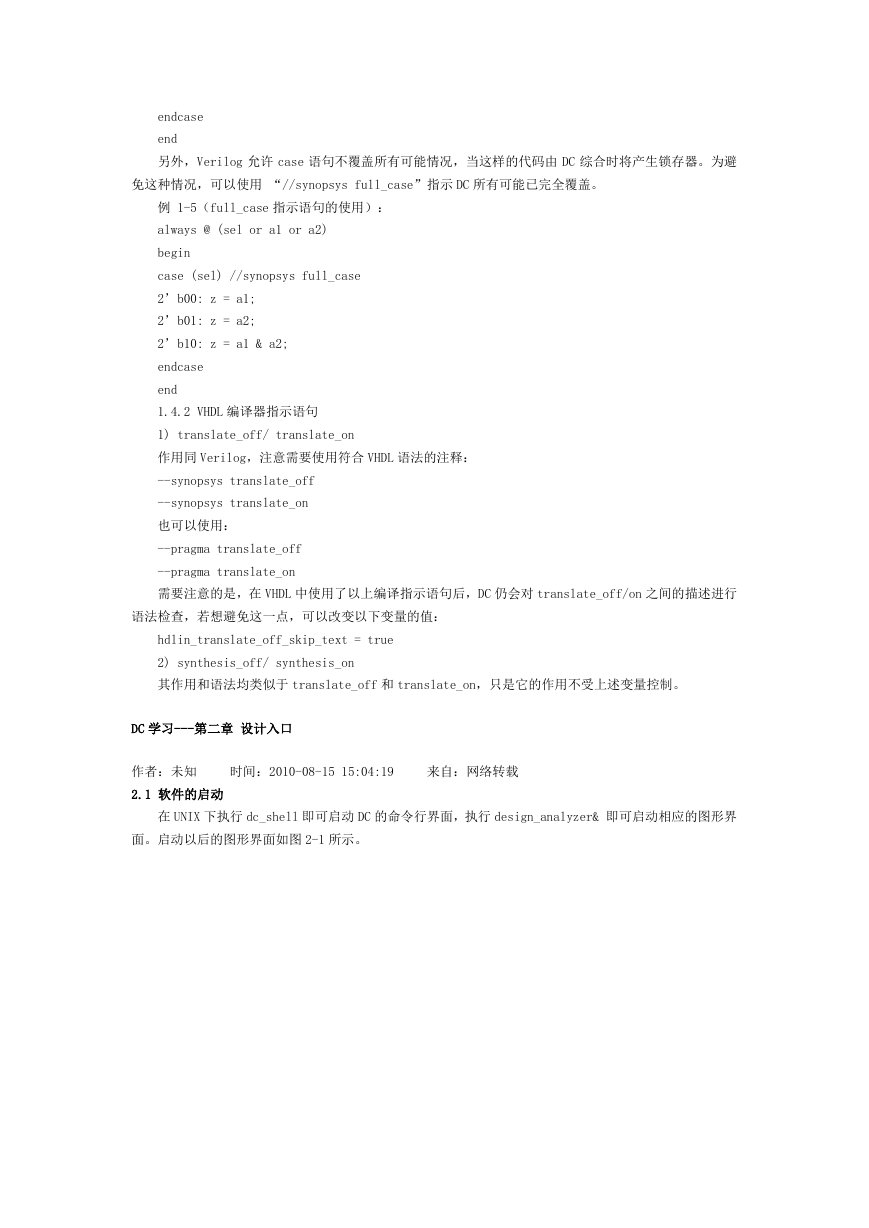

在图形界面中若需要执行命令行,可以用 Setup->Command Window 菜单打开命令行功能,如图 2-2 所

示。

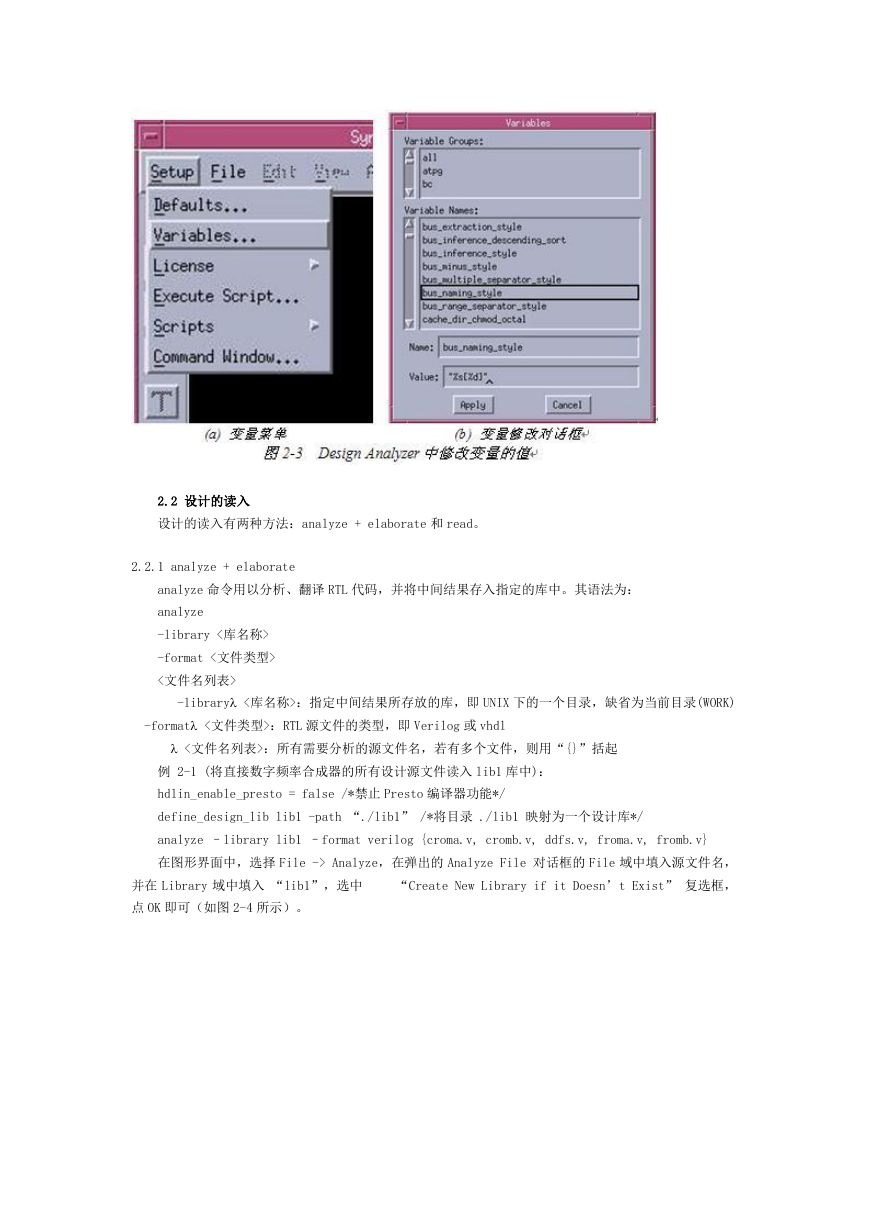

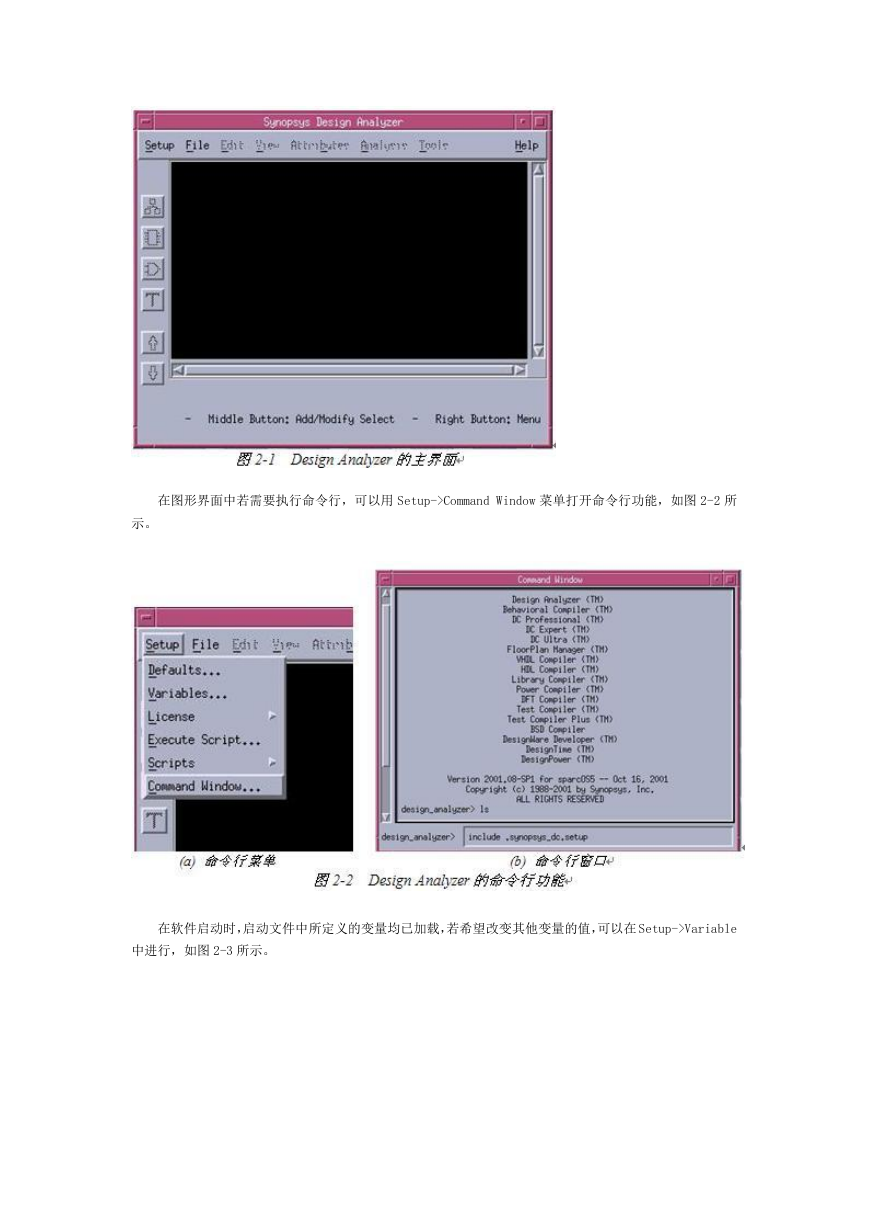

在软件启动时,启动文件中所定义的变量均已加载,若希望改变其他变量的值,可以在 Setup->Variable

中进行,如图 2-3 所示。

�

2.2 设计的读入

设计的读入有两种方法:analyze + elaborate 和 read。

2.2.1 analyze + elaborate

analyze 命令用以分析、翻译 RTL 代码,并将中间结果存入指定的库中。其语法为:

analyze

-library <库名称>

-format <文件类型>

<文件名列表>

-library <库名称>:指定中间结果所存放的库,即 UNIX 下的一个目录,缺省为当前目录(WORK)

-format <文件类型>:RTL 源文件的类型,即 Verilog 或 vhdl

<文件名列表>:所有需要分析的源文件名,若有多个文件,则用“{}”括起

例 2-1 (将直接数字频率合成器的所有设计源文件读入 lib1 库中):

hdlin_enable_presto = false /*禁止 Presto 编译器功能*/

define_design_lib lib1 -path “./lib1” /*将目录 ./lib1 映射为一个设计库*/

analyze –library lib1 –format verilog {croma.v, cromb.v, ddfs.v, froma.v, fromb.v}

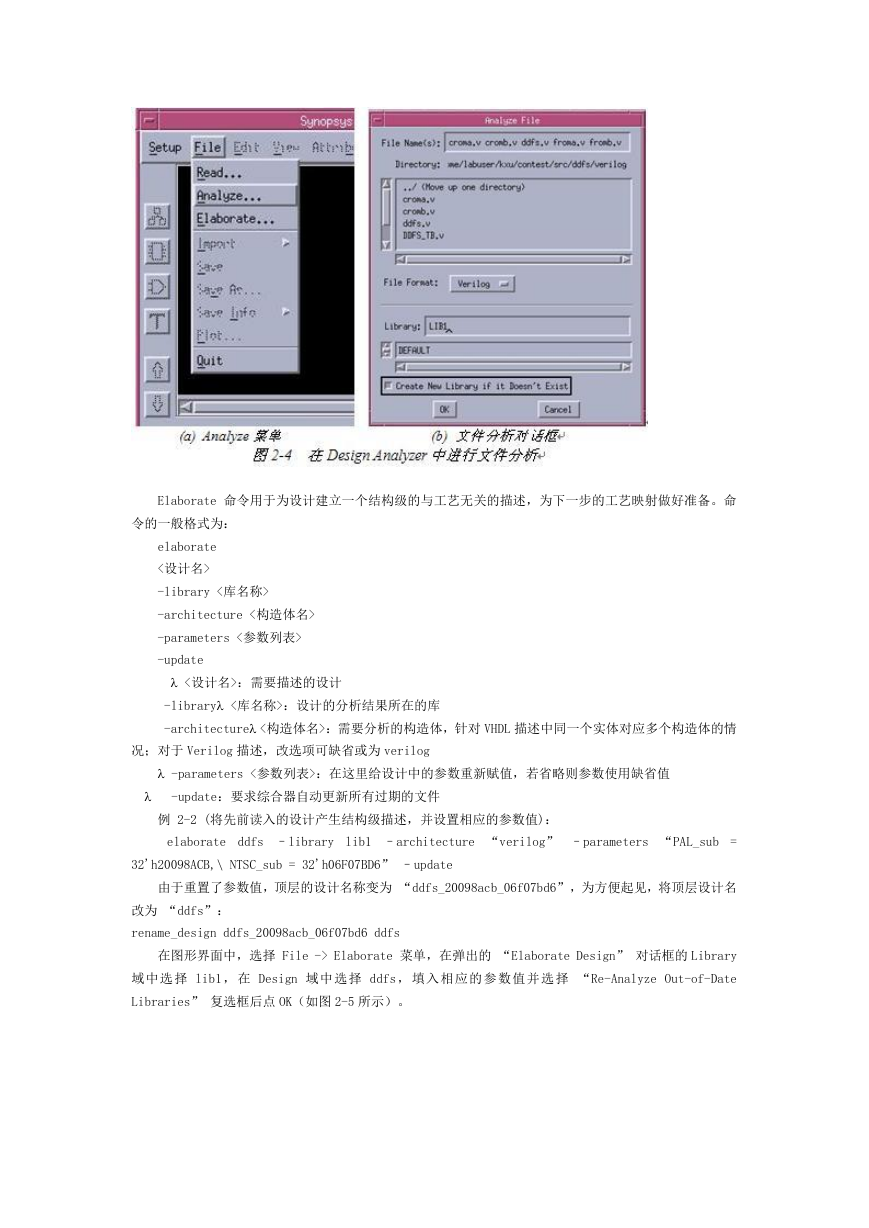

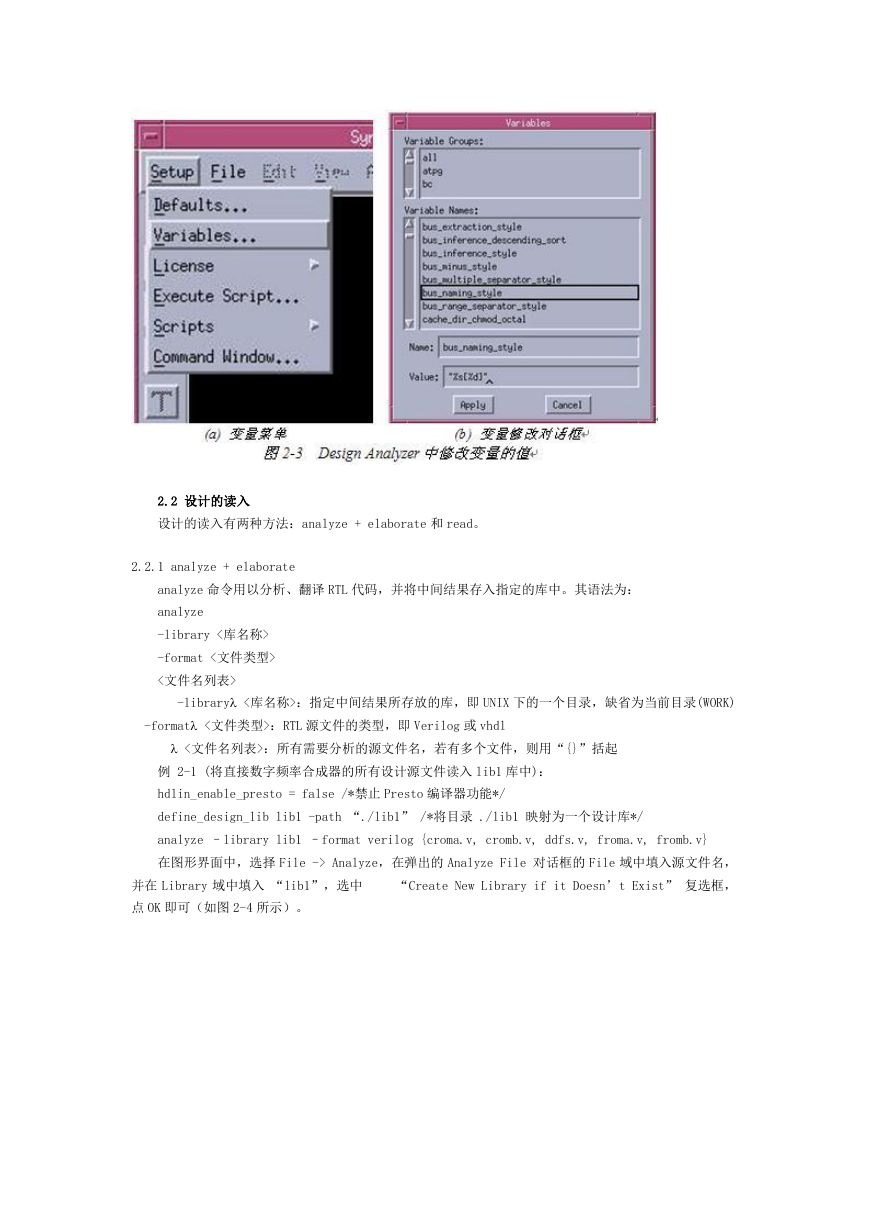

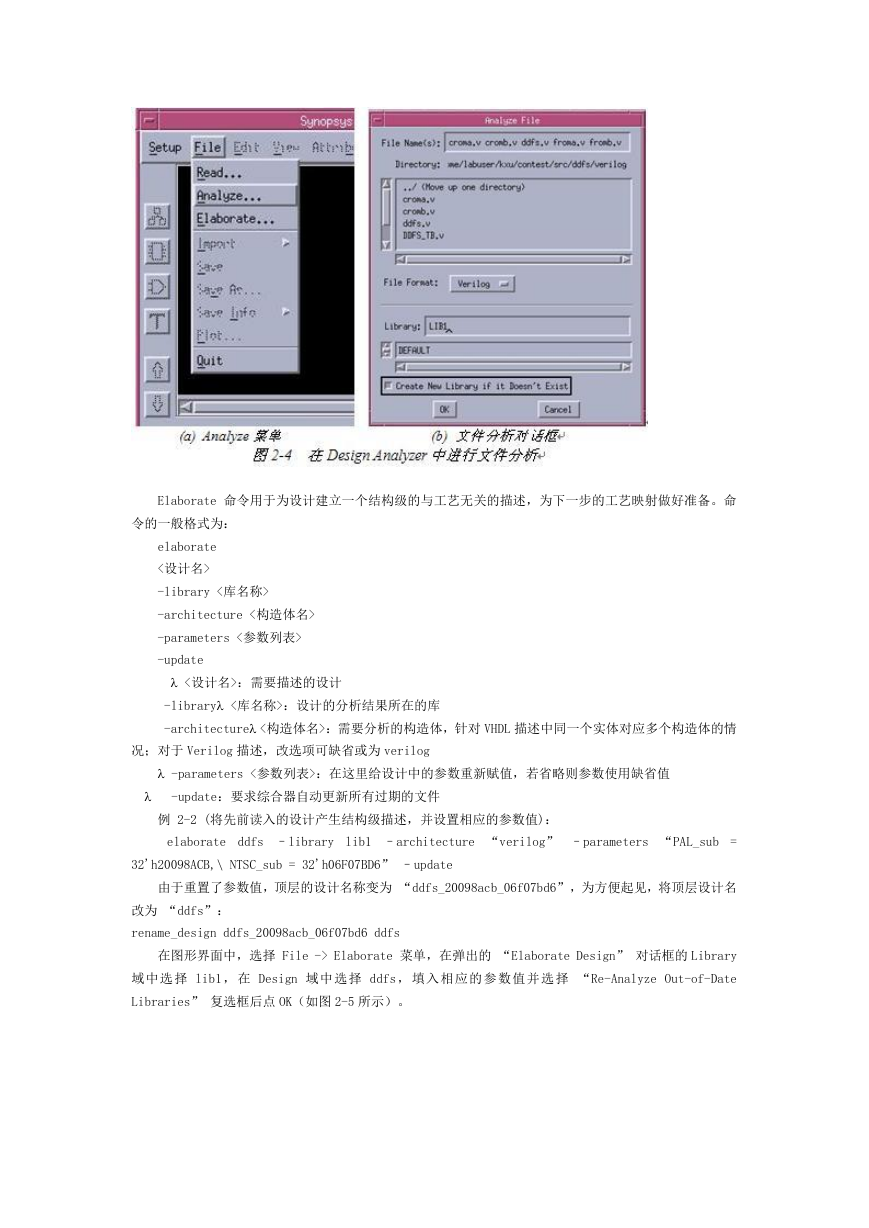

在图形界面中,选择 File -> Analyze,在弹出的 Analyze File 对话框的 File 域中填入源文件名,

并在 Library 域中填入 “lib1”,选中 “Create New Library if it Doesn’t Exist” 复选框,

点 OK 即可(如图 2-4 所示)。

�

Elaborate 命令用于为设计建立一个结构级的与工艺无关的描述,为下一步的工艺映射做好准备。命

令的一般格式为:

elaborate

<设计名>

-library <库名称>

-architecture <构造体名>

-parameters <参数列表>

-update

<设计名>:需要描述的设计

-library <库名称>:设计的分析结果所在的库

-architecture <构造体名>:需要分析的构造体,针对 VHDL 描述中同一个实体对应多个构造体的情

况;对于 Verilog 描述,改选项可缺省或为 verilog

-parameters <参数列表>:在这里给设计中的参数重新赋值,若省略则参数使用缺省值

-update:要求综合器自动更新所有过期的文件

例 2-2 (将先前读入的设计产生结构级描述,并设置相应的参数值):

elaborate ddfs –library lib1 –architecture “verilog” –parameters “PAL_sub =

32'h20098ACB,\ NTSC_sub = 32'h06F07BD6” –update

由于重置了参数值,顶层的设计名称变为 “ddfs_20098acb_06f07bd6”,为方便起见,将顶层设计名

改为 “ddfs”:

rename_design ddfs_20098acb_06f07bd6 ddfs

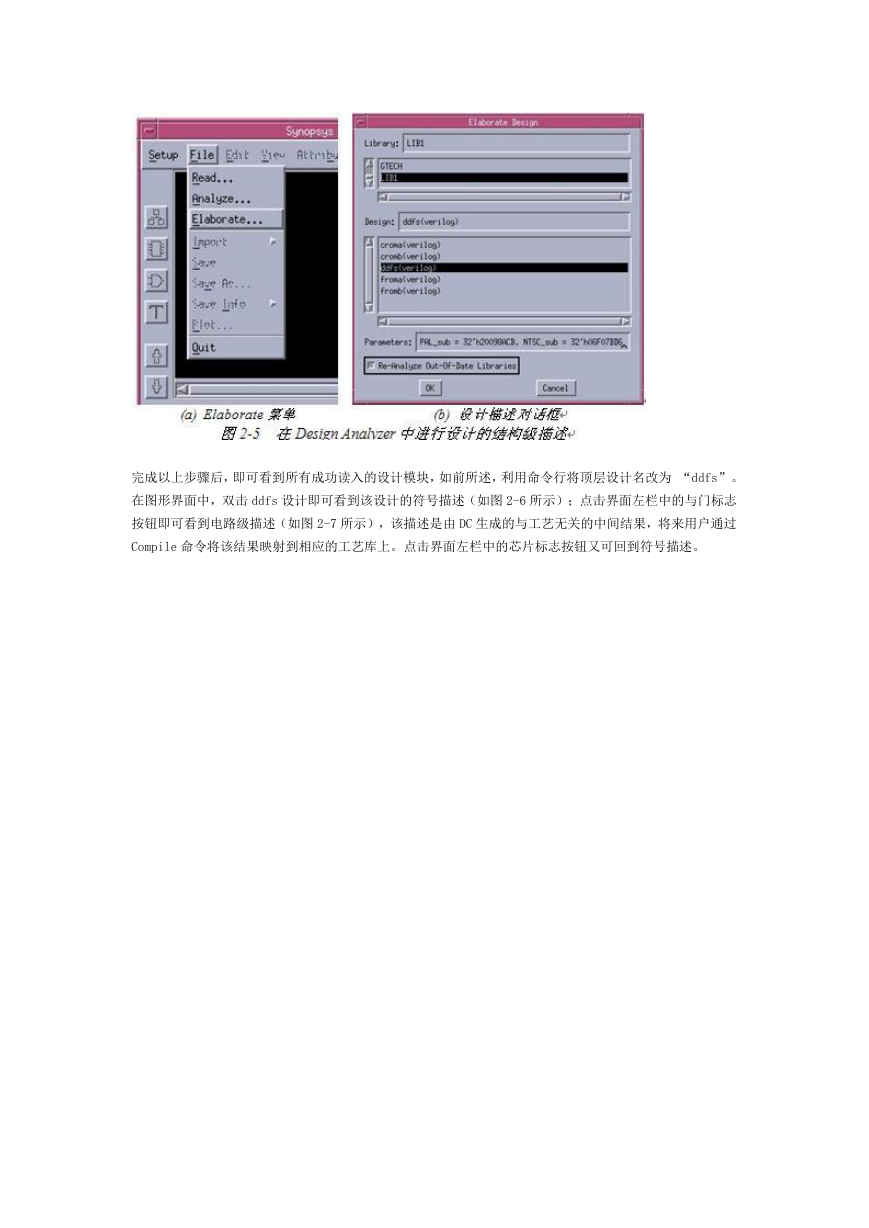

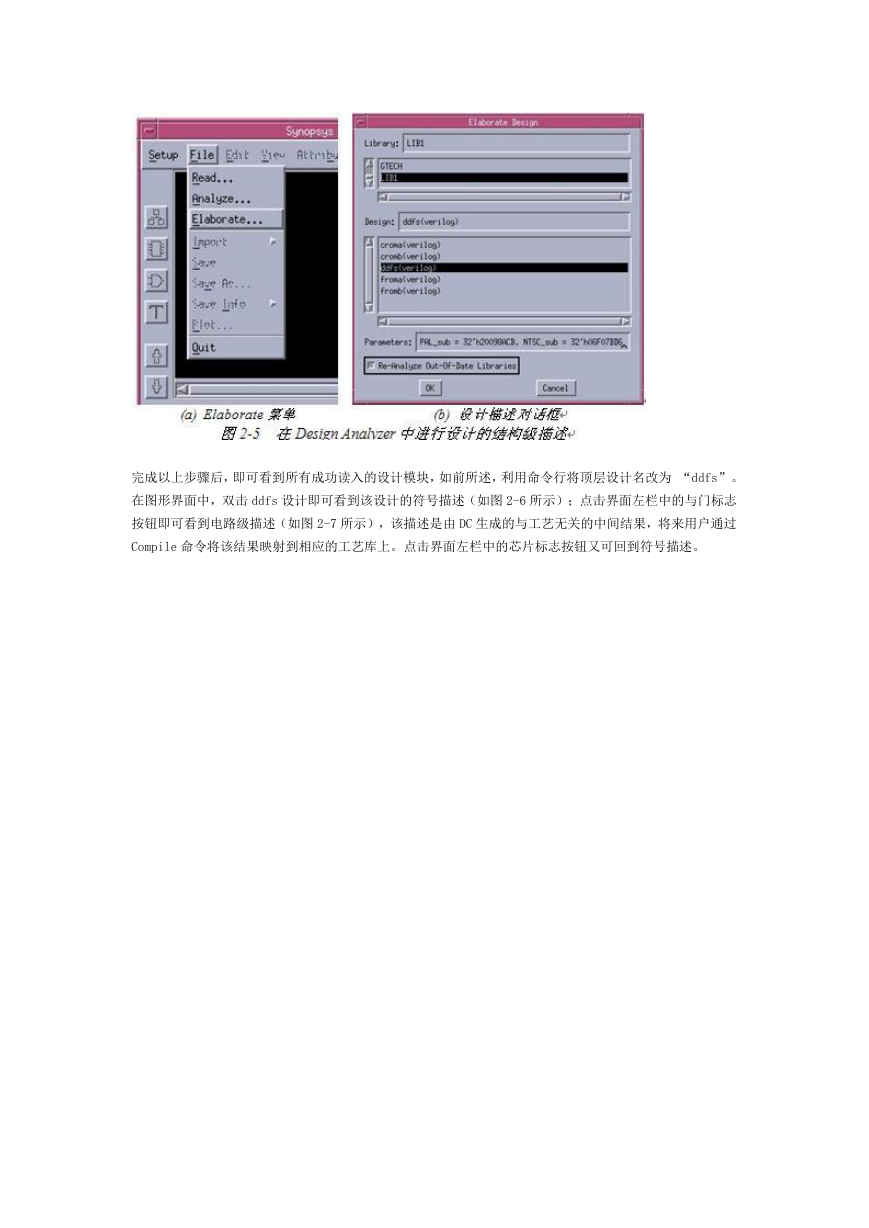

在图形界面中,选择 File -> Elaborate 菜单,在弹出的 “Elaborate Design” 对话框的 Library

域中选择 lib1,在 Design 域中选择 ddfs,填入相应的 参数值并 选择 “Re-Analyze Out-of-Date

Libraries” 复选框后点 OK(如图 2-5 所示)。

�

完成以上步骤后,即可看到所有成功读入的设计模块,如前所述,利用命令行将顶层设计名改为 “ddfs”。

在图形界面中,双击 ddfs 设计即可看到该设计的符号描述(如图 2-6 所示);点击界面左栏中的与门标志

按钮即可看到电路级描述(如图 2-7 所示),该描述是由 DC 生成的与工艺无关的中间结果,将来用户通过

Compile 命令将该结果映射到相应的工艺库上。点击界面左栏中的芯片标志按钮又可回到符号描述。

�

2.2.2 read 命令

使用 read 命令可以一步完成 analyze+elaborate 的工作,并且 read 命令还可以用来读取 db、EDIF 等

格式的设计(analyze+elaborate 仅能用于 VHDL 和 verilog)。但是,read 命令无法支持参数修改、VHDL 中

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc