目录

引言 .................................................................................................................................................... 1

1.总体电路结构设计 ........................................................................................................................ 2

1.1 电路功能与性能................................................................................................................. 2

1.2 关键功能电路设计 .............................................................................................................2

1.3 电路接口 ............................................................................................................................. 3

1.4 电路功能框图 ..................................................................................................................... 4

1.5 验证方案 ............................................................................................................................. 4

2.模块设计 ........................................................................................................................................ 4

2.1 数据接收模块 ..................................................................................................................... 4

2.2 时钟模块 ............................................................................................................................ 5

2.3 数据存储模块 .................................................................................................................... 5

2.4 VGA 显示模块 ..................................................................................................................... 6

3.代码输入与仿真 ............................................................................................................................ 6

3.1 UART_RX 代码仿真分析 .....................................................................................................6

3.2 RAM2 写入操作控制...........................................................................................................6

3.3 全局仿真分析 .................................................................................................................... 8

4.设计的 FPGA 实现及板级测试......................................................................................................9

4.1 管脚配置 ............................................................................................................................. 9

4.2 电路 FPGA 测试................................................................................................................... 9

结论 .................................................................................................................................................. 11

参考文献 .......................................................................................................................................... 12

I

�

引言

近十几年来,可编程器件 FPGA/CPLD成本的大幅度降低,且随着EDA技术的

日益普及,FPGA/CPLD以其较好的集成度和稳定性、可编程实现与升级的特点,

在电子设计领域得到了越来越多的应用。

本设计要实现一个用Verilog编写FPGA的VGA显示,达到上位机发送图片数据

UART进行接收至VGA、终端显示的功能。

本设计使用Altera的Cyclone IV代芯片,开发过程中使用Altera公司的集成

工具Quartus II 13.0实现本设计。基本流程如下:首先根据任务书的设计要求

进行方案的设计并做初步的分工,确定引脚、设计功能框图、划分模块、讨论数

据处理流程与方法等;然后依据模块设计进行模块VHDL代码的输入与功能仿真,

完成功能仿真后,进行布局与布线,生成配置文件,最后下载、测试,从而完成

设计。本设计主要完成前端功能设计部分,即方案设计、代码输入、功能仿真。

板级验证通过观察分析终端显示的图片来检验设计的正确性。

1

�

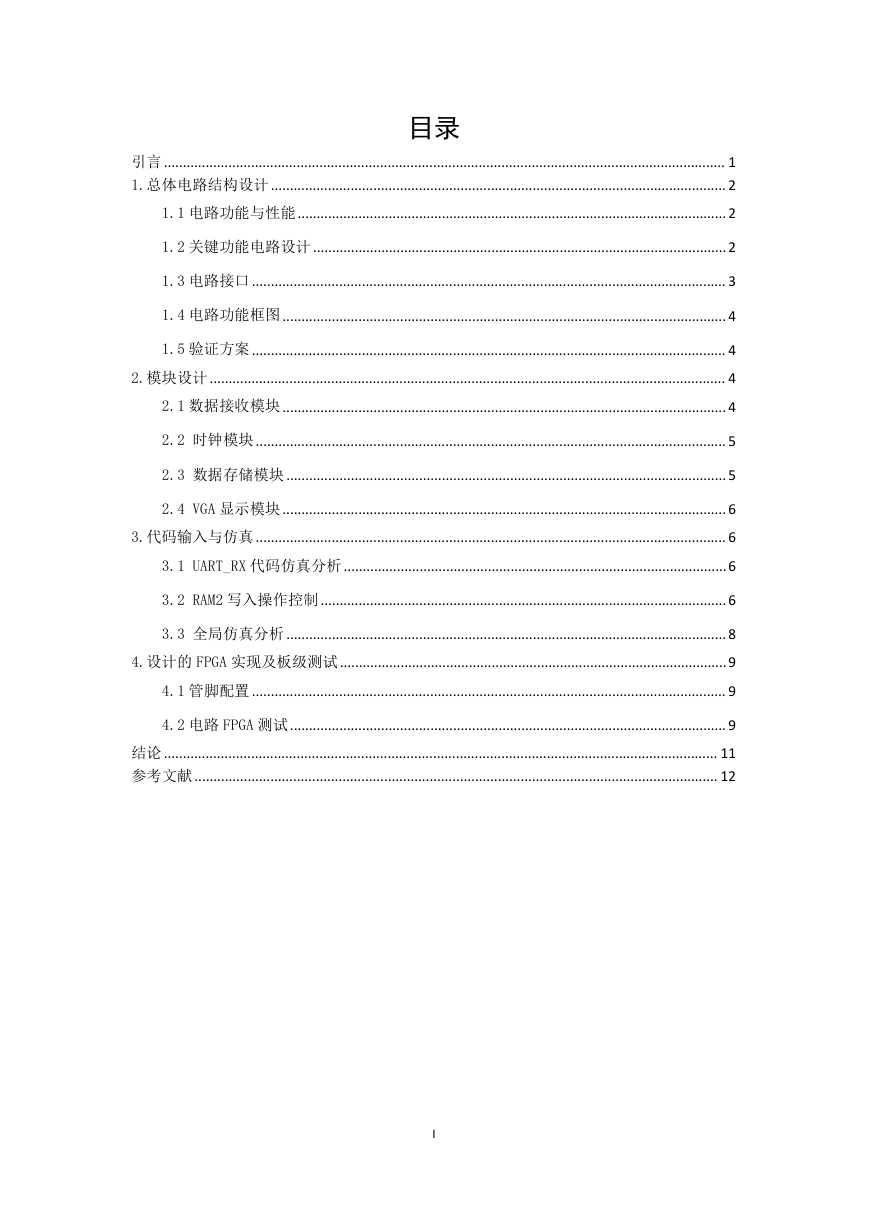

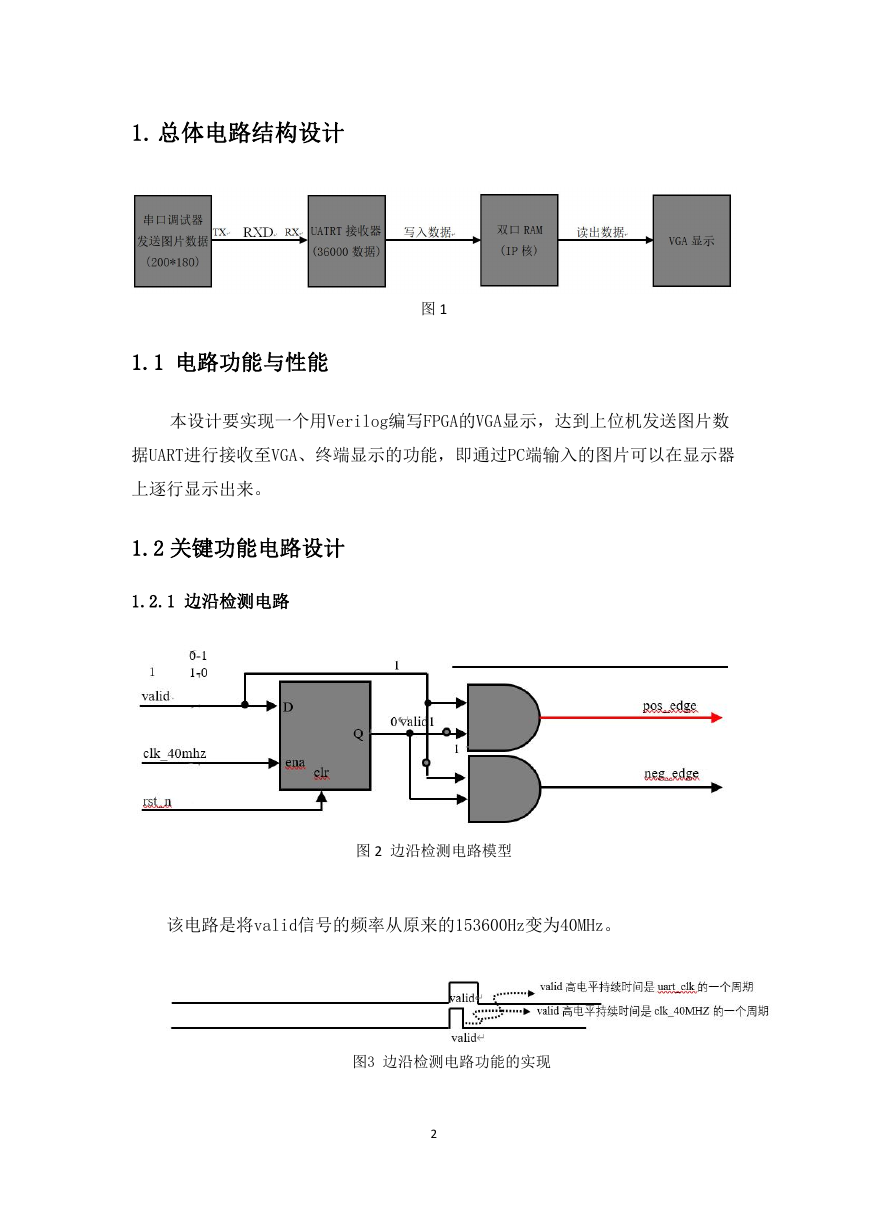

1. 总体电路结构设计

图 1

1.1 电路功能与性能

本设计要实现一个用Verilog编写FPGA的VGA显示,达到上位机发送图片数

据UART进行接收至VGA、终端显示的功能,即通过PC端输入的图片可以在显示器

上逐行显示出来。

1.2 关键功能电路设计

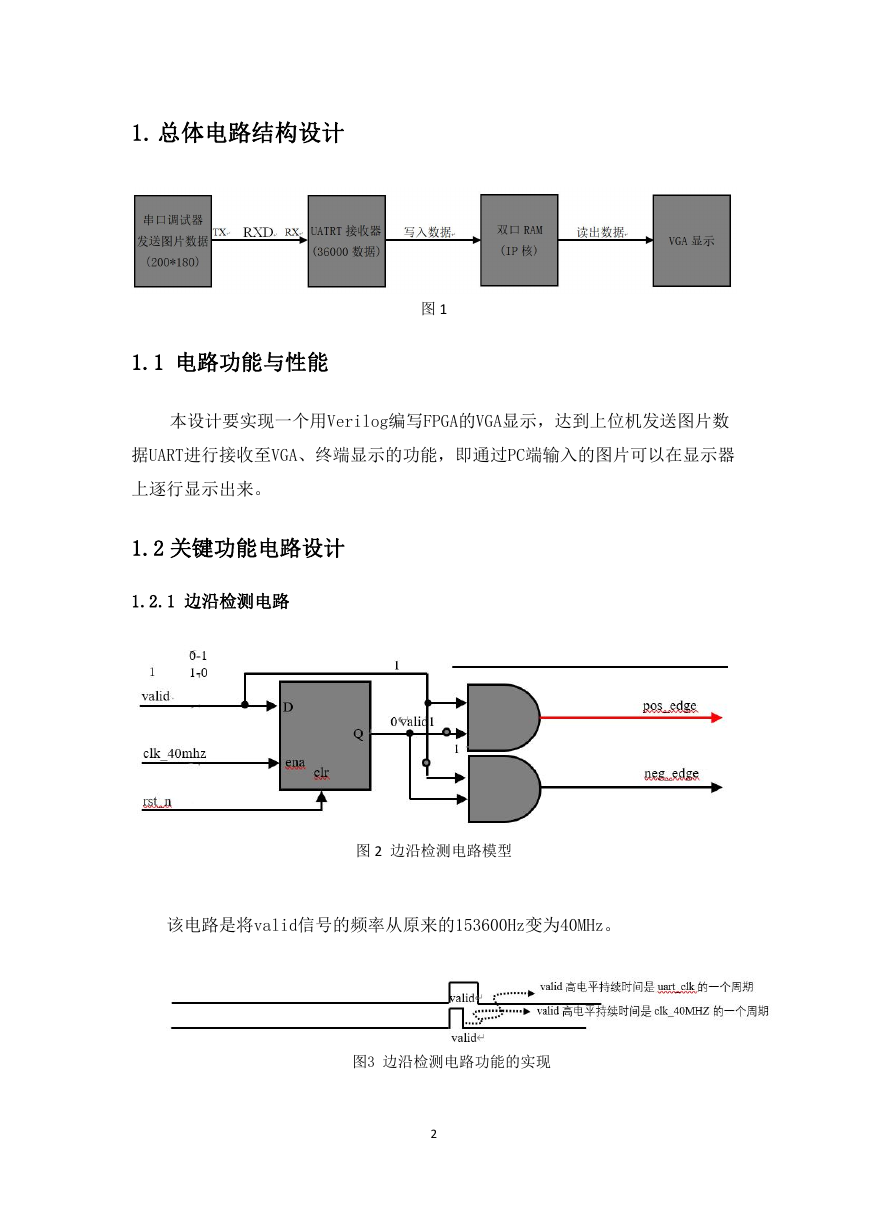

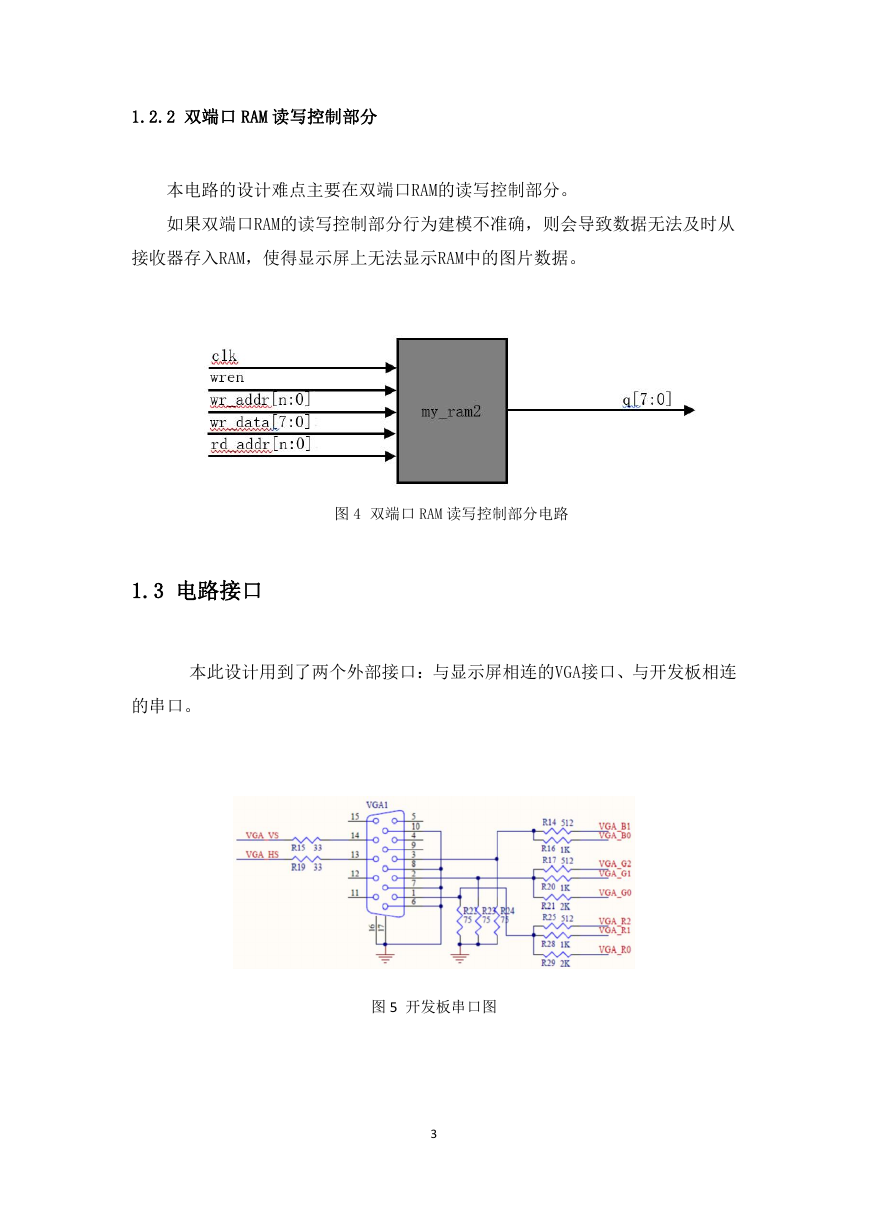

1.2.1 边沿检测电路

图 2 边沿检测电路模型

该电路是将valid信号的频率从原来的153600Hz变为40MHz。

图3 边沿检测电路功能的实现

2

�

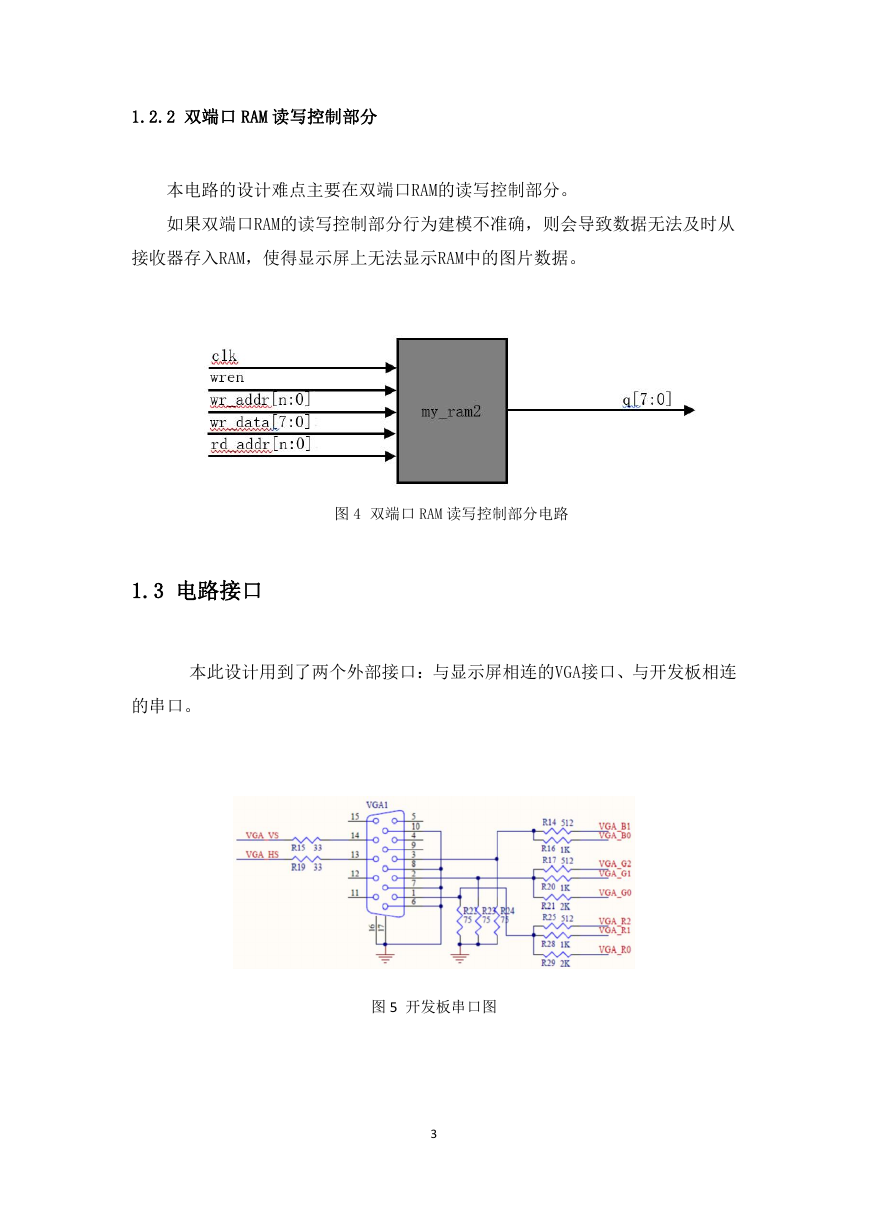

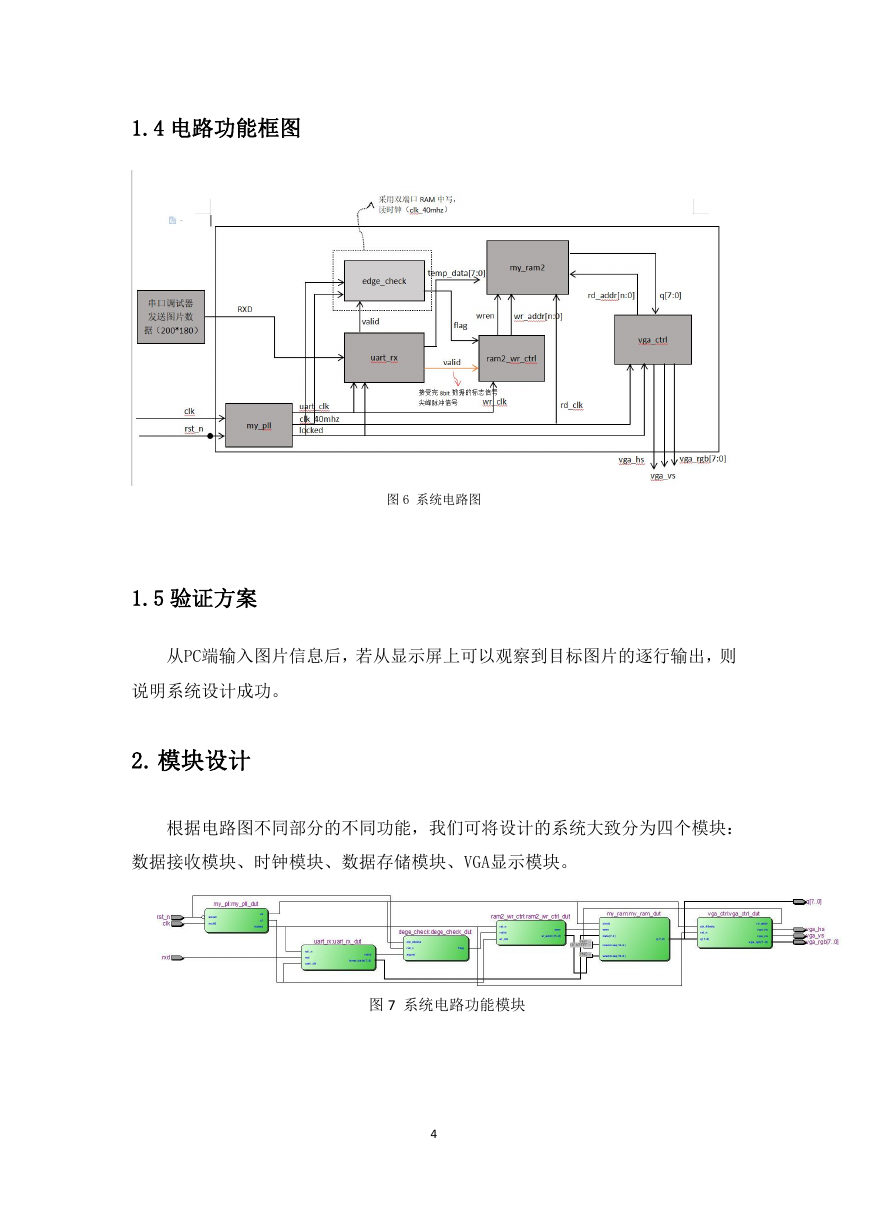

1.2.2 双端口 RAM 读写控制部分

本电路的设计难点主要在双端口RAM的读写控制部分。

如果双端口RAM的读写控制部分行为建模不准确,则会导致数据无法及时从

接收器存入RAM,使得显示屏上无法显示RAM中的图片数据。

图 4 双端口 RAM 读写控制部分电路

1.3 电路接口

本此设计用到了两个外部接口:与显示屏相连的VGA接口、与开发板相连

的串口。

图 5 开发板串口图

3

�

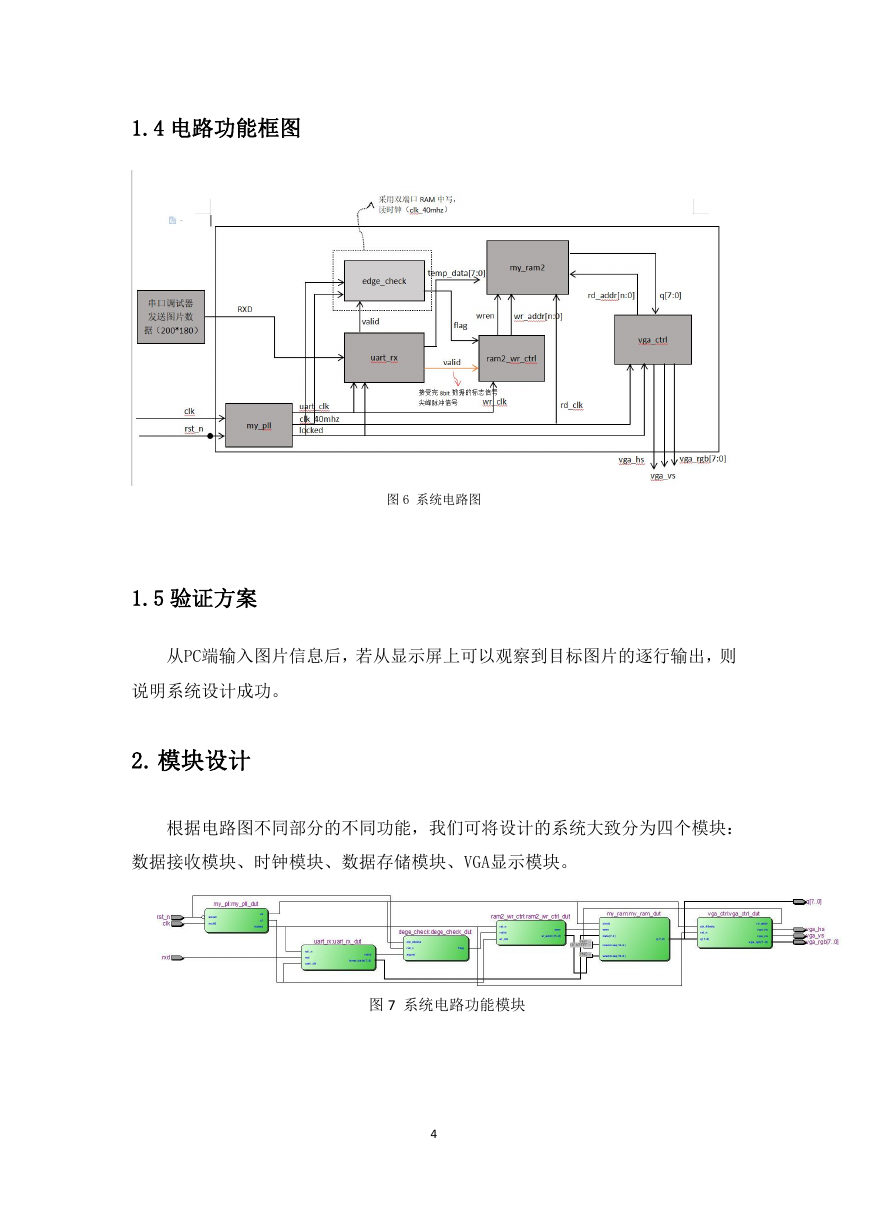

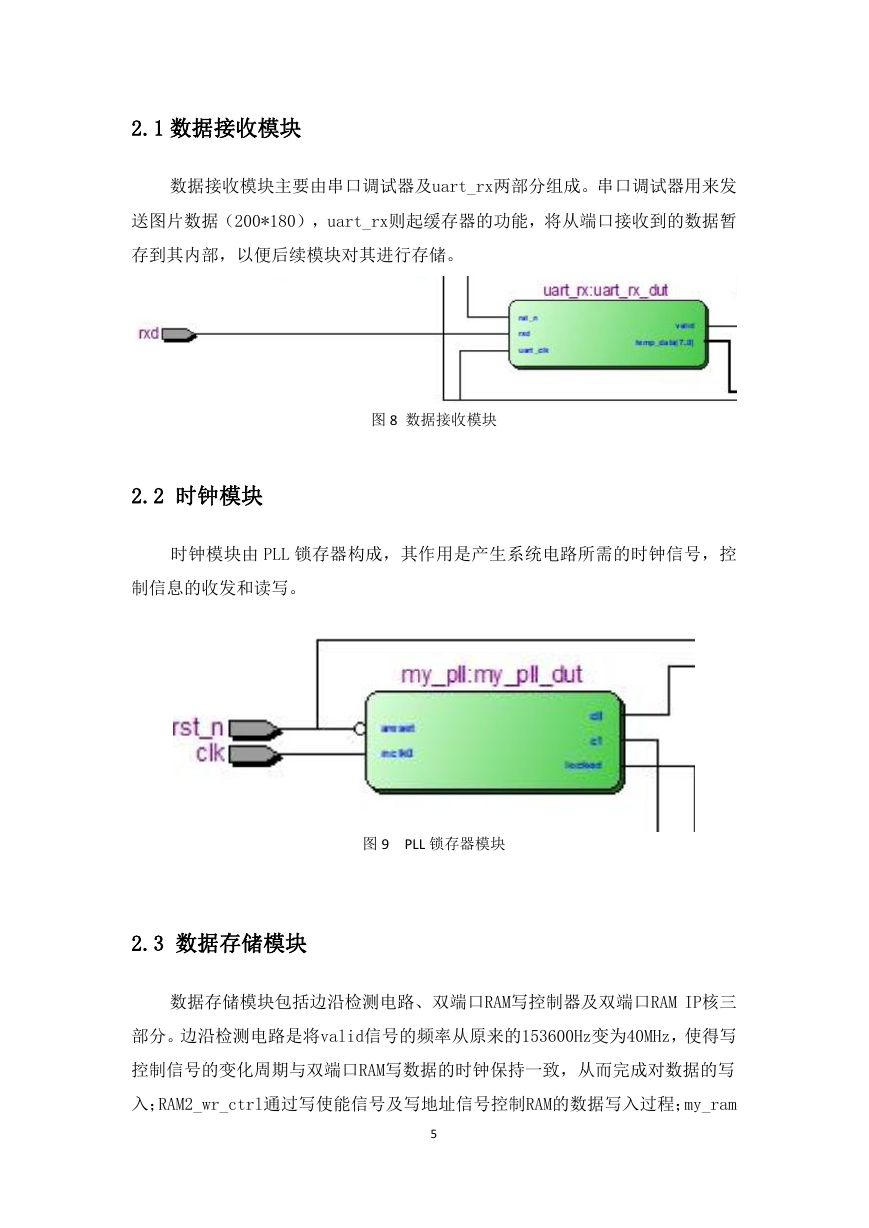

1.4 电路功能框图

图 6 系统电路图

1.5 验证方案

从PC端输入图片信息后,若从显示屏上可以观察到目标图片的逐行输出,则

说明系统设计成功。

2. 模块设计

根据电路图不同部分的不同功能,我们可将设计的系统大致分为四个模块:

数据接收模块、时钟模块、数据存储模块、VGA显示模块。

图 7 系统电路功能模块

4

�

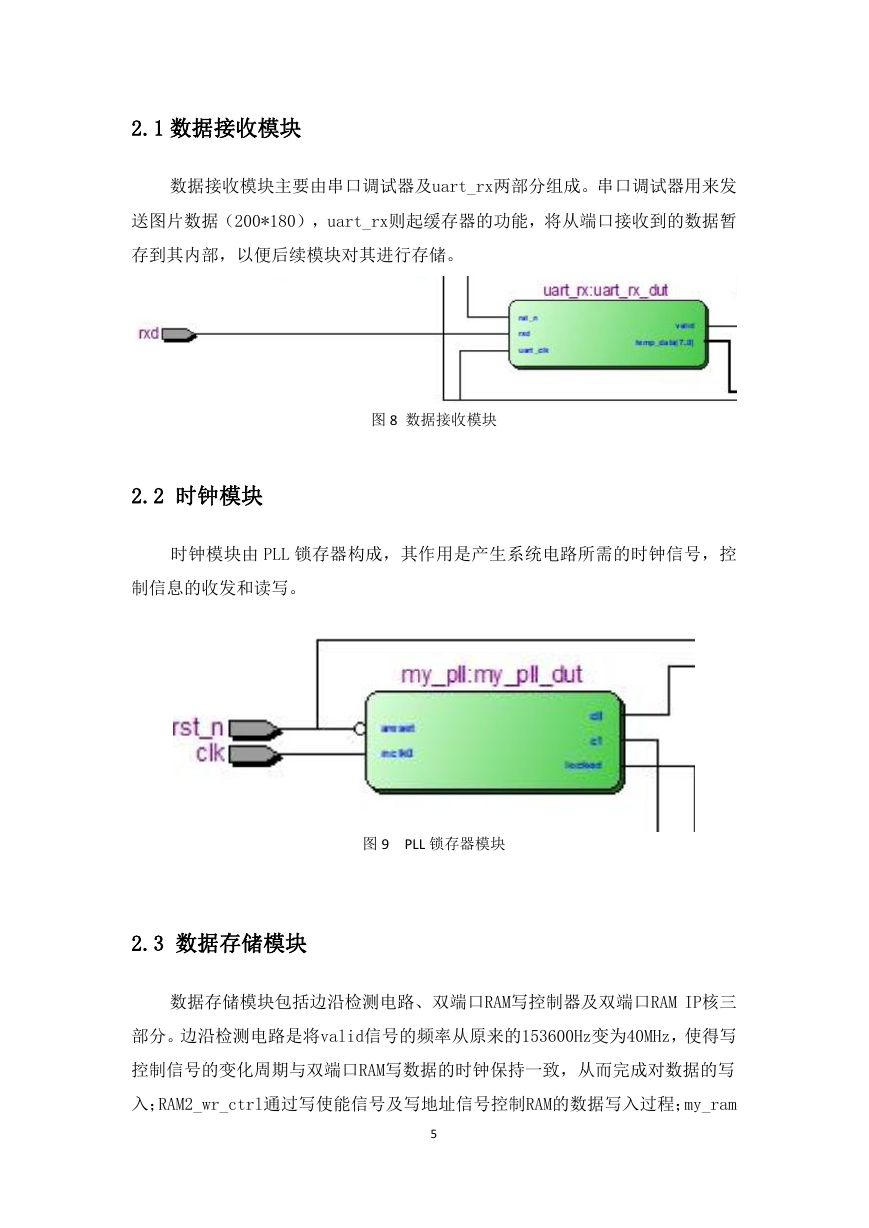

2.1 数据接收模块

数据接收模块主要由串口调试器及uart_rx两部分组成。串口调试器用来发

送图片数据(200*180),uart_rx则起缓存器的功能,将从端口接收到的数据暂

存到其内部,以便后续模块对其进行存储。

图 8 数据接收模块

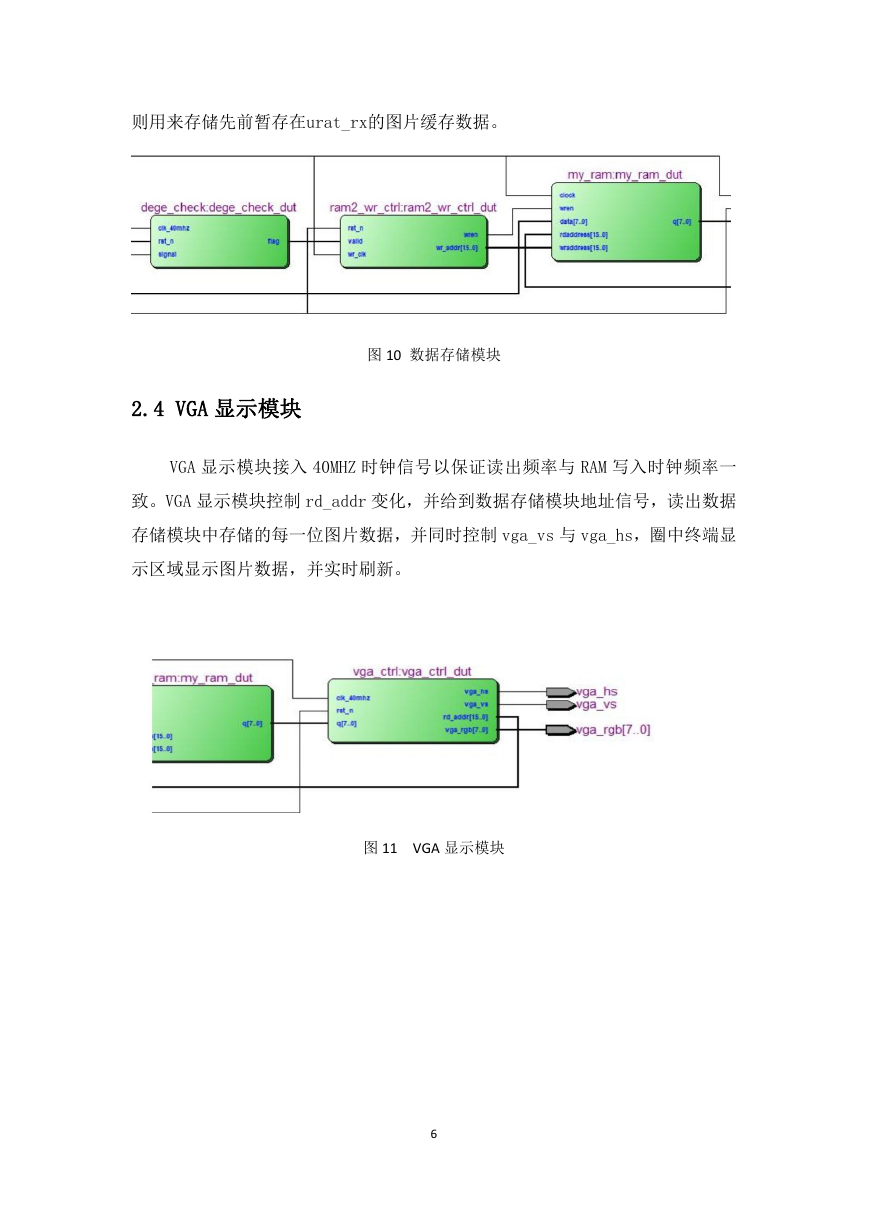

2.2 时钟模块

时钟模块由 PLL 锁存器构成,其作用是产生系统电路所需的时钟信号,控

制信息的收发和读写。

图 9 PLL 锁存器模块

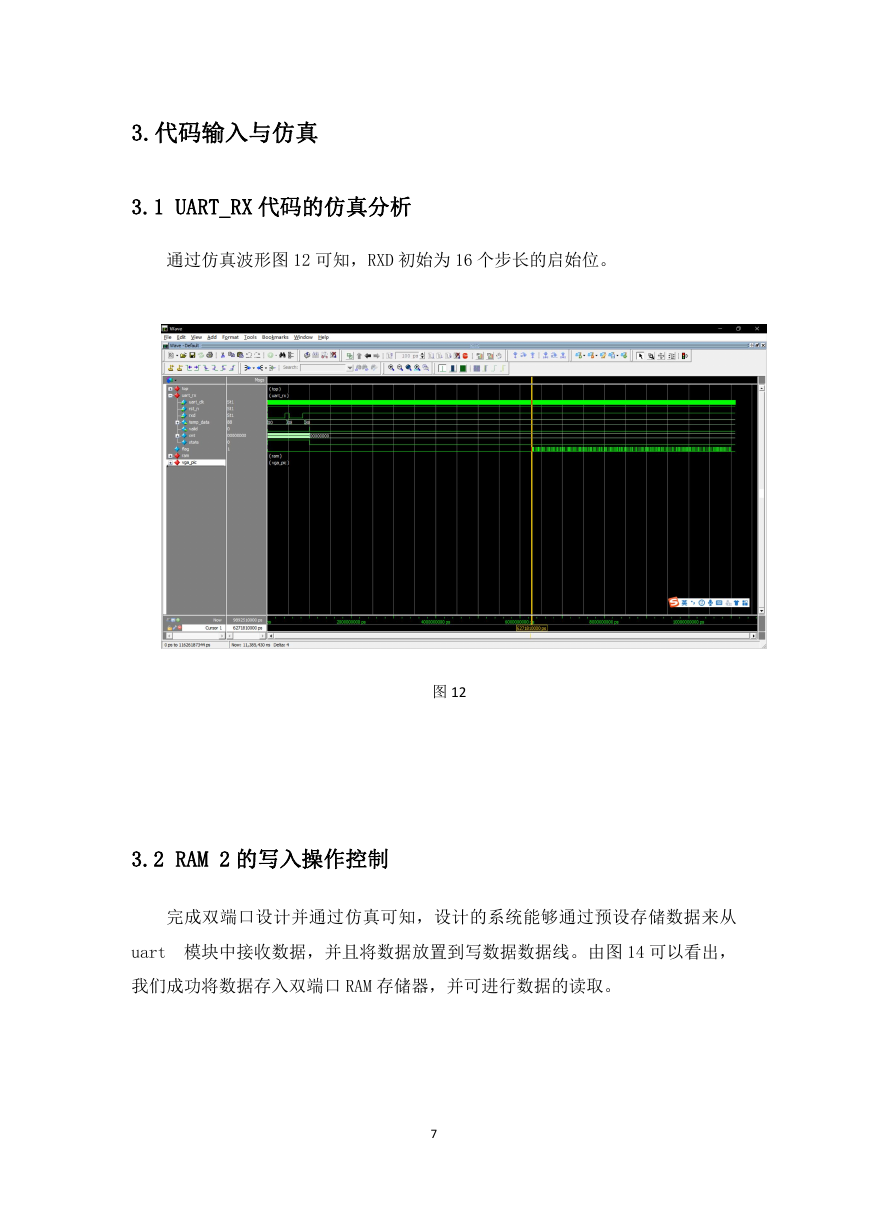

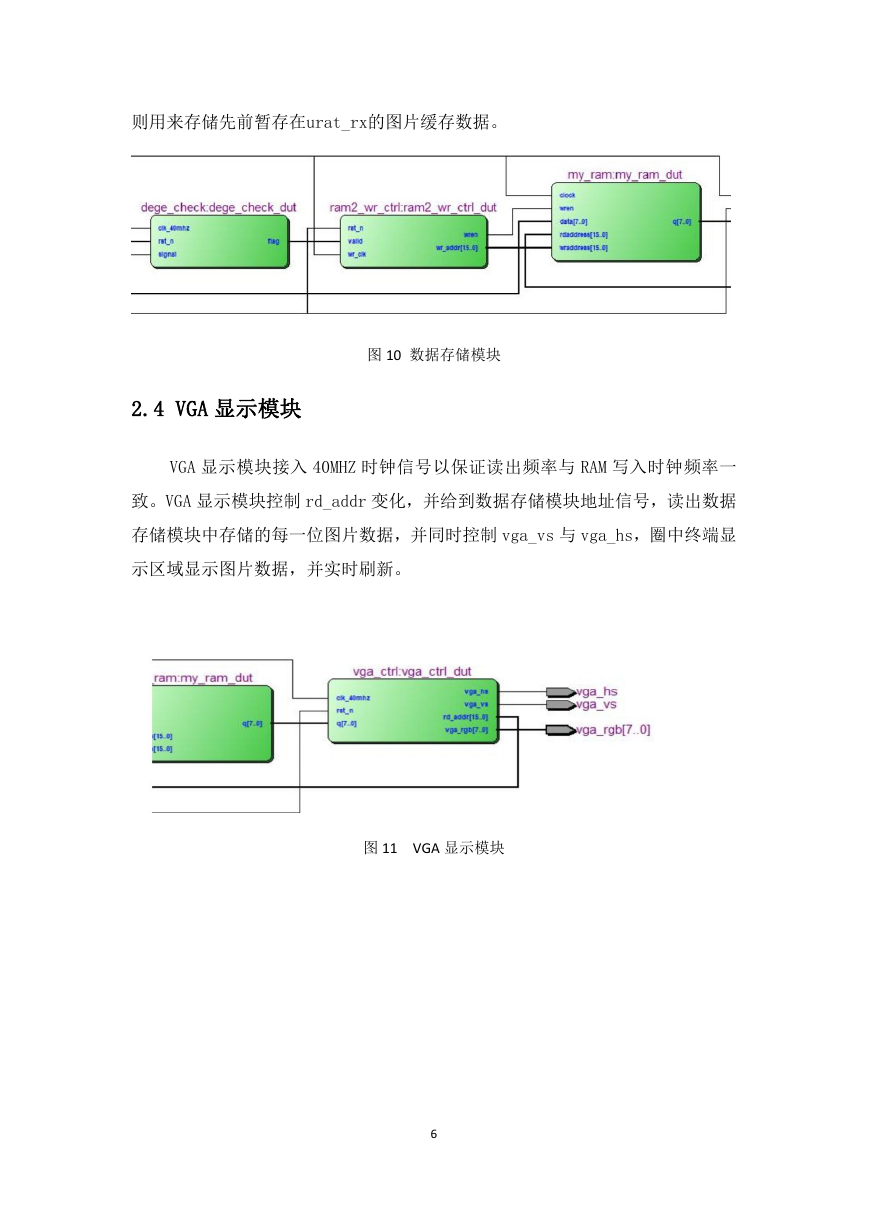

2.3 数据存储模块

数据存储模块包括边沿检测电路、双端口RAM写控制器及双端口RAM IP核三

部分。边沿检测电路是将valid信号的频率从原来的153600Hz变为40MHz,使得写

控制信号的变化周期与双端口RAM写数据的时钟保持一致,从而完成对数据的写

入;RAM2_wr_ctrl通过写使能信号及写地址信号控制RAM的数据写入过程;my_ram

5

�

则用来存储先前暂存在urat_rx的图片缓存数据。

图 10 数据存储模块

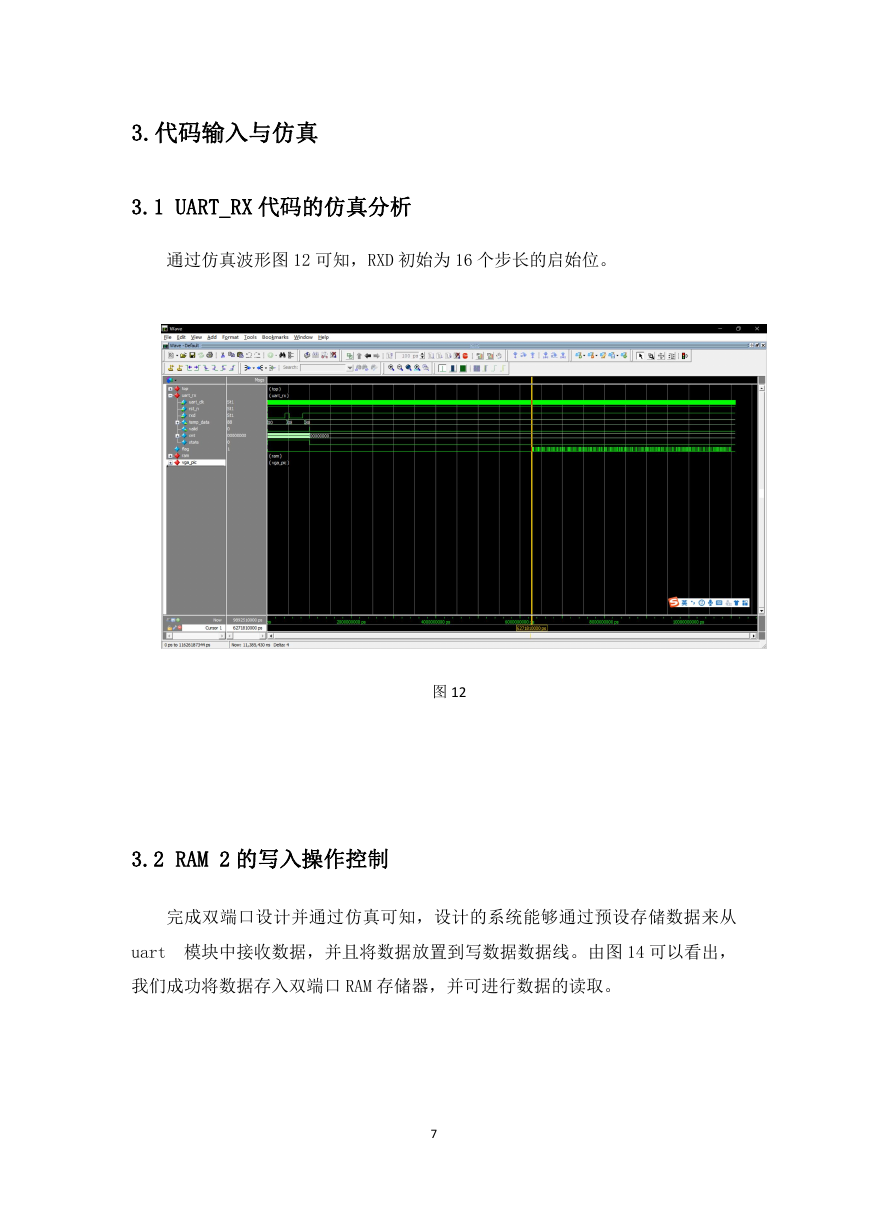

2.4 VGA 显示模块

VGA 显示模块接入 40MHZ 时钟信号以保证读出频率与 RAM 写入时钟频率一

致。VGA 显示模块控制 rd_addr 变化,并给到数据存储模块地址信号,读出数据

存储模块中存储的每一位图片数据,并同时控制 vga_vs 与 vga_hs,圈中终端显

示区域显示图片数据,并实时刷新。

图 11 VGA 显示模块

6

�

3.代码输入与仿真

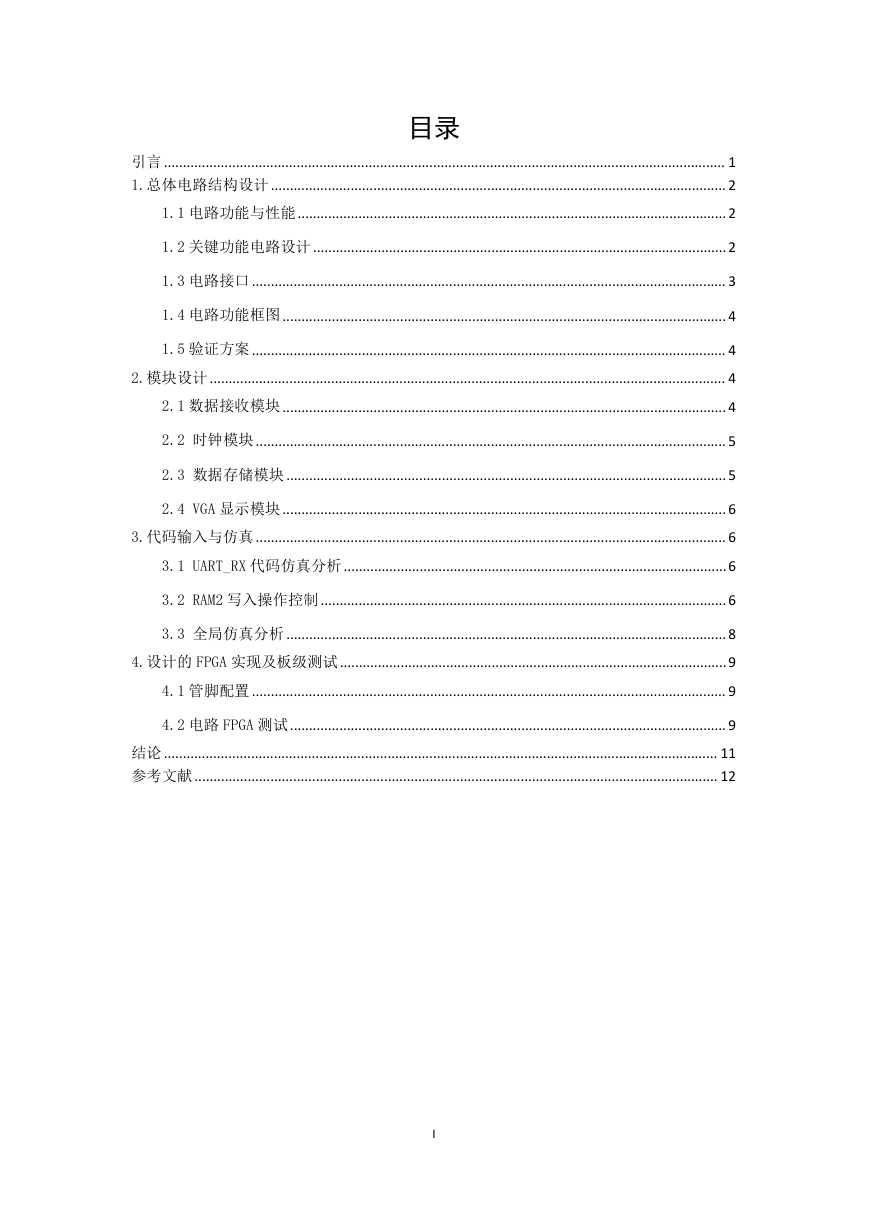

3.1 UART_RX 代码的仿真分析

通过仿真波形图 12 可知,RXD 初始为 16 个步长的启始位。

图 12

3.2 RAM 2 的写入操作控制

完成双端口设计并通过仿真可知,设计的系统能够通过预设存储数据来从

uart 模块中接收数据,并且将数据放置到写数据数据线。由图 14 可以看出,

我们成功将数据存入双端口 RAM 存储器,并可进行数据的读取。

7

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc