CYRF7936

2.4 GHz CyFi (TM) 收发器

特性

■ 2.4 GHz 直接序列扩频 (DSSS) 无线收发器

■ 可在全球工业、科学和医疗 (ISM) 免执照频段

(2.400 GHz – 2.483 GHz) 内工作

■ 21 mA 工作电流 (发射功率为 –5 dBm 时)

■ 最大发射功率 +4 dBm

■ 接收灵敏度最大可达 –97 dBm

■ 睡眠电流 <1 μA

■ DSSS 数据速率最大可达 250 kbps, GFSK 数据速率为

1 Mbps

■ 外部元件使用较少

■ 自动事务处理序列发生器 (ATS) — 无 MCU 干预

■ 成帧、长度、 CRC16 和自动 ACK

■ 适用于 MCU 的电源管理装置 (PMU)

■ 快速启动和快速频道更改

■ 独立的 16 字节发送和接收 FIFO

■ 动态数据速率接收

■ 接收信号强度指示 (RSSI)

■ 睡眠模式下的串行外设接口 (SPI) 控制

■ 4 MHz SPI 微控制器接口

■ 电池电压监控电路

■ 支持钮扣电池供电应用

■ 工作电压为 1.8V 到 3.6V

■ 工作温度为 0 到 70°C

■ 节省空间的 40 引脚 QFN 6x6 mm 封装

应用

■ 无线传感器网络

■ 无线制动器控制

■ 家庭自动化

■ 大型家用电器

■ 商用建筑自动化

■ 自动抄表器

■ 精准农业

■ 远程控制

■ 消费电子产品

■ 个人保健

■ 玩具

应用支持

有关开发工具、参考设计和应用笔记,请参见

www.cypress.com。

逻辑框图

VREG

VDD

VCC

PACTL

L/D

VBAT

VIO

IRQ

SS

SCK

MISO

MOSI

RST

PMU

CyFi Radio Modem

Data

Interface

and

Sequencer

SPI

RSSI

DSSS

Baseband

& Framer

GFSK

Modulator

GFSK

Demodulator

RFP

RFN

RFBIAS

Xtal Osc

Synthesizer

XTAL

XOUT

GND

Cypress Semiconductor Corporation

文件编号: 001-50428 修订版 **

•

198 Champion Court

•

San Jose, CA 95134-1709

408-943-2600

修订时间 2008 年 12 月 11 日

•

[+] Feedback

�

CYRF7936

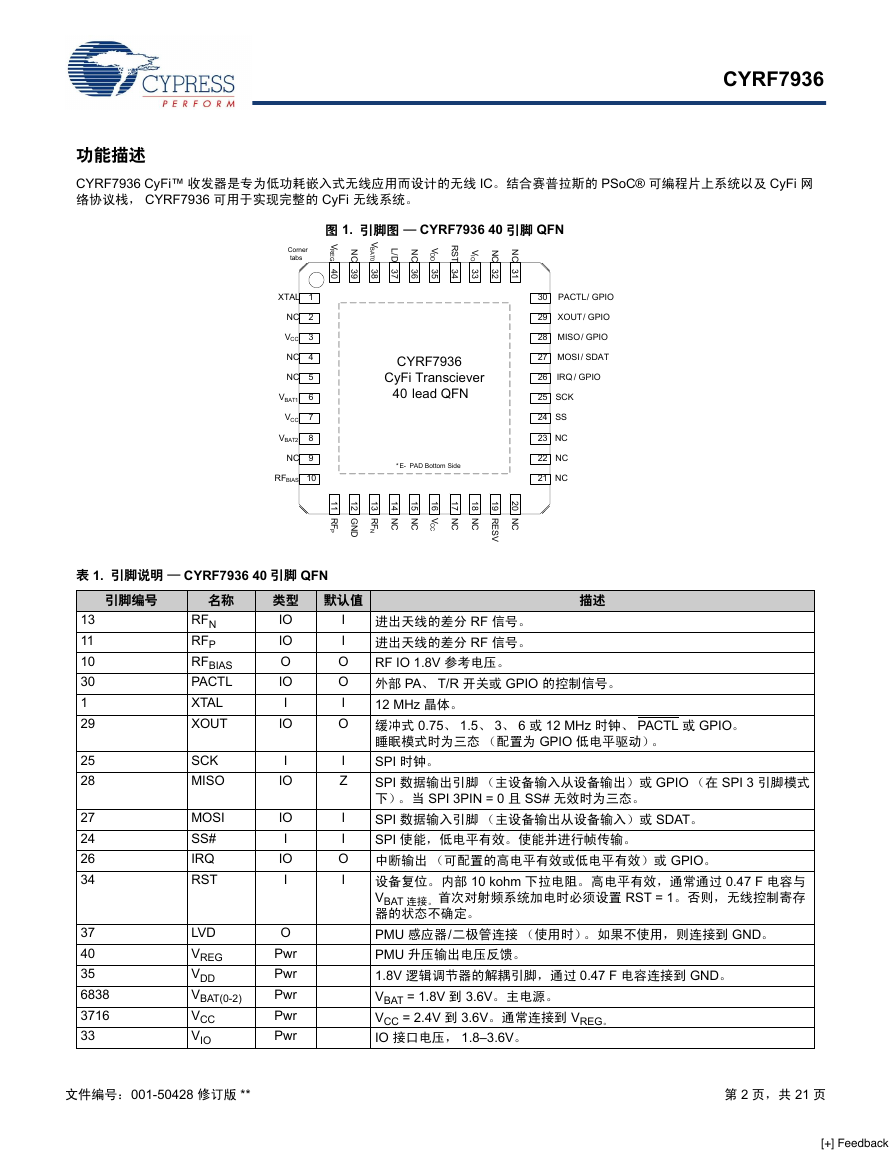

功能描述

CYRF7936 CyFi™ 收发器是专为低功耗嵌入式无线应用而设计的无线 IC。 结合赛普拉斯的 PSoC® 可编程片上系统以及 CyFi 网

络协议栈, CYRF7936 可用于实现完整的 CyFi 无线系统。

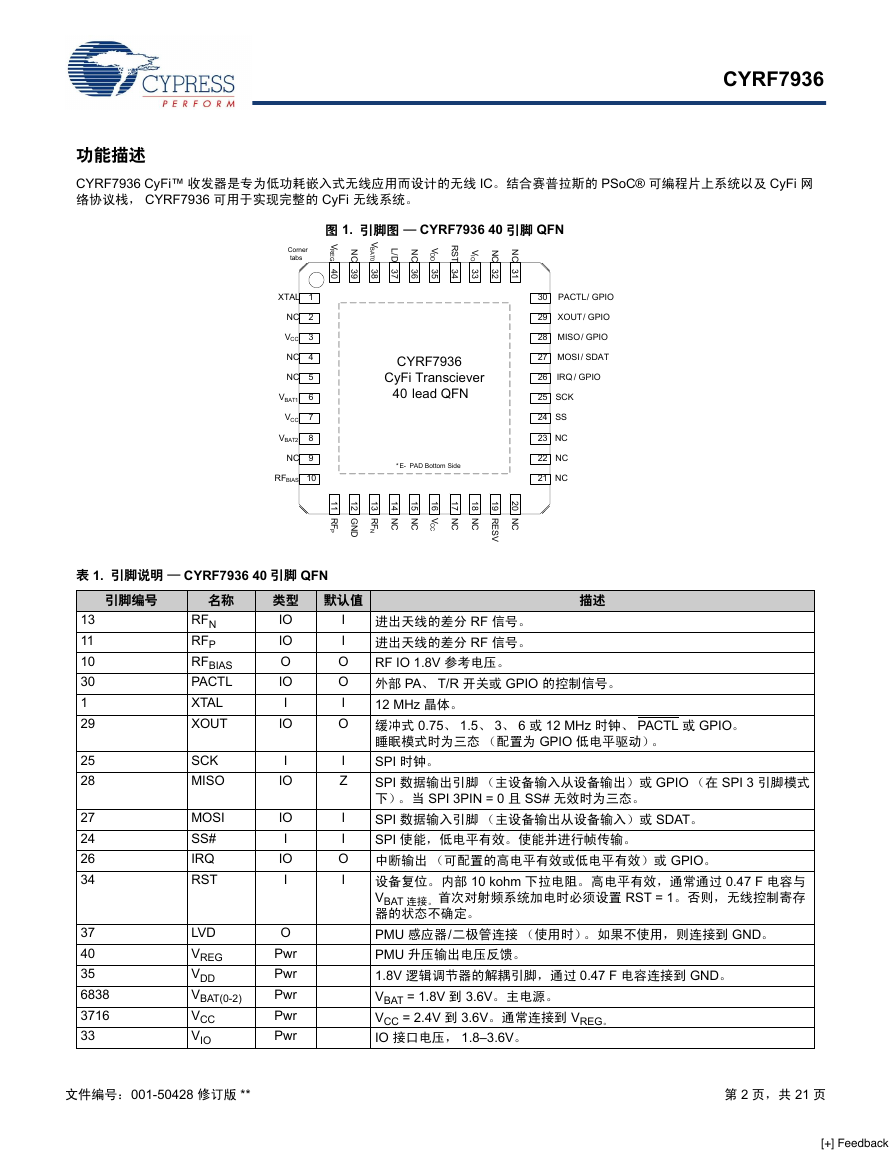

图 1. 引脚图 — CYRF7936 40 引脚 QFN

Corner

tabs

V

R

E

G

N

C

V

B

A

T

0

/

L

D

N

C

V

D

D

R

S

T

VI

O

N

C

N

C

4

0

3

9

3

8

3

7

3

6

3

5

3

4

3

3

3

2

3

1

XTAL

NC

VCC

NC

NC

VBAT1

VCC

VBAT2

NC

1

2

3

4

5

6

7

8

9

RFBIAS

10

CYRF7936

CyFi Transciever

40 lead QFN

* E- PAD Bottom Side

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

2

0

R

F

P

G

N

D

R

F

N

N

C

N

C

V

C

C

N

C

N

C

N

C

R

E

S

V

30

29

28

27

26

25

24

23

22

21

PACTL / GPIO

XOUT / GPIO

MISO / GPIO

MOSI / SDAT

IRQ / GPIO

SCK

SS

NC

NC

NC

表 1. 引脚说明 — CYRF7936 40 引脚 QFN

引脚编号

13

11

10

30

1

29

25

28

27

24

26

34

37

40

35

6838

3716

33

名称

RFN

RFP

RFBIAS

PACTL

XTAL

XOUT

SCK

MISO

MOSI

SS#

IRQ

RST

LVD

VREG

VDD

VBAT(0-2)

VCC

VIO

类型 默认值

IO

IO

O

IO

I

IO

I

I

O

O

I

O

I

Z

I

I

O

I

I

IO

IO

I

IO

I

O

Pwr

Pwr

Pwr

Pwr

Pwr

描述

进出天线的差分 RF 信号。

进出天线的差分 RF 信号。

RF IO 1.8V 参考电压。

外部 PA、 T/R 开关或 GPIO 的控制信号。

12 MHz 晶体。

缓冲式 0.75、 1.5、 3、 6 或 12 MHz 时钟、 PACTL 或 GPIO。

睡眠模式时为三态 (配置为 GPIO 低电平驱动)。

SPI 时钟。

SPI 数据输出引脚 (主设备输入从设备输出)或 GPIO (在 SPI 3 引脚模式

下)。 当 SPI 3PIN = 0 且 SS# 无效时为三态。

SPI 数据输入引脚 (主设备输出从设备输入)或 SDAT。

SPI 使能,低电平有效。 使能并进行帧传输。

中断输出 (可配置的高电平有效或低电平有效)或 GPIO。

设备复位。 内部 10 kohm 下拉电阻。 高电平有效,通常通过 0.47 F 电容与

VBAT 连接。 首次对射频系统加电时必须设置 RST = 1。 否则,无线控制寄存

器的状态不确定。

PMU 感应器 / 二极管连接 (使用时)。 如果不使用,则连接到 GND。

PMU 升压输出电压反馈。

1.8V 逻辑调节器的解耦引脚,通过 0.47 F 电容连接到 GND。

VBAT = 1.8V 到 3.6V。 主电源。

VCC = 2.4V 到 3.6V。 通常连接到 VREG。

IO 接口电压, 1.8–3.6V。

文件编号: 001-50428 修订版 **

第 2 页,共 21 页

[+] Feedback

�

CYRF7936

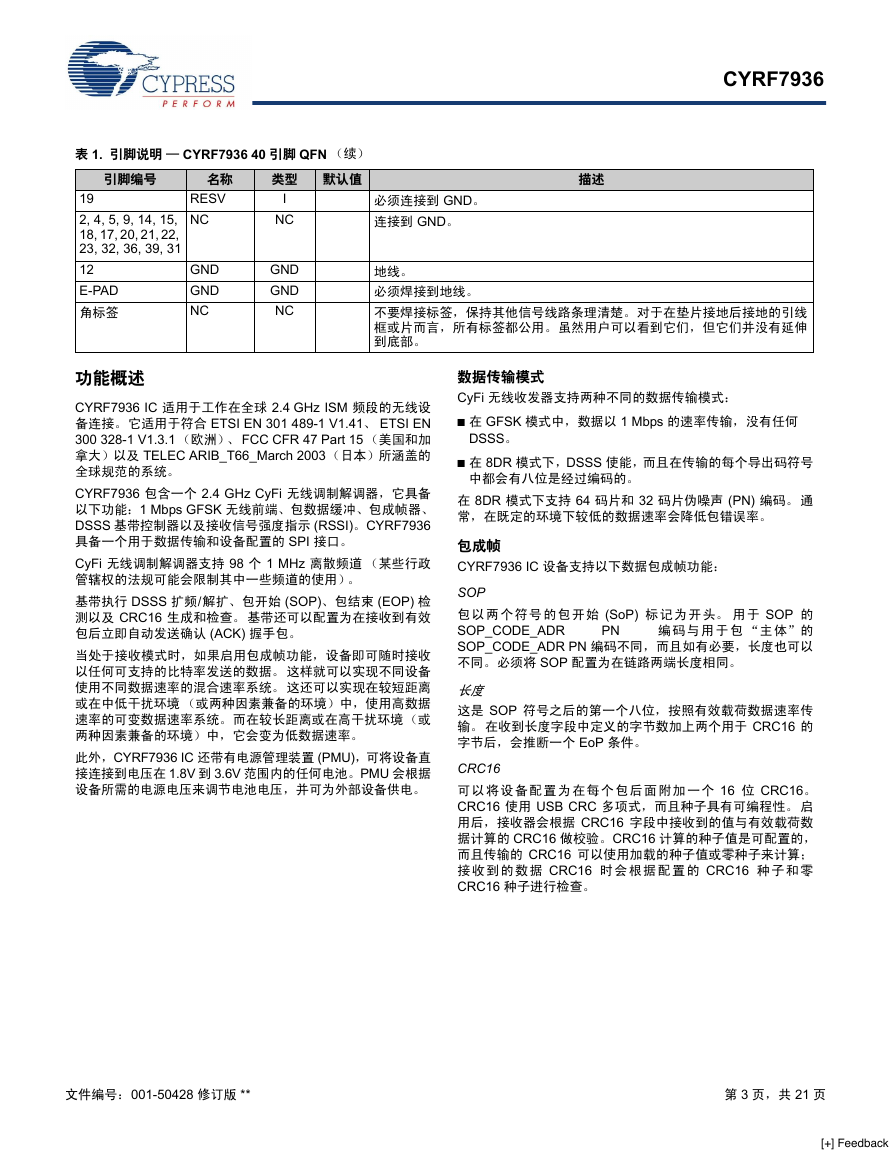

表 1. 引脚说明 — CYRF7936 40 引脚 QFN (续)

引脚编号

19

2, 4, 5, 9, 14, 15,

18, 17, 20, 21, 22,

23, 32, 36, 39, 31

12

E-PAD

角标签

名称

RESV

NC

GND

GND

NC

类型 默认值

描述

I

NC

GND

GND

NC

必须连接到 GND。

连接到 GND。

地线。

必须焊接到地线。

不要焊接标签,保持其他信号线路条理清楚。 对于在垫片接地后接地的引线

框或片而言,所有标签都公用。 虽然用户可以看到它们,但它们并没有延伸

到底部。

功能概述

CYRF7936 IC 适用于工作在全球 2.4 GHz ISM 频段的无线设

备连接。 它适用于符合 ETSI EN 301 489-1 V1.41、 ETSI EN

300 328-1 V1.3.1 (欧洲)、 FCC CFR 47 Part 15 (美国和加

拿大)以及 TELEC ARIB_T66_March 2003(日本)所涵盖的

全球规范的系统。

CYRF7936 包含一个 2.4 GHz CyFi 无线调制解调器,它具备

以下功能:1 Mbps GFSK 无线前端、包数据缓冲、包成帧器、

DSSS 基带控制器以及接收信号强度指示 (RSSI)。 CYRF7936

具备一个用于数据传输和设备配置的 SPI 接口。

CyFi 无线调制解调器支持 98 个 1 MHz 离散频道 (某些行政

管辖权的法规可能会限制其中一些频道的使用)。

基带执行 DSSS 扩频 / 解扩、包开始 (SOP)、包结束 (EOP) 检

测以及 CRC16 生成和检查。 基带还可以配置为在接收到有效

包后立即自动发送确认 (ACK) 握手包。

当处于接收模式时,如果启用包成帧功能,设备即可随时接收

以任何可支持的比特率发送的数据。 这样就可以实现不同设备

使用不同数据速率的混合速率系统。 这还可以实现在较短距离

或在中低干扰环境 (或两种因素兼备的环境)中,使用高数据

速率的可变数据速率系统。 而在较长距离或在高干扰环境(或

两种因素兼备的环境)中,它会变为低数据速率。

此外,CYRF7936 IC 还带有电源管理装置 (PMU),可将设备直

接连接到电压在 1.8V 到 3.6V 范围内的任何电池。 PMU 会根据

设备所需的电源电压来调节电池电压,并可为外部设备供电。

数据传输模式

CyFi 无线收发器支持两种不同的数据传输模式:

■ 在 GFSK 模式中,数据以 1 Mbps 的速率传输,没有任何

DSSS。

■ 在 8DR 模式下,DSSS 使能,而且在传输的每个导出码符号

中都会有八位是经过编码的。

在 8DR 模式下支持 64 码片和 32 码片伪噪声 (PN) 编码。 通

常,在既定的环境下较低的数据速率会降低包错误率。

包成帧

CYRF7936 IC 设备支持以下数据包成帧功能:

SOP

包以两个符号的包开始 (SoP) 标记为开头。 用于 SOP 的

SOP_CODE_ADR

编码 与用 于包 “主 体”的

SOP_CODE_ADR PN 编码不同,而且如有必要,长度也可以

不同。 必须将 SOP 配置为在链路两端长度相同。

PN

长度

这是 SOP 符号之后的第一个八位,按照有效载荷数据速率传

输。 在收到长度字段中定义的字节数加上两个用于 CRC16 的

字节后,会推断一个 EoP 条件。

CRC16

可以将设备配置为 在每个包后面附加一 个 16 位 CRC16。

CRC16 使用 USB CRC 多项式,而且种子具有可编程性。 启

用后,接收器会根据 CRC16 字段中接收到的值与有效载荷数

据计算的 CRC16 做校验。 CRC16 计算的种子值是可配置的,

而且传输的 CRC16 可以使用加载的种子值或零种子来计算;

接收 到的 数据 CRC16 时会 根据 配置的 CRC16 种子和 零

CRC16 种子进行检查。

文件编号: 001-50428 修订版 **

第 3 页,共 21 页

[+] Feedback

�

CYRF7936

CRC16 可检测以下错误:

■ 任何一个错误的位。

■ 任何两个错误的位 (无论离得多远,哪个列等等)。

■ 任何奇数个错误的位 (无论位置如何)。

■ 一个与校验和自身一样等宽的错误突发。

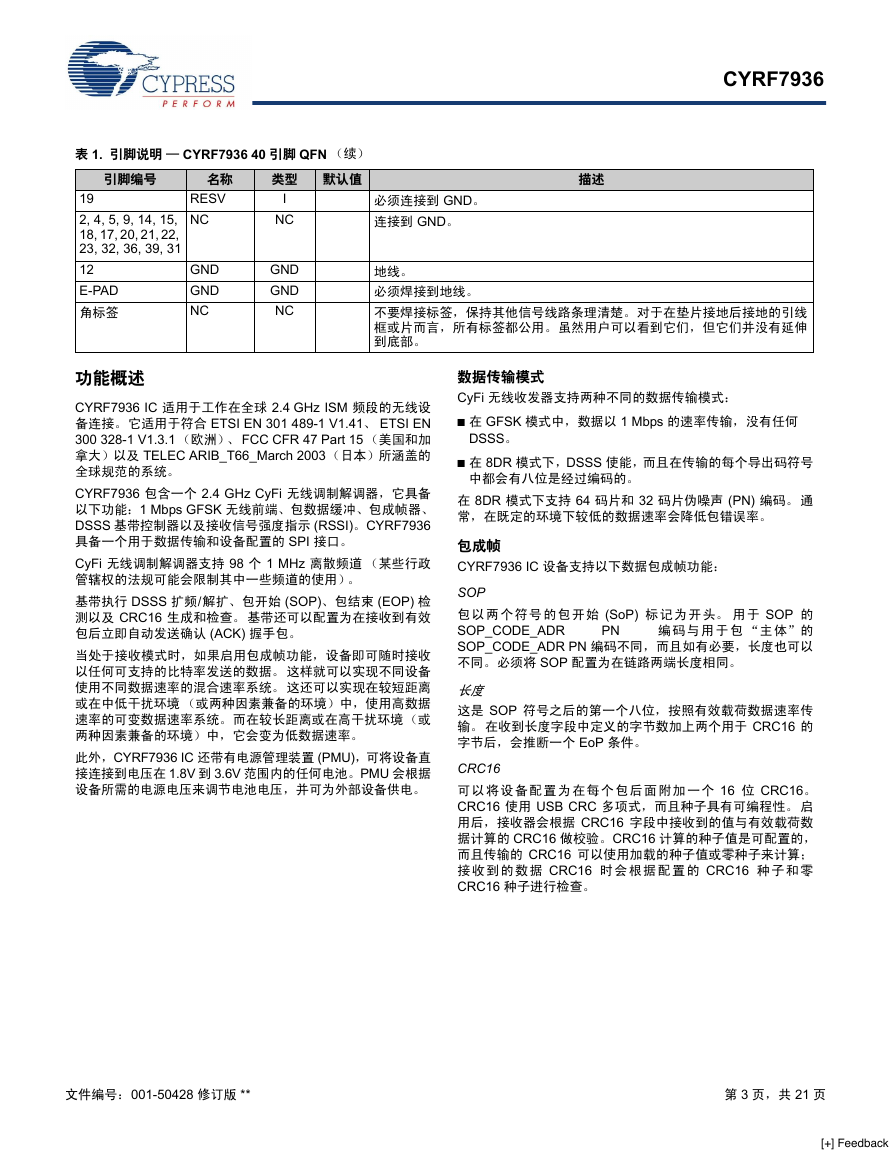

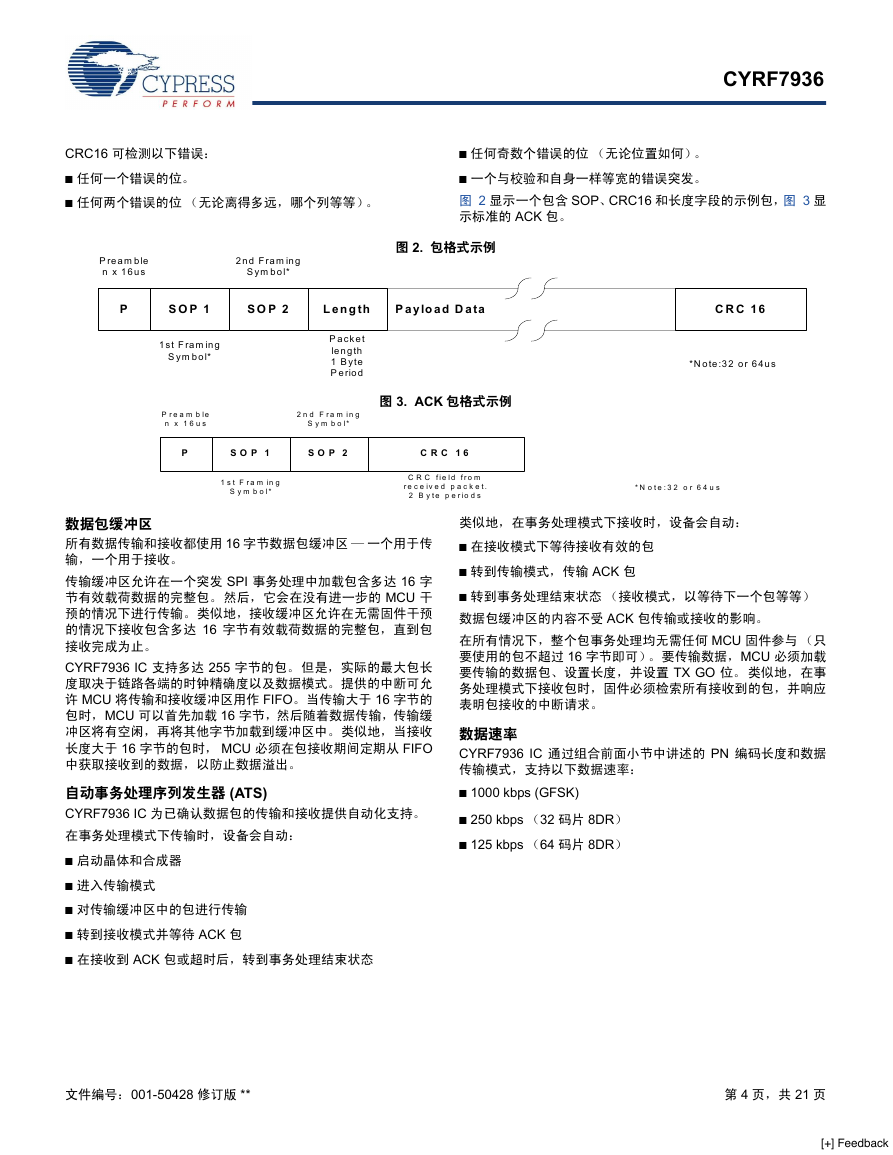

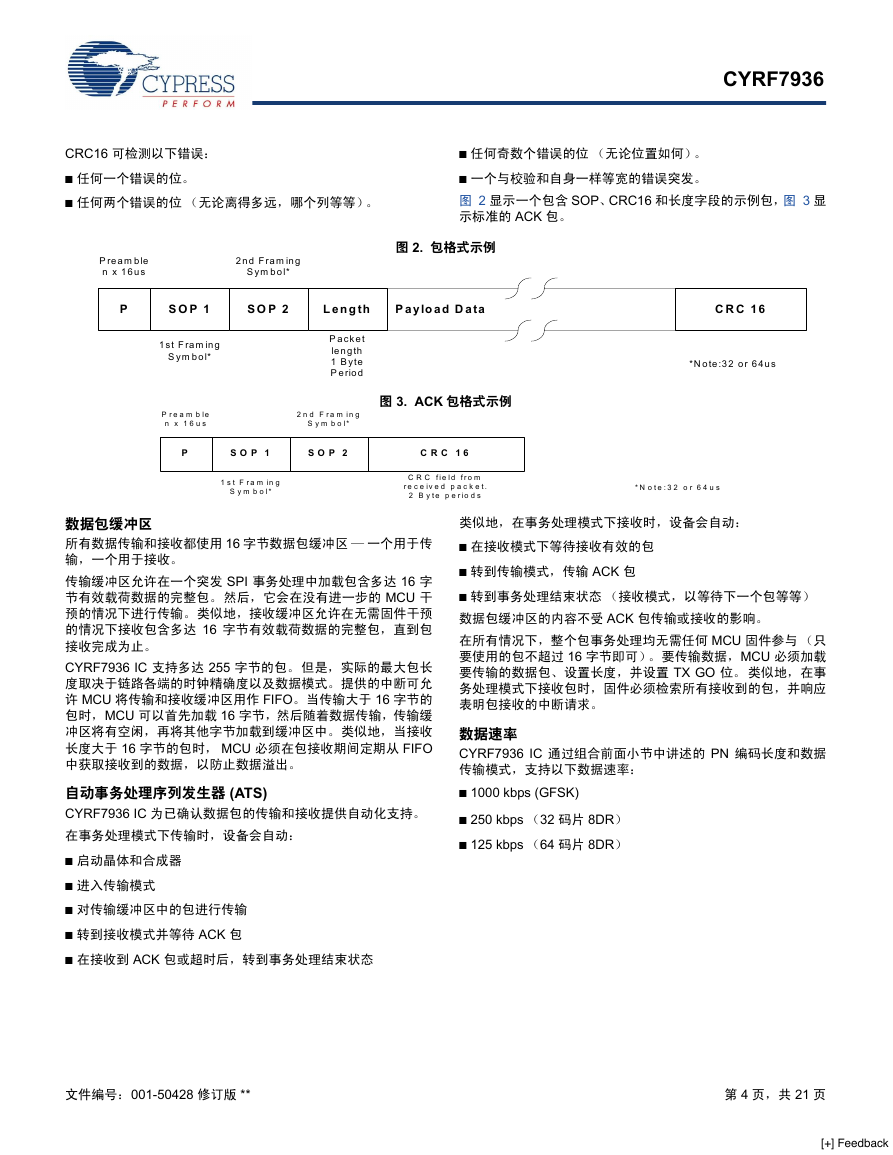

图 2 显示一个包含 SOP、CRC16 和长度字段的示例包,图 3 显

示标准的 ACK 包。

P ream ble

n x 16us

2nd F ram ing

S ym bol*

图 2. 包格式示例

P

S O P 1

S O P 2

L en g th

P aylo ad D ata

C R C 16

1st F ram ing

S ym bol*

P acket

length

1 B yte

P eriod

P r e a m b le

n x 1 6 u s

2 n d F r a m in g

S y m b o l*

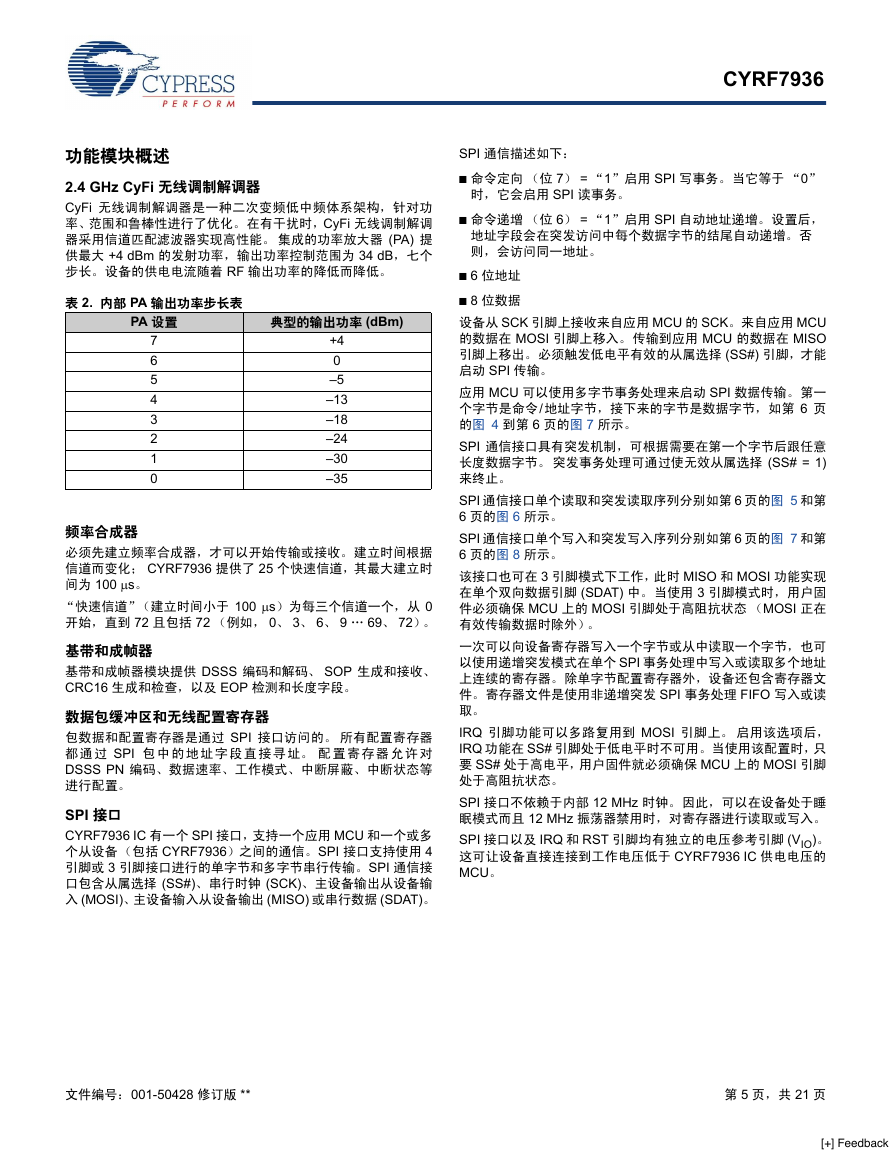

图 3. ACK 包格式示例

P

S O P 1

S O P 2

C R C 1 6

1 s t F r a m in g

S y m b o l*

C R C f ie ld f r o m

r e c e iv e d p a c k e t .

2 B y t e p e r io d s

*N ote:32 or 64us

* N o t e : 3 2 o r 6 4 u s

数据包缓冲区

所有数据传输和接收都使用 16 字节数据包缓冲区 — 一个用于传

输,一个用于接收。

传输缓冲区允许在一个突发 SPI 事务处理中加载包含多达 16 字

节有效载荷数据的完整包。 然后,它会在没有进一步的 MCU 干

预的情况下进行传输。 类似地,接收缓冲区允许在无需固件干预

的情况下接收包含多达 16 字节有效载荷数据的完整包,直到包

接收完成为止。

CYRF7936 IC 支持多达 255 字节的包。 但是,实际的最大包长

度取决于链路各端的时钟精确度以及数据模式。 提供的中断可允

许 MCU 将传输和接收缓冲区用作 FIFO。 当传输大于 16 字节的

包时,MCU 可以首先加载 16 字节,然后随着数据传输,传输缓

冲区将有空闲,再将其他字节加载到缓冲区中。 类似地,当接收

长度大于 16 字节的包时, MCU 必须在包接收期间定期从 FIFO

中获取接收到的数据,以防止数据溢出。

自动事务处理序列发生器 (ATS)

CYRF7936 IC 为已确认数据包的传输和接收提供自动化支持。

在事务处理模式下传输时,设备会自动:

■ 启动晶体和合成器

■ 进入传输模式

■ 对传输缓冲区中的包进行传输

■ 转到接收模式并等待 ACK 包

■ 在接收到 ACK 包或超时后,转到事务处理结束状态

类似地,在事务处理模式下接收时,设备会自动:

■ 在接收模式下等待接收有效的包

■ 转到传输模式,传输 ACK 包

■ 转到事务处理结束状态 (接收模式,以等待下一个包等等)

数据包缓冲区的内容不受 ACK 包传输或接收的影响。

在所有情况下,整个包事务处理均无需任何 MCU 固件参与 (只

要使用的包不超过 16 字节即可)。 要传输数据,MCU 必须加载

要传输的数据包、设置长度,并设置 TX GO 位。 类似地,在事

务处理模式下接收包时,固件必须检索所有接收到的包,并响应

表明包接收的中断请求。

数据速率

CYRF7936 IC 通过组合前面小节中讲述的 PN 编码长度和数据

传输模式,支持以下数据速率:

■ 1000 kbps (GFSK)

■ 250 kbps (32 码片 8DR)

■ 125 kbps (64 码片 8DR)

文件编号: 001-50428 修订版 **

第 4 页,共 21 页

[+] Feedback

�

CYRF7936

功能模块概述

2.4 GHz CyFi 无线调制解调器

CyFi 无线调制解调器是一种二次变频低中频体系架构,针对功

率、范围和鲁棒性进行了优化。 在有干扰时,CyFi 无线调制解调

器采用信道匹配滤波器实现高性能。 集成的功率放大器 (PA) 提

供最大 +4 dBm 的发射功率,输出功率控制范围为 34 dB,七个

步长。 设备的供电电流随着 RF 输出功率的降低而降低。

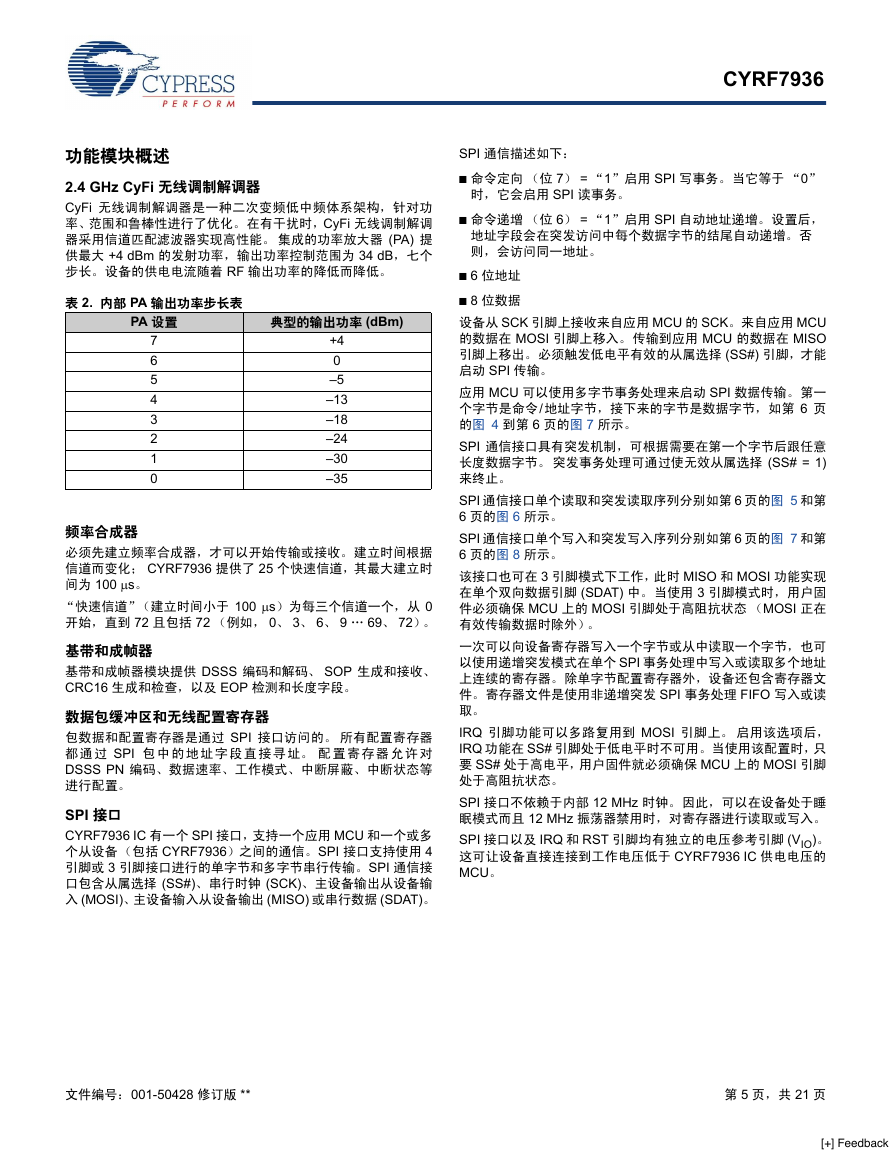

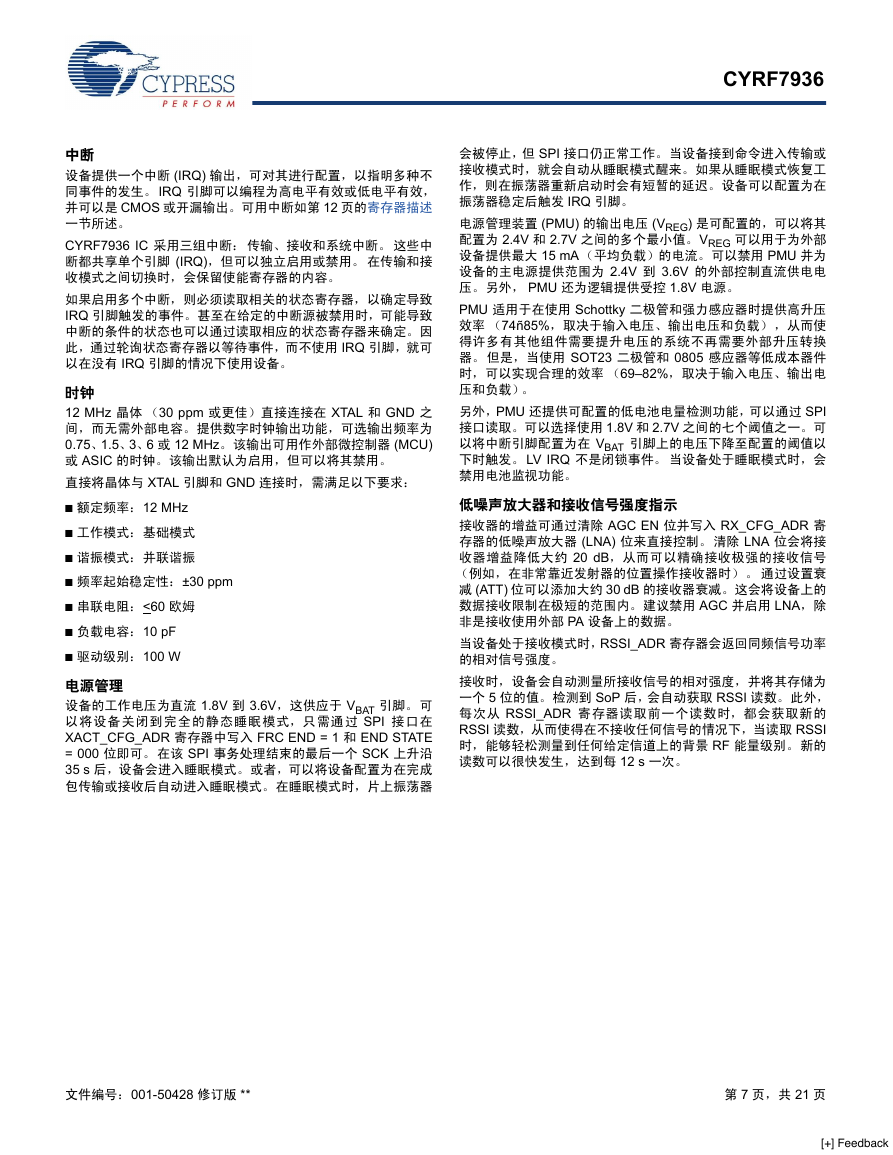

表 2. 内部 PA 输出功率步长表

PA 设置

典型的输出功率 (dBm)

7

6

5

4

3

2

1

0

+4

0

–5

–13

–18

–24

–30

–35

频率合成器

必须先建立频率合成器,才可以开始传输或接收。 建立时间根据

信道而变化; CYRF7936 提供了 25 个快速信道,其最大建立时

间为 100 μs。

“快速信道”(建立时间小于 100 μs)为每三个信道一个,从 0

开始,直到 72 且包括 72 (例如, 0、 3、 6、 9 … 69、 72)。

基带和成帧器

基带和成帧器模块提供 DSSS 编码和解码、 SOP 生成和接收、

CRC16 生成和检查,以及 EOP 检测和长度字段。

数据包缓冲区和无线配置寄存器

包数据和配置寄存器是通过 SPI 接口访问的。 所有配置寄存器

都 通 过 SPI 包中 的 地 址 字 段直 接 寻 址。 配 置 寄存 器 允 许 对

DSSS PN 编码、数据速率、工作模式、中断屏蔽、中断状态等

进行配置。

SPI 接口

CYRF7936 IC 有一个 SPI 接口,支持一个应用 MCU 和一个或多

个从设备 (包括 CYRF7936)之间的通信。 SPI 接口支持使用 4

引脚或 3 引脚接口进行的单字节和多字节串行传输。 SPI 通信接

口包含从属选择 (SS#)、串行时钟 (SCK)、主设备输出从设备输

入 (MOSI)、主设备输入从设备输出 (MISO) 或串行数据 (SDAT)。

SPI 通信描述如下:

■ 命令定向 (位 7) = “1”启用 SPI 写事务。 当它等于 “0”

时,它会启用 SPI 读事务。

■ 命令递增 (位 6) = “1”启用 SPI 自动地址递增。 设置后,

地址字段会在突发访问中每个数据字节的结尾自动递增。 否

则,会访问同一地址。

■ 6 位地址

■ 8 位数据

设备从 SCK 引脚上接收来自应用 MCU 的 SCK。 来自应用 MCU

的数据在 MOSI 引脚上移入。 传输到应用 MCU 的数据在 MISO

引脚上移出。 必须触发低电平有效的从属选择 (SS#) 引脚,才能

启动 SPI 传输。

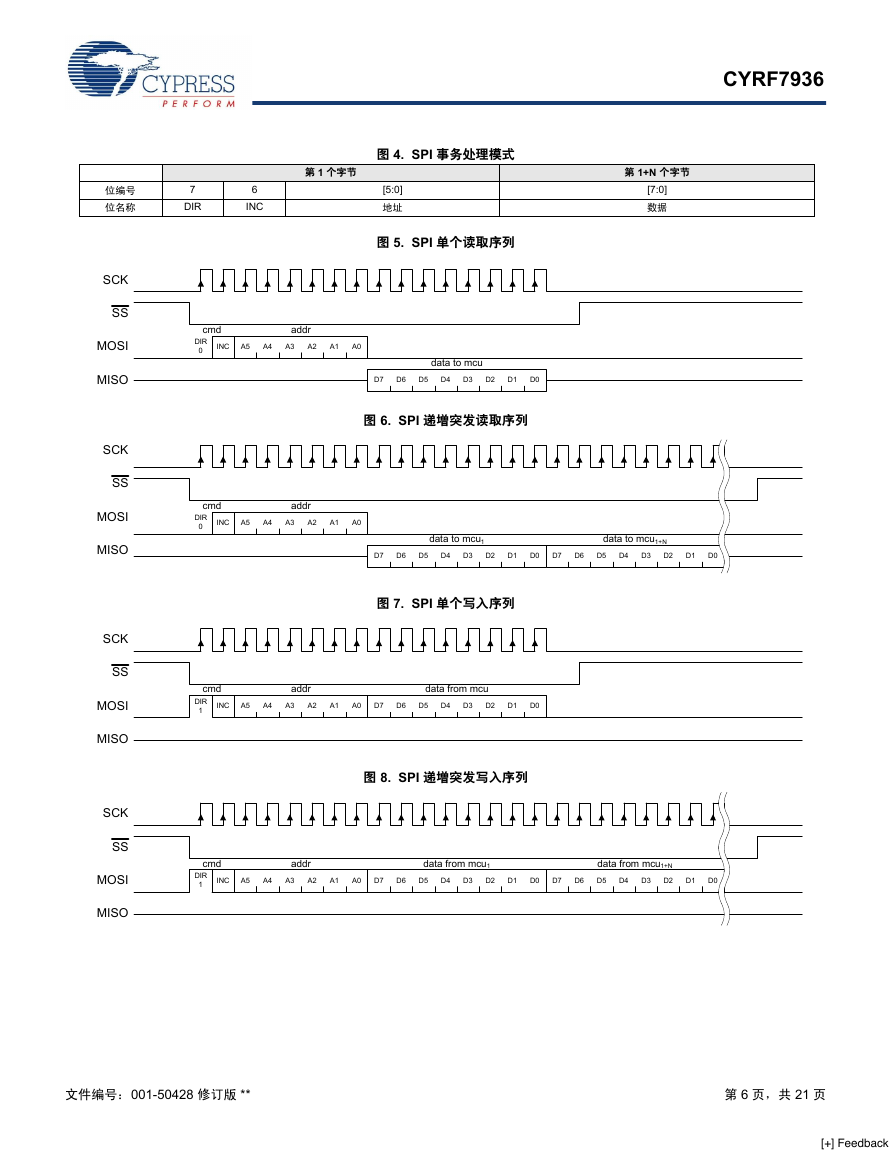

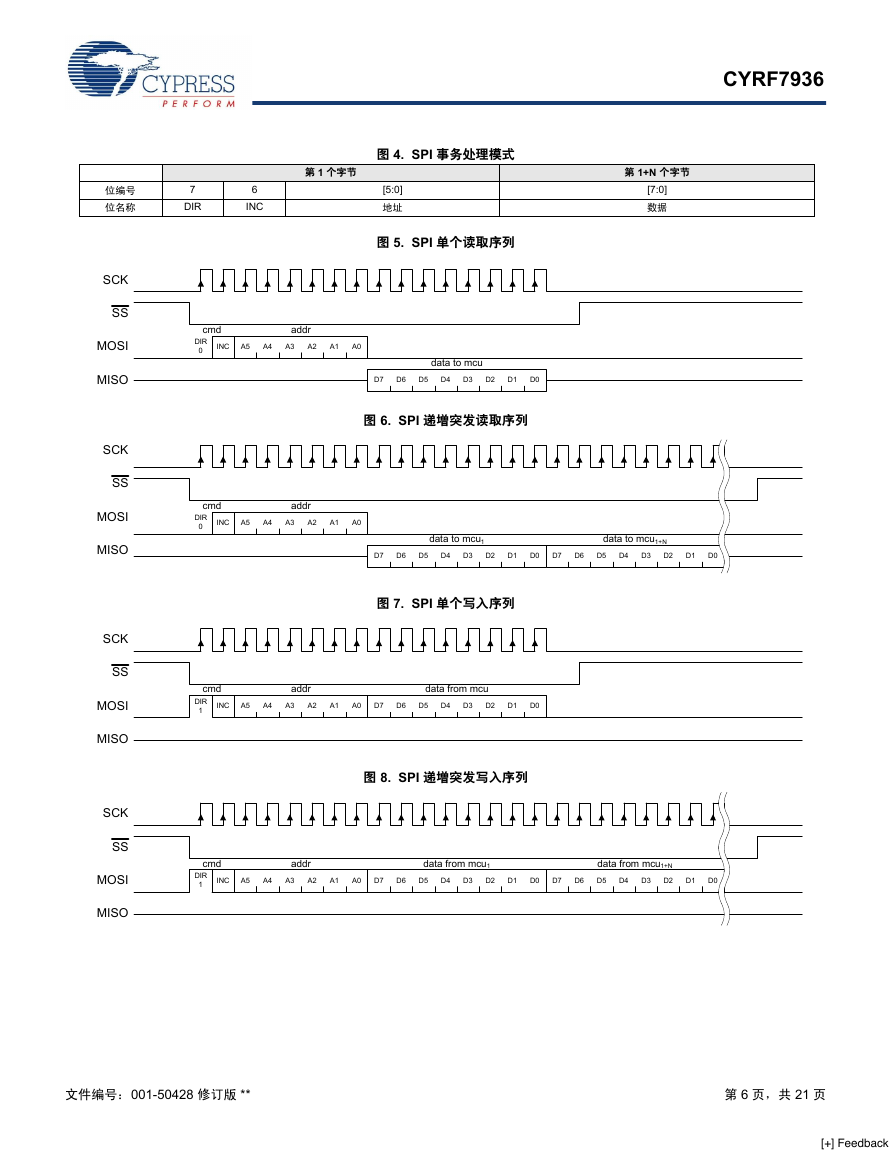

应用 MCU 可以使用多字节事务处理来启动 SPI 数据传输。 第一

个字节是命令 / 地址字节,接下来的字节是数据字节,如第 6 页

的图 4 到第 6 页的图 7 所示。

SPI 通信接口具有突发机制,可根据需要在第一个字节后跟任意

长度数据字节。 突发事务处理可通过使无效从属选择 (SS# = 1)

来终止。

SPI 通信接口单个读取和突发读取序列分别如第 6 页的图 5 和第

6 页的图 6 所示。

SPI 通信接口单个写入和突发写入序列分别如第 6 页的图 7 和第

6 页的图 8 所示。

该接口也可在 3 引脚模式下工作,此时 MISO 和 MOSI 功能实现

在单个双向数据引脚 (SDAT) 中。 当使用 3 引脚模式时,用户固

件必须确保 MCU 上的 MOSI 引脚处于高阻抗状态 (MOSI 正在

有效传输数据时除外)。

一次可以向设备寄存器写入一个字节或从中读取一个字节,也可

以使用递增突发模式在单个 SPI 事务处理中写入或读取多个地址

上连续的寄存器。 除单字节配置寄存器外,设备还包含寄存器文

件。 寄存器文件是使用非递增突发 SPI 事务处理 FIFO 写入或读

取。

IRQ 引脚功能可以多路复用到 MOSI 引脚上。 启用该选项后,

IRQ 功能在 SS# 引脚处于低电平时不可用。 当使用该配置时,只

要 SS# 处于高电平,用户固件就必须确保 MCU 上的 MOSI 引脚

处于高阻抗状态。

SPI 接口不依赖于内部 12 MHz 时钟。 因此,可以在设备处于睡

眠模式而且 12 MHz 振荡器禁用时,对寄存器进行读取或写入。

SPI 接口以及 IRQ 和 RST 引脚均有独立的电压参考引脚 (VIO)。

这可让设备直接连接到工作电压低于 CYRF7936 IC 供电电压的

MCU。

文件编号: 001-50428 修订版 **

第 5 页,共 21 页

[+] Feedback

�

CYRF7936

位编号

位名称

7

DIR

6

INC

第 1 个字节

[5:0]

地址

第 1+N 个字节

[7:0]

数据

图 4. SPI 事务处理模式

图 5. SPI 单个读取序列

SCK

SS

MOSI

MISO

SCK

SS

MOSI

MISO

SCK

SS

MOSI

MISO

SCK

SS

MOSI

MISO

cmd

DIR

0

INC

A5

A4

addr

A3

A2

A1

A0

data to mcu

D7

D6

D5

D4

D3

D2

D1

D0

图 6. SPI 递增突发读取序列

cmd

DIR

0

INC

A5

A4

addr

A3

A2

A1

A0

data to mcu1

D7

D6

D5

D4

D3

D2

D1

D0

D7

D6

图 7. SPI 单个写入序列

data to mcu1+N

D5

D2

D3

D4

cmd

DIR

1

INC

A5

A4

addr

A3

A2

A1

A0

D7

D6

data from mcu

D2

D3

D4

D5

D1

D0

图 8. SPI 递增突发写入序列

cmd

DIR

1

INC

A5

A4

addr

A3

A2

A1

A0

D7

D6

data from mcu1

D5

D2

D3

D4

D1

D0

D7

D6

data from mcu1+N

D5

D2

D3

D4

D1

D0

D1

D0

文件编号: 001-50428 修订版 **

第 6 页,共 21 页

[+] Feedback

�

CYRF7936

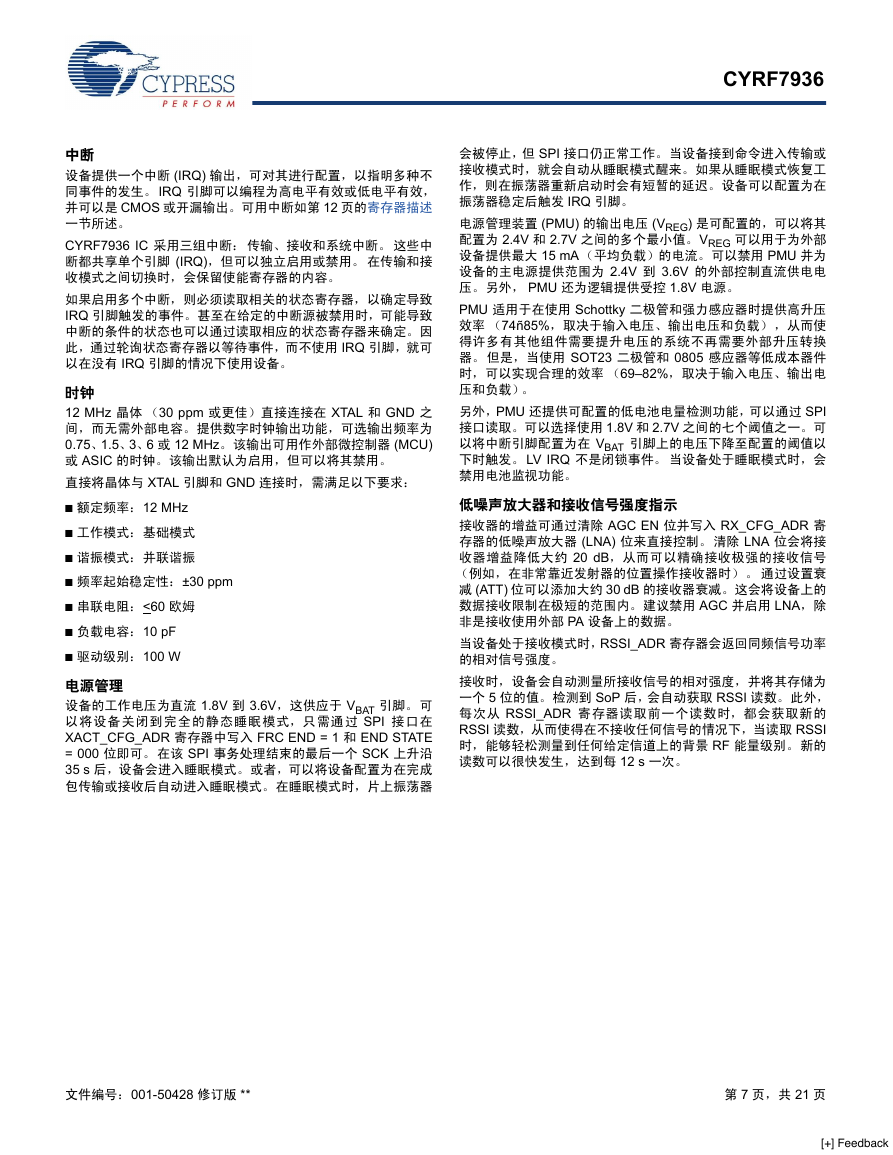

中断

设备提供一个中断 (IRQ) 输出,可对其进行配置,以指明多种不

同事件的发生。 IRQ 引脚可以编程为高电平有效或低电平有效,

并可以是 CMOS 或开漏输出。 可用中断如第 12 页的寄存器描述

一节所述。

CYRF7936 IC 采用三组中断: 传输、接收和系统中断。 这些中

断都共享单个引脚 (IRQ),但可以独立启用或禁用。 在传输和接

收模式之间切换时,会保留使能寄存器的内容。

如果启用多个中断,则必须读取相关的状态寄存器,以确定导致

IRQ 引脚触发的事件。 甚至在给定的中断源被禁用时,可能导致

中断的条件的状态也可以通过读取相应的状态寄存器来确定。 因

此,通过轮询状态寄存器以等待事件,而不使用 IRQ 引脚,就可

以在没有 IRQ 引脚的情况下使用设备。

时钟

12 MHz 晶体 (30 ppm 或更佳)直接连接在 XTAL 和 GND 之

间,而无需外部电容。 提供数字时钟输出功能,可选输出频率为

0.75、1.5、3、6 或 12 MHz。 该输出可用作外部微控制器 (MCU)

或 ASIC 的时钟。 该输出默认为启用,但可以将其禁用。

直接将晶体与 XTAL 引脚和 GND 连接时,需满足以下要求:

■ 额定频率: 12 MHz

■ 工作模式: 基础模式

■ 谐振模式: 并联谐振

■ 频率起始稳定性: ±30 ppm

■ 串联电阻: <60 欧姆

■ 负载电容: 10 pF

■ 驱动级别: 100 W

电源管理

设备的工作电压为直流 1.8V 到 3.6V,这供应于 VBAT 引脚。 可

以将设备关闭到完全的静态睡眠模式,只需通过 SPI 接口在

XACT_CFG_ADR 寄存器中写入 FRC END = 1 和 END STATE

= 000 位即可。 在该 SPI 事务处理结束的最后一个 SCK 上升沿

35 s 后,设备会进入睡眠模式。 或者,可以将设备配置为在完成

包传输或接收后自动进入睡眠模式。 在睡眠模式时,片上振荡器

会被停止,但 SPI 接口仍正常工作。 当设备接到命令进入传输或

接收模式时,就会自动从睡眠模式醒来。 如果从睡眠模式恢复工

作,则在振荡器重新启动时会有短暂的延迟。 设备可以配置为在

振荡器稳定后触发 IRQ 引脚。

电源管理装置 (PMU) 的输出电压 (VREG) 是可配置的,可以将其

配置为 2.4V 和 2.7V 之间的多个最小值。 VREG 可以用于为外部

设备提供最大 15 mA (平均负载)的电流。 可以禁用 PMU 并为

设备的主电源提供范围为 2.4V 到 3.6V 的外部控制直流供电电

压。 另外, PMU 还为逻辑提供受控 1.8V 电源。

PMU 适用于在使用 Schottky 二极管和强力感应器时提供高升压

效率 (74ñ85%,取决于输入电压、输出电压和负载),从而使

得许多有其他组件需要提升电压的系统不再需要外部升压转换

器。 但是,当使用 SOT23 二极管和 0805 感应器等低成本器件

时,可以实现合理的效率 (69–82%,取决于输入电压、输出电

压和负载)。

另外,PMU 还提供可配置的低电池电量检测功能,可以通过 SPI

接口读取。 可以选择使用 1.8V 和 2.7V 之间的七个阈值之一。 可

以将中断引脚配置为在 VBAT 引脚上的电压下降至配置的阈值以

下时触发。 LV IRQ 不是闭锁事件。 当设备处于睡眠模式时,会

禁用电池监视功能。

低噪声放大器和接收信号强度指示

接收器的增益可通过清除 AGC EN 位并写入 RX_CFG_ADR 寄

存器的低噪声放大器 (LNA) 位来直接控制。 清除 LNA 位会将接

收器增益降低大约 20 dB,从而可以精确接收极强的接收信号

(例如,在非常靠近发射器的位置操作接收器时)。 通过设置衰

减 (ATT) 位可以添加大约 30 dB 的接收器衰减。 这会将设备上的

数据接收限制在极短的范围内。 建议禁用 AGC 并启用 LNA,除

非是接收使用外部 PA 设备上的数据。

当设备处于接收模式时,RSSI_ADR 寄存器会返回同频信号功率

的相对信号强度。

接收时,设备会自动测量所接收信号的相对强度,并将其存储为

一个 5 位的值。 检测到 SoP 后,会自动获取 RSSI 读数。 此外,

每次从 RSSI_ADR 寄存器读取前一个读数时,都会获取新的

RSSI 读数,从而使得在不接收任何信号的情况下,当读取 RSSI

时,能够轻松测量到任何给定信道上的背景 RF 能量级别。 新的

读数可以很快发生,达到每 12 s 一次。

文件编号: 001-50428 修订版 **

第 7 页,共 21 页

[+] Feedback

�

CYRF7936

应用示例

图 9. VBAT ≤ 2.4V 时的推荐系统电路

6

3

9

7

F

R

Y

C

文件编号: 001-50428 修订版 **

第 8 页,共 21 页

[+] Feedback

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc