内容

1 介绍

1.1 特性

1.2 应用范围

1.3 支持国防、航天和医疗应用

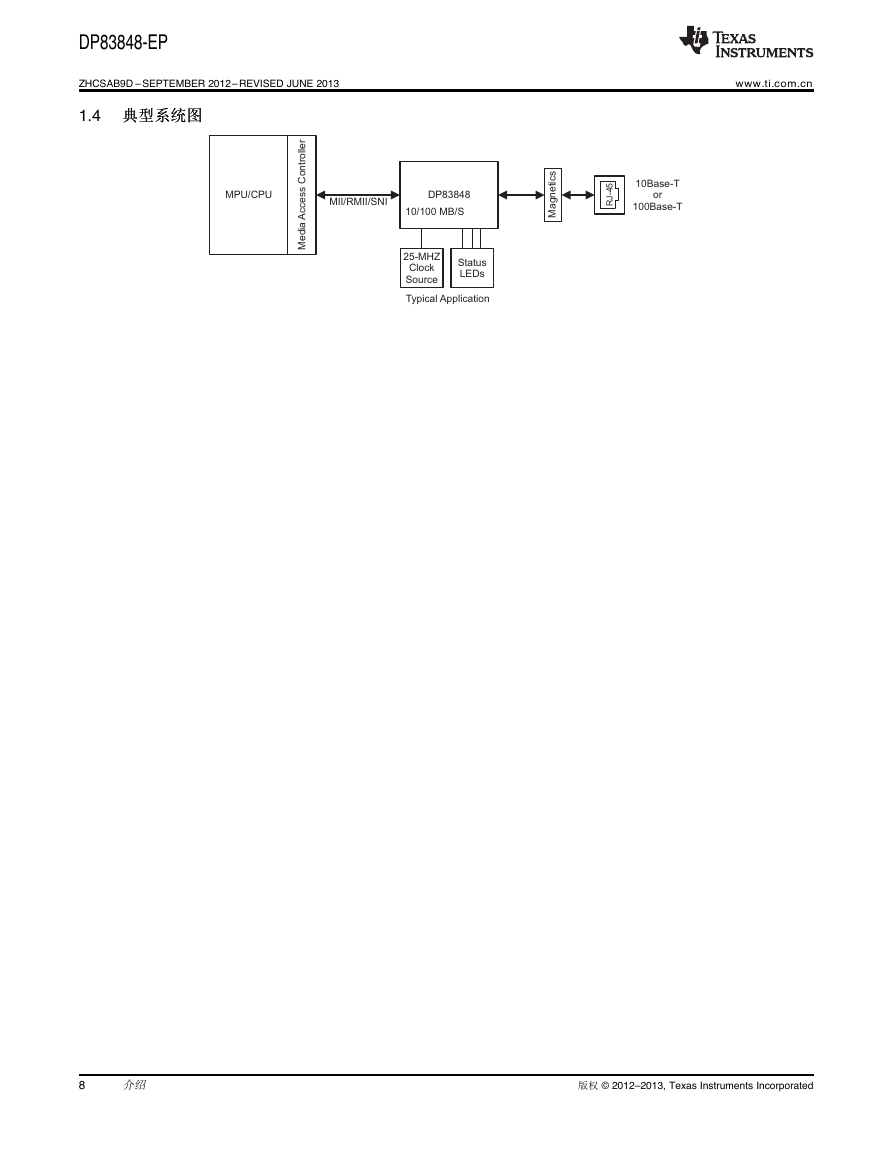

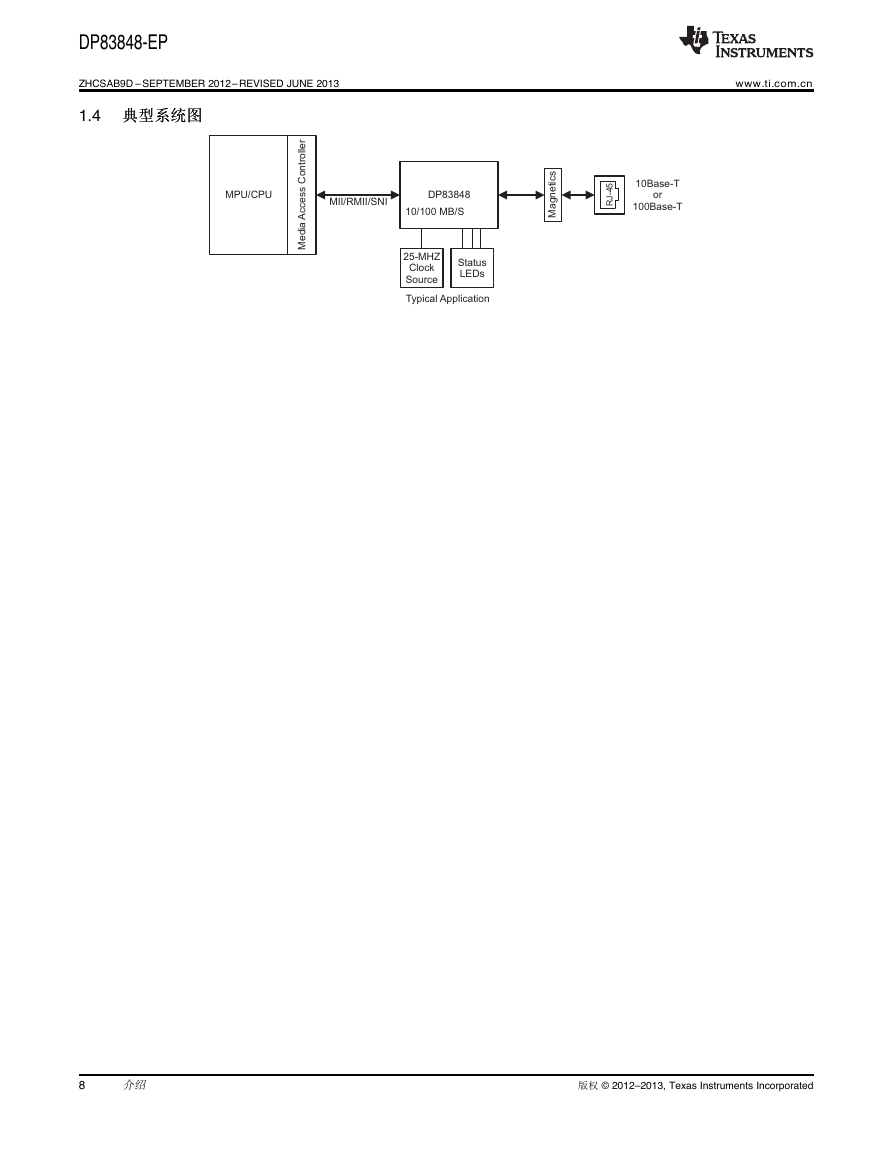

1.4 典型系统图

2 概述

2.1 描述

2.2 订购信息

2.3 器件信息

2.4 端子说明

3 ELECTRICAL SPECIFICATIONS

3.1 Absolute Maximum Ratings

3.2 Recommended Operating Conditions

3.3 Thermal Information

3.4 DC Specifications

3.4.1 Electrical Characteristics

3.5 AC Specifications

3.5.1 Power Up Timing

3.5.2 Reset Timing

3.5.3 MII Serial Management Timing

3.5.4 100 Mb/s MII Transmit Timing

3.5.5 100 Mb/s MII Receive Timing

3.5.6 100BASE-TX Transmit Packet Latency Timing

3.5.7 100BASE-TX Transmit Packet Deassertion Timing

3.5.8 100BASE-TX Transmit Timing (tR/F & Jitter)

3.5.9 100BASE-TX Receive Packet Latency Timing

3.5.10 100BASE-TX Receive Packet Deassertion Timing

3.5.11 10 Mb/s MII Transmit Timing

3.5.12 10 Mb/s MII Receive Timing

3.5.13 10 Mb/s Serial Mode Transmit Timing

3.5.14 10 Mb/s Serial Mode Receive Timing

3.5.15 10BASE-T Transmit Timing (Start of Packet)

3.5.16 10BASE-T Transmit Timing (End of Packet)

3.5.17 10BASE-T Receive Timing (Start of Packet)

3.5.18 10BASE-T Receive Timing (End of Packet)

3.5.19 10 Mb/s Heartbeat Timing

3.5.20 10 Mb/s Jabber Timing

3.5.21 10BASE-T Normal Link Pulse Timing

3.5.22 Auto-Negotiation Fast Link Pulse (FLP) Timing

3.5.23 100BASE-TX Signal Detect Timing

3.5.24 100 Mb/s Internal Loopback Timing

3.5.25 10 Mb/s Internal Loopback Timing

3.5.26 RMII Transmit Timing

3.5.27 RMII Receive Timing

3.5.28 Isolation Timing

3.5.29 25 MHz_OUT Timing

4 CONFIGURATION

4.1 Auto-Negotiation

4.1.1 Auto-Negotiation Pin Control

4.1.2 Auto-Negotiation Register Control

4.1.3 Auto-Negotiation Parallel Detection

4.1.4 Auto-Negotiation Restart

4.1.5 Enabling Auto-Negotiation via Software

4.1.6 Auto-Negotiation Complete Time

4.2 Auto-MDIX

4.3 PHY Address

4.3.1 MII Isolate Mode

4.4 LED Interface

4.4.1 LEDs

4.4.2 LED Direct Control

4.5 Half Duplex vs Full Duplex

4.6 Internal Loopback

4.7 BIST

5 FUNCTIONAL DESCRIPTION

5.1 MII Interface

5.1.1 Nibble-Wide MII Data Interface

5.1.2 Collision Detect

5.1.3 Carrier Sense

5.2 Reduced MII Interface

5.3 10 Mb Serial Network Interface (SNI)

5.4 802.3u MII Serial Management Interface

5.4.1 Serial Management Register Access

5.4.2 Serial Management Access Protocol

5.4.3 Serial Management Preamble Suppression

6 ARCHITECTURE

6.1 100BASE-TX Transmitter

6.1.1 Code-Group Encoding and Injection

6.1.2 Scrambler

6.1.3 NRZ to NRZI Encoder

6.1.4 Binary to MLT-3 Convertor

6.2 100BASE-TX Receiver

6.2.1 Analog Front End

6.2.2 Digital Signal Processor

6.2.2.1 Digital Adaptive Equalization and Gain Control

6.2.2.2 Base Line Wander Compensation

6.2.3 Signal Detect

6.2.4 MLT-3 to NRZI Decoder

6.2.5 NRZI to NRZ

6.2.6 Serial to Parallel

6.2.7 Descrambler

6.2.8 Code-Group Alignment

6.2.9 4B/5B Decoder

6.2.10 100BASE-TX Link Integrity Monitor

6.2.11 Bad SSD Detection

6.3 10BASE-T Transceiver Module

6.3.1 Operational Modes

6.3.1.1 Half Duplex Mode

6.3.1.2 Full Duplex Mode

6.3.2 Smart Squelch

6.3.3 Collision Detection and SQE

6.3.4 Carrier Sense

6.3.5 Normal Link Pulse Detection/Generation

6.3.6 Jabber Function

6.3.7 Automatic Link Polarity Detection and Correction

6.3.8 Transmit and Receive Filtering

6.3.9 Transmitter

6.3.10 Receiver

7 DESIGN GUIDELINES

7.1 TPI Network Circuit

7.2 ESD Protection

7.3 Clock In (X1) Requirements

7.3.1 Oscillator

7.3.2 Crystal

7.4 Power Feedback Circuit

7.5 Power Down and Interrupt

7.5.1 Power Down Control Mode

7.5.2 Interrupt Mechanisms

7.6 Energy Detect Mode

7.7 Thermal Vias Recommendation

8 RESET OPERATION

8.1 Hardware Reset

8.2 Software Reset

9 REGISTER BLOCK

9.1

9.2 Register Definition

9.2.1 Basic Mode Control Register (BMCR)

9.2.2 Basic Mode Status Register (BMSR)

9.2.3 PHY Identifier Register #1 (PHYIDR1)

9.2.4 PHY Identifier Register #2 (PHYIDR2)

9.2.5 Auto-Negotiation Advertisement Register (ANAR)

9.2.6 Auto-Negotiation Link Partner Ability Register (ANLPAR) (BASE Page)

9.2.7 Auto-Negotiation Link Partner Ability Register (ANLPAR) (Next Page)

9.2.8 Auto-Negotiate Expansion Register (ANER)

9.2.9 Auto-Negotiation Next Page Transmit Register (ANNPTR)

9.3 Extended Registers

9.3.1 PHY Status Register (PHYSTS)

9.3.2 MII Interrupt Control Register (MICR)

9.3.3 MII Interrupt Status and Miscellaneous Control Register (MISR)

9.3.4 False Carrier Sense Counter Register (FCSCR)

9.3.5 Receiver Error Counter Register (RECR)

9.3.6 100 Mb/s PCS Configuration and Status Register (PCSR)

9.3.7 RMII and Bypass Register (RBR)

9.3.8 LED Direct Control Register (LEDCR)

9.3.9 PHY Control Register (PHYCR)

9.3.10 10Base-T Status/Control Register (10BTSCR)

9.3.11 CD Test and BIST Extensions Register (CDCTRL1)

9.3.12 Energy Detect Control (EDCR)

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc