ASR Microelectronics Confidential

密级状态:绝密( ) 秘密( √ ) 内部资料(√) 公开()

文档编号: (芯片型号) –ASR6505(英文、数字)

ASR6505 硬件设计指南

文件状态:

当前版本:

V1.2

[√] 正在修改

作者:

ASR6505 AE Team

[ ] 正式发布

启动日期:

2019‐5‐03

审核:

完成日期:

2019‐10‐08

翱捷科技(上海)有限公司

ASR Microelectronics Co., Ltd

(版本所有,翻版必究)

1 / 12

�

ASR Microelectronics Confidential

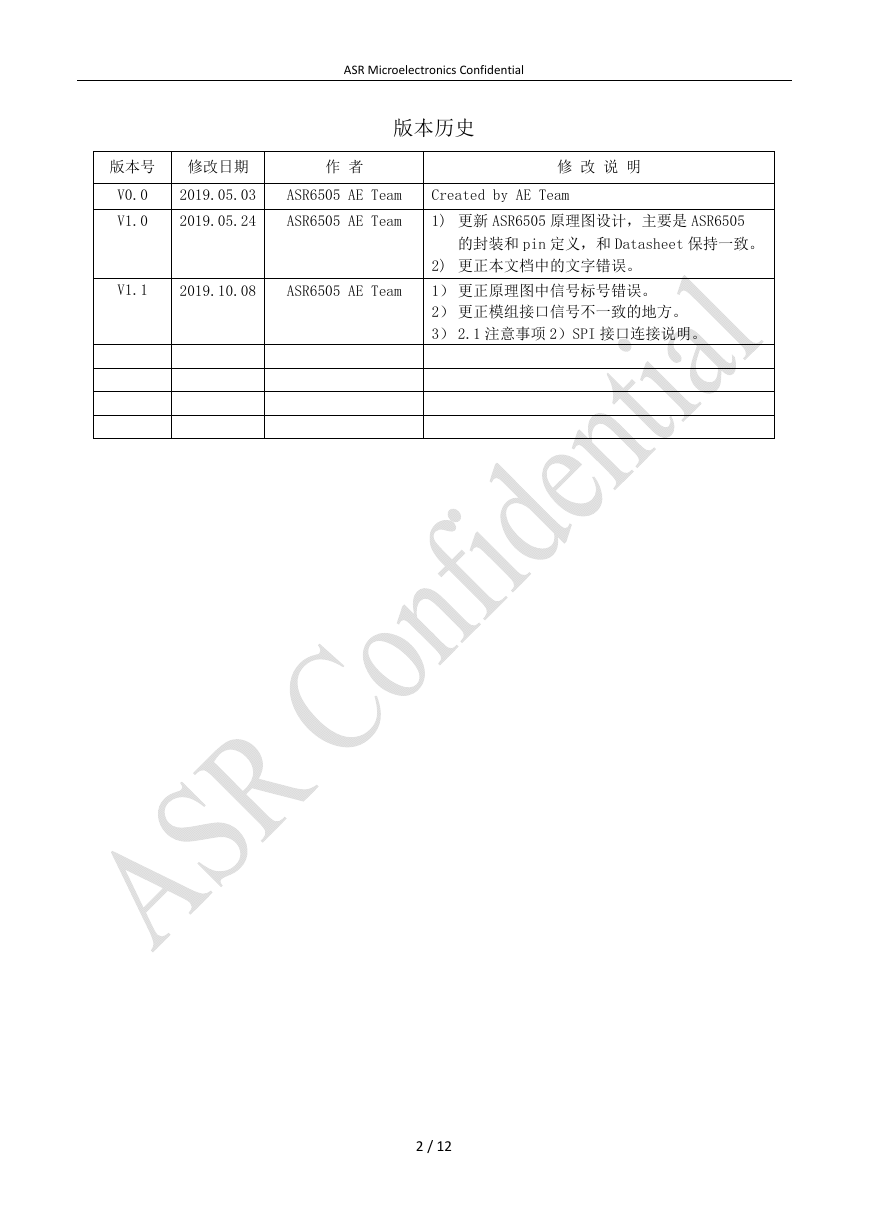

版本历史

版本号 修改日期

作 者

修 改 说 明

V0.0

2019.05.03

ASR6505 AE Team

V1.0

2019.05.24

ASR6505 AE Team

Created by AE Team

1) 更新 ASR6505 原理图设计,主要是 ASR6505

V1.1

2019.10.08

ASR6505 AE Team

的封装和 pin 定义,和 Datasheet 保持一致。

2) 更正本文档中的文字错误。

1) 更正原理图中信号标号错误。

2) 更正模组接口信号不一致的地方。

3) 2.1 注意事项 2)SPI 接口连接说明。

2 / 12

�

ASR Microelectronics Confidential

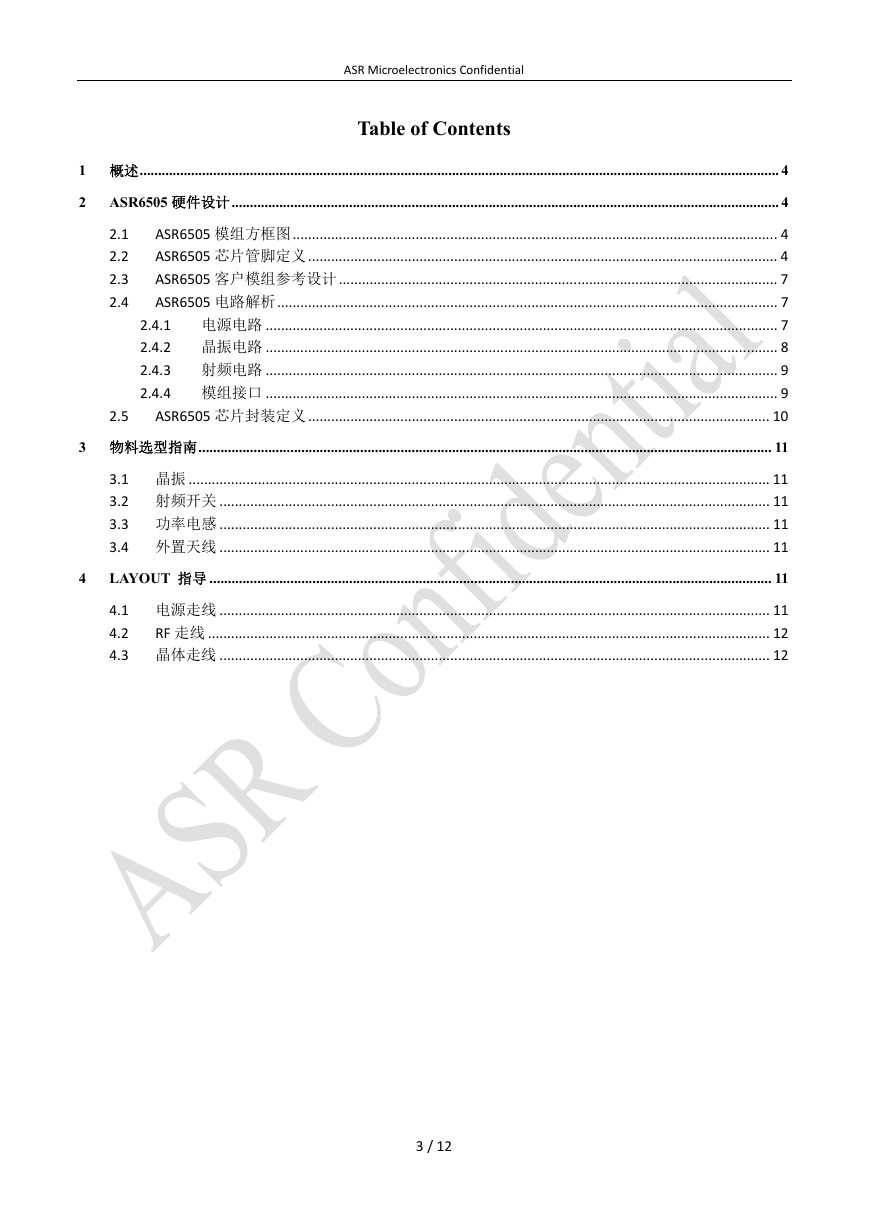

Table of Contents

1 概述 .............................................................................................................................................................................. 4

2 ASR6505 硬件设计 ..................................................................................................................................................... 4

2.1

2.2

2.3

2.4

ASR6505 模组方框图 .............................................................................................................................. 4

ASR6505 芯片管脚定义 .......................................................................................................................... 4

ASR6505 客户模组参考设计 .................................................................................................................. 7

ASR6505 电路解析 .................................................................................................................................. 7

2.4.1 电源电路 ..................................................................................................................................... 7

2.4.2 晶振电路 ..................................................................................................................................... 8

2.4.3 射频电路 ..................................................................................................................................... 9

2.4.4 模组接口 ..................................................................................................................................... 9

ASR6505 芯片封装定义 ........................................................................................................................ 10

3 物料选型指南 ............................................................................................................................................................ 11

2.5

3.1 晶振 ....................................................................................................................................................... 11

3.2 射频开关 ............................................................................................................................................... 11

3.3 功率电感 ............................................................................................................................................... 11

3.4 外置天线 ............................................................................................................................................... 11

LAYOUT 指导 ......................................................................................................................................................... 11

4.1 电源走线 ............................................................................................................................................... 11

4.2

RF 走线 .................................................................................................................................................. 12

4.3 晶体走线 ............................................................................................................................................... 12

4

3 / 12

�

ASR Microelectronics Confidential

1 概述

ASR6505 是一款通用的 LoRa 无线通讯芯片, 该芯片集成了 LoRa 射频收发器, LoRa 调制解调器和 8 位的

RISC MCU。 MCU 采用 ST 的 STM8L152 系列芯片,Harvard architecture and 3‐stage pipeline; Max freq: 16 MHz, 16

CISC MIPS peak, up to 64‐KB Flash, 2‐KB data EEPROM, RTC, LCD, timers, USARTs, I2C, SPIs, ADC, DAC, comparators;LoRa

射频收发器的频率覆盖 150M‐960M 的连续频段;LoRa 调制解调器除支持 LoRa 调制还支持(G)FSK 调制。

ASR6505 在 SF12 下接受灵敏超过‐140dBm,最大的发送功率为 22dBm,最大的工作电流为 108mA,Sleep

mode 下电流低至 1.8uA,因此 ASR6505 芯片特别适合超远距离,超低功耗,高性价比的 LPWAN 应用。

该应用笔记主要用于指导客户进行ASR6505的硬件设计,包括原理图参考设计,layout注意事项,以及

重要物料选型和替换。

2 ASR6505 硬件设计

2.1 ASR6505 模组方框图

ASR6505 LoRa 模组方框图如下:

图 2‐1‐1 ASR6505 模组方框图

注意事项:

1)ASR6505 是基于LoRa 射频芯片SX1262 和STM8L152 的SIP 封装的LoRa 芯片组,因此ASR6505 的射频性

能和Semtech SX1262 性能基本一样,MCU 的参数也和STM 的STM8L152 芯片性能一致。

2)LoRa 射频芯片(SX1262)和 MCU 芯片(STM8L152)两者通过 SPI 接口进行通讯,SX1262 和STM8L152 的

SPI 信号除SPI0_NSS 外都在芯片内部相连,特别注意SPI0_NSS 必须连到SPI0_SEL。

3)ASR6505 不支持ClassB。

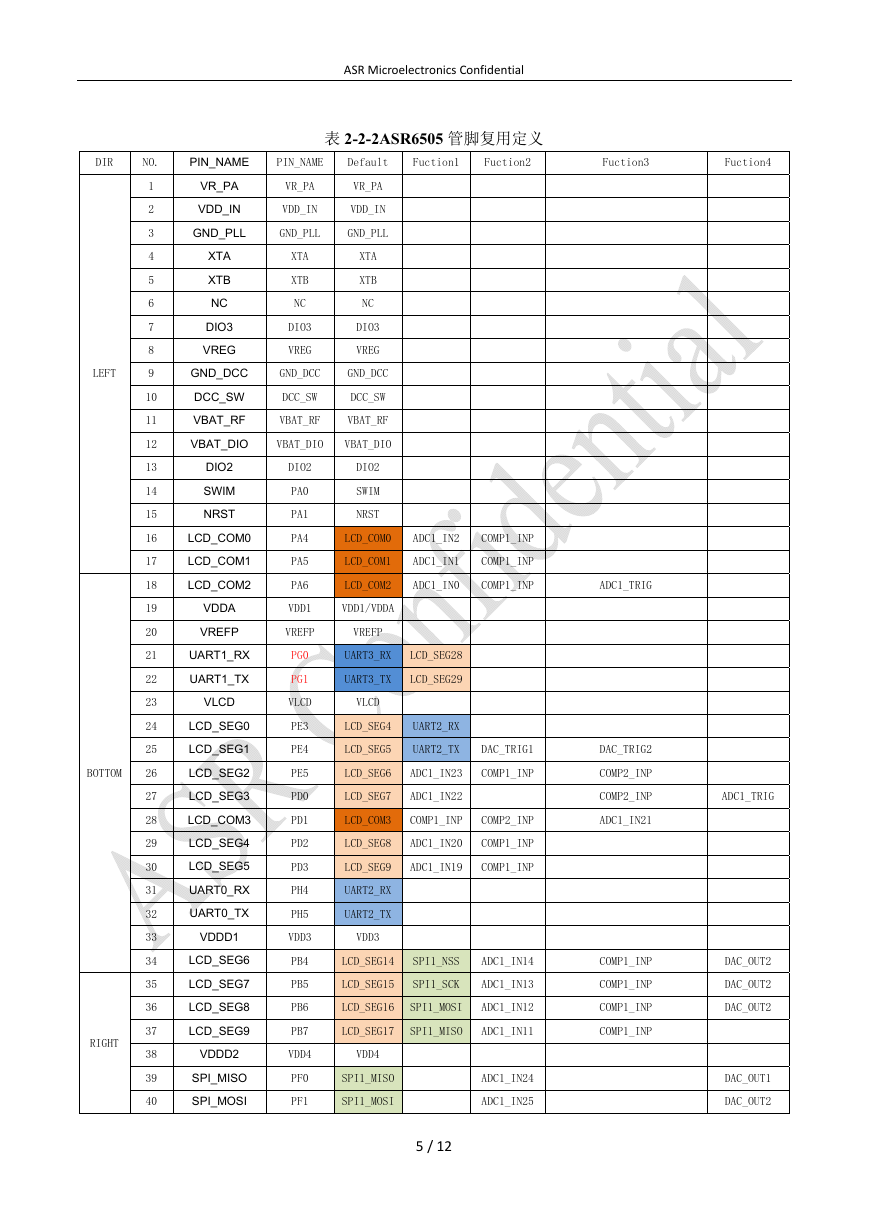

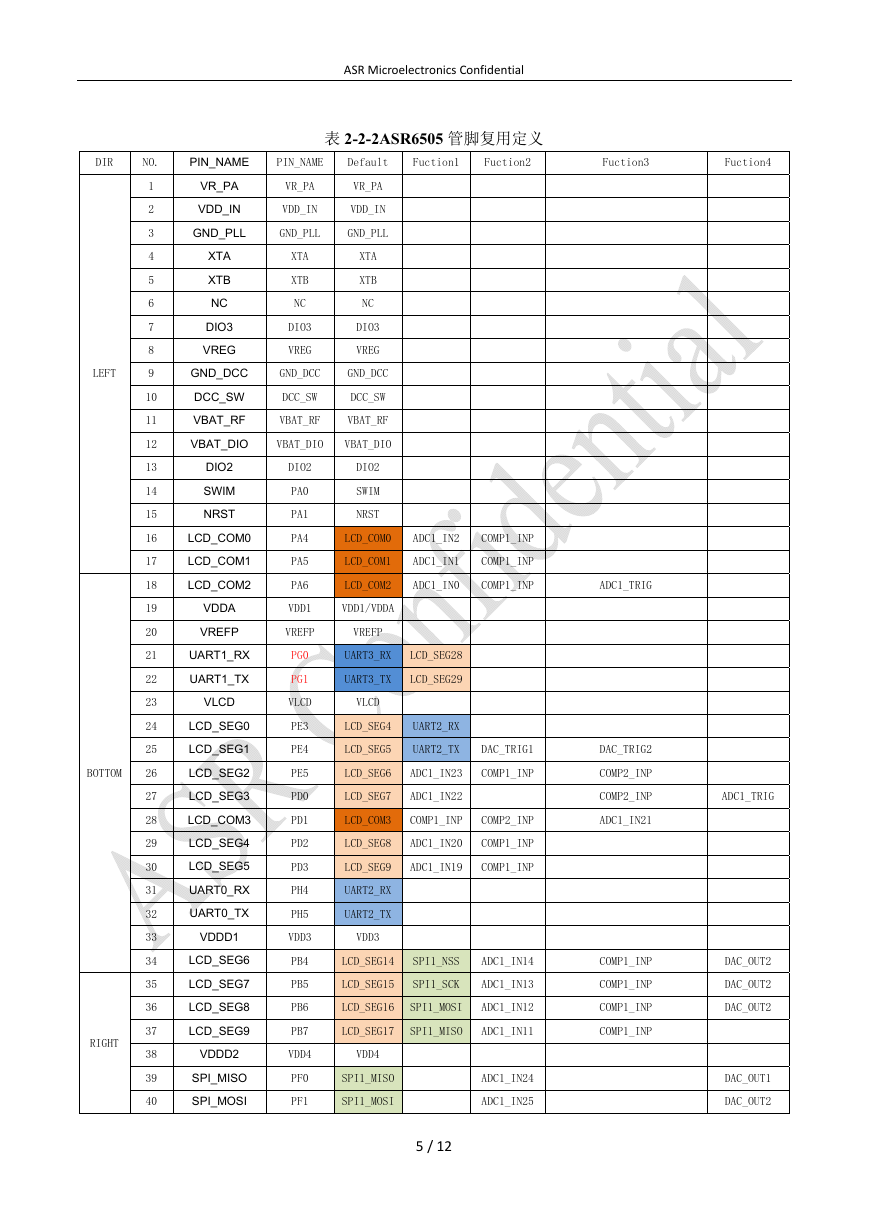

2.2 ASR6505 芯片管脚定义

表2-2-1 ASR6501管脚类型定义

Pin Type

I

O

I/O

P

G

Description

Input

Output

Input/output

Power

Ground

4 / 12

�

ASR Microelectronics Confidential

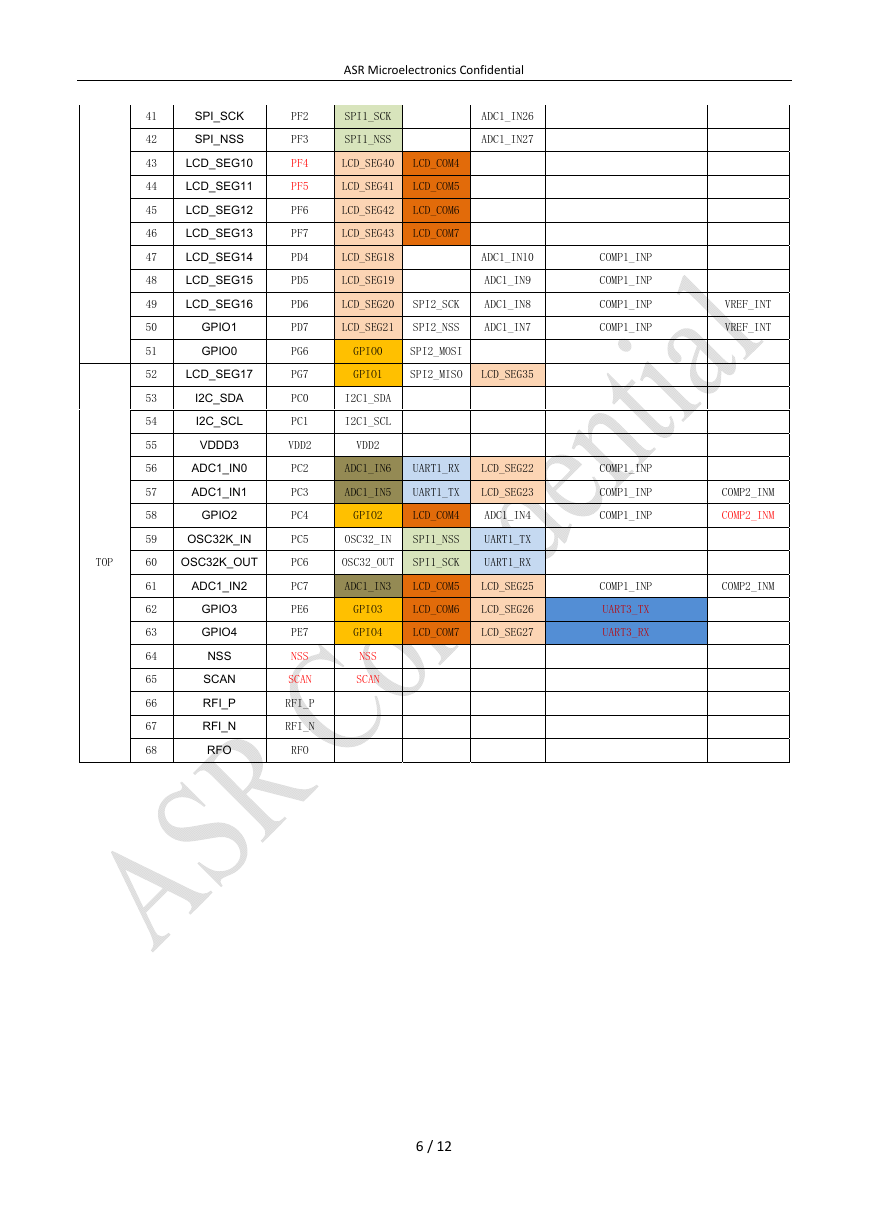

表 2-2-2ASR6505 管脚复用定义

DIR

NO.

PIN_NAME

PIN_NAME

Default

Fuction1

Fuction2

Fuction3

Fuction4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

LEFT

BOTTOM

RIGHT

XTA

XTB

NC

DIO3

VREG

GND_DCC

DCC_SW

VBAT_RF

VBAT_DIO

DIO2

SWIM

NRST

LCD_COM0

LCD_COM1

LCD_COM2

VDDA

VREFP

UART1_RX

UART1_TX

VLCD

LCD_SEG0

LCD_SEG1

LCD_SEG2

LCD_SEG3

LCD_COM3

LCD_SEG4

LCD_SEG5

UART0_RX

UART0_TX

VDDD1

LCD_SEG6

LCD_SEG7

LCD_SEG8

LCD_SEG9

VDDD2

SPI_MISO

SPI_MOSI

VR_PA

VDD_IN

GND_PLL

VR_PA

VR_PA

VDD_IN

VDD_IN

GND_PLL

GND_PLL

XTA

XTB

NC

DIO3

VREG

XTA

XTB

NC

DIO3

VREG

GND_DCC

GND_DCC

DCC_SW

DCC_SW

VBAT_RF

VBAT_RF

VBAT_DIO

VBAT_DIO

DIO2

SWIM

NRST

DIO2

PA0

PA1

PA4

PA5

PA6

PE3

PE4

PE5

PD0

PD1

PD2

PD3

PH4

PH5

VDD1

VDD1/VDDA

VREFP

VREFP

PG0

PG1

UART3_RX

LCD_SEG28

UART3_TX

LCD_SEG29

VLCD

VLCD

LCD_SEG4

UART2_RX

LCD_SEG5

UART2_TX

DAC_TRIG1

LCD_SEG6

ADC1_IN23

COMP1_INP

LCD_SEG7

ADC1_IN22

LCD_COM3

COMP1_INP

COMP2_INP

LCD_SEG8

ADC1_IN20

COMP1_INP

LCD_SEG9

ADC1_IN19

COMP1_INP

UART2_RX

UART2_TX

VDD3

VDD3

PB4

PB5

PB6

PB7

LCD_SEG14

SPI1_NSS

ADC1_IN14

LCD_SEG15

SPI1_SCK

ADC1_IN13

LCD_SEG16 SPI1_MOSI

ADC1_IN12

LCD_SEG17 SPI1_MISO

ADC1_IN11

VDD4

VDD4

PF0

PF1

SPI1_MISO

SPI1_MOSI

ADC1_IN24

ADC1_IN25

5 / 12

LCD_COM0

ADC1_IN2

COMP1_INP

LCD_COM1

ADC1_IN1

COMP1_INP

LCD_COM2

ADC1_IN0

COMP1_INP

ADC1_TRIG

DAC_TRIG2

COMP2_INP

COMP2_INP

ADC1_IN21

COMP1_INP

COMP1_INP

COMP1_INP

COMP1_INP

ADC1_TRIG

DAC_OUT2

DAC_OUT2

DAC_OUT2

DAC_OUT1

DAC_OUT2

�

ASR Microelectronics Confidential

SPI1_SCK

SPI1_NSS

ADC1_IN26

ADC1_IN27

LCD_SEG40

LCD_COM4

LCD_SEG41

LCD_COM5

LCD_SEG42

LCD_COM6

LCD_SEG43

LCD_COM7

LCD_SEG18

LCD_SEG19

ADC1_IN10

ADC1_IN9

LCD_SEG20

SPI2_SCK

ADC1_IN8

LCD_SEG21

SPI2_NSS

ADC1_IN7

GPIO0

SPI2_MOSI

GPIO1

SPI2_MISO

LCD_SEG35

ADC1_IN6

UART1_RX

LCD_SEG22

ADC1_IN5

UART1_TX

LCD_SEG23

GPIO2

LCD_COM4

ADC1_IN4

OSC32_IN

SPI1_NSS

UART1_TX

OSC32_OUT

SPI1_SCK

UART1_RX

I2C1_SDA

I2C1_SCL

VDD2

VDD2

PF2

PF3

PF4

PF5

PF6

PF7

PD4

PD5

PD6

PD7

PG6

PG7

PC0

PC1

PC2

PC3

PC4

PC5

PC6

PC7

PE6

PE7

NSS

SCAN

RFI_P

RFI_N

RFO

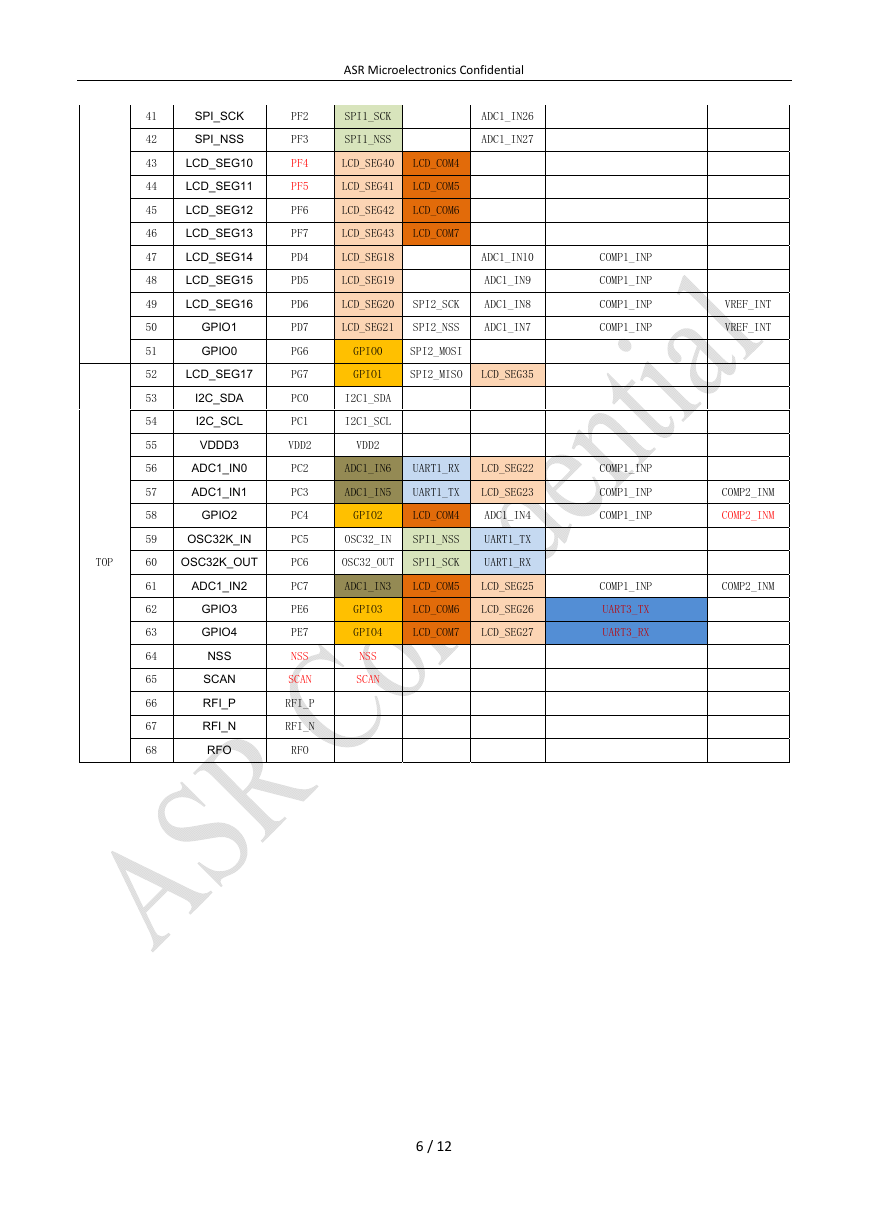

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

SPI_SCK

SPI_NSS

LCD_SEG10

LCD_SEG11

LCD_SEG12

LCD_SEG13

LCD_SEG14

LCD_SEG15

LCD_SEG16

GPIO1

GPIO0

LCD_SEG17

I2C_SDA

I2C_SCL

VDDD3

ADC1_IN0

ADC1_IN1

GPIO2

59

OSC32K_IN

60 OSC32K_OUT

ADC1_IN2

61

62

63

64

65

66

67

68

GPIO3

GPIO4

NSS

SCAN

RFI_P

RFI_N

RFO

TOP

COMP1_INP

COMP1_INP

COMP1_INP

COMP1_INP

COMP1_INP

COMP1_INP

COMP1_INP

VREF_INT

VREF_INT

COMP2_INM

COMP2_INM

ADC1_IN3

LCD_COM5

LCD_SEG25

COMP1_INP

COMP2_INM

GPIO3

LCD_COM6

LCD_SEG26

GPIO4

LCD_COM7

LCD_SEG27

UART3_TX

UART3_RX

NSS

SCAN

6 / 12

�

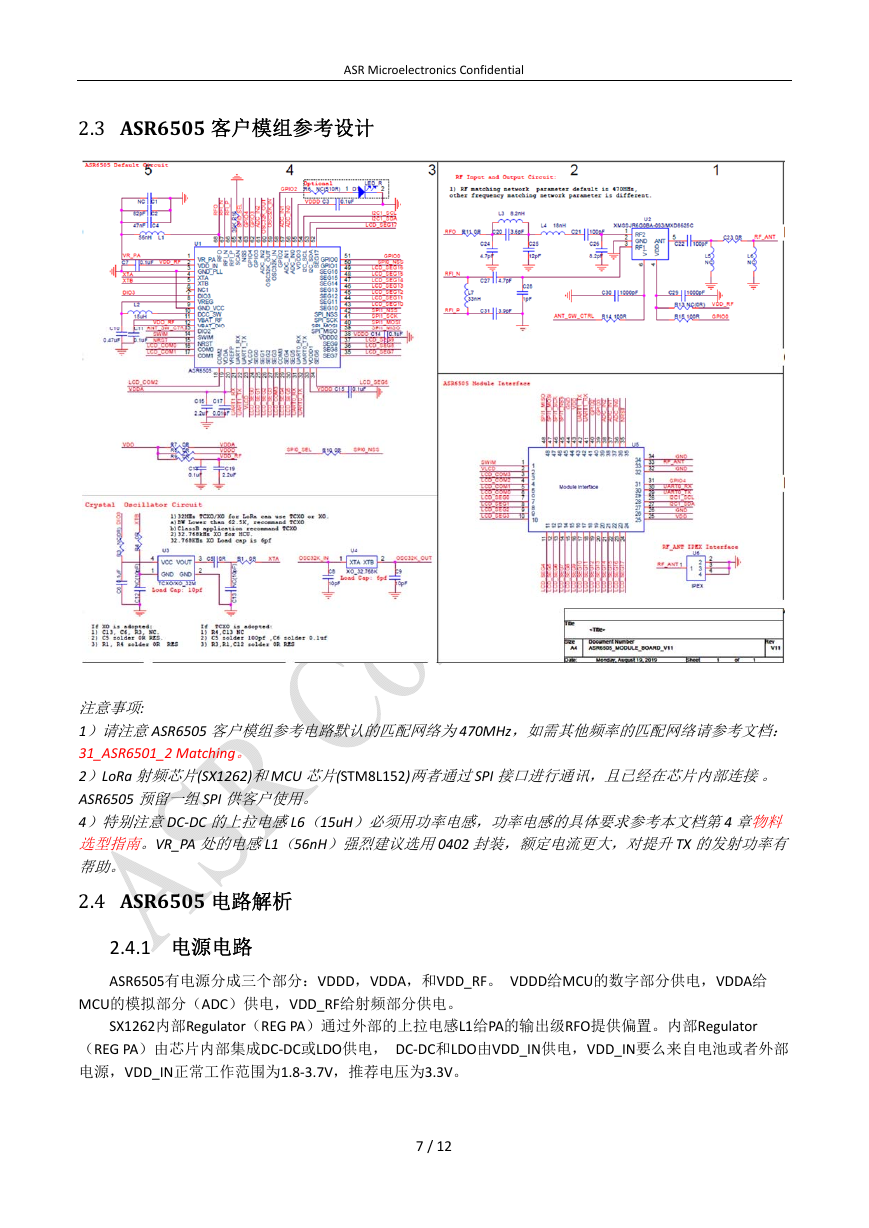

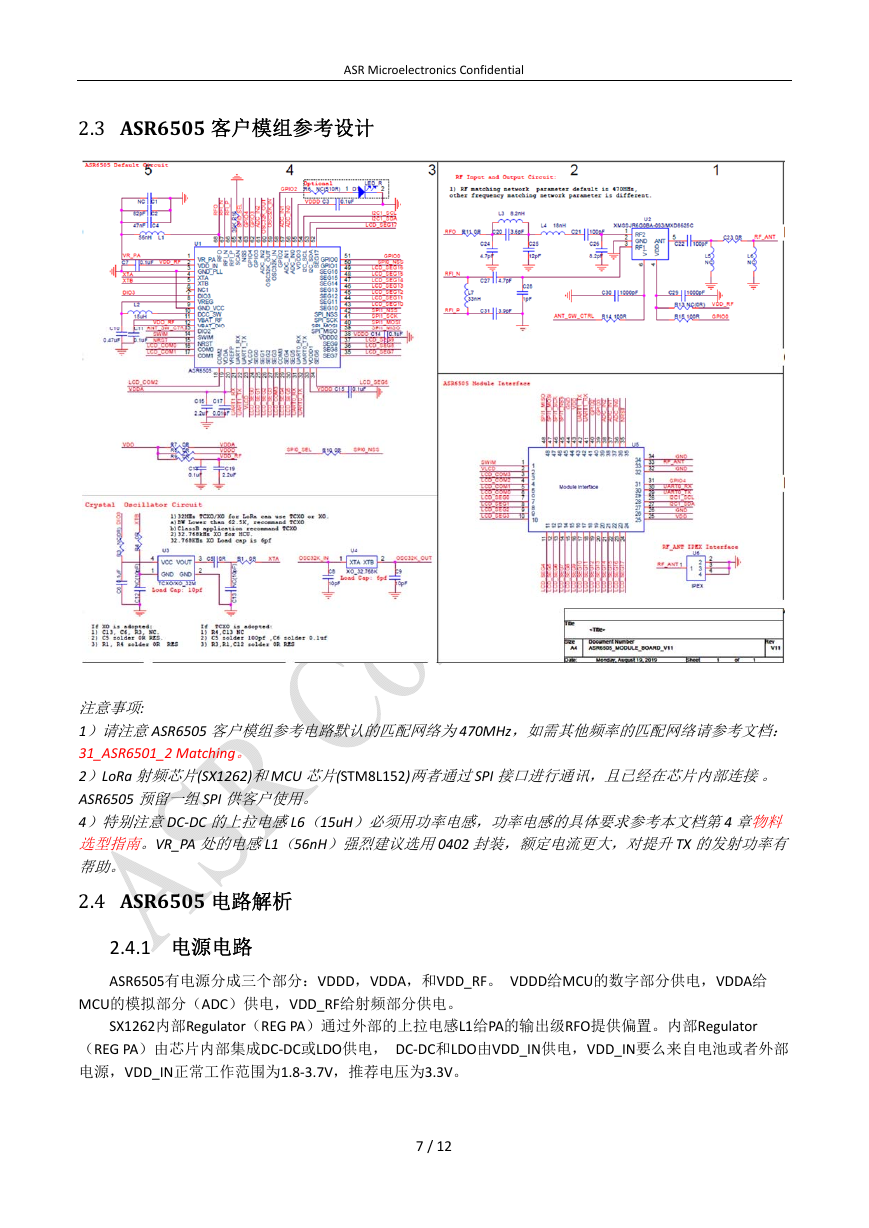

2.3 ASR6505 客户模组参考设计

ASR Microelectronics Confidential

注意事项:

1)请注意ASR6505 客户模组参考电路默认的匹配网络为470MHz,如需其他频率的匹配网络请参考文档:

31_ASR6501_2 Matching。

2)LoRa 射频芯片(SX1262)和 MCU 芯片(STM8L152)两者通过 SPI 接口进行通讯,且已经在芯片内部连接 。

ASR6505 预留一组SPI 供客户使用。

4)特别注意DC‐DC 的上拉电感L6(15uH)必须用功率电感,功率电感的具体要求参考本文档第4 章物料

选型指南。VR_PA 处的电感L1(56nH)强烈建议选用0402 封装,额定电流更大,对提升TX 的发射功率有

帮助。

2.4 ASR6505 电路解析

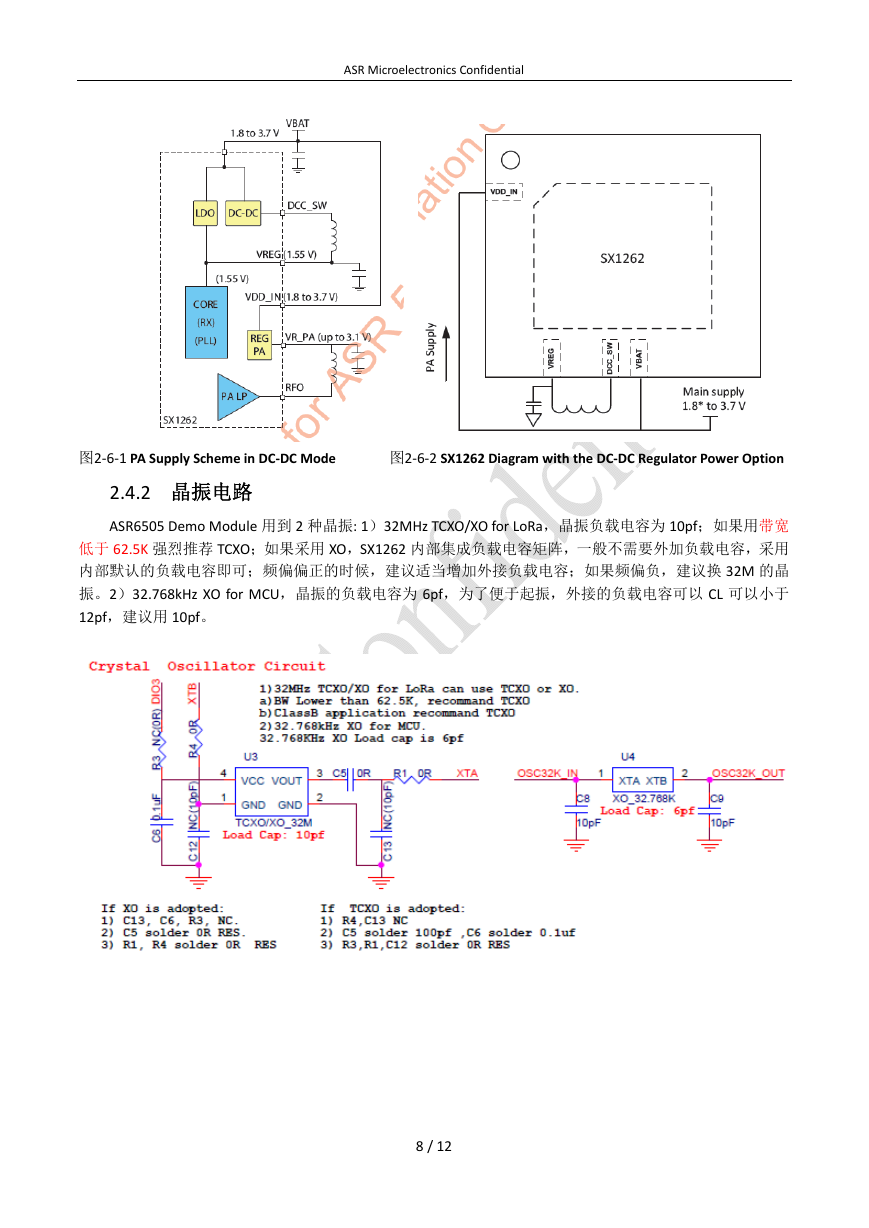

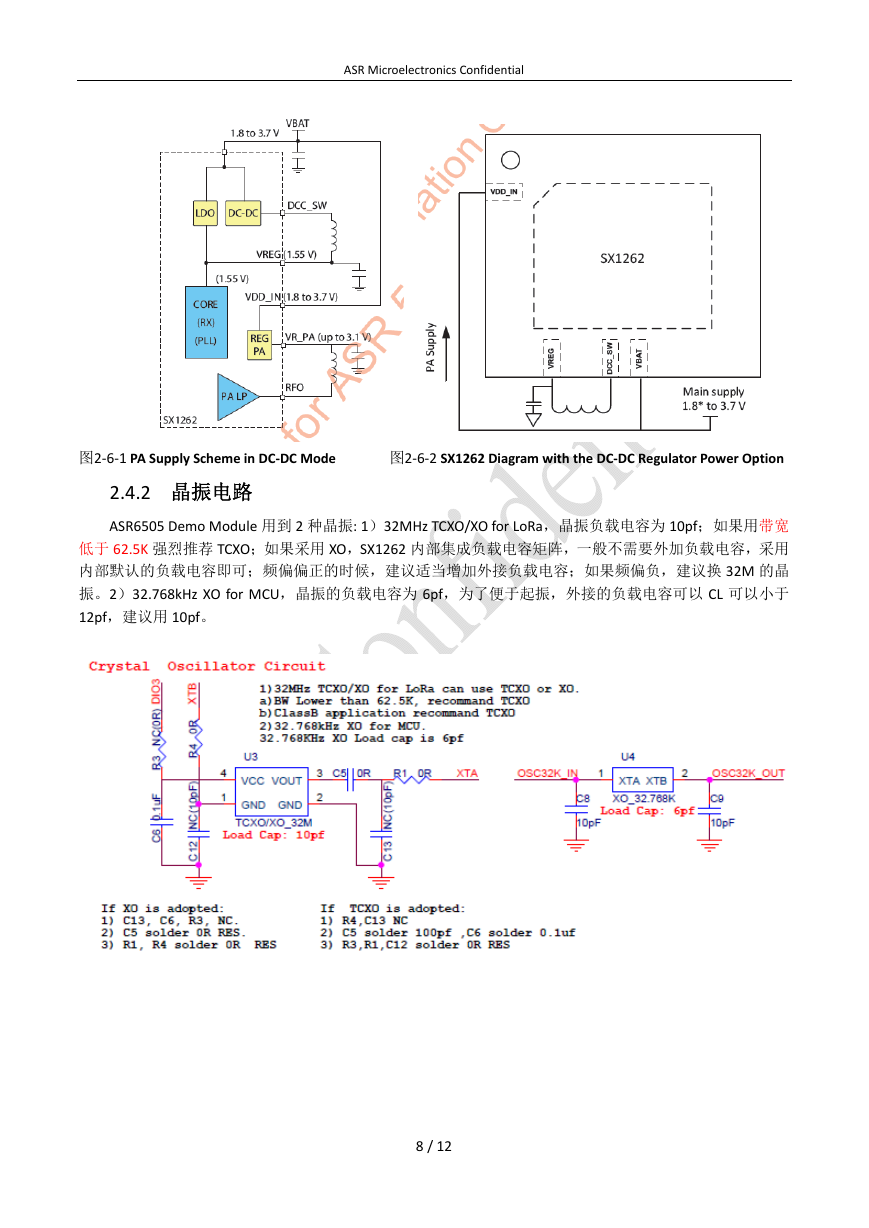

2.4.1 电源电路

ASR6505有电源分成三个部分:VDDD,VDDA,和VDD_RF。 VDDD给MCU的数字部分供电,VDDA给

MCU的模拟部分(ADC)供电,VDD_RF给射频部分供电。

SX1262内部Regulator(REG PA)通过外部的上拉电感L1给PA的输出级RFO提供偏置。内部Regulator

(REG PA)由芯片内部集成DC‐DC或LDO供电, DC‐DC和LDO由VDD_IN供电,VDD_IN要么来自电池或者外部

电源,VDD_IN正常工作范围为1.8‐3.7V,推荐电压为3.3V。

7 / 12

�

ASR Microelectronics Confidential

图2‐6‐1 PA Supply Scheme in DC‐DC Mode 图2‐6‐2 SX1262 Diagram with the DC‐DC Regulator Power Option

2.4.2 晶振电路

ASR6505 Demo Module 用到 2 种晶振: 1)32MHz TCXO/XO for LoRa,晶振负载电容为 10pf;如果用带宽

低于 62.5K 强烈推荐 TCXO;如果采用 XO,SX1262 内部集成负载电容矩阵,一般不需要外加负载电容,采用

内部默认的负载电容即可;频偏偏正的时候,建议适当增加外接负载电容;如果频偏负,建议换 32M 的晶

振。2)32.768kHz XO for MCU,晶振的负载电容为 6pf,为了便于起振,外接的负载电容可以 CL 可以小于

12pf,建议用 10pf。

8 / 12

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc