5

10

15

20

25

30

35

40

中国科技论文在线

基于 PCIe 的 FPGA 动态配置设计与实现

http://www.paper.edu.cn

袁爱民,陈通**

(北京邮电大学信息与通信工程学院,北京 100876)

摘要:随着现代处理器技术的发展,在互联领域中,使用高速差分总线替代并行总线是大势

所趋。因此 PCIe 取代 PCI,越来越多的应用在高速互联系统中。本文先简单介绍了 FPGA 的

不同配置方法,然后描述了 SelectMAP 配置流程和数据格式。紧接着给出了作者所使用的

PCIe 子卡的系统结构。最后详述了 SelectMAP 配置方法的具体实现过程,包括 FPGA 程序设

计和上位机应用程序设计。该配置方法灵活、快捷、可靠,可广泛应用于高速互联系统设计

中。

关键词:通信与信息系统;PCIe;动态配置;SelectMAP

中图分类号:TB4

Design and Implementation of FPGA's Dynamic

Configuration Based on PCIe

Yuan Aimin, Chen Tong

(Information and Communication Engineering School,Beijing University of Posts and

Telecommunications, Beijing 100876)

Abstract: With the development of modern processor technology, using high-speed differential

bus rather than a parallel bus is the trend in the interconnection field. Instead of PCI, PCIe is used

more and more in high-speed Interconnection system. This paper briefly introduces the different

configuration methods of FPGA, and then describes the SelectMAP configuration processes and

data formats. Then it discribes the architecture of the PCIe card. Finally it gives a detail discription

of SelectMAP's implementation process, including FPGA programming and application program

design. This configuration method is flexible, fast and reliable, which can be widely used in high

speed interconnection system design.

Keywords: communication; PCIe; configuration; SelectMAP

0 引言

传统的 PCI 总线虽然其带宽峰值可以达到 133MB/s,但是它使用共享总线拓扑结构,总

线带宽在多个设备间共享,导致每个设备实际占用的带宽十分有限。PCIe 采用点到点传输,

单个信道即可提供 2.5Gbps 单向传输带宽。信道可以组合在一起形成 x1、x2、x4、x8、x16、

x32 等模式,从而可以大大提高信道带宽。PCIe 取代 PCI 成为必然趋势[1]。PCIe 接口的硬

件实现一般可以使用专用 ASIC,也可以用 FPGA。用 FPGA 实现 PCIe 接口的优点是设计灵

活,可以很方便的进行各种功能扩展。Spartan-6 系列 FPGA 是 Xilinx 公司针对低功耗市场

的最新产品。集成了 PCI Express 接口硬核。本文详述了利用 PCIe 接口对 Spartan-6 进行动

态配置的原理和实现过程。

1 FPGA 配置方法概述

不同器件厂商生产的 FPGA 配置方式各不相同,同一厂商不同系列的器件其配置方式也

会有差别。一般来说,FPGA 的配置方式主要有三种:JTAG 配置、存储器配置和上位机配

置。本文所指的动态配置即是上面所说的上位机配置。对于 Xilinx 的 Spartan-6 系列 FPGA

而言,其动态配置方式又可细分为 Slave Serial 和 SelectMAP 两种。前者属于串行配置,后

作者简介:袁爱民,(1986-),男,硕士,主要研究方向为通信与信息系统。

通信联系人:陈通,(1982-),男,讲师,宽带通信新技术. E-mail: chentong@bupt.edu.cn

- 1 -

�

中国科技论文在线

http://www.paper.edu.cn

者属于并行配置。由于并行配置速度快,实现起来也比较简单,所以 SelectMAP 配置方法

是本文论述的重点。

2 SelectMAP 配置方法

45

2.1 配置流程

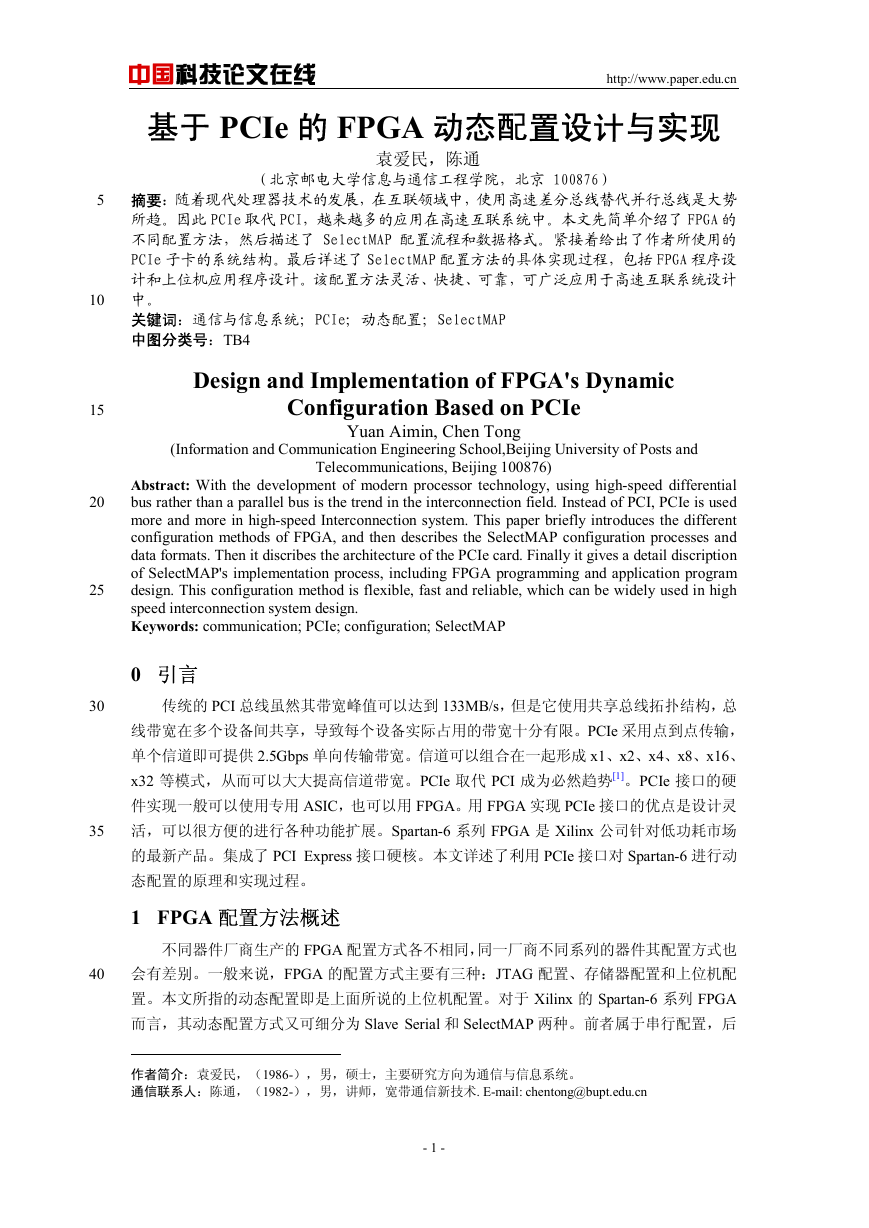

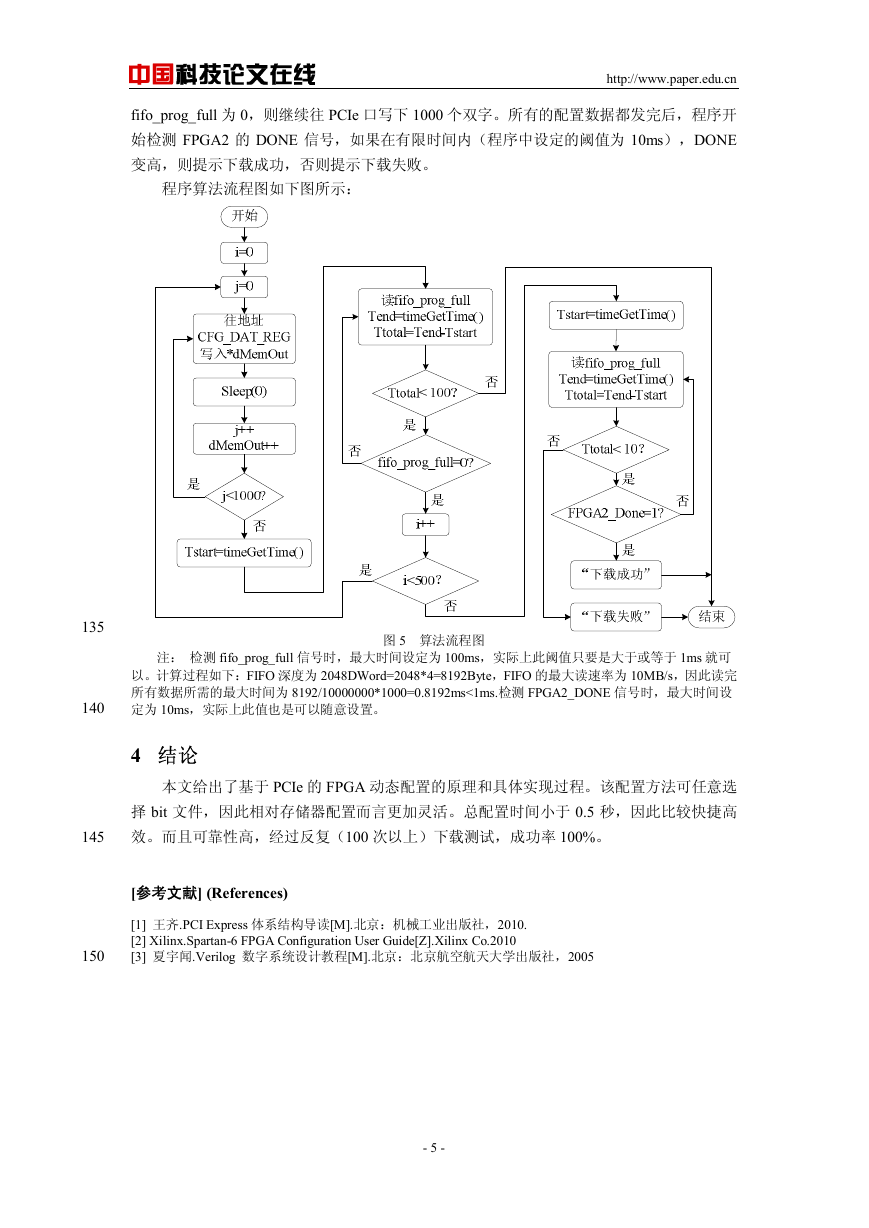

SelectMAP 总体配置流程如下图所示[2]:

50

55

60

65

70

图 1 SelectMAP 配置流程

Power-Up

FPGA 上电后,内部状态机复位,设备被唤醒。此时,PROGRAM_B 和 INIT_B 引脚都

被 FPGA 自动拉低。

Device Initialization

FPGA 已经正常上电,但是内部配置寄存器需要复位。此时 PROGRAM_B 电平变高,

INIT_B 随之也变高。如果用户将 PROGRAM_B 或者 INIT_B 外部拉低,则 FPGA 将始终停

留在 Device Initialization 状态。

Configuration Load

INIT_B 由低变高就标志着 Configuration Load 步骤的开始。此时 FPGA 内部对模式引脚

(M1:M0)采样读取。Slave SelectMAP 模式对应为 M[1:0]=2’b10。进入 Configuration Load

步骤后,FPGA 开始接收配置数据。所有的配置事件都由 CCLK 的上升沿驱动。

Start-Up

当 FPGA 接收完所有配置数据,DONE 由低变高,即标志着 FPGA 进入 Start-Up 进程。

DONE 变高不一定就代表配置成功。此时还需要额外的 CCLK 时钟周期才能完成 Start-Up。

具体还需要多少额外的 CCLK 周期,跟 bit 文件生成时 BitGen 的选项有关系。最好的办法

就是在下载完 bit 文件对应的配置数据后,让 CCLK 继续有效,同时将数据信号置为全 1,

直到 DONE 引脚变高。DONE 变高后,再加8 个额外的CCLK 周期,以确保 FPGA 完成 Start-Up

进程。

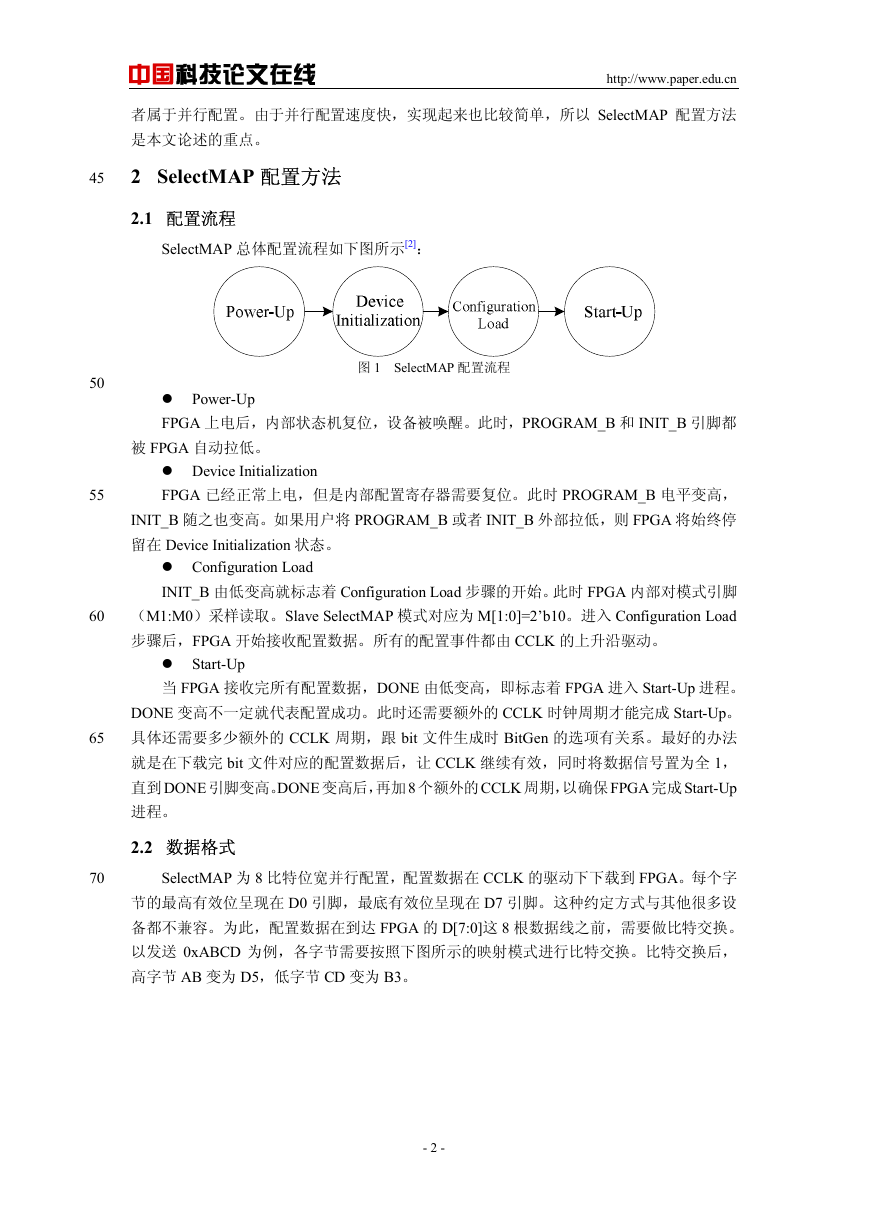

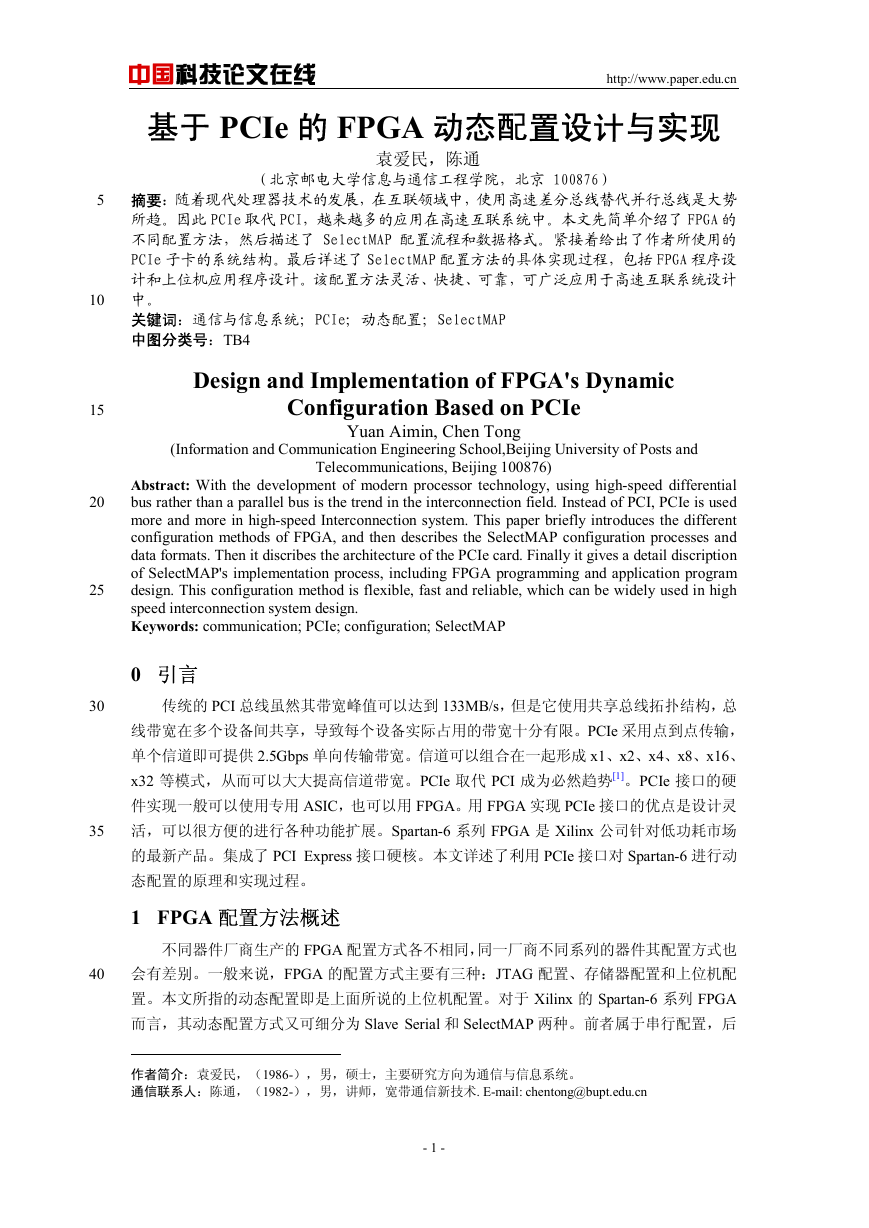

2.2 数据格式

SelectMAP 为 8 比特位宽并行配置,配置数据在 CCLK 的驱动下下载到 FPGA。每个字

节的最高有效位呈现在 D0 引脚,最底有效位呈现在 D7 引脚。这种约定方式与其他很多设

备都不兼容。为此,配置数据在到达 FPGA 的 D[7:0]这 8 根数据线之前,需要做比特交换。

以发送 0xABCD 为例,各字节需要按照下图所示的映射模式进行比特交换。比特交换后,

高字节 AB 变为 D5,低字节 CD 变为 B3。

- 2 -

�

中国科技论文在线

http://www.paper.edu.cn

75

80

85

图 2 比特交换

3 SelectMAP 实现过程

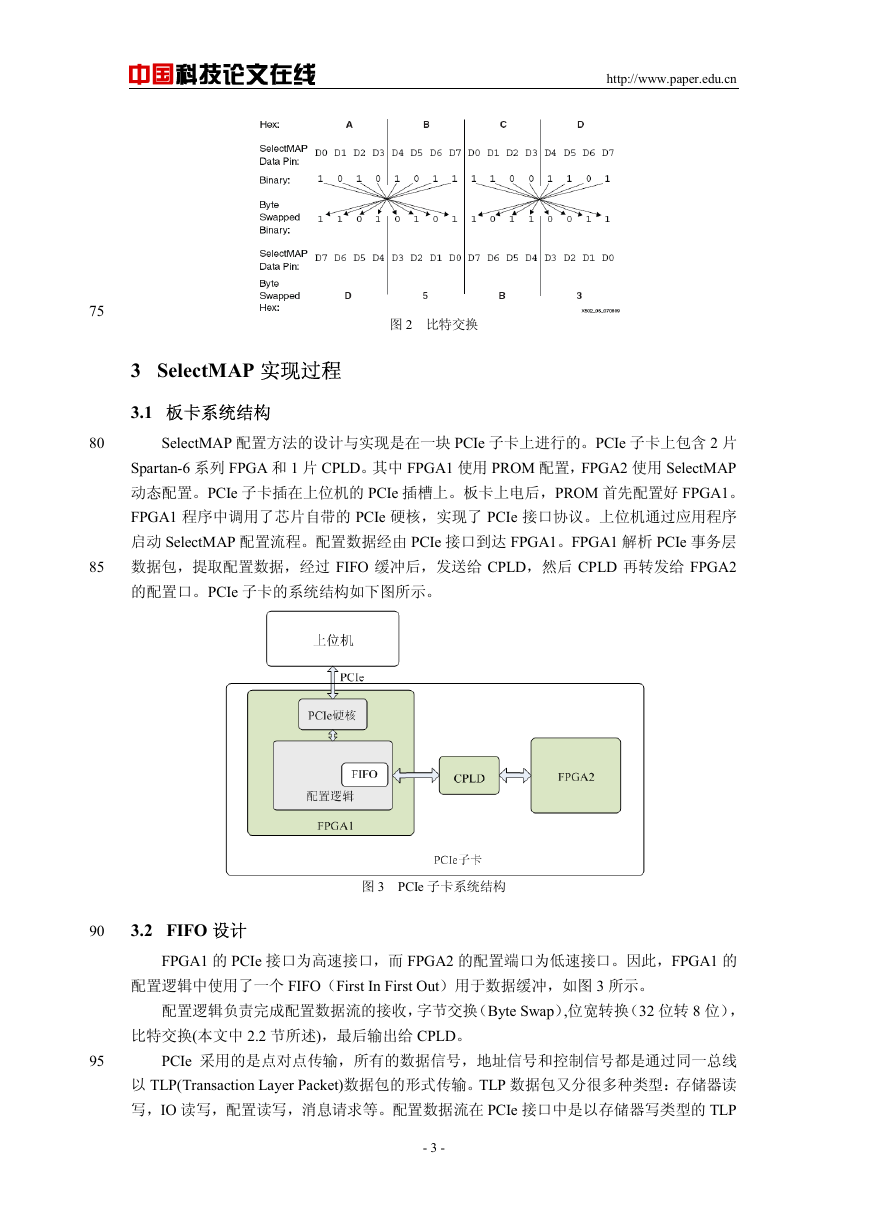

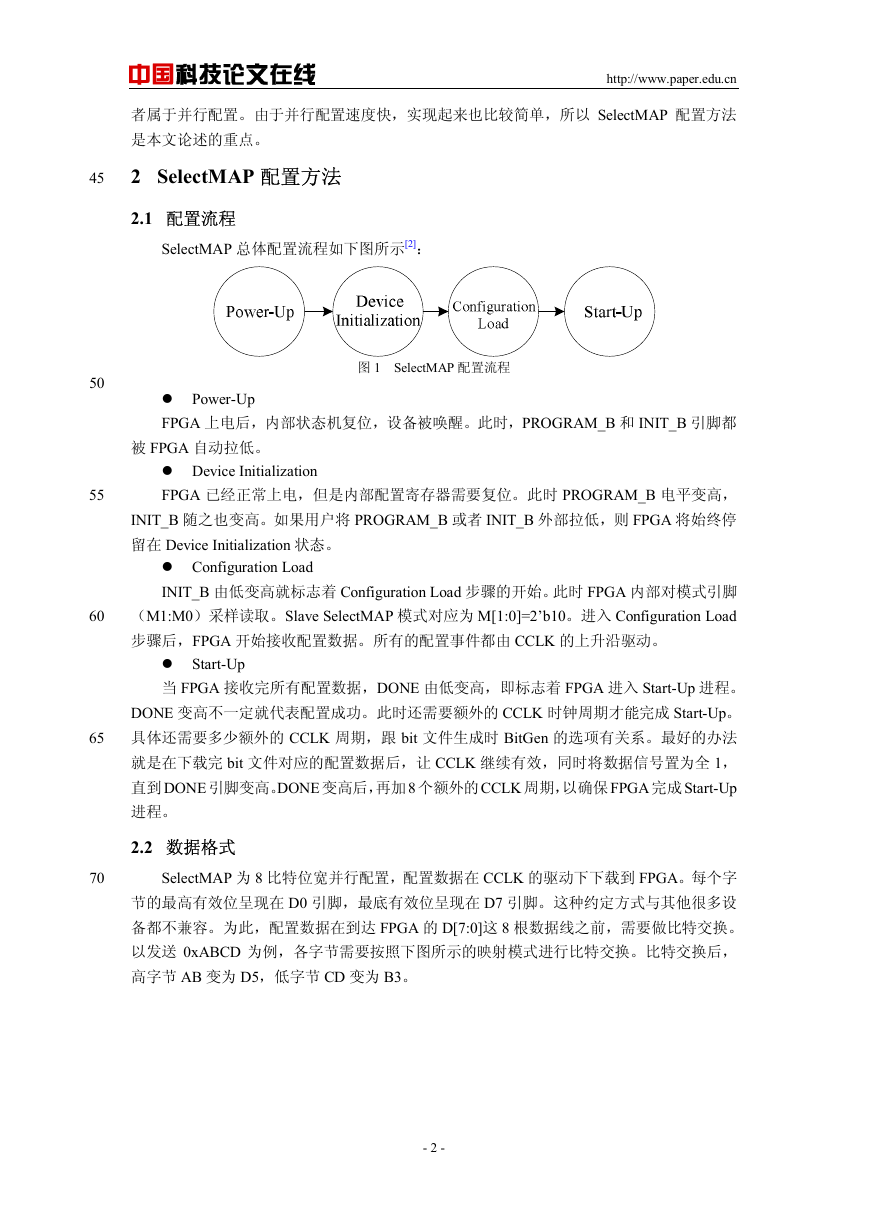

3.1 板卡系统结构

SelectMAP 配置方法的设计与实现是在一块 PCIe 子卡上进行的。PCIe 子卡上包含 2 片

Spartan-6 系列 FPGA 和 1 片 CPLD。其中 FPGA1 使用 PROM 配置,FPGA2 使用 SelectMAP

动态配置。PCIe 子卡插在上位机的 PCIe 插槽上。板卡上电后,PROM 首先配置好 FPGA1。

FPGA1 程序中调用了芯片自带的 PCIe 硬核,实现了 PCIe 接口协议。上位机通过应用程序

启动 SelectMAP 配置流程。配置数据经由 PCIe 接口到达 FPGA1。FPGA1 解析 PCIe 事务层

数据包,提取配置数据,经过 FIFO 缓冲后,发送给 CPLD,然后 CPLD 再转发给 FPGA2

的配置口。PCIe 子卡的系统结构如下图所示。

图 3 PCIe 子卡系统结构

90

3.2 FIFO 设计

FPGA1 的 PCIe 接口为高速接口,而 FPGA2 的配置端口为低速接口。因此,FPGA1 的

配置逻辑中使用了一个 FIFO(First In First Out)用于数据缓冲,如图 3 所示。

配置逻辑负责完成配置数据流的接收,字节交换(Byte Swap),位宽转换(32 位转 8 位),

比特交换(本文中 2.2 节所述),最后输出给 CPLD。

95

PCIe 采用的是点对点传输,所有的数据信号,地址信号和控制信号都是通过同一总线

以 TLP(Transaction Layer Packet)数据包的形式传输。TLP 数据包又分很多种类型:存储器读

写,IO 读写,配置读写,消息请求等。配置数据流在 PCIe 接口中是以存储器写类型的 TLP

- 3 -

�

中国科技论文在线

http://www.paper.edu.cn

发送给 FPGA1 的。因此配置逻辑需要从所有的 TLP 数据包中识别哪些是存储器写类型的。

同时,配置逻辑还需要识别这些写操作对应的地址。有的地址用于写控制信号(例如 programb

信号,FIFO_rst 信号),有的地址用于写配置数据。因此配置逻辑还需要从 TLP 中识别写

操作对应的地址,以此来判断该 TLP 中的数据载荷是属于何种类型的数据。

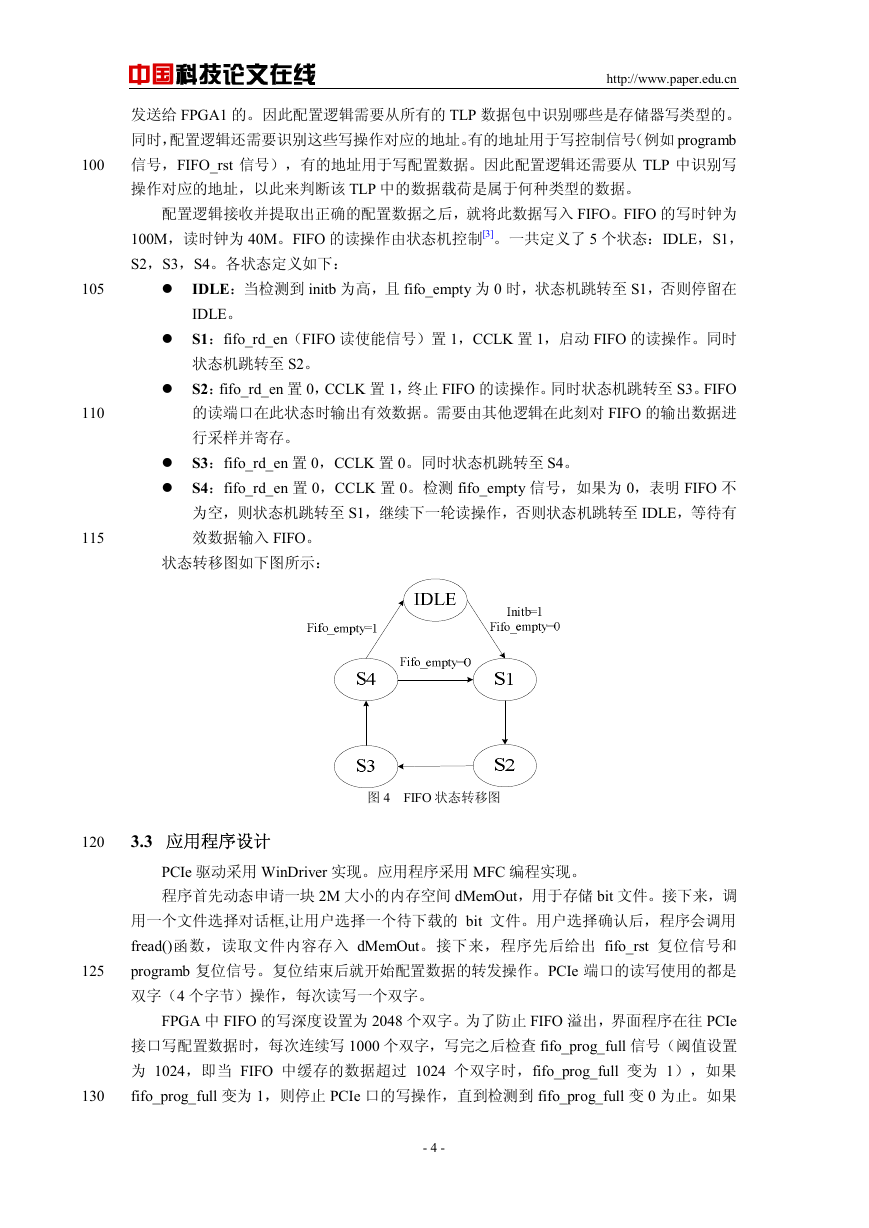

配置逻辑接收并提取出正确的配置数据之后,就将此数据写入 FIFO。FIFO 的写时钟为

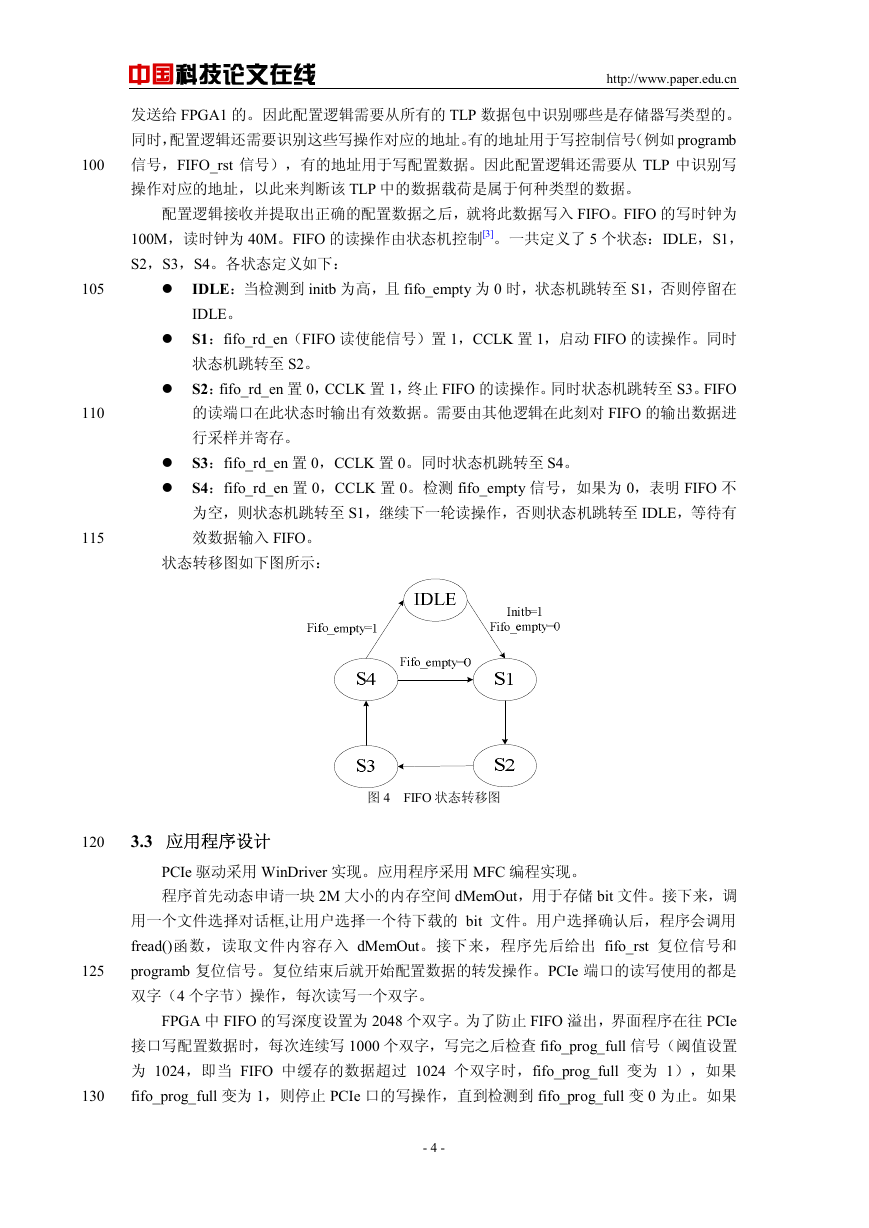

100M,读时钟为 40M。FIFO 的读操作由状态机控制[3]。一共定义了 5 个状态:IDLE,S1,

S2,S3,S4。各状态定义如下:

IDLE:当检测到 initb 为高,且 fifo_empty 为 0 时,状态机跳转至 S1,否则停留在

IDLE。

S1:fifo_rd_en(FIFO 读使能信号)置 1,CCLK 置 1,启动 FIFO 的读操作。同时

状态机跳转至 S2。

S2:fifo_rd_en 置 0,CCLK 置 1,终止 FIFO 的读操作。同时状态机跳转至 S3。FIFO

的读端口在此状态时输出有效数据。需要由其他逻辑在此刻对 FIFO 的输出数据进

行采样并寄存。

S3:fifo_rd_en 置 0,CCLK 置 0。同时状态机跳转至 S4。

S4:fifo_rd_en 置 0,CCLK 置 0。检测 fifo_empty 信号,如果为 0,表明 FIFO 不

为空,则状态机跳转至 S1,继续下一轮读操作,否则状态机跳转至 IDLE,等待有

效数据输入 FIFO。

状态转移图如下图所示:

100

105

110

115

图 4 FIFO 状态转移图

120

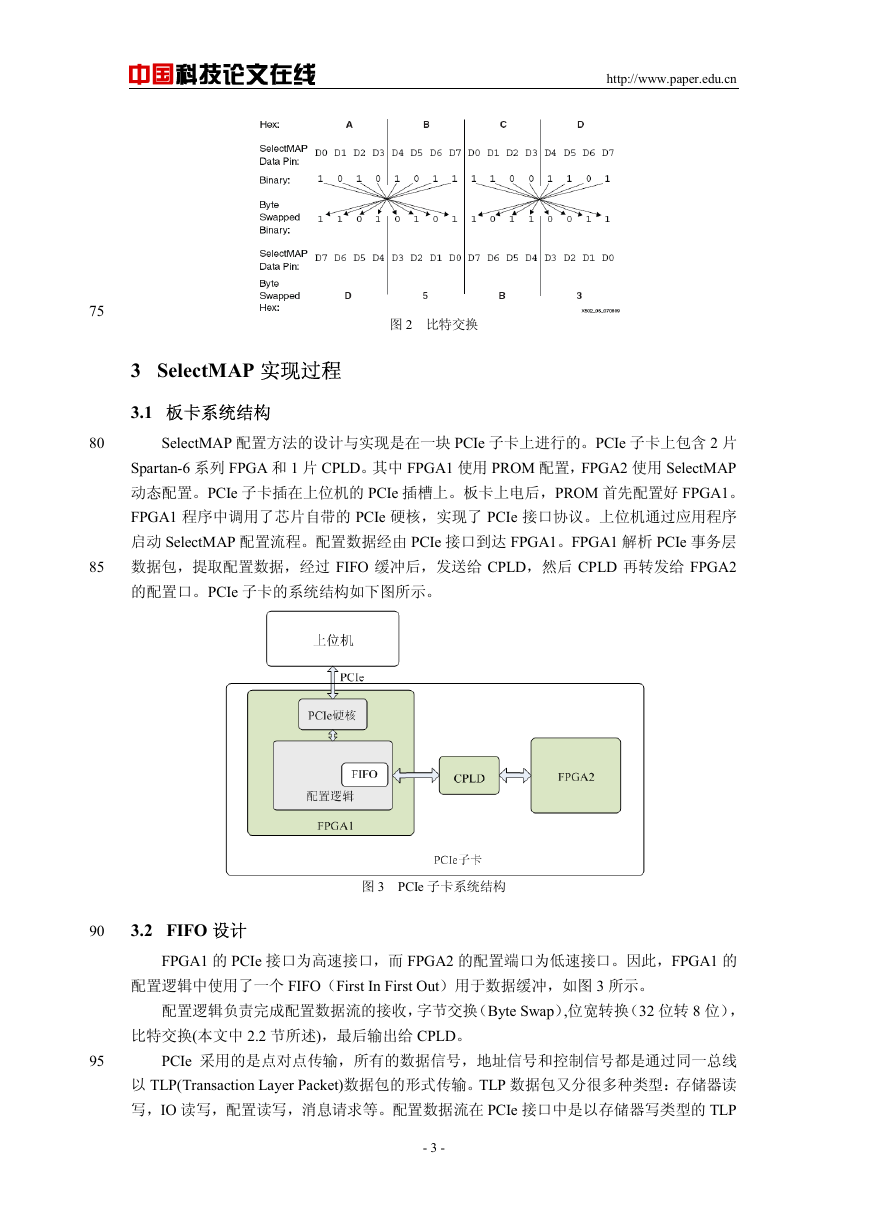

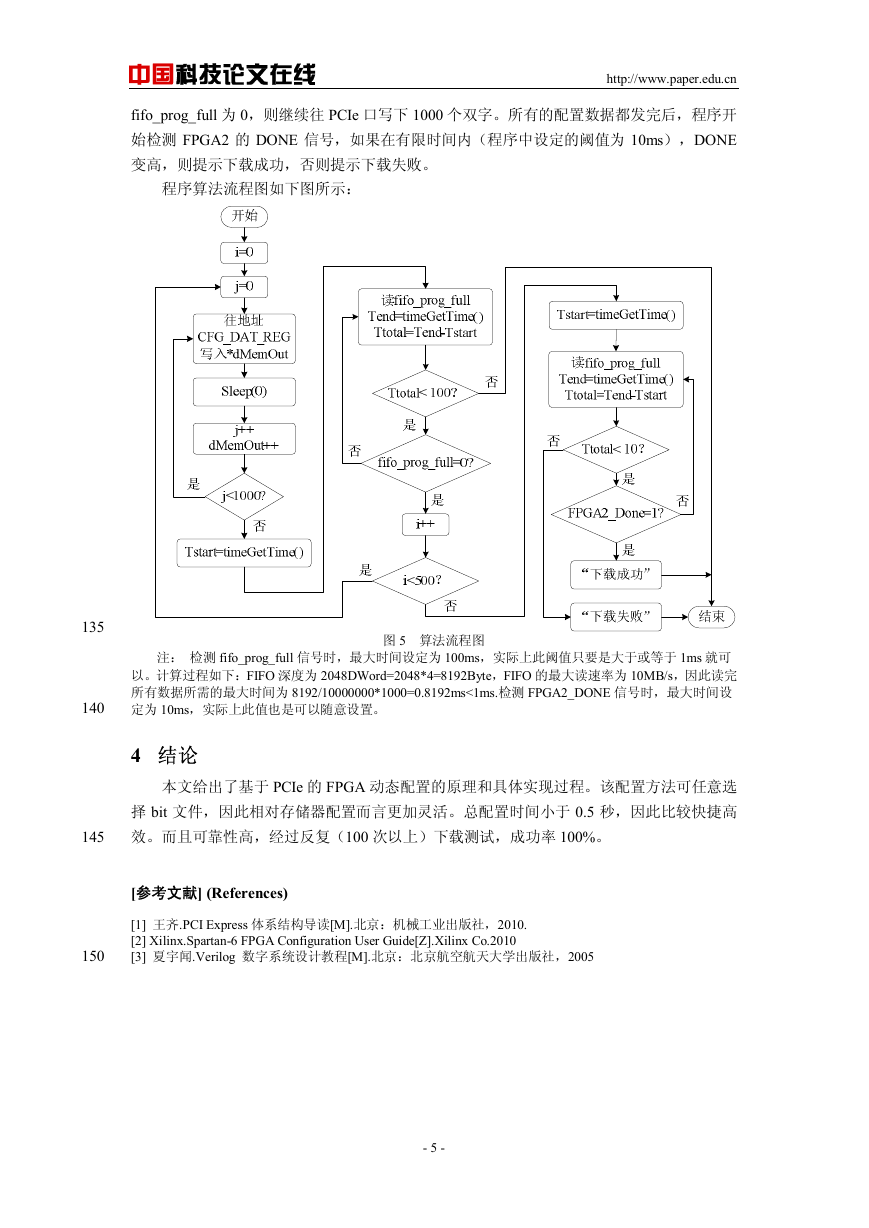

3.3 应用程序设计

PCIe 驱动采用 WinDriver 实现。应用程序采用 MFC 编程实现。

程序首先动态申请一块 2M 大小的内存空间 dMemOut,用于存储 bit 文件。接下来,调

用一个文件选择对话框,让用户选择一个待下载的 bit 文件。用户选择确认后,程序会调用

fread()函数,读取文件内容存入 dMemOut。接下来,程序先后给出 fifo_rst 复位信号和

programb 复位信号。复位结束后就开始配置数据的转发操作。PCIe 端口的读写使用的都是

双字(4 个字节)操作,每次读写一个双字。

FPGA 中 FIFO 的写深度设置为 2048 个双字。为了防止 FIFO 溢出,界面程序在往 PCIe

接口写配置数据时,每次连续写 1000 个双字,写完之后检查 fifo_prog_full 信号(阈值设置

为 1024,即当 FIFO 中缓存的数据超过 1024 个双字时,fifo_prog_full 变为 1),如果

fifo_prog_full 变为 1,则停止 PCIe 口的写操作,直到检测到 fifo_prog_full 变 0 为止。如果

125

130

- 4 -

�

中国科技论文在线

http://www.paper.edu.cn

fifo_prog_full 为 0,则继续往 PCIe 口写下 1000 个双字。所有的配置数据都发完后,程序开

始检测 FPGA2 的 DONE 信号,如果在有限时间内(程序中设定的阈值为 10ms),DONE

变高,则提示下载成功,否则提示下载失败。

程序算法流程图如下图所示:

135

140

145

150

图 5 算法流程图

注: 检测 fifo_prog_full 信号时,最大时间设定为 100ms,实际上此阈值只要是大于或等于 1ms 就可

以。计算过程如下:FIFO 深度为 2048DWord=2048*4=8192Byte,FIFO 的最大读速率为 10MB/s,因此读完

所有数据所需的最大时间为 8192/10000000*1000=0.8192ms<1ms.检测 FPGA2_DONE 信号时,最大时间设

定为 10ms,实际上此值也是可以随意设置。

4 结论

本文给出了基于 PCIe 的 FPGA 动态配置的原理和具体实现过程。该配置方法可任意选

择 bit 文件,因此相对存储器配置而言更加灵活。总配置时间小于 0.5 秒,因此比较快捷高

效。而且可靠性高,经过反复(100 次以上)下载测试,成功率 100%。

[参考文献] (References)

[1] 王齐.PCI Express 体系结构导读[M].北京:机械工业出版社,2010.

[2] Xilinx.Spartan-6 FPGA Configuration User Guide[Z].Xilinx Co.2010

[3] 夏宇闻.Verilog 数字系统设计教程[M].北京:北京航空航天大学出版社,2005

- 5 -

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc