可编程逻辑器件与硬件描述语言

实 验 报 告

评 语:

成

绩

教 师:

年 月 日

班 级:

学 号:

姓 名:

地 点:

时 间:

�

组合逻辑电路实验

(一)实验名称:

3-8 译码器电路设计

(二)实验目的:

1)掌握 ISE 开发工具的使用,掌握 FPGA 开发的基本步骤;

2)掌握组合逻辑电路设计的一般方法;

3)掌握程序下载方法,了解 UCF 文件的格式;

4)初步了解开发板资源,掌握开发板使用方法。重点了解滑动开关和 LED

显示灯的使用方法。

5)理解并掌握 VHDL 程序的结构,掌握输入输出端口的含义;

(三)实验内容:

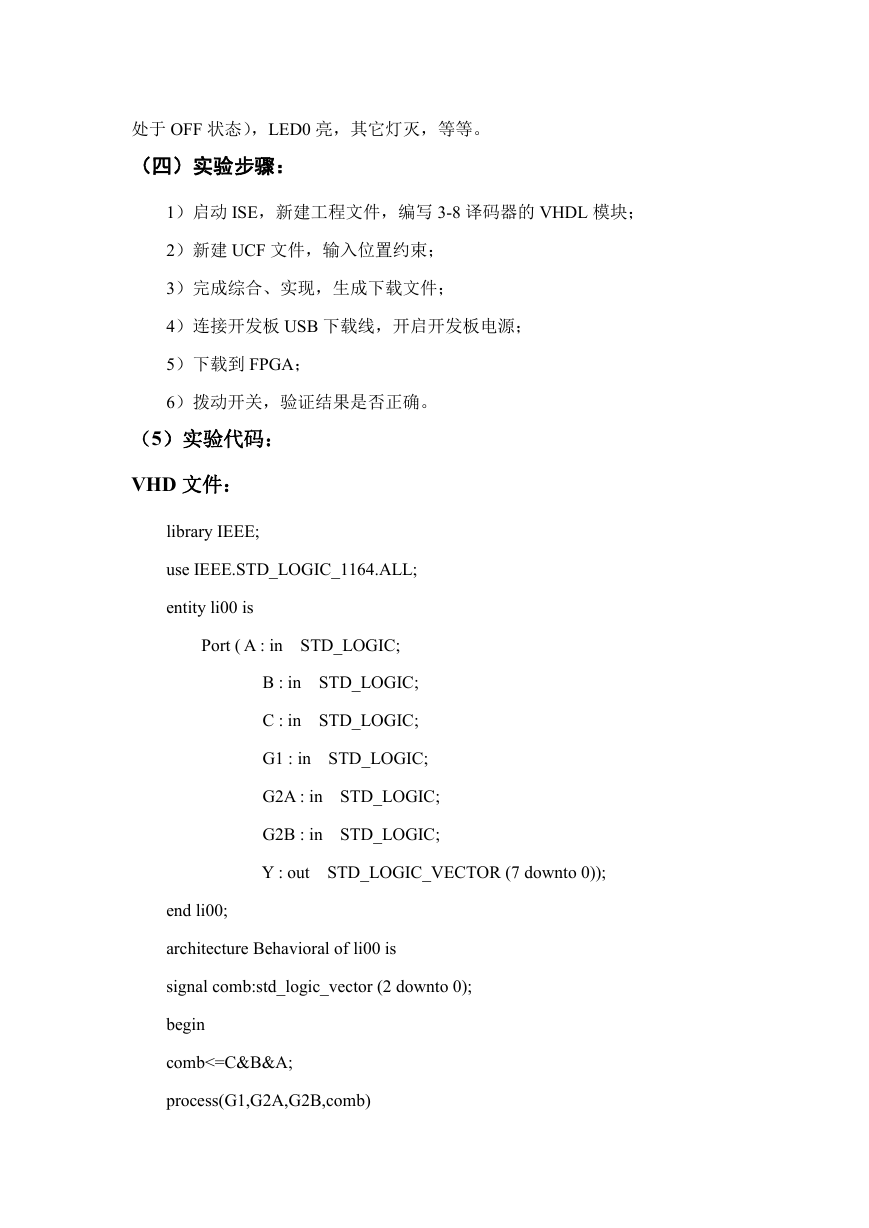

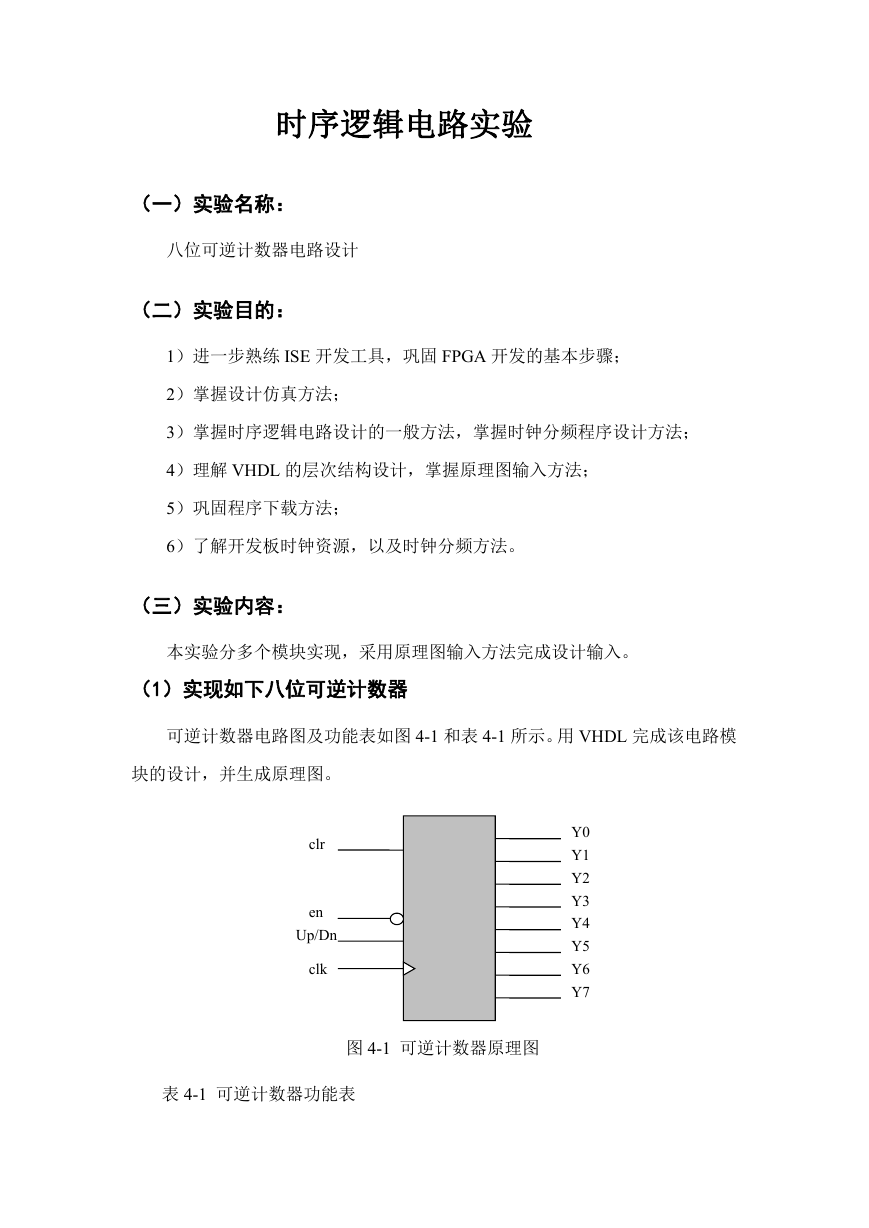

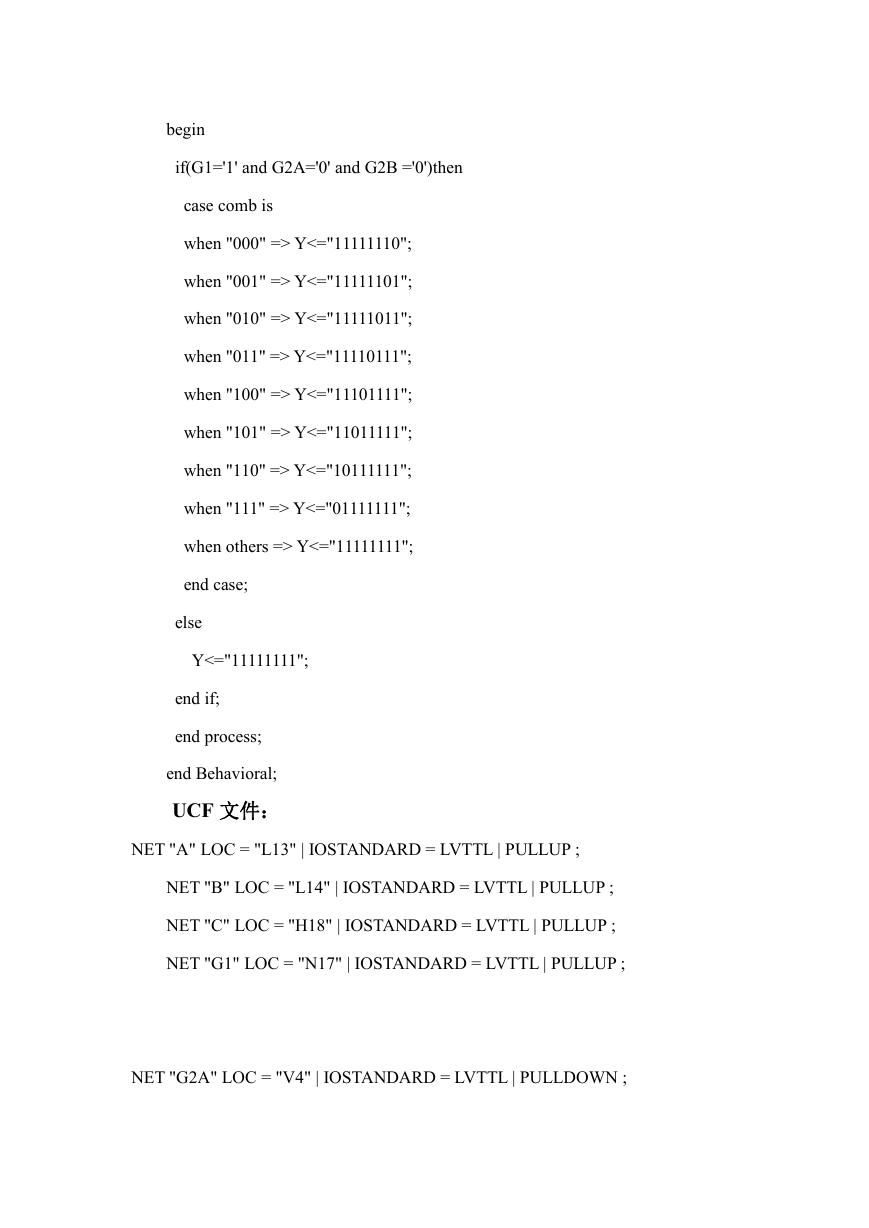

(1)用 VHDL 实现 3-8 译码器模块

译码器电路如图 3-1 所示。其功能如表 3-1 所示。试用 VHDL 完成该译码器

的设计,并在开发板上进行检验。

�

A

B

C

3-8

译码器

G1

G2A

G2B

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

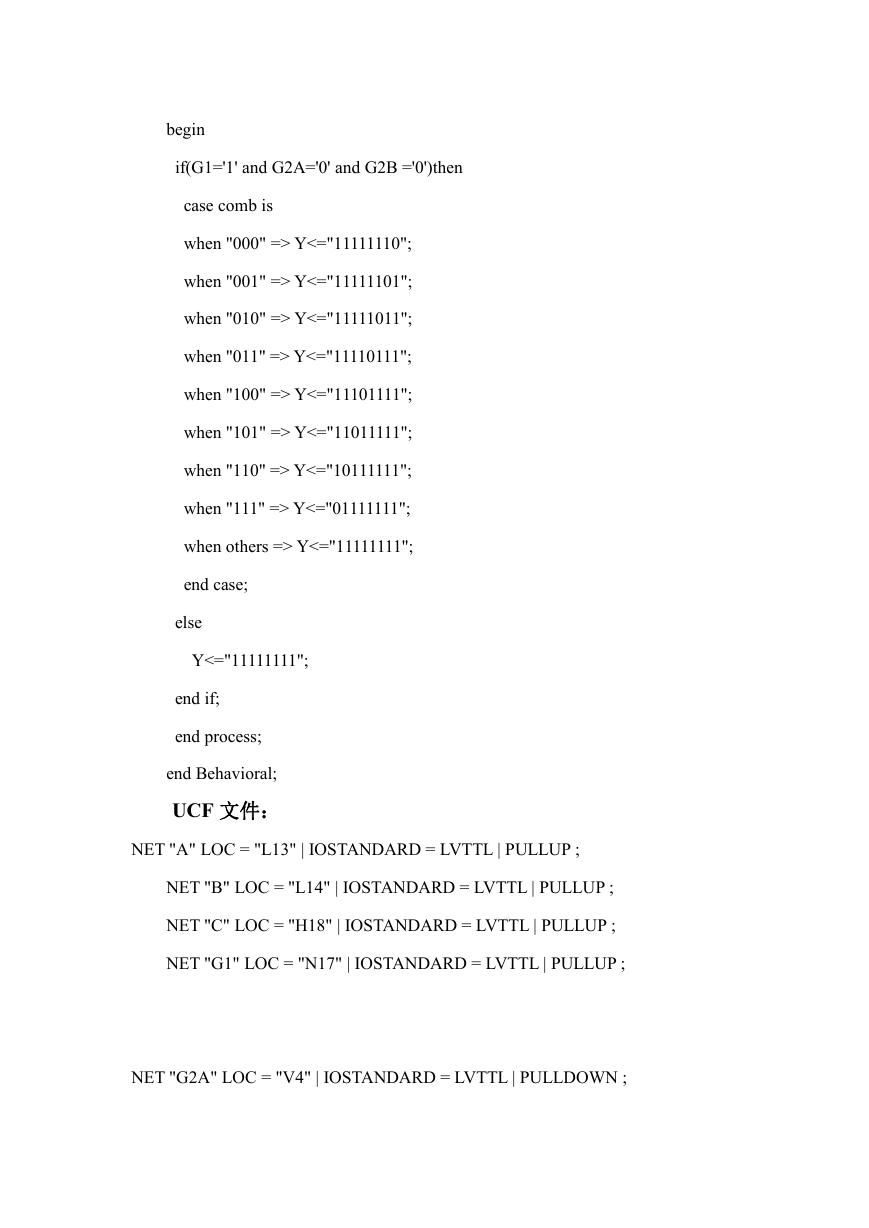

表 3-1 译码器功能表

输入

G2A G2B C

X

X

X

1

X

X

0

0

0

0

0

0

0

0

1

0

1

0

0

1

1

0

X

X

1

0

0

0

0

0

0

0

0

G1

0

X

X

1

1

1

1

1

1

1

1

B

X

X

X

0

0

1

1

0

0

1

1

图 3-1 74x138 3-8 译码器

A

X

X

X

0

1

0

1

0

1

0

1

Y7

0

0

0

0

0

0

0

0

0

0

1

Y6

0

0

0

0

0

0

0

0

0

1

0

Y5

0

0

0

0

0

0

0

0

1

0

0

输出

Y3

0

0

0

0

0

0

1

0

0

0

0

Y4

0

0

0

0

0

0

0

1

0

0

0

Y2

0

0

0

0

0

1

0

0

0

0

0

Y1

0

0

0

0

1

0

0

0

0

0

0

Y0

0

0

0

1

0

0

0

0

0

0

0

(2)将程序下载到 FPGA 并进行检验

资源使用要求:

用滑动开关 SW0~SW4 作为输入 A,B,C,G1;

滑动开关 BTN_EAST,BTN_WEST 作为控制端 G2A,G2B;

8 个 LED 灯表示 8 个输出。

检验方法:

当 SW0 处于 OFF(G1=1)或者 SW1 处于 ON(G2A=1)或者 SW2 处于 ON

(G2B=1)位置时,所有 LED 灯灭;

当 SW0 处于 ON(G1=1),且 BTN_EAST,BTN_WEST 均处于 OFF 状态时,

反映当前输入的译码输出在 LED 灯上显示,即当输入为 000(滑动开关 SW0-SW2

�

处于 OFF 状态),LED0 亮,其它灯灭,等等。

(四)实验步骤:

1)启动 ISE,新建工程文件,编写 3-8 译码器的 VHDL 模块;

2)新建 UCF 文件,输入位置约束;

3)完成综合、实现,生成下载文件;

4)连接开发板 USB 下载线,开启开发板电源;

5)下载到 FPGA;

6)拨动开关,验证结果是否正确。

(5)实验代码:

VHD 文件:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity li00 is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

C : in STD_LOGIC;

G1 : in STD_LOGIC;

G2A : in STD_LOGIC;

G2B : in STD_LOGIC;

Y : out STD_LOGIC_VECTOR (7 downto 0));

end li00;

architecture Behavioral of li00 is

signal comb:std_logic_vector (2 downto 0);

begin

comb<=C&B&A;

process(G1,G2A,G2B,comb)

�

begin

if(G1='1' and G2A='0' and G2B ='0')then

case comb is

when "000" => Y<="11111110";

when "001" => Y<="11111101";

when "010" => Y<="11111011";

when "011" => Y<="11110111";

when "100" => Y<="11101111";

when "101" => Y<="11011111";

when "110" => Y<="10111111";

when "111" => Y<="01111111";

when others => Y<="11111111";

end case;

else

Y<="11111111";

end if;

end process;

end Behavioral;

UCF 文件:

NET "A" LOC = "L13" | IOSTANDARD = LVTTL | PULLUP ;

NET "B" LOC = "L14" | IOSTANDARD = LVTTL | PULLUP ;

NET "C" LOC = "H18" | IOSTANDARD = LVTTL | PULLUP ;

NET "G1" LOC = "N17" | IOSTANDARD = LVTTL | PULLUP ;

NET "G2A" LOC = "V4" | IOSTANDARD = LVTTL | PULLDOWN ;

�

NET "G2B" LOC = "K17" | IOSTANDARD = LVTTL | PULLDOWN ;

NET "Y<7>" LOC = "F9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE =

8 ;

NET "Y<6>" LOC = "E9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE =

8 ;

NET "Y<5>" LOC = "D11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE =

8 ;

NET "Y<4>" LOC = "C11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE =

8 ;

NET "Y<3>" LOC = "F11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE =

8 ;

NET "Y<2>" LOC = "E11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE =

8 ;

NET "Y<1>" LOC = "E12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE =

8 ;

NET "Y<0>" LOC = "F12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE =

8 ;

�

时序逻辑电路实验

(一)实验名称:

八位可逆计数器电路设计

(二)实验目的:

1)进一步熟练 ISE 开发工具,巩固 FPGA 开发的基本步骤;

2)掌握设计仿真方法;

3)掌握时序逻辑电路设计的一般方法,掌握时钟分频程序设计方法;

4)理解 VHDL 的层次结构设计,掌握原理图输入方法;

5)巩固程序下载方法;

6)了解开发板时钟资源,以及时钟分频方法。

(三)实验内容:

本实验分多个模块实现,采用原理图输入方法完成设计输入。

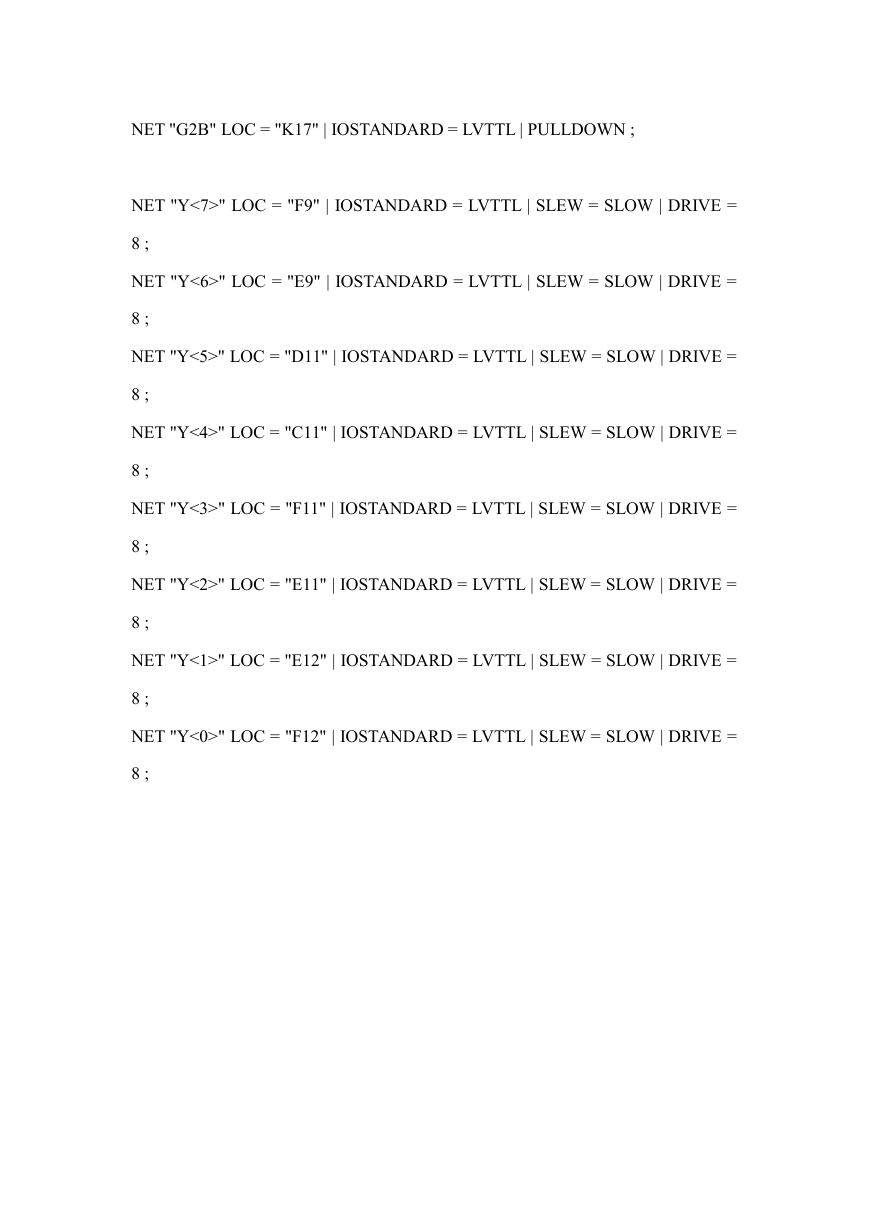

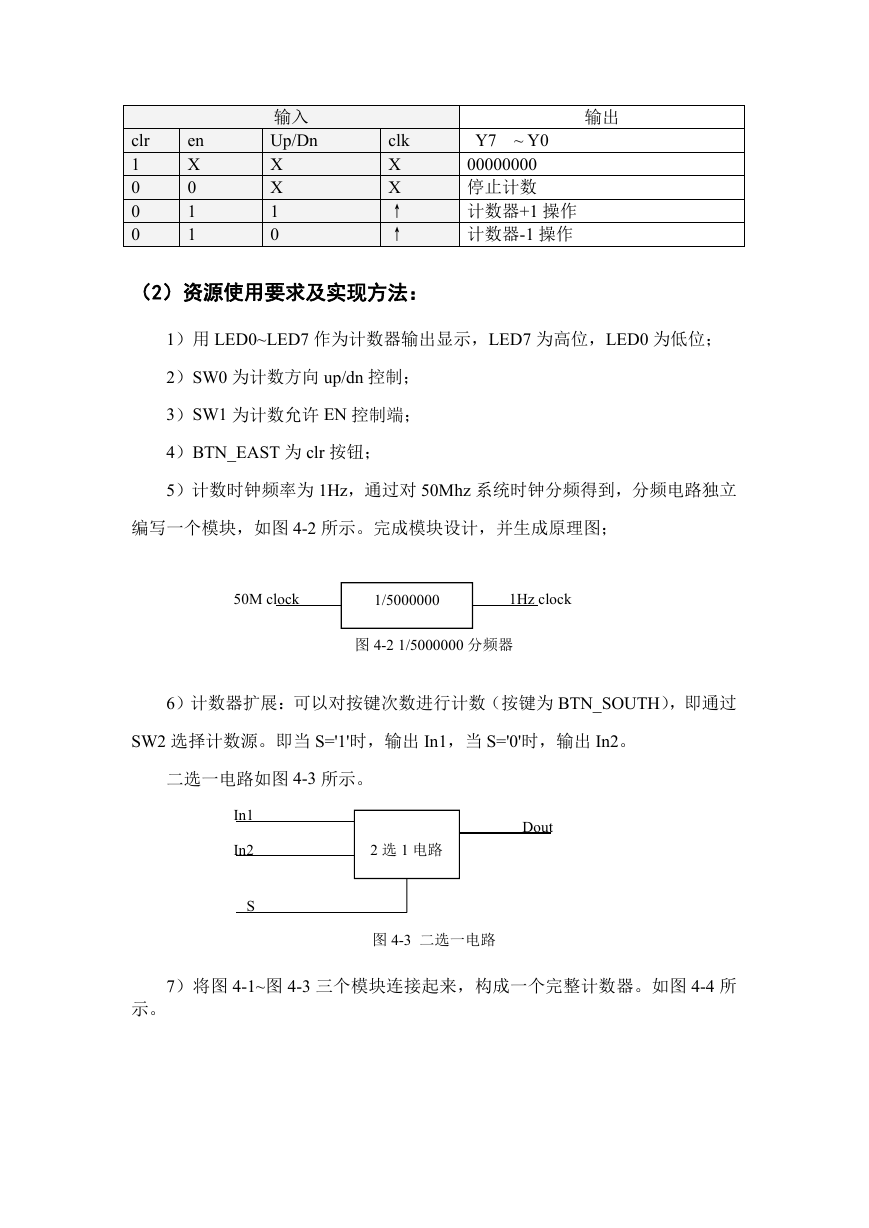

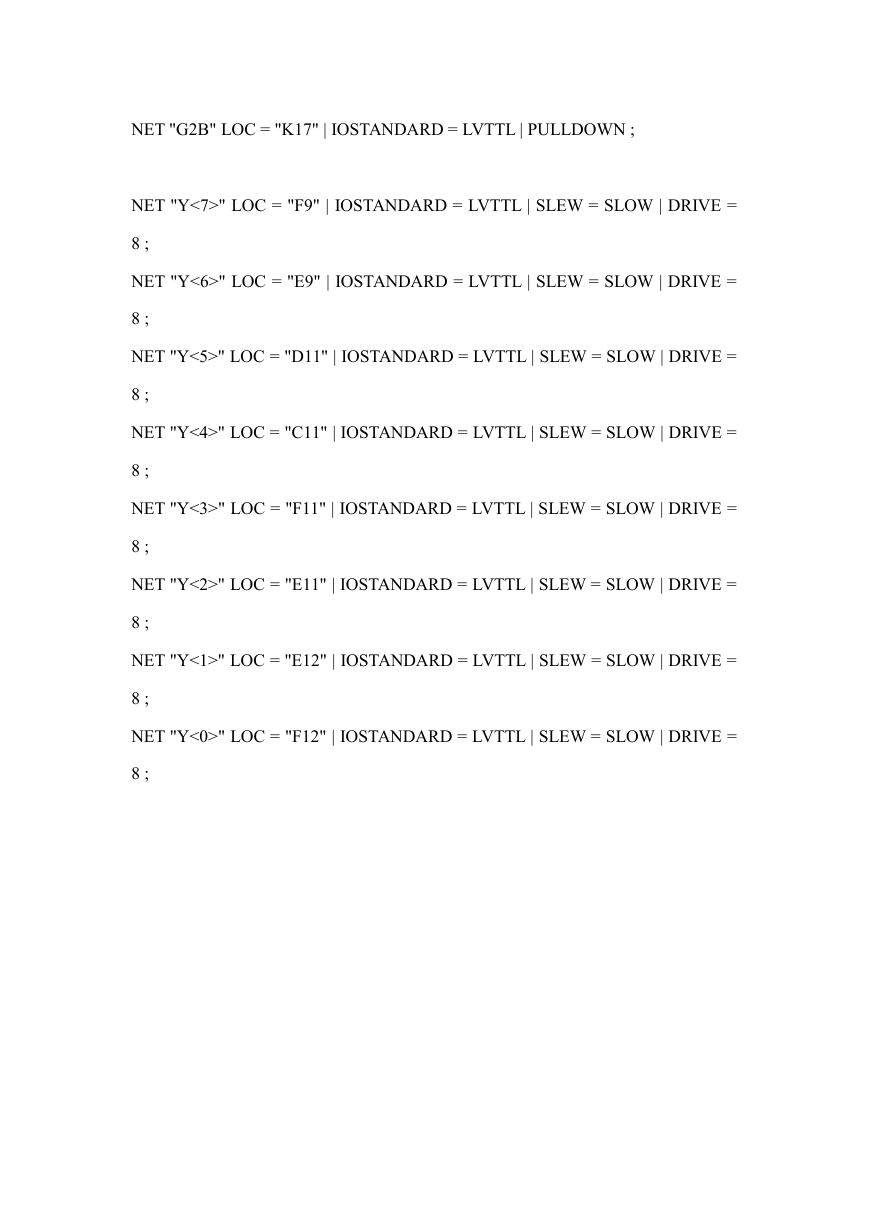

(1)实现如下八位可逆计数器

可逆计数器电路图及功能表如图 4-1 和表 4-1 所示。用 VHDL 完成该电路模

块的设计,并生成原理图。

clr

en

Up/Dn

clk

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

图 4-1 可逆计数器原理图

表 4-1 可逆计数器功能表

�

clr

1

0

0

0

en

X

0

1

1

输入

Up/Dn

X

X

1

0

输出

clk

X

X

↑

↑

Y7 ~ Y0

00000000

停止计数

计数器+1 操作

计数器-1 操作

(2)资源使用要求及实现方法:

1)用 LED0~LED7 作为计数器输出显示,LED7 为高位,LED0 为低位;

2)SW0 为计数方向 up/dn 控制;

3)SW1 为计数允许 EN 控制端;

4)BTN_EAST 为 clr 按钮;

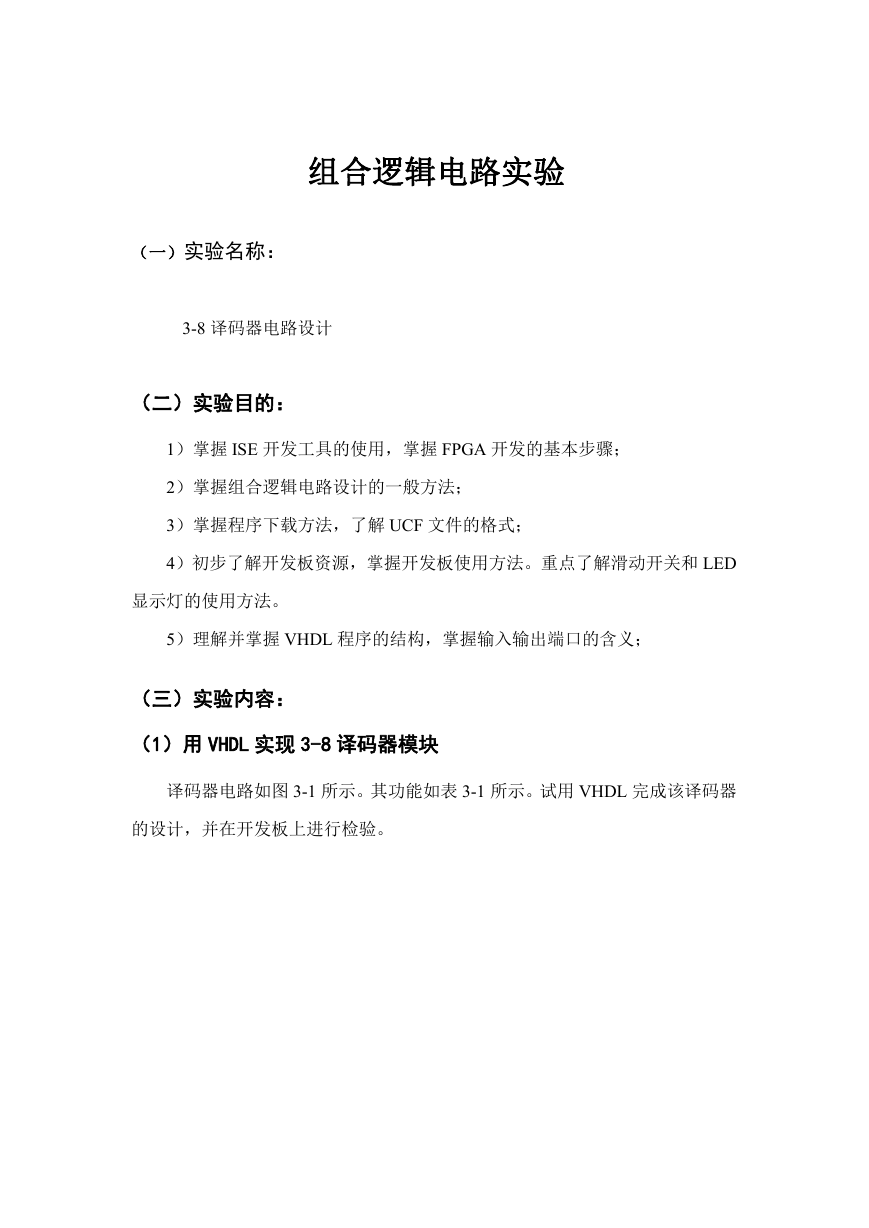

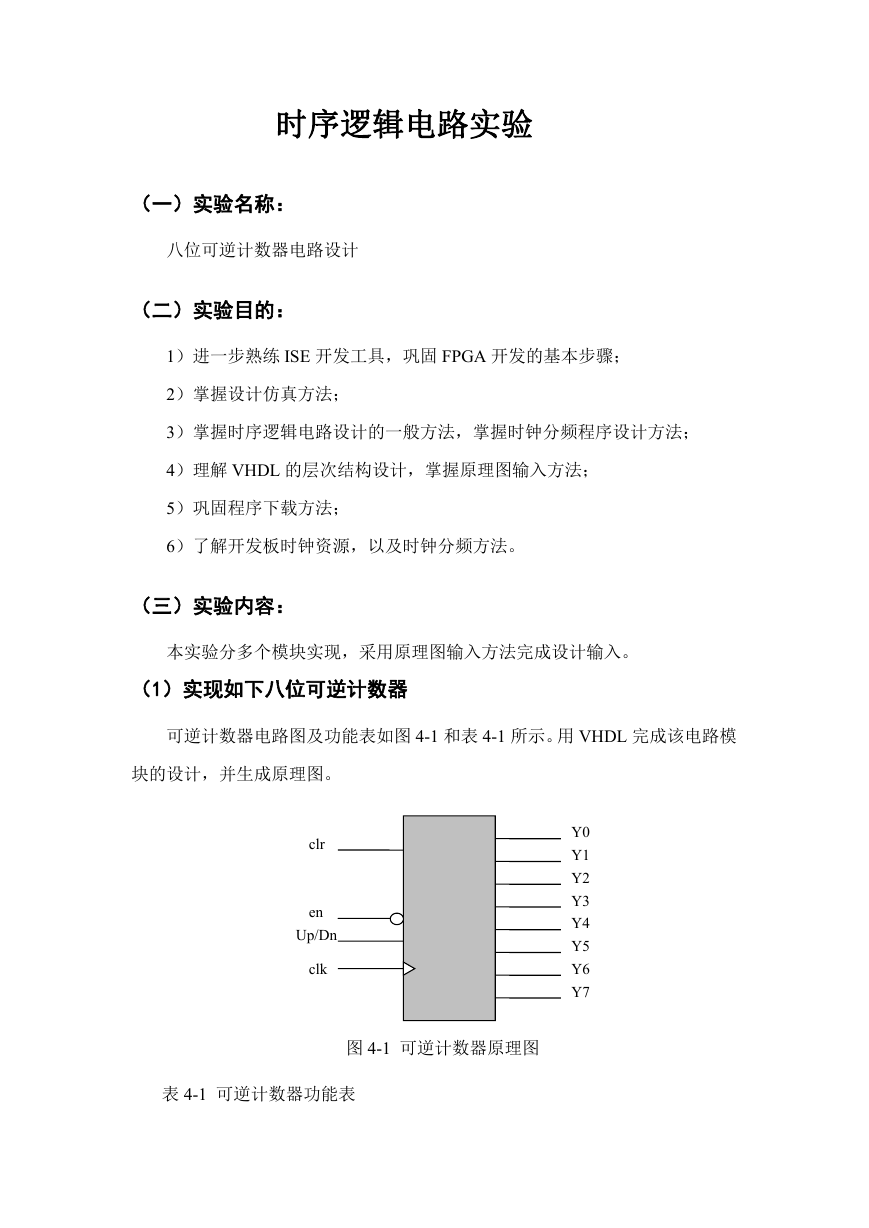

5)计数时钟频率为 1Hz,通过对 50Mhz 系统时钟分频得到,分频电路独立

编写一个模块,如图 4-2 所示。完成模块设计,并生成原理图;

50M clock

1/5000000

1Hz clock

图 4-2 1/5000000 分频器

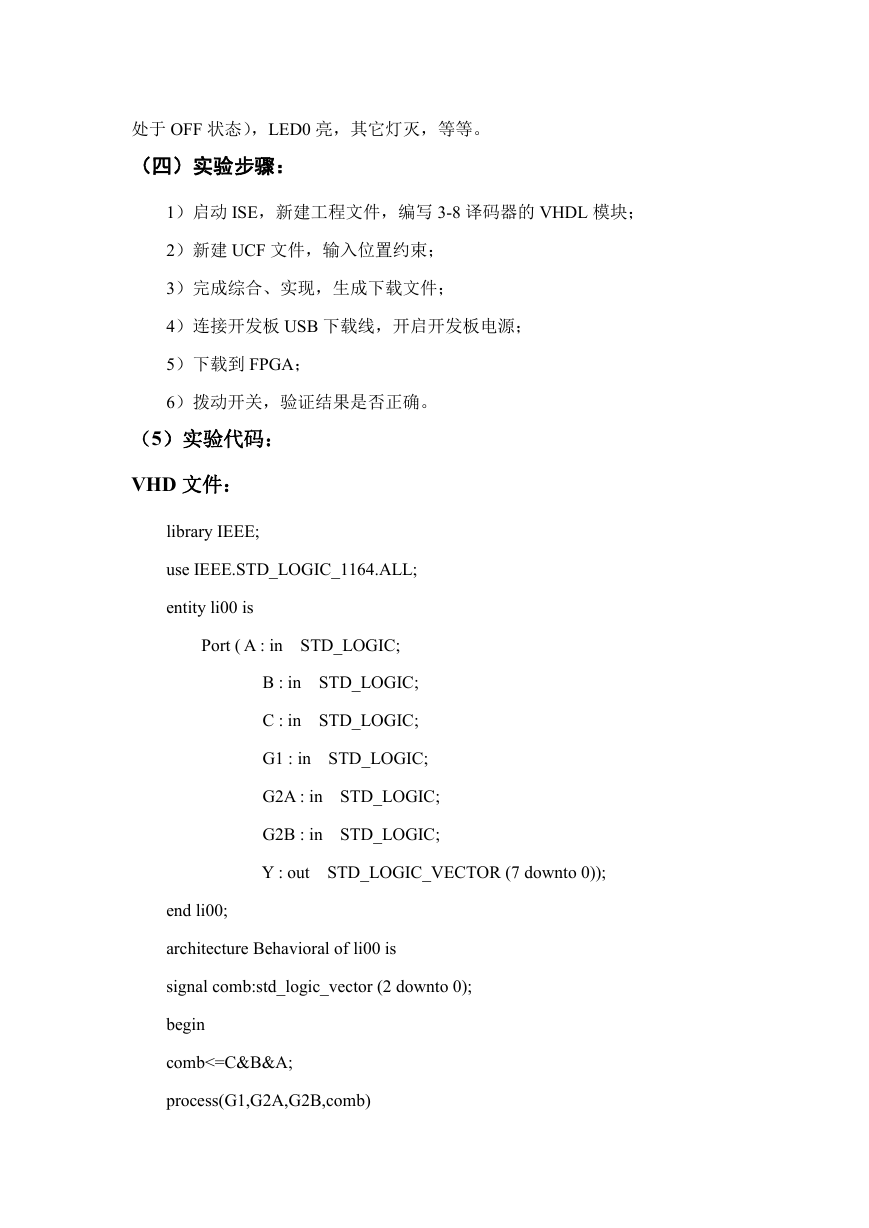

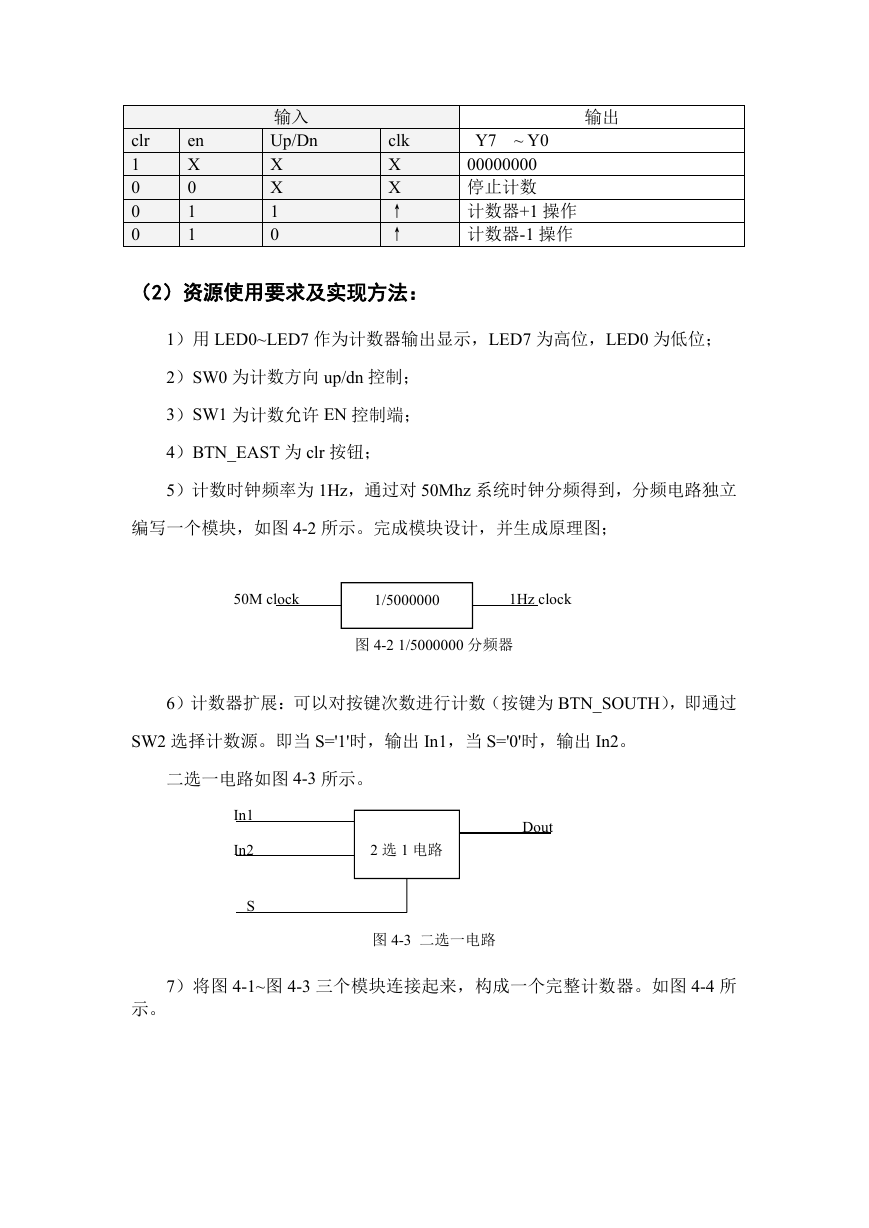

6)计数器扩展:可以对按键次数进行计数(按键为 BTN_SOUTH),即通过

SW2 选择计数源。即当 S='1'时,输出 In1,当 S='0'时,输出 In2。

二选一电路如图 4-3 所示。

In1

In2

S

2 选 1 电路

Dout

图 4-3 二选一电路

7)将图 4-1~图 4-3 三个模块连接起来,构成一个完整计数器。如图 4-4 所

示。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc