www.analog.eetchina.com

电子工程师必备电子书

ADC/DAC 应用设计宝典

目录

ADC 与 DAC 概念 …… 1

ADC 与 DAC 原理

……

1-3

ADC 与 DAC 基础知识详解

……

3-43

ADC 与 DAC 实用设计问答

……

43-45

20 款主流 ADC/DAC 器件综合介绍 ……

46-51

22 篇相关技术参考资料

……

51-56

第一章

第二章

第三章

第四章

第五章

第六章

�

www.analog.eetchina.com

第一章 ADC 与 DAC 概念

什么是 ADC?

“ADC”Analog-to-Digital Converter 的缩写,指模/数转换器或者模拟/数字转换器。真实世

界的模拟信号,例如温度、压力、声音或者图像等,需要转换成更容易储存、处理和发射的数

字形式。模/数转换器可以实现这个功能。

什么是 DAC?

“DAC”是 Digital-to-Analog Canverter 的缩写,指数/模转换器或者数字/模拟转换器。

ADC 和 DAC 有什么区别?

不,这不是一个“愚弄人的”问题或脑筋急转弯,并且我认为我们的读者都非常清楚模数转换

器(ADC)及数模转换器(DAC)的基本功能。

但在如何使用这些转换器以及人们的认知度上也存在着哲理性区别。用最简单的话讲,ADC 是

用来捕获大量未知的信号,并把它转换成已知的描述。相反,DAC 是接受完全已知的、深刻理

解的描述,然后“简单地”产生等效的模拟数值。

简而言之,DAC 工作在确定的领域,而 ADC 则工作在随机输入信号和未知性领域,只要输入在

规定的范围内。在传统的信号处理理论中,比如在 Harry L.Van Trees 的经典著作 Detection,

Estimation, and Modulation Theory 中介绍的那样,信号处理面临着不同程度的挑战。举例

来说,一个特征参数已经相当明了的信号(如受到 AM 调制的模拟信号)与一个充满了许多未知参

数的信号(如受到噪声干扰的雷达反射波)相比,评估起来要容易得多。

因此 ADC 面临的挑战确实要比 DAC 大得多。为了充分发挥 ADC 的功能,特别是较高性能(速度或

精度)的 ADC,需要采用精心设计的模拟信号调节输入信道,通常还带有与 ADC 本身精确匹配的

ADC 驱动器。

DAC 的设计要简单得多。不过这种相对的简单不应让设计师对 DAC 设计产生松懈心理。实际应

用中设计师很容易对 DAC 的模拟输出电路不予以足够的重视,比如在摆率、输出驱动(电压、电

流、范围)等参数和负载故障保护方面,而这样做很容易导致原型评估和产品现场应用时发生令

人头疼的电路和系统级问题。

第二章 ADC 与 DAC 原理

一、 转换原理

�

www.analog.eetchina.com

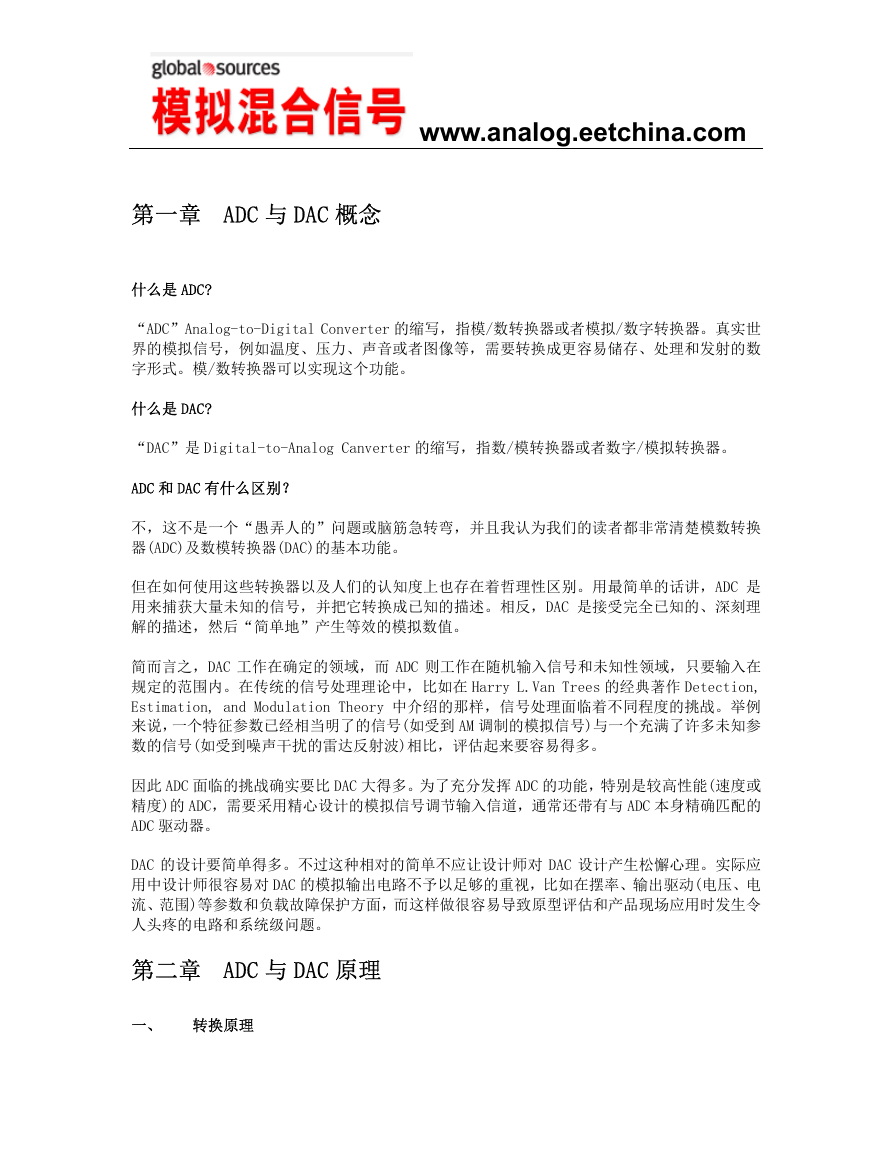

数字量是用代码按数位组合起来表示的,对于有权码,每位代码都有一定的位权。为了将数字

量转换成模拟量,必须将每 1 位的代码按其位权的大小转换成相应的模拟量,然后将这些模拟

量相加,即可得到与数字量成正比的总模拟量,从而实现了数字—模拟转换。这就是组成 D/A

转换器的基本指导思想。

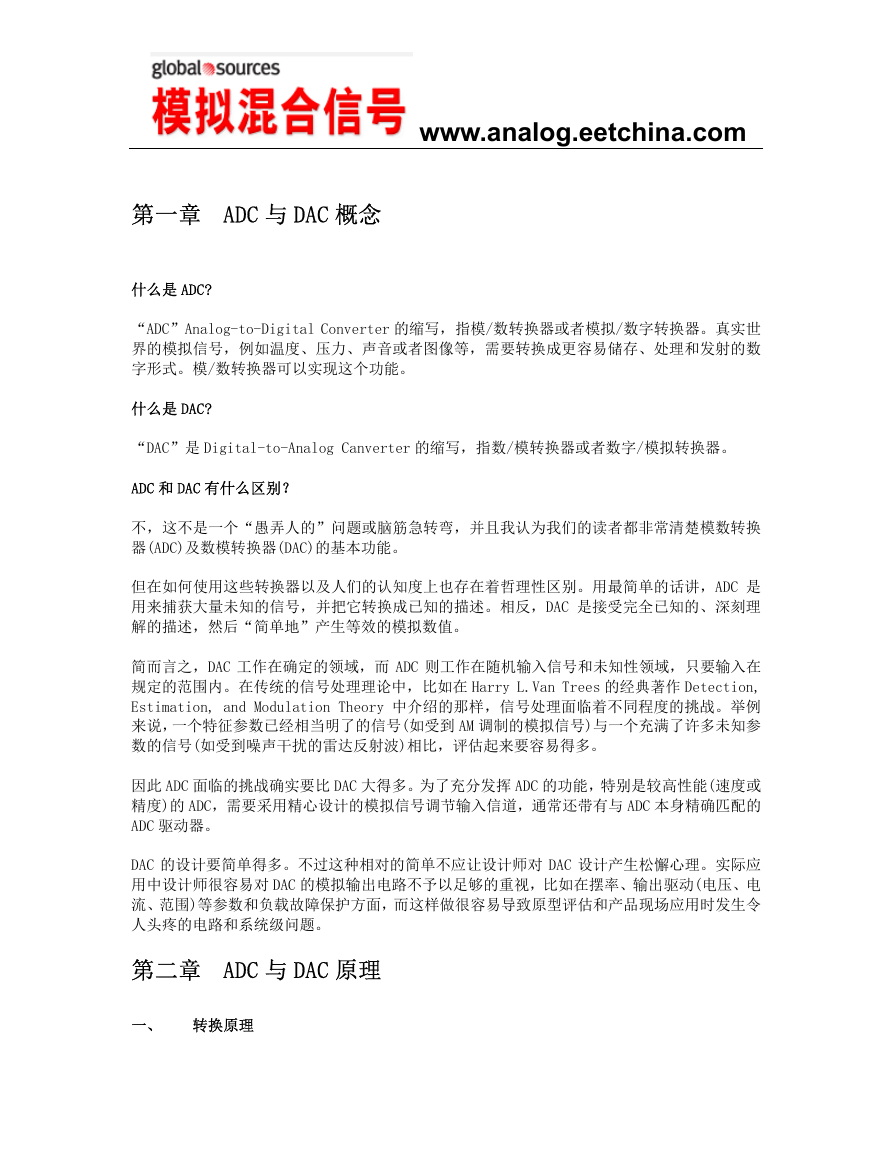

下图表示了 4 位二进制数字量与经过 D/A 转换后输出的电压模拟量之间的对应关系。 由下图还

可看出,两个相邻数码转换出的电压值是不连续的,两者的电压差由最低码位代表的位权值决

定。它是信息所能分辨的最小量,也就是我们所说的用 1LSB(Least Significant Bit)表示。

对应于最大输入数字量的最大电压输出值(绝对值),用 FSR(Full Scale Range)表示。图中

1LSB=1kV;1FSR=15kV(k 为比例系数)。

D/A 转换器输入数字量与输出电压的对应关系

二、一般组成

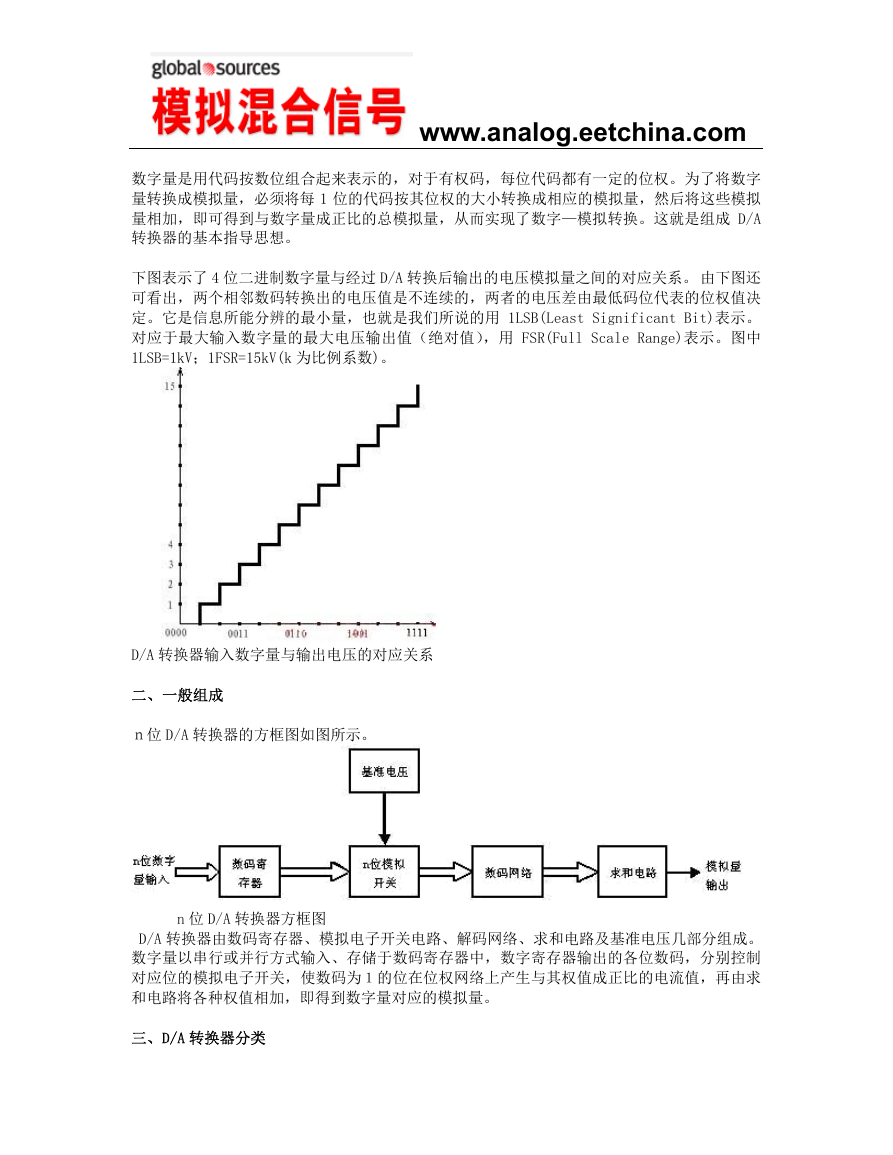

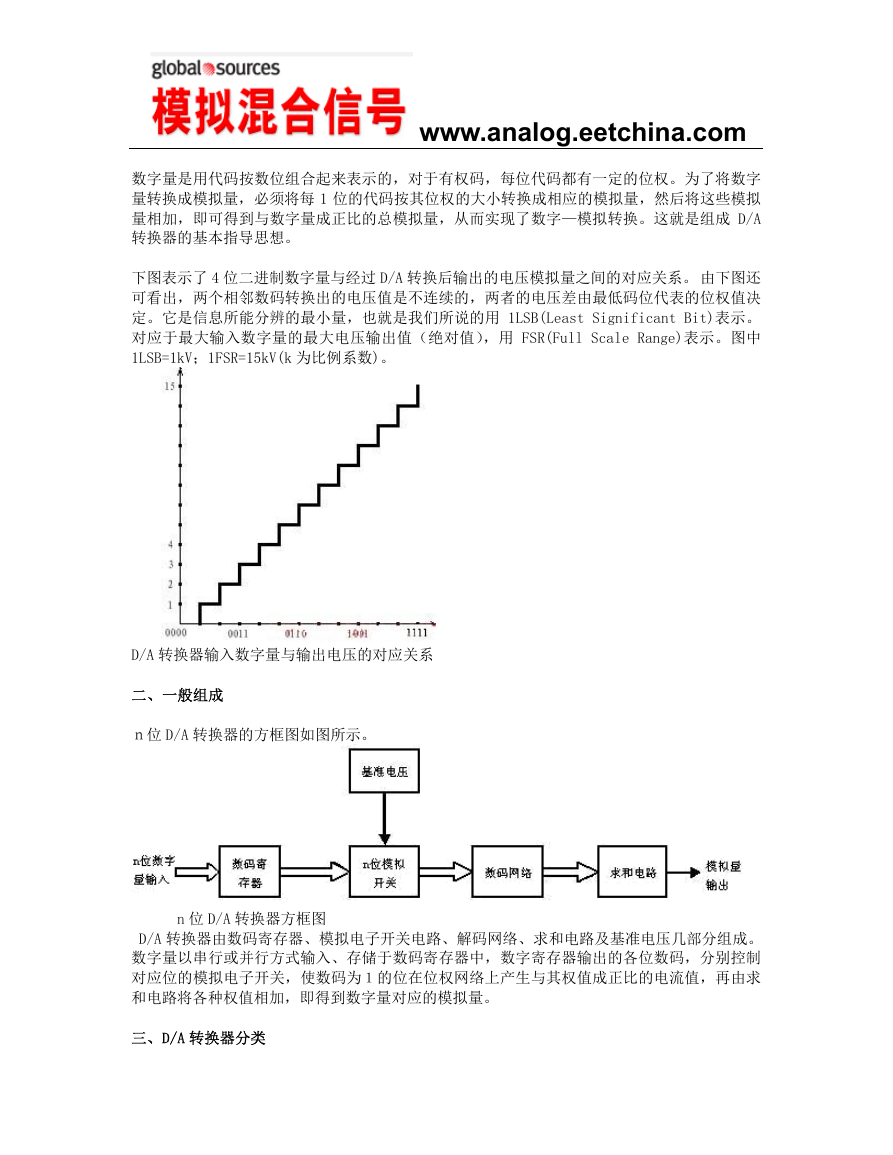

n位 D/A 转换器的方框图如图所示。

n 位 D/A 转换器方框图

D/A 转换器由数码寄存器、模拟电子开关电路、解码网络、求和电路及基准电压几部分组成。

数字量以串行或并行方式输入、存储于数码寄存器中,数字寄存器输出的各位数码,分别控制

对应位的模拟电子开关,使数码为1的位在位权网络上产生与其权值成正比的电流值,再由求

和电路将各种权值相加,即得到数字量对应的模拟量。

三、D/A 转换器分类

�

www.analog.eetchina.com

第三章 ADC 与 DAC 基础知识详解

本系列文章分为 5 个部分,第一部分介绍采样的概念以及奈奎斯特(Nyquist)采样准则。第 5

部分同样也说明了如何运用欠采样和抗混叠滤波器。

第一部分

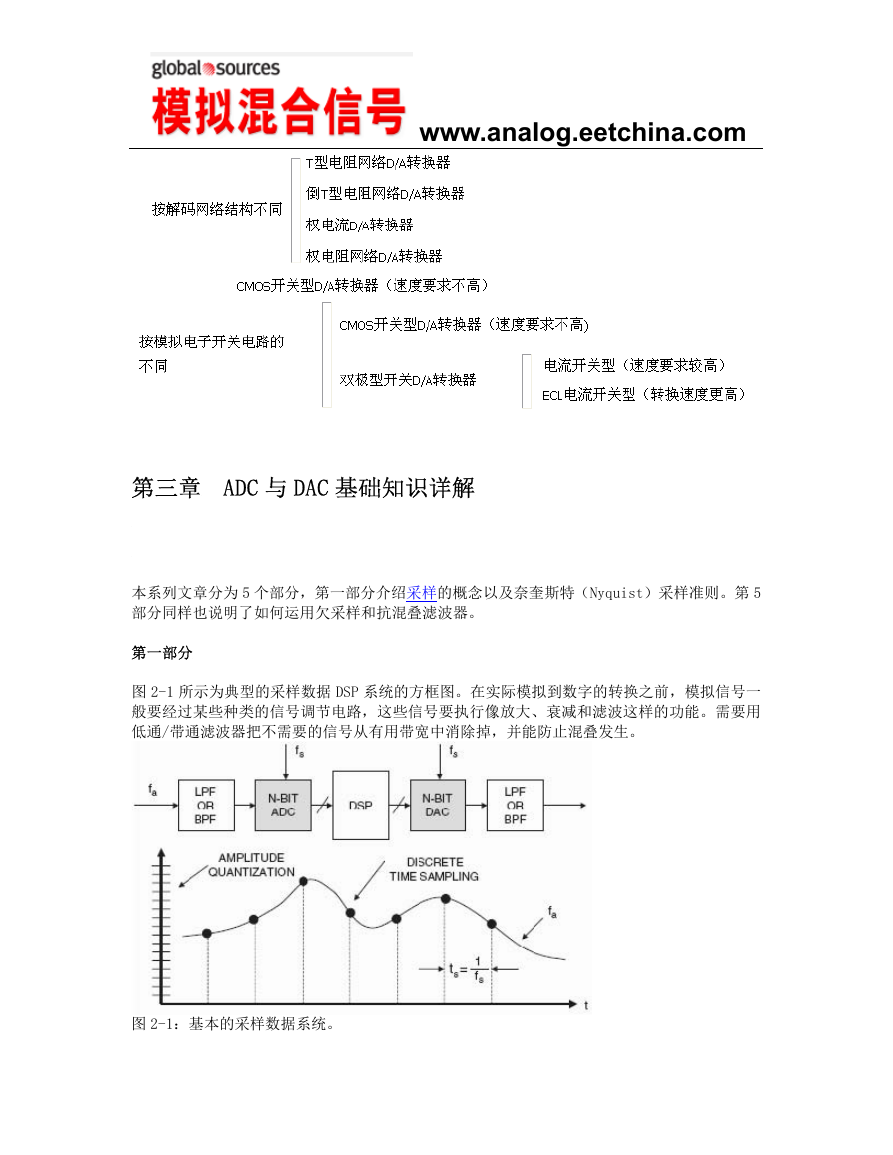

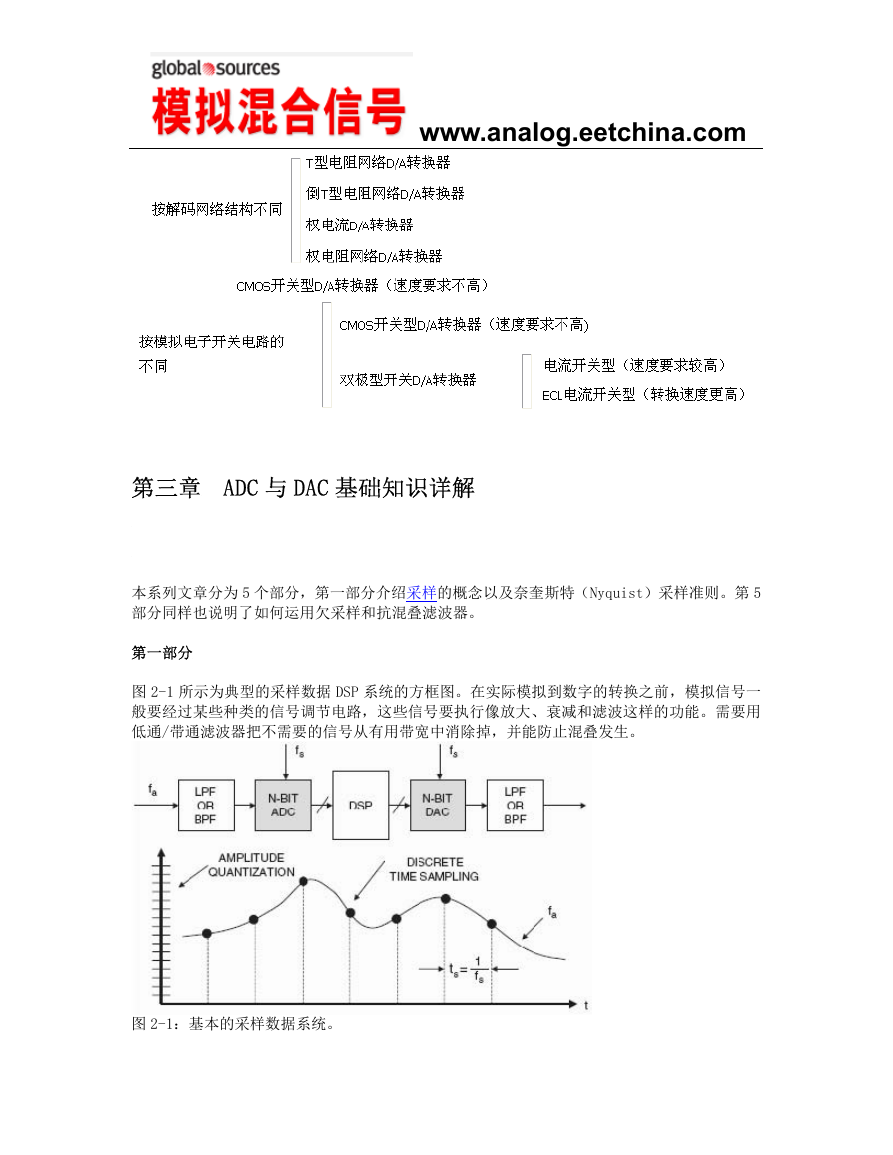

图 2-1 所示为典型的采样数据 DSP 系统的方框图。在实际模拟到数字的转换之前,模拟信号一

般要经过某些种类的信号调节电路,这些信号要执行像放大、衰减和滤波这样的功能。需要用

低通/带通滤波器把不需要的信号从有用带宽中消除掉,并能防止混叠发生。

图 2-1:基本的采样数据系统。

�

www.analog.eetchina.com

图 2-1 所示的系统为一个实时系统,也就是说到 ADC 的信号是以等于 fs 的速率被连续地采样,

然后 ADC 又以这样的速率向 DSP 提供新的样本。为了保持实时的工作, DSP 必须在采样间隔内

执行所有需要的计算 1/fs,并在来自 ACD 的下一个样本出现之前,把输出样本提供给 DAC。典

型的 DSP 功能的实例即是数字滤波器。

在 FFT 分析中,数据模块首先被传输到 DSP 内存中。 FFT 在新的数据模块被传输到存储器时被

计算,以便保持实时的操作。在数据传输间隔期间,DSP 必需计算 FFT,以便为处理下一个数

据模块做好准备。

要注意的是:只有在DSP数据必须被转换回模拟信号(例如在语音带宽或视频应用)的情况下,才

需要DAC。在许多应用中,在最初的A/D转换后,信号要完全地保持数字格式。同样,在一些应

用中,如在CD播放器电子设备中,DSP单独负责产生到DAC的信号。如果采用 DAC ,也必须采用

抗镜像滤波器把镜像频率消除。

在实际的模拟到数字和数字到模拟的转换过程中,涉及到两个关键的概念:离散时间采样和因

量子化产生的有限振幅分辨率。对这两个概念的理解是 DSP 应用的关键。

模拟信号的离散时间采样

模拟信号的离散时间采样和量子化的概念如图 2-1 所示。连续的模拟信号必需在离散间隔内被

采样,ts = 1/fs,对它必需加以仔细地选择以确保原始模拟信号的正确表示。很显然,被采用

的样本越多(采样率越快), 数字表示更精确,但是如果被采用的样本越少(采样率越慢),总会

遇到重要信息实际上被丢失的点。这让我们提出了如图 2-2 中给出的奈奎斯特定律。

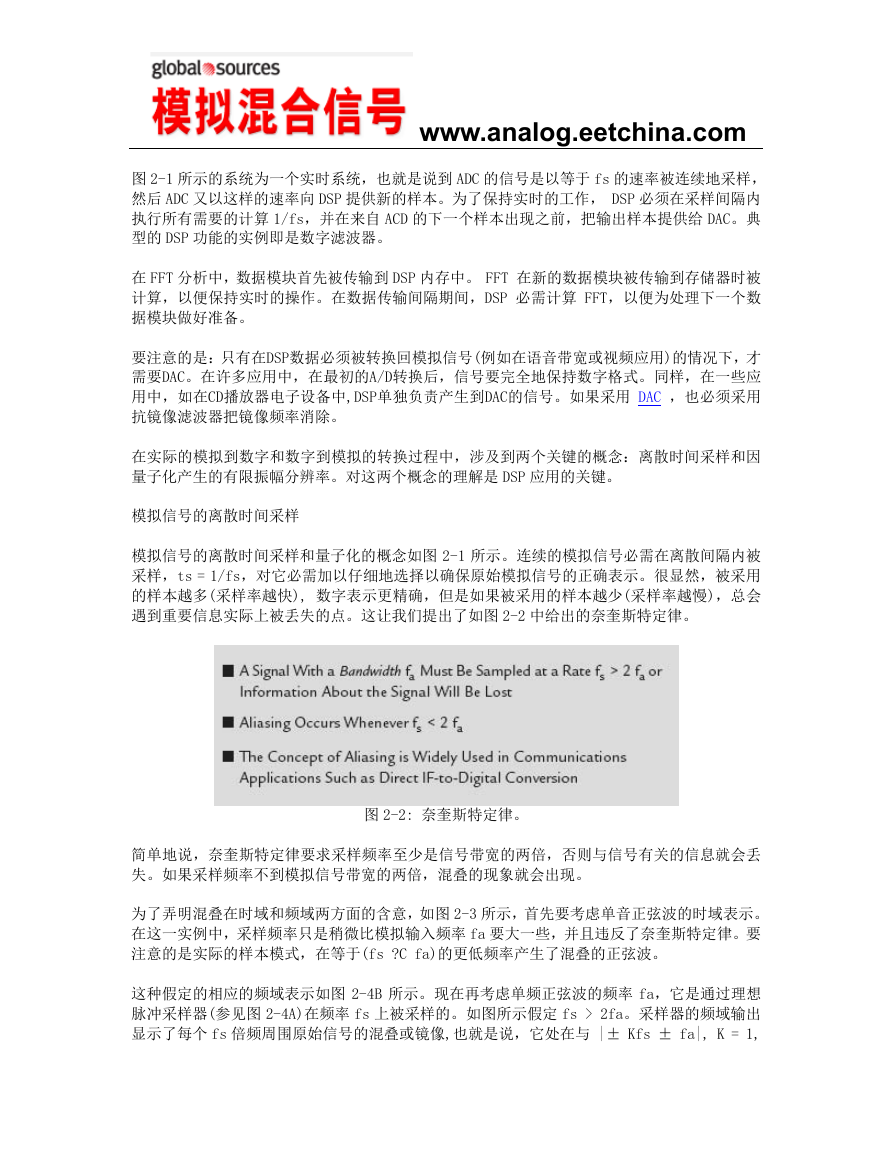

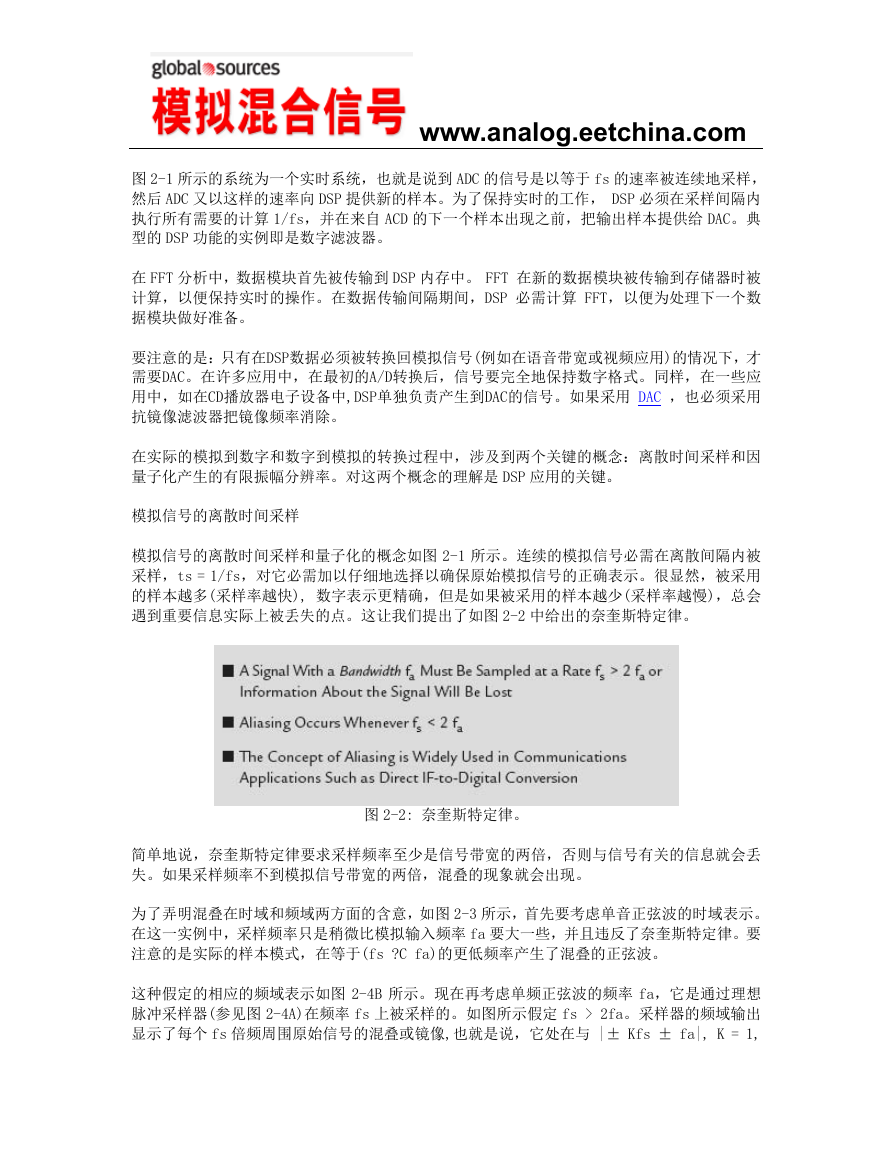

图 2-2: 奈奎斯特定律。

简单地说,奈奎斯特定律要求采样频率至少是信号带宽的两倍,否则与信号有关的信息就会丢

失。如果采样频率不到模拟信号带宽的两倍,混叠的现象就会出现。

为了弄明混叠在时域和频域两方面的含意,如图 2-3 所示,首先要考虑单音正弦波的时域表示。

在这一实例中,采样频率只是稍微比模拟输入频率 fa 要大一些,并且违反了奈奎斯特定律。要

注意的是实际的样本模式,在等于(fs ?C fa)的更低频率产生了混叠的正弦波。

这种假定的相应的频域表示如图 2-4B 所示。现在再考虑单频正弦波的频率 fa,它是通过理想

脉冲采样器(参见图 2-4A)在频率 fs 上被采样的。如图所示假定 fs > 2fa。采样器的频域输出

显示了每个 fs 倍频周围原始信号的混叠或镜像,也就是说,它处在与 |± Kfs ± fa|, K = 1,

�

2, 3, 4, 相等的频率上。

www.analog.eetchina.com

图 2-3:时域内的混叠。

图 2-4: 采用理想的采样器进行采样的、频率为 fa 的 模拟信号在|±Kfs ±fa|, K = 1, 2, 3, ….

处具有镜像。

奈奎斯特带宽被定义为从 dc 到 fs/2 的频谱。该频谱被分割为一个有着无限数目的奈奎斯特区,

如图所示,每个区有一个与 0.5 fs 相等的带宽。实际上理想的采样器—继 FFT 处理器之后—

由 ADC 所取代。FFT 处理器只能提供从 dc 到 fs/2 的输出,如出现在第一个奈奎斯特区中的信

号或混叠。

现在再对第一个奈奎斯特区(见图 2-4B)外的信号予以考虑。信号频率只稍微比采样频率像小一

点,这与图 2-3 所示的时域表示中显示的状态是一致的。要注意的是:即使该信号在第一个奈

奎斯特区外,其镜像 (或混叠)—(fs?Cfa)—却不在第一个奈奎斯特区内。再返回图 2-4A,显

然如果不需要的信号出现在任何镜像频率的 fa 上,它也会出现在 fa 中,因此,在第一个奈奎

斯特区中产生不真实的频率成分。

这与模拟混合处理相类似,并且意味着在需要采样器之前就要进行一些滤波,以去除在奈奎斯

特区之外的频率成分,但是,那些混叠的成分却不能进入奈奎斯特区内。滤波器的性能将取决

于带外信号与 fs/2 有多近,以及所需衰减的量。

基带抗混叠滤波器

�

www.analog.eetchina.com

基带采样意味着要被采样的信号位于第一个奈奎斯特区中。要特别强调的是:在理想采样器的

输入中没有输入滤波, 任何落在奈奎斯特区内的奈奎斯特带宽之外的频率成分(或是信号或是

噪声)将会被混叠回第一个奈奎斯特区。基于这个原因, 抗混叠滤波器被用在几乎所有的正在

采样 ADC 应用中,以去除这些不需要的信号。

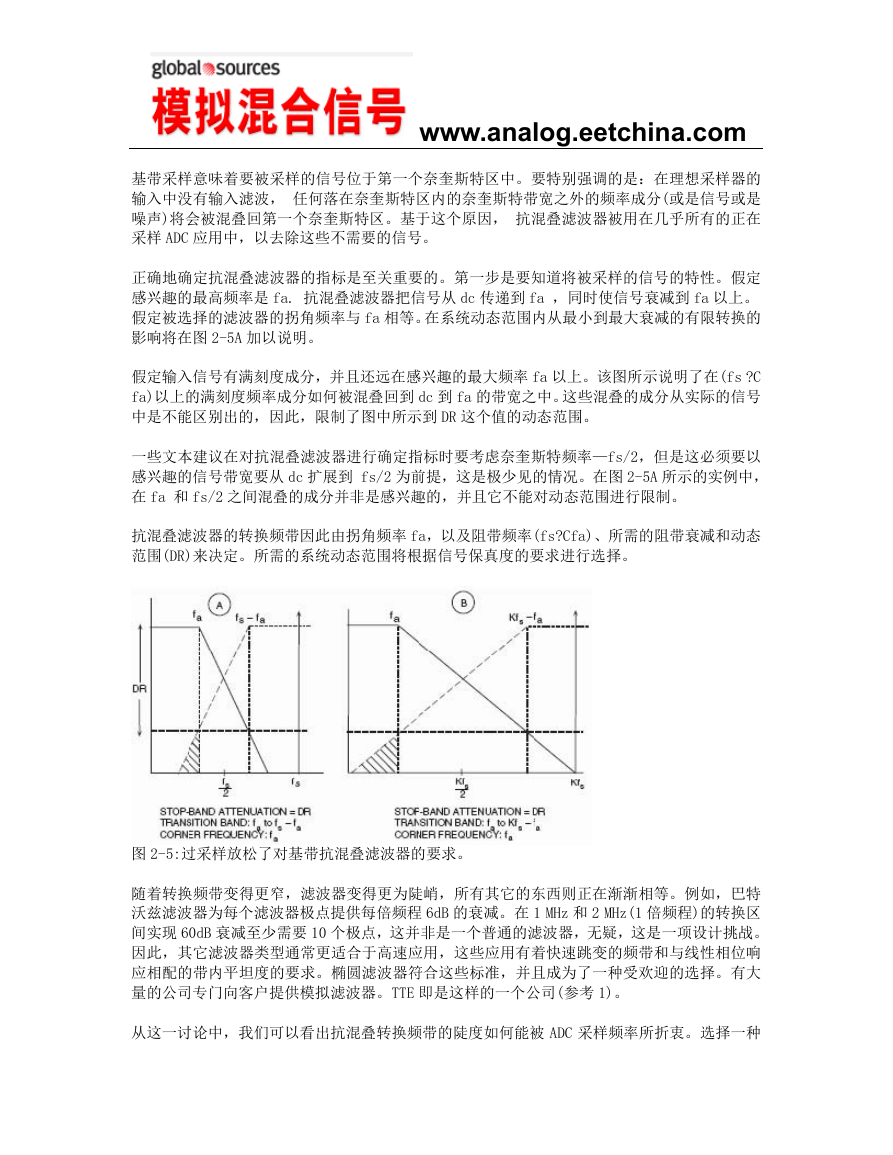

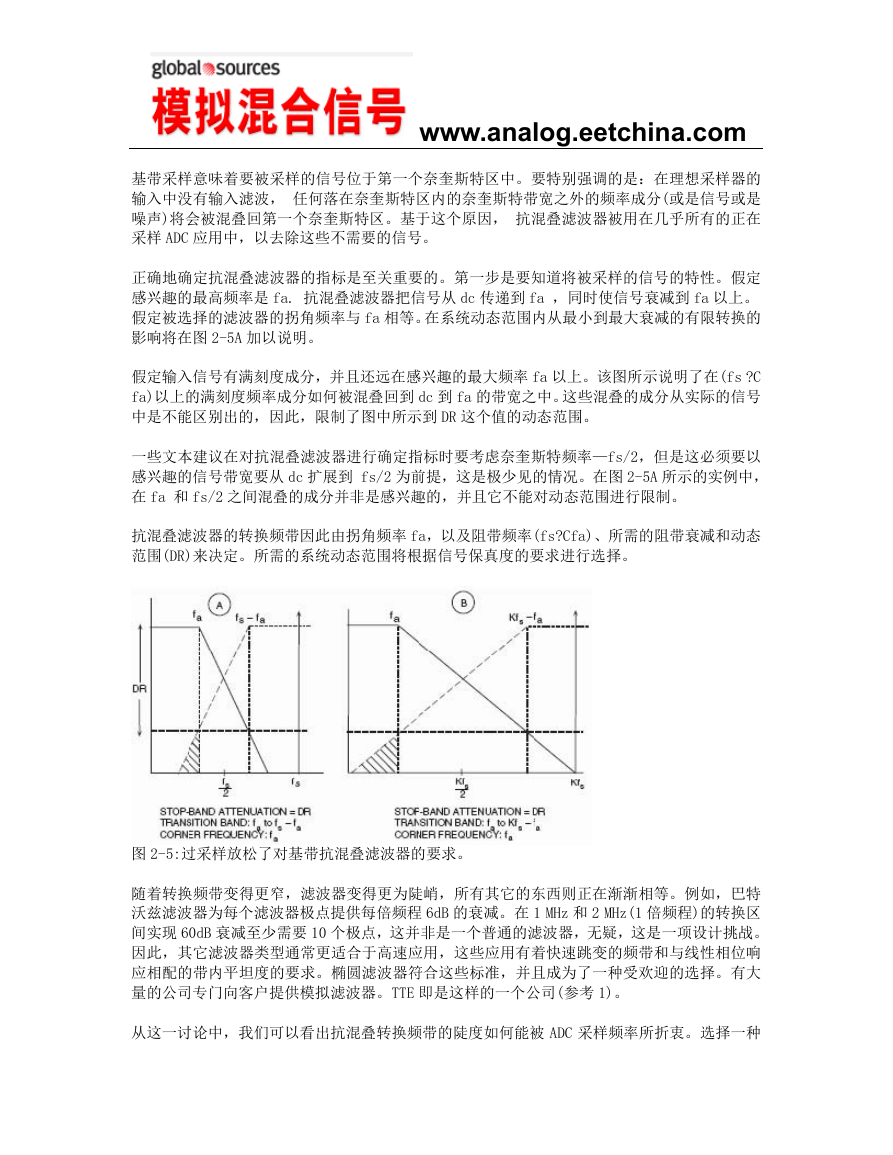

正确地确定抗混叠滤波器的指标是至关重要的。第一步是要知道将被采样的信号的特性。假定

感兴趣的最高频率是 fa. 抗混叠滤波器把信号从 dc 传递到 fa ,同时使信号衰减到 fa 以上。

假定被选择的滤波器的拐角频率与 fa 相等。在系统动态范围内从最小到最大衰减的有限转换的

影响将在图 2-5A 加以说明。

假定输入信号有满刻度成分,并且还远在感兴趣的最大频率 fa 以上。该图所示说明了在(fs ?C

fa)以上的满刻度频率成分如何被混叠回到 dc 到 fa 的带宽之中。这些混叠的成分从实际的信号

中是不能区别出的,因此,限制了图中所示到 DR 这个值的动态范围。

一些文本建议在对抗混叠滤波器进行确定指标时要考虑奈奎斯特频率—fs/2,但是这必须要以

感兴趣的信号带宽要从 dc 扩展到 fs/2 为前提,这是极少见的情况。在图 2-5A 所示的实例中,

在 fa 和 fs/2 之间混叠的成分并非是感兴趣的,并且它不能对动态范围进行限制。

抗混叠滤波器的转换频带因此由拐角频率 fa,以及阻带频率(fs?Cfa)、所需的阻带衰减和动态

范围(DR)来决定。所需的系统动态范围将根据信号保真度的要求进行选择。

图 2-5:过采样放松了对基带抗混叠滤波器的要求。

随着转换频带变得更窄,滤波器变得更为陡峭,所有其它的东西则正在渐渐相等。例如,巴特

沃兹滤波器为每个滤波器极点提供每倍频程 6dB 的衰减。在 1 MHz 和 2 MHz(1 倍频程)的转换区

间实现 60dB 衰减至少需要 10 个极点,这并非是一个普通的滤波器,无疑,这是一项设计挑战。

因此,其它滤波器类型通常更适合于高速应用,这些应用有着快速跳变的频带和与线性相位响

应相配的带内平坦度的要求。椭圆滤波器符合这些标准,并且成为了一种受欢迎的选择。有大

量的公司专门向客户提供模拟滤波器。TTE 即是这样的一个公司(参考 1)。

从这一讨论中,我们可以看出抗混叠转换频带的陡度如何能被 ADC 采样频率所折衷。选择一种

�

www.analog.eetchina.com

更高的采样率(过采样)能降低对转换频带陡度(亦即滤波器复杂性)的要求,付出的代价就是采

用更快的 ADC 和以更快的速率处理数据。如图 2-5B 所示,该图显示了通过因子 K 增加采样频率

的效果,同时又保持了相同的模拟拐角频率—fa、相同的动态范围—DR 等要求。更宽的转换频

带(fa 到(Kfs ?C fa))使得这种滤波器比图 2-5A 所示的滤波器在设计上更易实现。

抗混叠滤波器的设计过程是从选择 2.5 到 4 倍 fa 的初始采样率开始的。确定滤波器指标要以

所需的动态范围为基础,并且要看这样的滤波器在系统成本和性能的约束方面是否可行。如果

不可能,就要对更高的采样率予以考虑,这可能需要采用更快的 ADC。应当注意的是西格玛-德

尔塔 ADC 是固有的过采样转换器,并且会放松对模拟抗混叠滤波器的要求,因此,也成为这种

架构的一个额外的优越性。

如果确定在阻带频率(fs ?C fa)上从不会有满刻度信号,对抗混叠滤波器的要求在某种程度上

也会被放松。在许多应用中,满刻度信号是不可能出现在这个频率中的。如果在频(fs ?C fa)

的最大信号将从不超过满刻度以下的 XdB ,那么,滤波器阻带衰减的要求也会有与之相同数量

的减少。在以这一信号认识为基础的(fs ?C fa)上,阻带衰减的新的要求目前仅有 (DR ?C X)dB。

在进行这种类型的假定时,要对可能出现在最大信号频率 fa 以上的不需要的任何噪声信号加以

仔细处理, 这些信号也将会混叠回信号带宽中。

参考 1. Active and Passive Electrical Wave Filter Catalog, Vol. 34, TTE, Incorporated,

2251 Barry Avenue, Los Angeles, CA 90064.

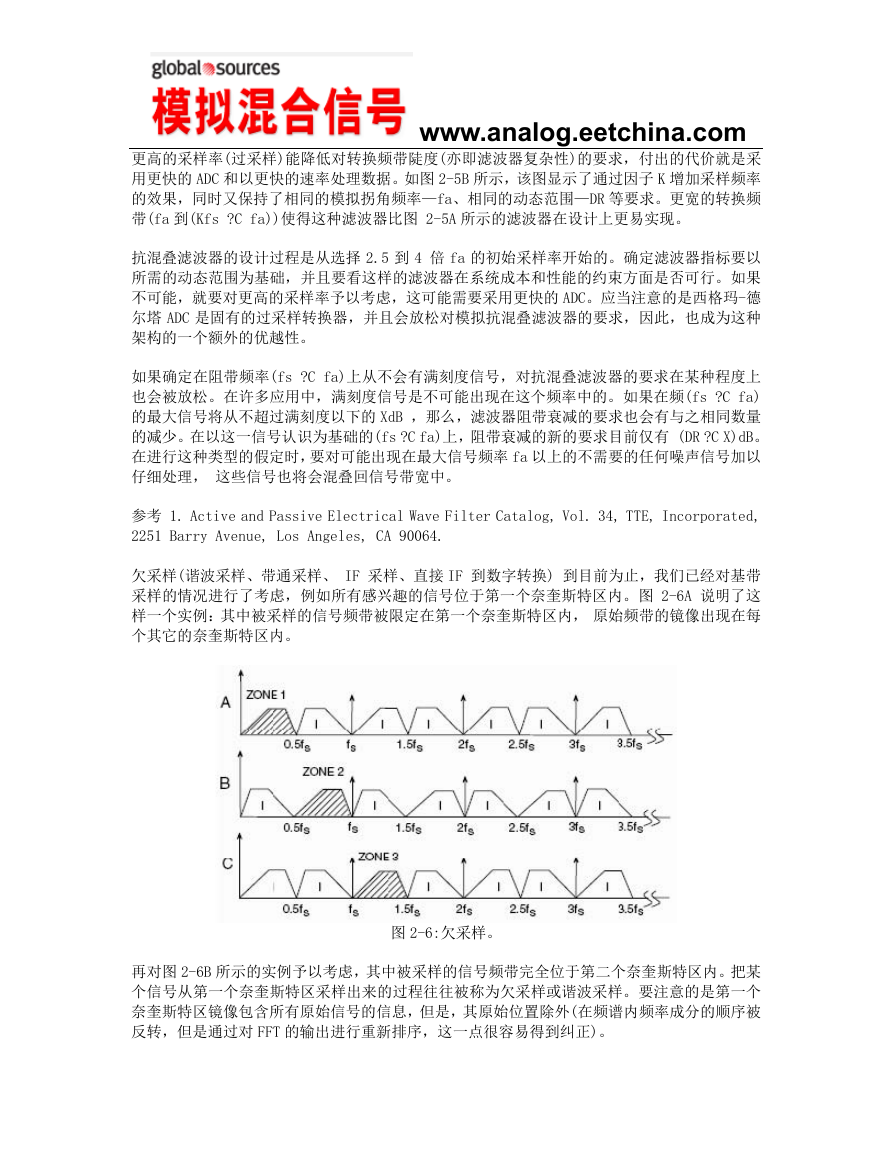

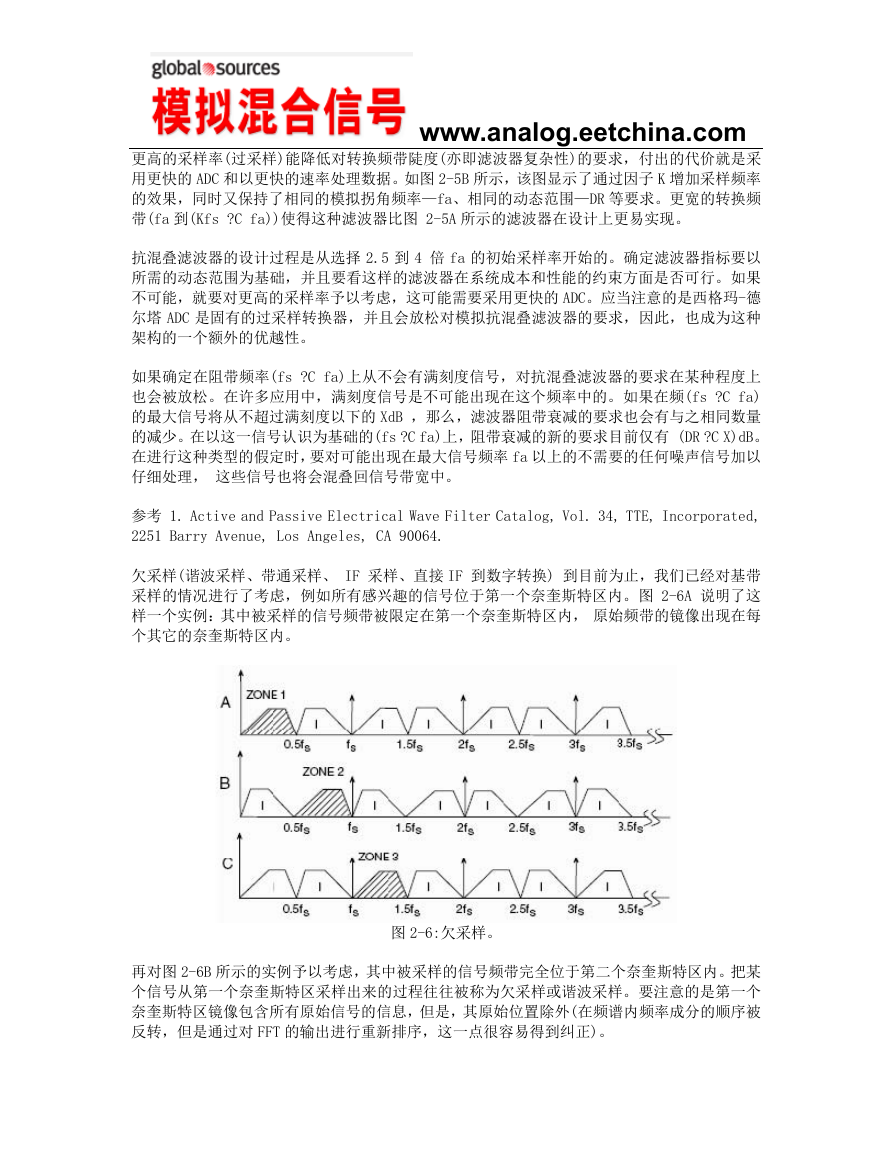

欠采样(谐波采样、带通采样、 IF 采样、直接 IF 到数字转换) 到目前为止,我们已经对基带

采样的情况进行了考虑,例如所有感兴趣的信号位于第一个奈奎斯特区内。图 2-6A 说明了这

样一个实例:其中被采样的信号频带被限定在第一个奈奎斯特区内, 原始频带的镜像出现在每

个其它的奈奎斯特区内。

图 2-6:欠采样。

再对图 2-6B 所示的实例予以考虑,其中被采样的信号频带完全位于第二个奈奎斯特区内。把某

个信号从第一个奈奎斯特区采样出来的过程往往被称为欠采样或谐波采样。要注意的是第一个

奈奎斯特区镜像包含所有原始信号的信息,但是,其原始位置除外(在频谱内频率成分的顺序被

反转,但是通过对 FFT 的输出进行重新排序,这一点很容易得到纠正)。

�