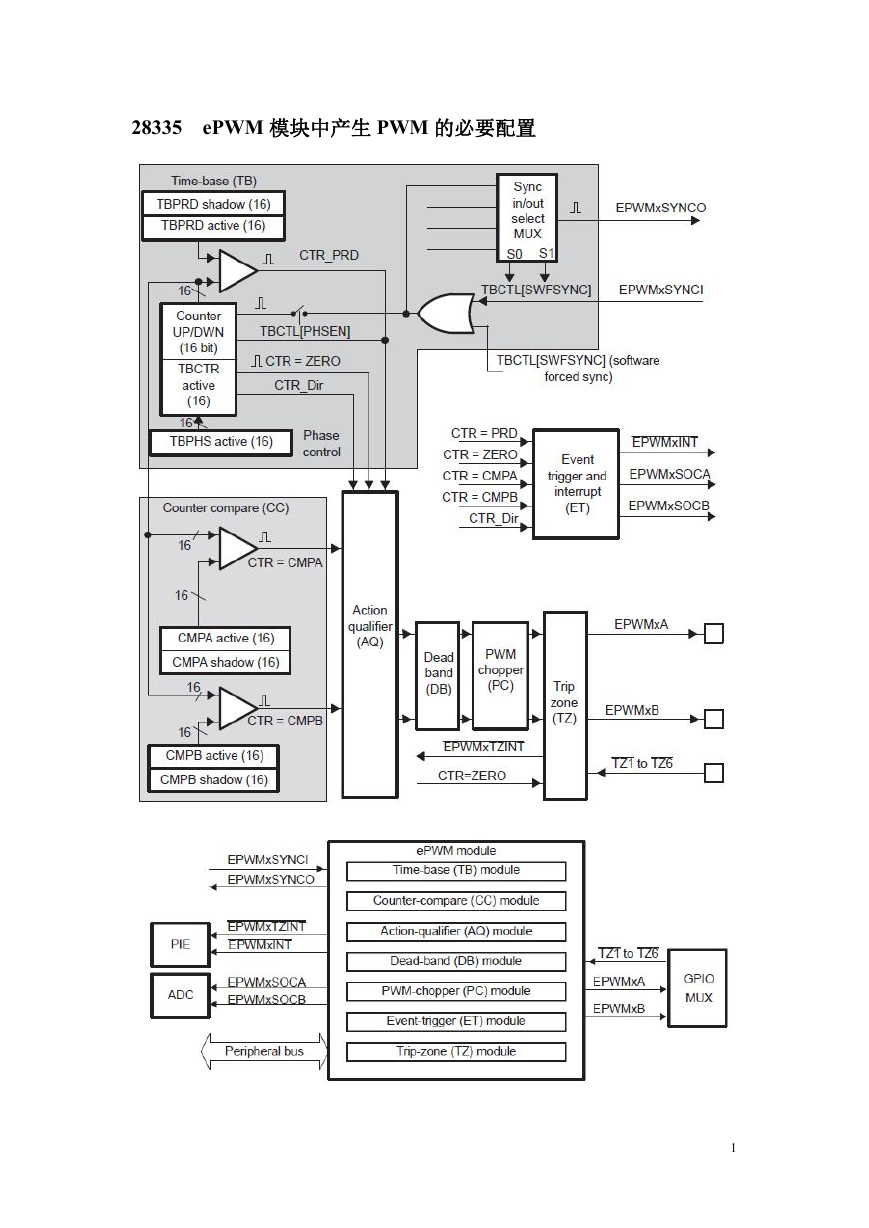

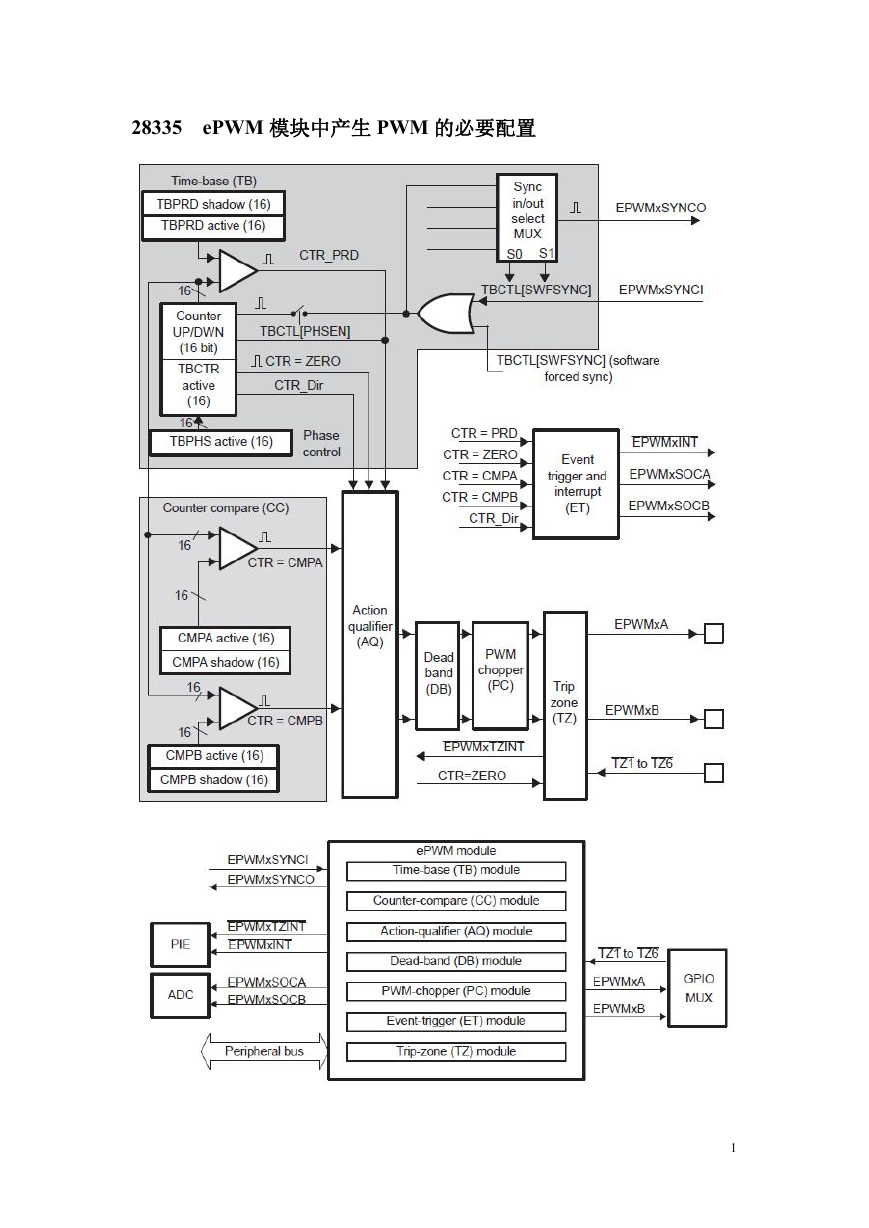

28335 ePWM 模块中产生 PWM 的必要配置

1

�

一个 ePWM module 包括 Time-base (TB) module,Counter-compare (CC) module,

Action-qualifier (AQ) module,Dead-band (DB) module,PWM-chopper (PC) module,

Event-trigger (ET) module,Trip-zone (TZ) module 等七个模块。正常的发出 PWM 波要配

置 TB(定时器模块)、CC(比较计数器模块)、AQ(比较方式预设模块)、DB(死区模

块)、ET(事件触发模块)等五个模块。

2

�

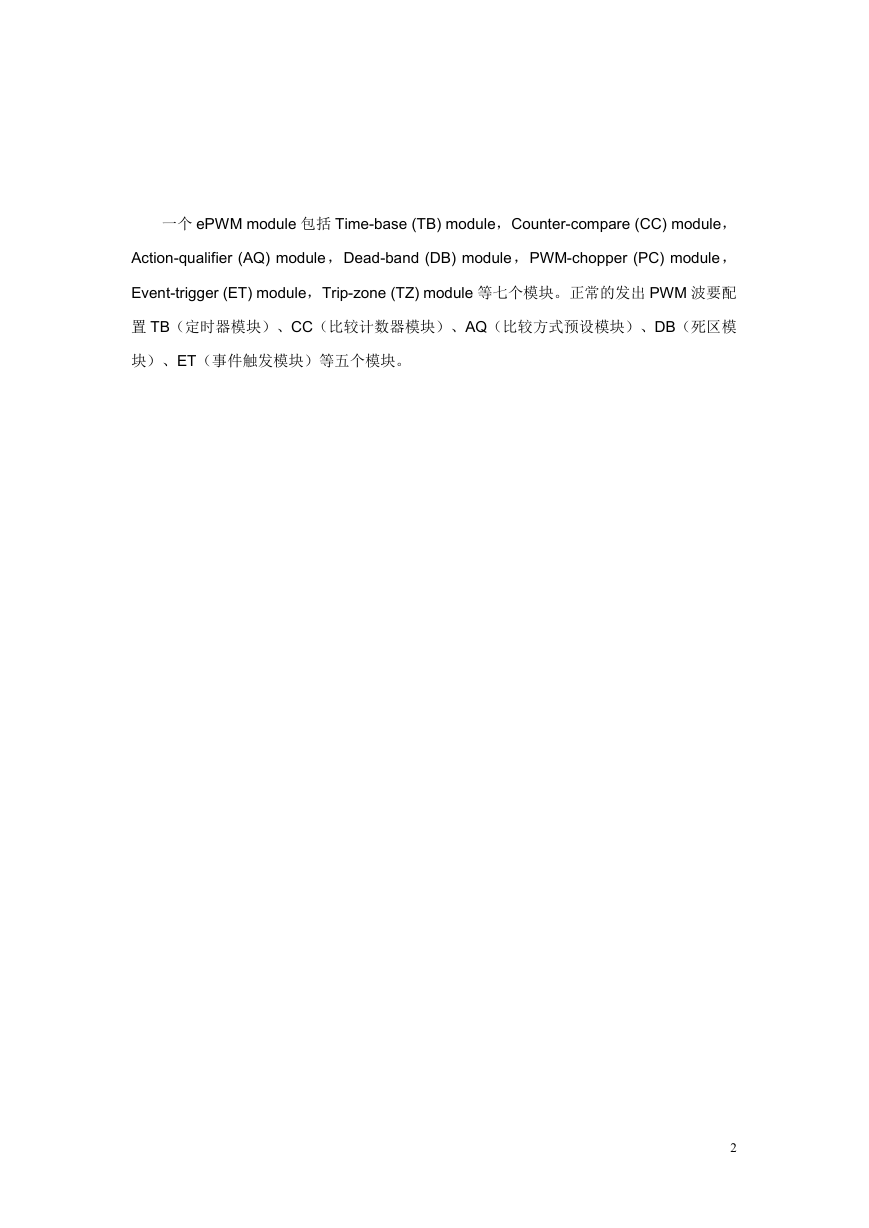

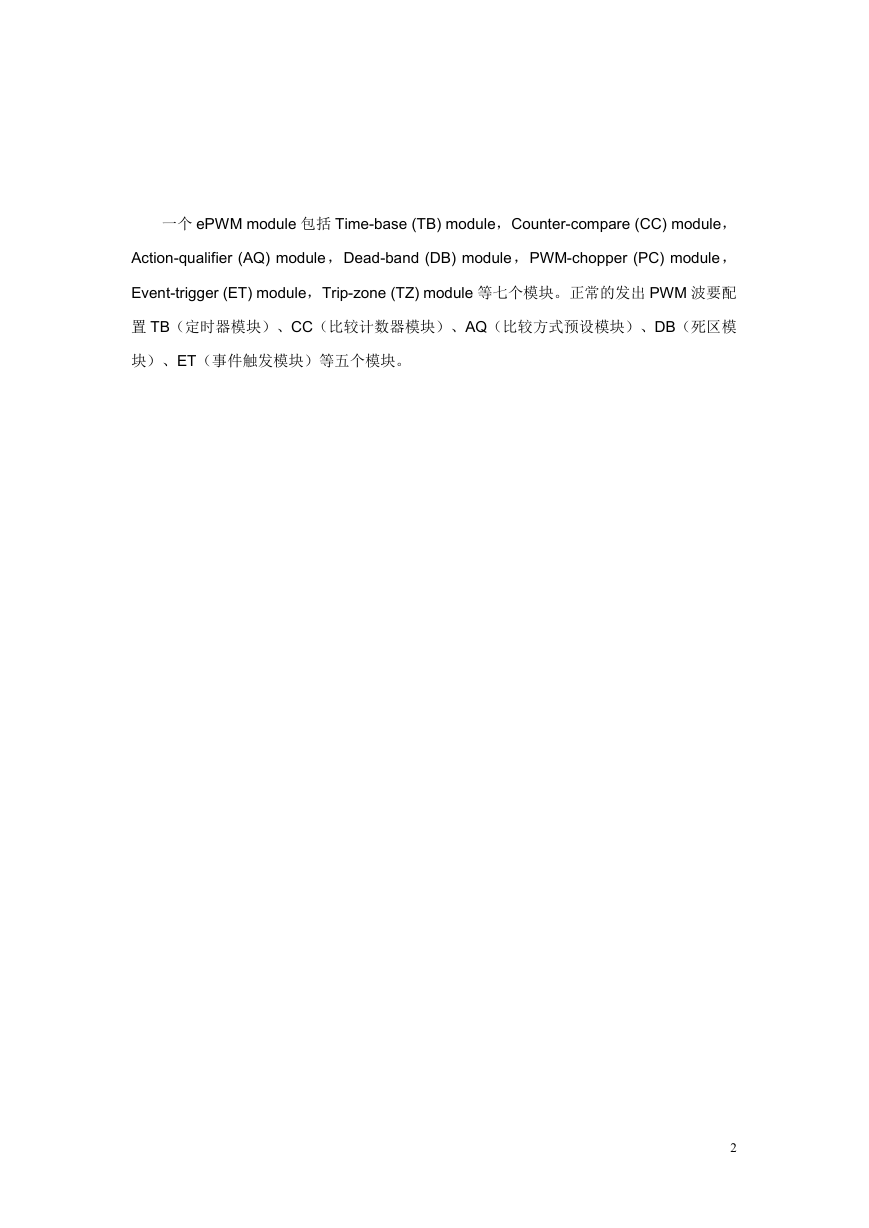

Time-base (TB) module

Time-base (TB) module 为定时器模块,有

TBCTL(控制寄存器)配置定时器的时钟、计数模式、同步模式

TBSTS(状态寄存器)

TBPHSHR(高速 PWM 用)

TBPHS(相位寄存器)计数器的起始计数位置,例如寄存器为 0x0100 则计数器从

0x0100 开始计数

TBCTR(计数器)

TBPRD(周期寄存器)设置计数器的计数周期。只有 TBPRD(周期寄存器)有影子寄

存器。

本程序的设置为 count-up-and-down mode 计数模式,相位为零,ePWM2 、ePWM3、

ePWM4、ePWM5、ePWM6,通过 ePWM1 的计数器到零时进行同步,计数周期为 0.5ms。

3

�

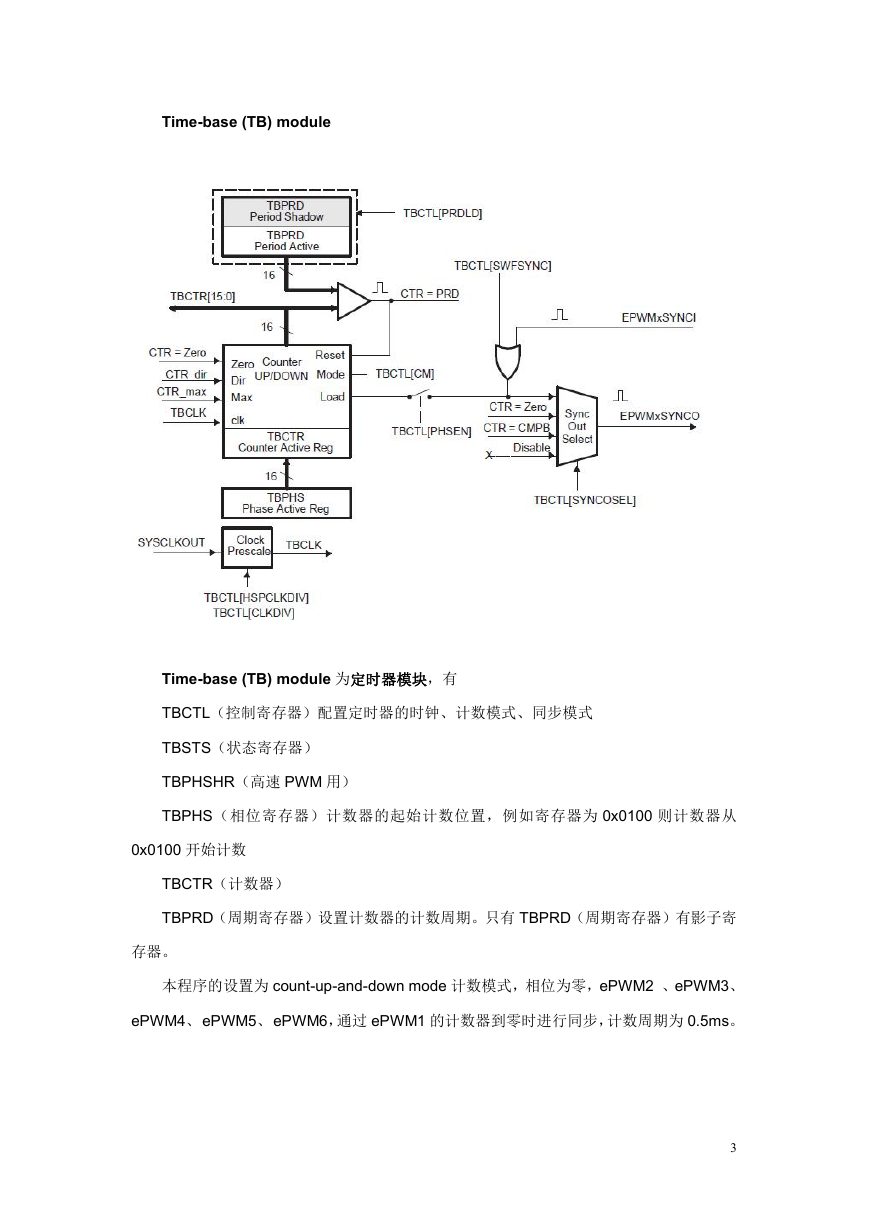

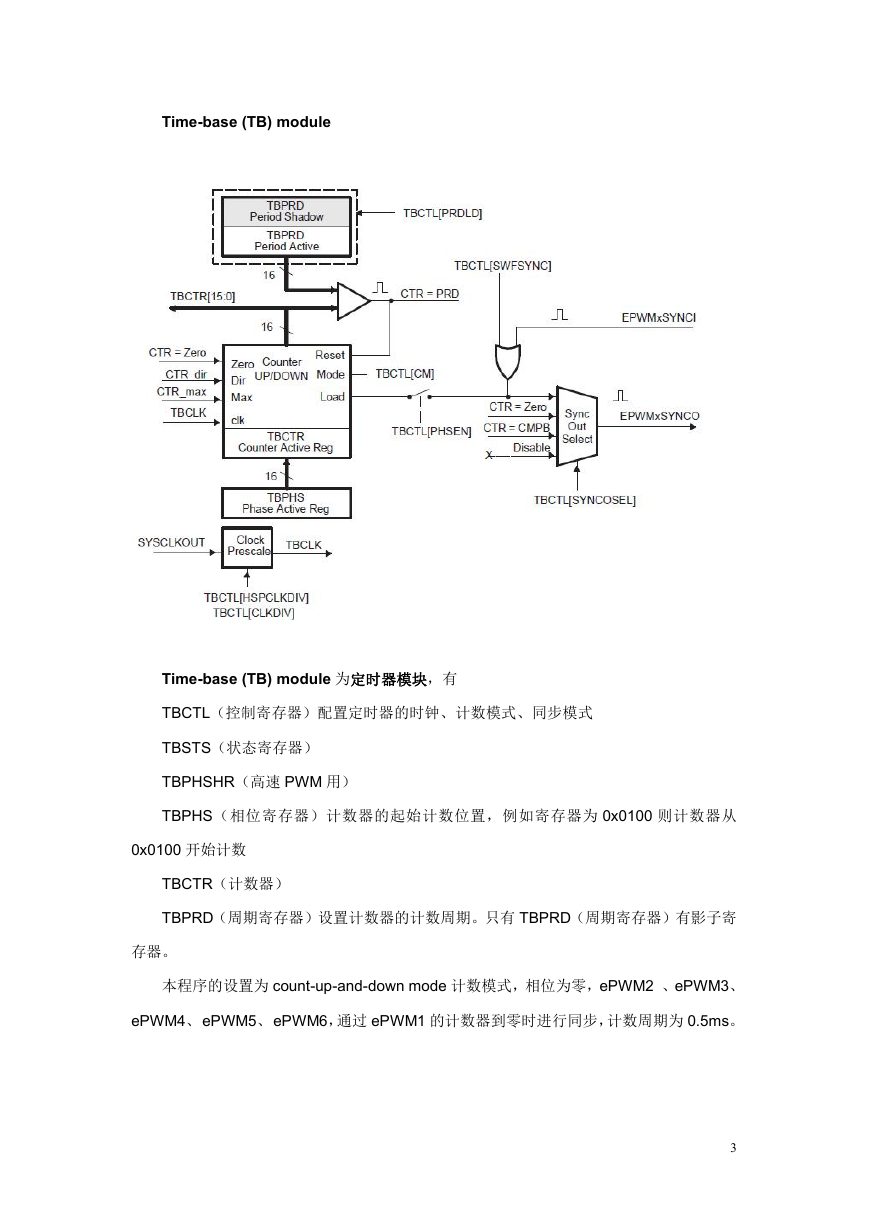

Counter-compare (CC) module

Counter-compare (CC) module 为比较器模块有

CMPCTL (比较控制寄存器)设置 CMPA、CMPB 的重载模式

CMPAHR(高速 PWM 用),

CMPA(比较值寄存器 A)设置 EPWMxA 的比较值,有影子寄存器。

CMPB(比较值寄存器 B)设置 EPWMxB 的比较值,有影子寄存器。

本程序只应用了 CMPA,设置计数器到零时重载 CMPA。

4

�

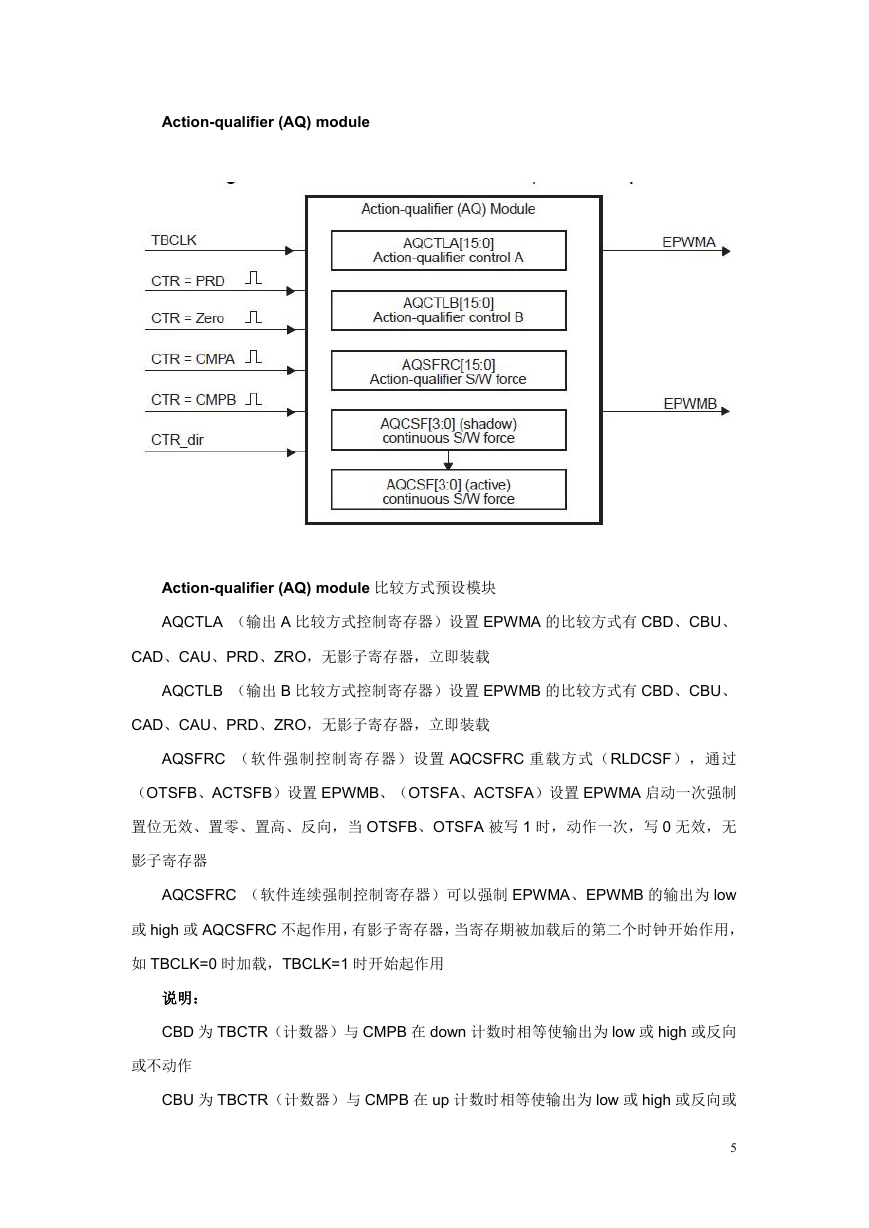

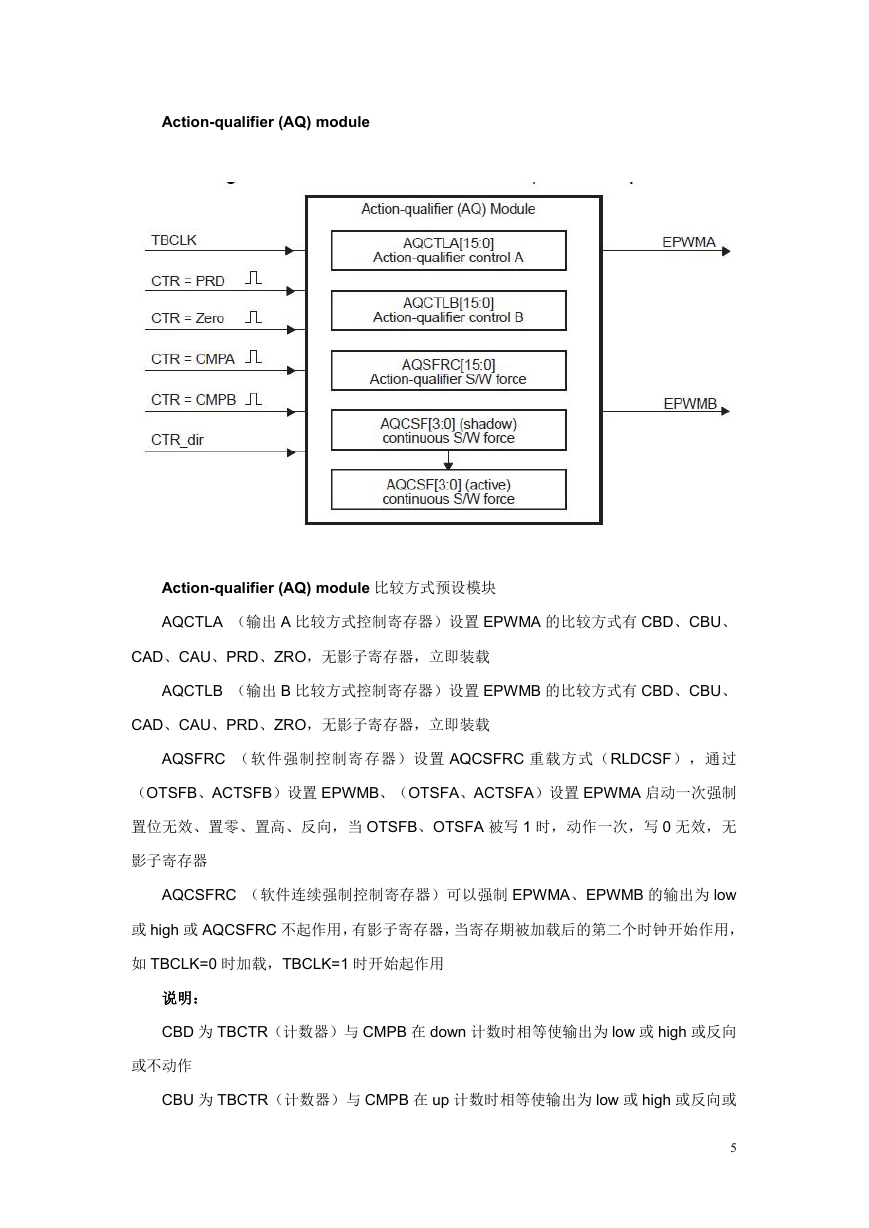

Action-qualifier (AQ) module

Action-qualifier (AQ) module 比较方式预设模块

AQCTLA (输出 A 比较方式控制寄存器)设置 EPWMA 的比较方式有 CBD、CBU、

CAD、CAU、PRD、ZRO,无影子寄存器,立即装载

AQCTLB (输出 B 比较方式控制寄存器)设置 EPWMB 的比较方式有 CBD、CBU、

CAD、CAU、PRD、ZRO,无影子寄存器,立即装载

AQSFRC (软件强制控制寄存器)设置 AQCSFRC 重载方式(RLDCSF),通过

(OTSFB、ACTSFB)设置 EPWMB、(OTSFA、ACTSFA)设置 EPWMA 启动一次强制

置位无效、置零、置高、反向,当 OTSFB、OTSFA 被写 1 时,动作一次,写 0 无效,无

影子寄存器

AQCSFRC (软件连续强制控制寄存器)可以强制 EPWMA、EPWMB 的输出为 low

或 high 或 AQCSFRC 不起作用,有影子寄存器,当寄存期被加载后的第二个时钟开始作用,

如 TBCLK=0 时加载,TBCLK=1 时开始起作用

说明:

CBD 为 TBCTR(计数器)与 CMPB 在 down 计数时相等使输出为 low 或 high 或反向

或不动作

CBU 为 TBCTR(计数器)与 CMPB 在 up 计数时相等使输出为 low 或 high 或反向或

5

�

不动作

CAD 为 TBCTR(计数器)与 CMPA 在 down 计数时相等使输出为 low 或 high 或反向

或不动作

CAU 为 TBCTR(计数器)与 CMPA 在 up 计数时相等使输出为 low 或 high 或反向或

不动作

PRD 为 TBCTR(计数器)与 TBPRD(周期寄存器)相等时使输出为 low 或 high 或反

向或不动作

ZRO 为 TBCTR(计数器)计到零时使输出为 low 或 high 或反向或不动作

注意:以上均是相等时起作用,其它时间不管,只有 AQCSFRC(软件连续强制控制

寄存器)持续起作用

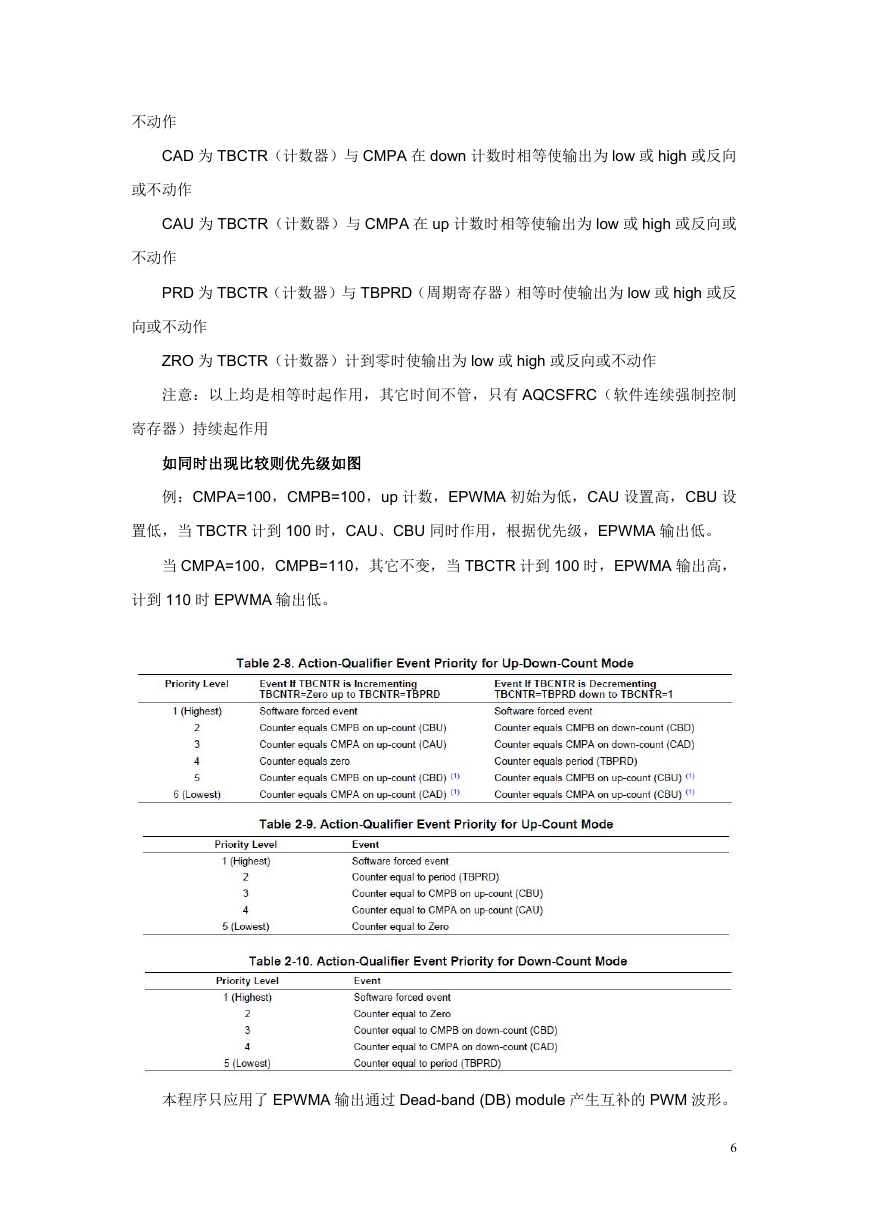

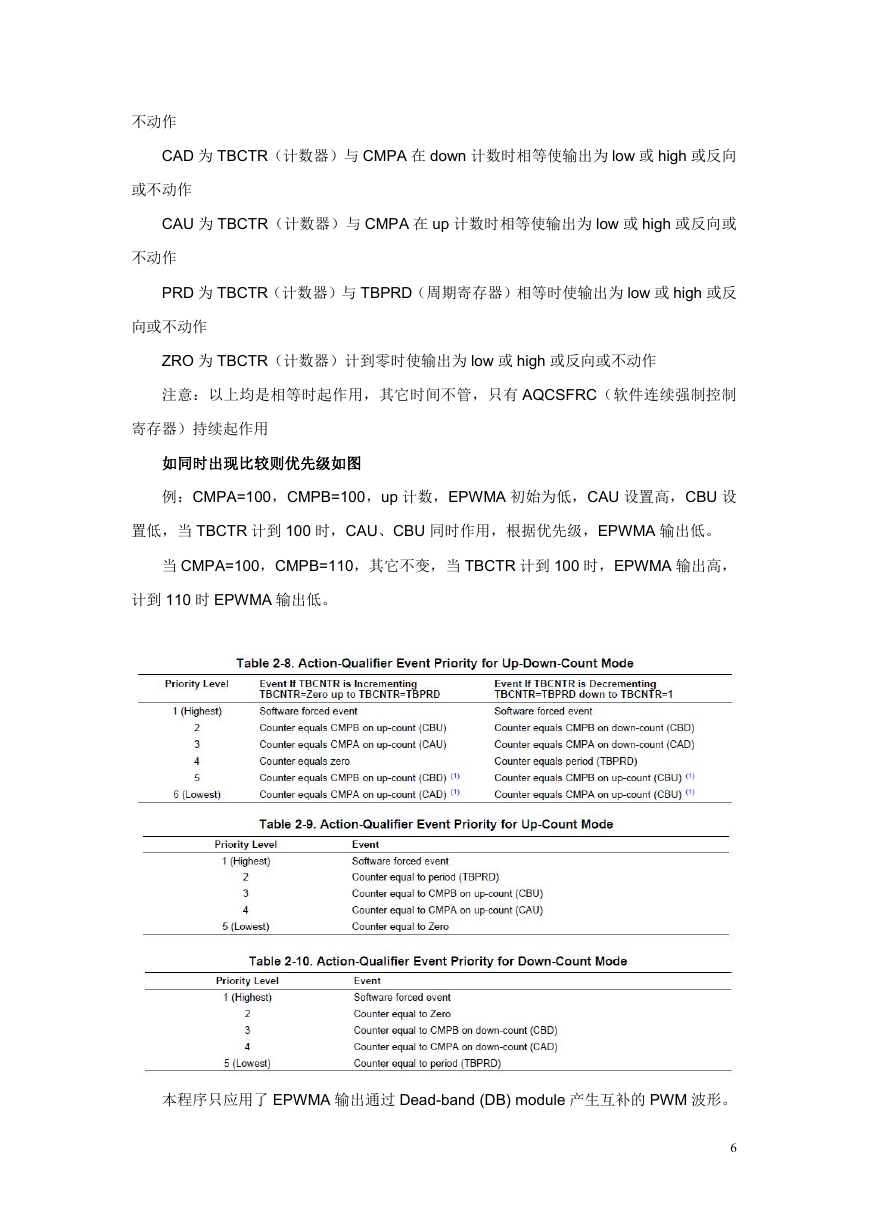

如同时出现比较则优先级如图

例:CMPA=100,CMPB=100,up 计数,EPWMA 初始为低,CAU 设置高,CBU 设

置低,当 TBCTR 计到 100 时,CAU、CBU 同时作用,根据优先级,EPWMA 输出低。

当 CMPA=100,CMPB=110,其它不变,当 TBCTR 计到 100 时,EPWMA 输出高,

计到 110 时 EPWMA 输出低。

本程序只应用了 EPWMA 输出通过 Dead-band (DB) module 产生互补的 PWM 波形。

6

�

Action-qualifier (AQ) module 比较方式预设模块配置如下:AQCTLA (输出 A 比较方式控

制寄存器)的 CAU 置高,CAD 置低,其它无效。在初始化中配置。

AQCSFRC (软件连续强制控制寄存器)通过 AQSFRC(软件强制控制寄存器)的

RLDCSF 配置为 TBCTR(计数器)计到零时装载,根据需要每次中断配置 CSFA 置高、置

低或软件连续强制无效。其优先级最高,强制时 CAU 置高,CAD 置低不起作用,无效时

CAU 置高,CAD 置低起作用。

AQSFRC(软件强制控制寄存器)的 ACTSFA 配置为置低,当本周期软件连续强制无

效时,向 OTSFA 写 1,保证有效高周期的起始是低状态,防止上一周期结束时为高。

7

�

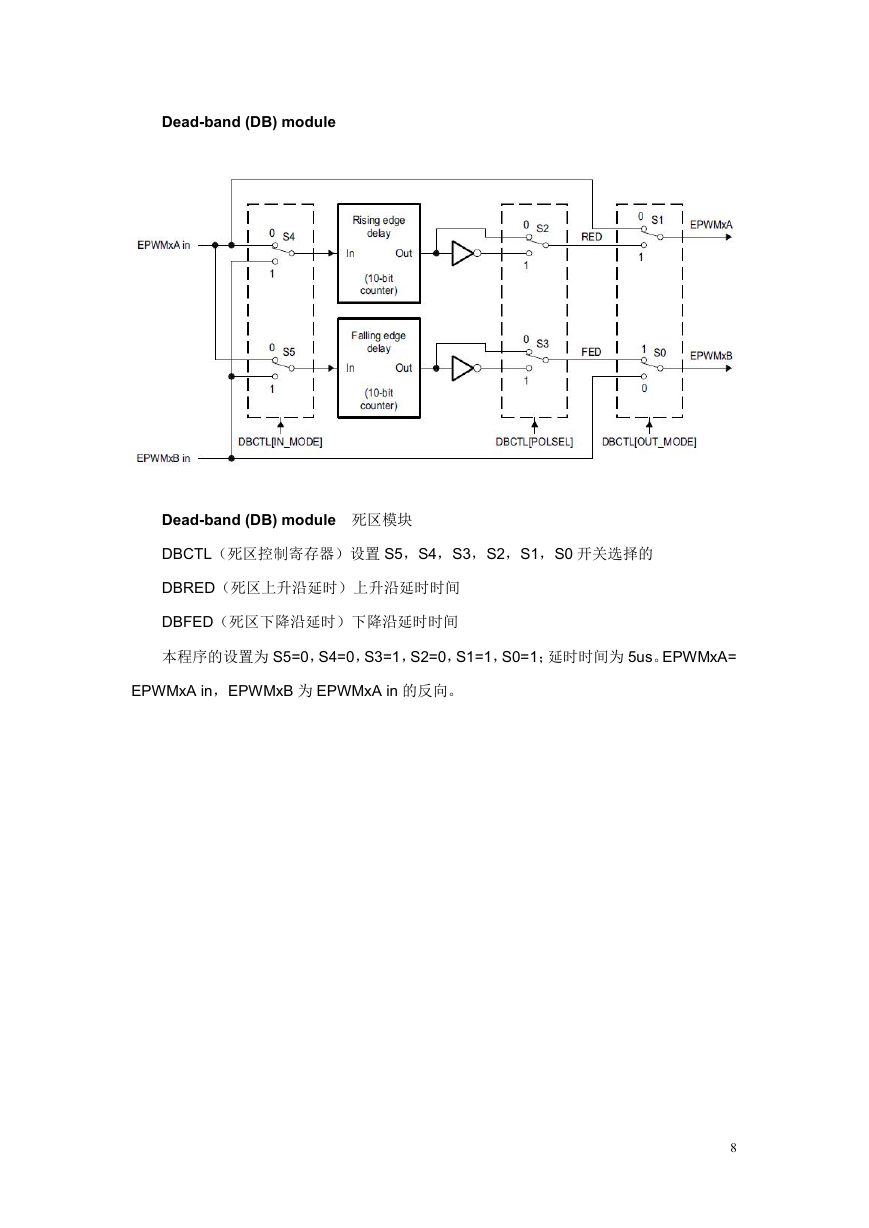

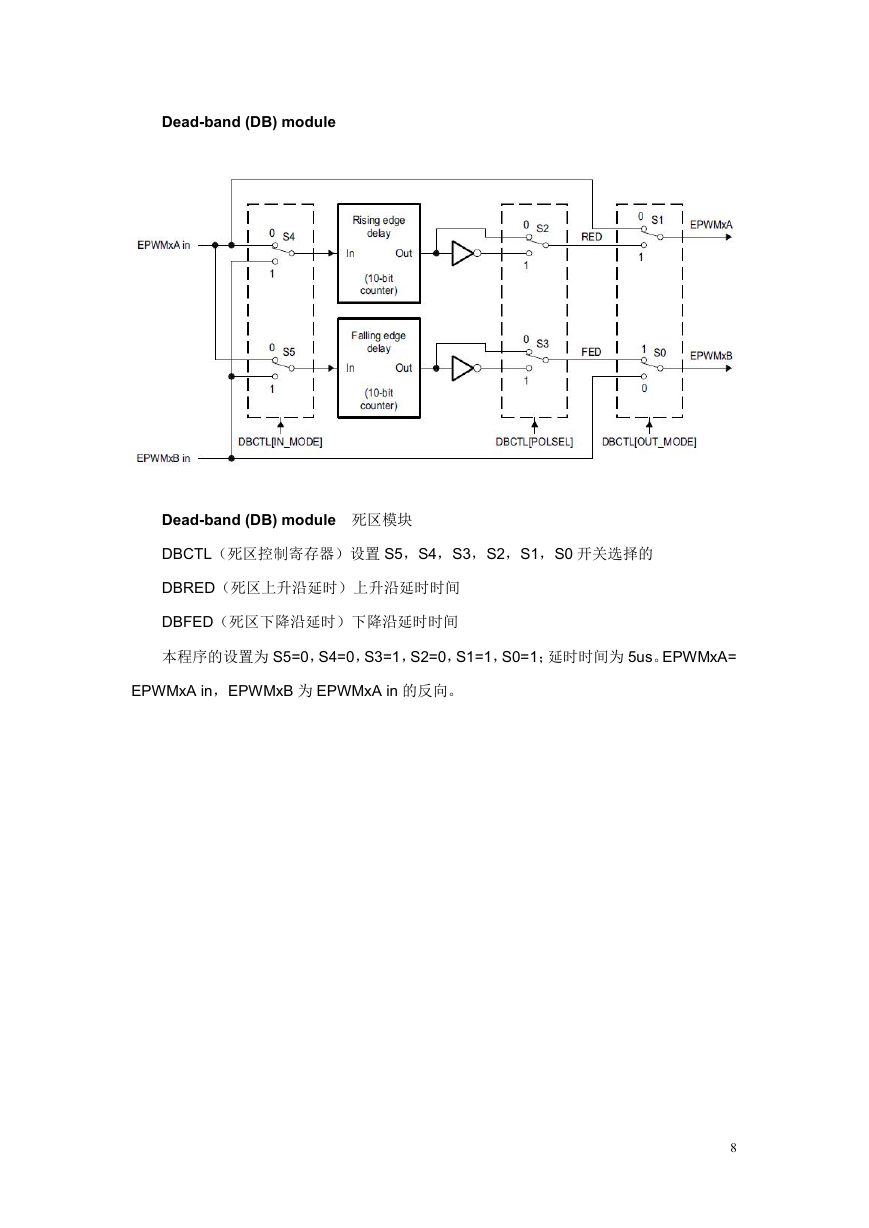

Dead-band (DB) module

Dead-band (DB) module 死区模块

DBCTL(死区控制寄存器)设置 S5,S4,S3,S2,S1,S0 开关选择的

DBRED(死区上升沿延时)上升沿延时时间

DBFED(死区下降沿延时)下降沿延时时间

本程序的设置为 S5=0,S4=0,S3=1,S2=0,S1=1,S0=1;延时时间为 5us。EPWMxA=

EPWMxA in,EPWMxB 为 EPWMxA in 的反向。

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc