verilog HDL 设计练习进阶(一)

时间:2006-08-11 来源: 作者: 点击:2252 字体大小:【大 中 小】

练习一.简单的组合逻辑设计

目的: 掌握基本组合逻辑电路的实现方法。

这是一个可综合的数据比较器,很容易看出它的功能是比较数据 a 与数据 b,如果两个数据相同,则给出结果 1,否则给出

结果 0。在 Verilog HDL 中,描述组合逻辑时常使用 assign 结构。注意 equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时

常使用的格式。

模块源代码:

//--------------- compare.v -----------------

module compare(equal,a,b);

input a,b;

output equal;

assign equal=(a==b)?1:0; //a 等于 b 时,equal 输出为 1;a 不等于 b 时,

//equal 输出为 0。

endmodule

测试模块用于检测模块设计得正确与否,它给出模块的输入信号,观察模块的内部信号和输出信号,如果发现结果与预期的

有所偏差,则要对设计模块进行修改。

测试模块源代码:

`timescale 1ns/1ns //定义时间单位。

`include "./compare.v" //包含模块文件。在有的仿真调试环境中并不需要此语句。

//而需要从调试环境的菜单中键入有关模块文件的路径和名称

module comparetest;

reg a,b;

wire equal;

initial //initial 常用于仿真时信号的给出。

begin a=0;

�

b=0;

#100 a=0;

b=1;

#100 a=1;

b=1;

#100 a=1;

b=0;

#100 $stop; //系统任务,暂停仿真以便观察仿真波形。

end

compare compare1(.equal(equal),.a(a),.b(b)); //调用模块。

endmodule

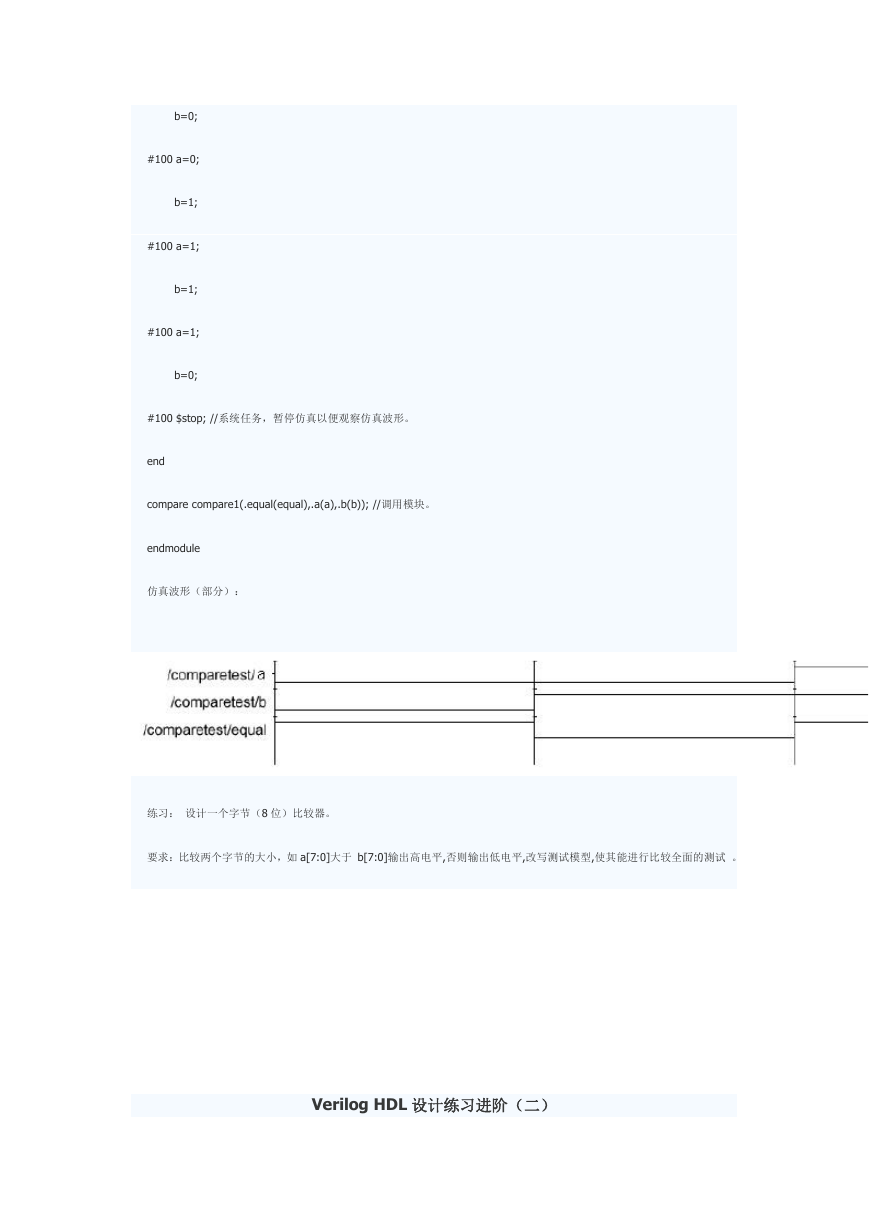

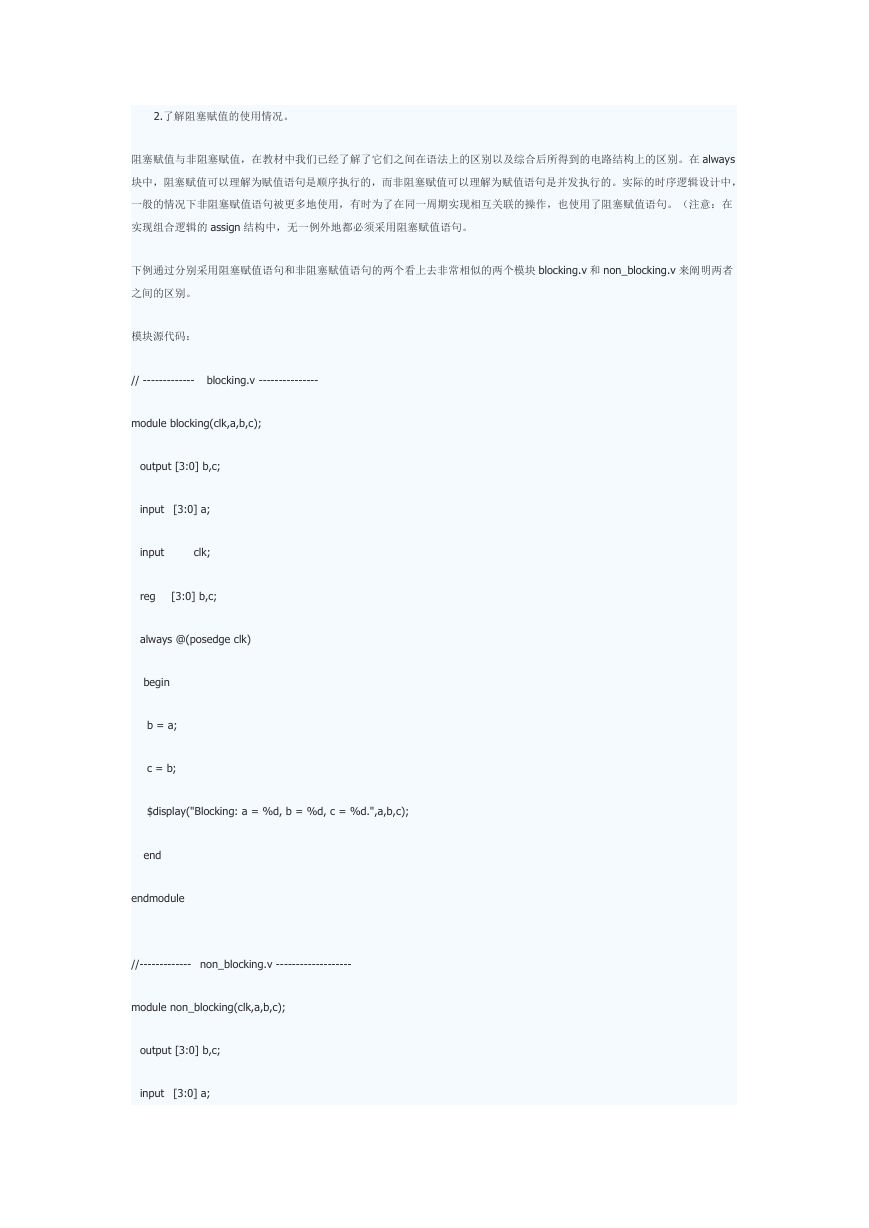

仿真波形(部分):

练习: 设计一个字节(8 位)比较器。

要求:比较两个字节的大小,如 a[7:0]大于 b[7:0]输出高电平,否则输出低电平,改写测试模型,使其能进行比较全面的测试 。

Verilog HDL 设计练习进阶(二)

�

时间:2006-08-11 来源: 作者: 点击:1755 字体大小:【大 中 小】

目的:掌握基本时序逻辑电路的实现。

练习二. 简单时序逻辑电路的设计

在 Verilog HDL 中,相对于组合逻辑电路,时序逻辑电路也有规定的表述方式。在可综合的 Verilog HDL 模型,我们通常使用

always 块和 @(posedge clk)或 @(negedge clk)的结构来表述时序逻辑。下面是一个 1/2 分频器的可综合模型。

// half_clk.v:

module half_clk(reset,clk_in,clk_out);

input clk_in,reset;

output clk_out;

reg clk_out;

always @(posedge clk_in)

begin

if(!reset) clk_out=0;

else

clk_out=~clk_out;

end

endmodule

在 always 块中,被赋值的信号都必须定义为 reg 型,这是由时序逻辑电路的特点所决定的。对于 reg 型数据,如果未对它进行

赋值,仿真工具会认为它是不定态。为了能正确地观察到仿真结果,在可综合风格的模块中我们通常定义一个复位信号 reset,

当 reset 为低电平时,对电路中的寄存器进行复位。

测试模块的源代码:

//------------------- clk_Top.v -----------------------------

`timescale 1ns/100ps

`define clk_cycle 50

module clk_Top.v

reg clk,reset;

wire clk_out;

�

always #`clk_cycle clk = ~clk;

initial

begin

clk = 0;

reset = 1;

#100 reset = 0;

#100 reset = 1;

#10000 $stop;

end

half_clk half_clk(.reset(reset),.clk_in(clk),.clk_out(clk_out));

endmodule

仿真波形:

练习:依然作 clk_in 的二分频 clk_out,要求输出与上例的输出正好反相。编写测试模块,给出仿真波形

Verilog HDL 设计练习进阶(三)

时间:2006-08-11 来源: 作者: 点击:1440 字体大小:【大 中 小】

�

目的:掌握条件语句在 Verilog HDL 中的使用。

练习三. 利用条件语句实现较复杂的时序逻辑电路

与常用的高级程序语言一样,为了描述较为复杂的时序关系,Verilog HDL 提供了条件语句供分支判断时使用。在可综合风格的

Verilog HDL 模型中常用的条件语句有 if…else 和 case…endcase 两种结构,用法和 C 程序语言中类似。两者相较,if…else 用于

不很复杂的分支关系,实际编写可综合风格的模块、特别是用状态机构成的模块时,更常用的是 case…endcase 风格的代码。这

一节我们给的是有关 if…else 的范例,有关 case…endcase 结构的代码已后会经常用到。

下面给出的范例也是一个可综合风格的分频器,是将 10M 的时钟分频为 500K 的时钟。基本原理与 1/2 分频器是一样的,但是

需要定义一个计数器,以便准确获得 1/20 分频

模块源代码:

// --------------- fdivision.v -----------------------------

module fdivision(RESET,F10M,F500K);

input F10M,RESET;

output F500K;

reg F500K;

reg [7:0]j;

always @(posedge F10M)

if(!RESET)

//低电平复位。

begin

F500K <= 0;

j <= 0;

end

else

begin

if(j==19)

//对计数器进行判断,以确定 F500K 信号是否反转。

begin

j <= 0;

�

F500K <= ~F500K;

end

else

j <= j+1;

end

endmodule

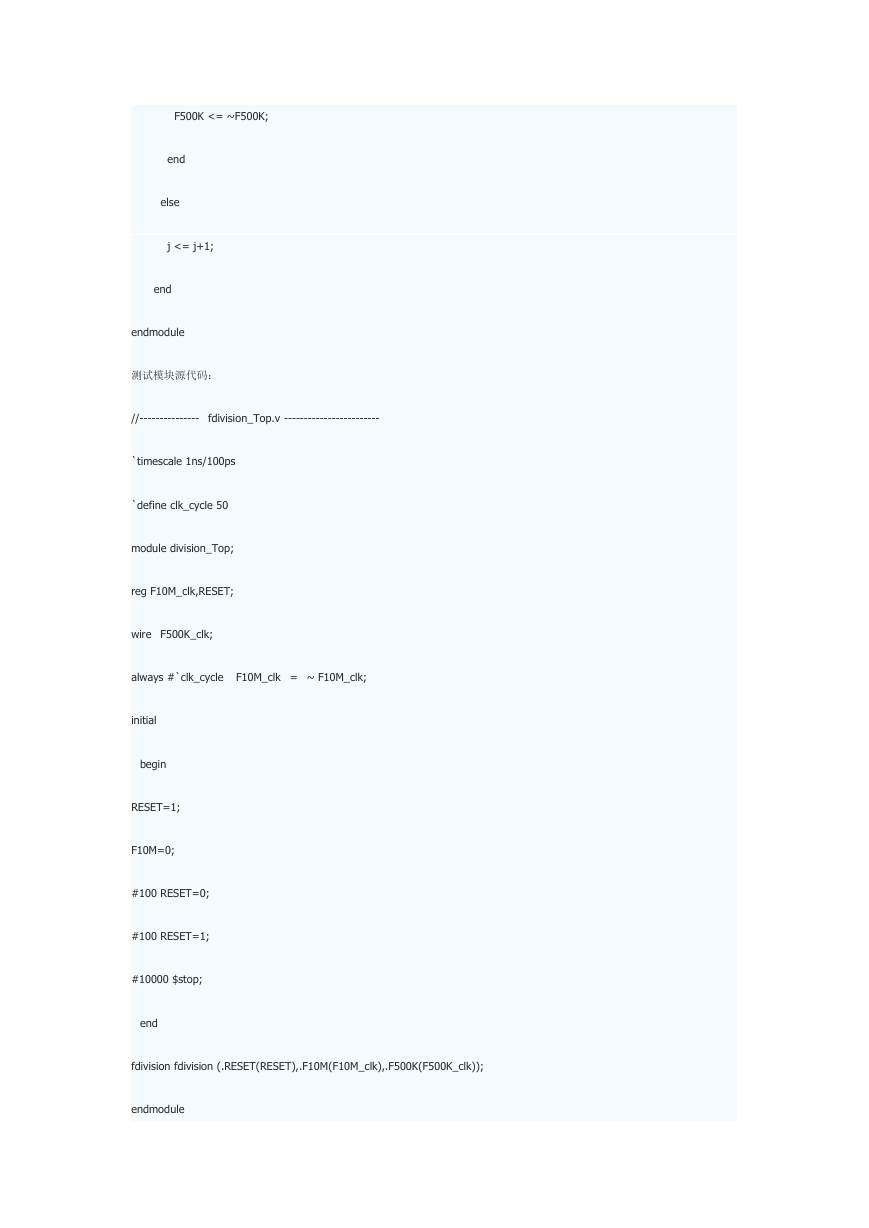

测试模块源代码:

//---------------

fdivision_Top.v ------------------------

`timescale 1ns/100ps

`define clk_cycle 50

module division_Top;

reg F10M_clk,RESET;

wire F500K_clk;

always #`clk_cycle

F10M_clk = ~ F10M_clk;

initial

begin

RESET=1;

F10M=0;

#100 RESET=0;

#100 RESET=1;

#10000 $stop;

end

fdivision fdivision (.RESET(RESET),.F10M(F10M_clk),.F500K(F500K_clk));

endmodule

�

仿真波形:

练习:利用 10M 的时钟,设计一个单周期形状如下的周期波形。

Verilog HDL 设计练习进阶(四)

时间:2006-08-11 来源: 作者: 点击:1158 字体大小:【大 中 小】

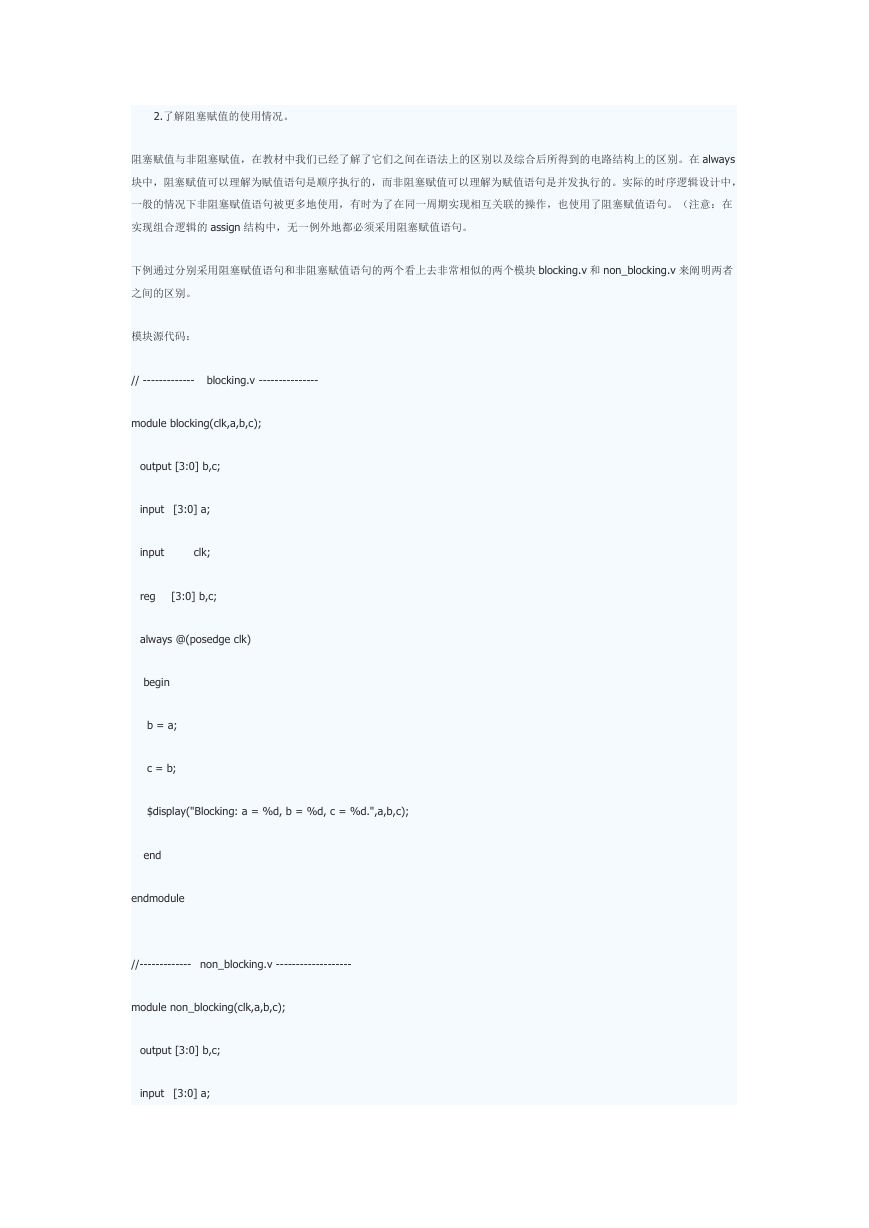

目的:1.明确掌握阻塞赋值与非阻塞赋值的概念和区别;

练习四. 设计时序逻辑时采用阻塞赋值与非阻塞赋值的区别

�

2.了解阻塞赋值的使用情况。

阻塞赋值与非阻塞赋值,在教材中我们已经了解了它们之间在语法上的区别以及综合后所得到的电路结构上的区别。在 always

块中,阻塞赋值可以理解为赋值语句是顺序执行的,而非阻塞赋值可以理解为赋值语句是并发执行的。实际的时序逻辑设计中,

一般的情况下非阻塞赋值语句被更多地使用,有时为了在同一周期实现相互关联的操作,也使用了阻塞赋值语句。(注意:在

实现组合逻辑的 assign 结构中,无一例外地都必须采用阻塞赋值语句。

下例通过分别采用阻塞赋值语句和非阻塞赋值语句的两个看上去非常相似的两个模块 blocking.v 和 non_blocking.v 来阐明两者

之间的区别。

模块源代码:

// -------------

blocking.v ---------------

module blocking(clk,a,b,c);

output [3:0] b,c;

input

[3:0] a;

input

clk;

reg

[3:0] b,c;

always @(posedge clk)

begin

b = a;

c = b;

$display("Blocking: a = %d, b = %d, c = %d.",a,b,c);

end

endmodule

//------------- non_blocking.v -------------------

module non_blocking(clk,a,b,c);

output [3:0] b,c;

input

[3:0] a;

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc