实践教学报告

第 2 学期

2011-2012 学年

项目名称:基于 FPGA 的 4 位数频率计设计

所属课程: 电子产品开发设计与实践教程

班

学

姓

级

号

名

电子 10A2 班

1006013215

于浩

指导老师

张亚

实训时间 2012.3.26~2012.3.31

�

【摘要】:

在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方

案、测量结果都有十分密切的关系,因此频率的测量就显得更为重要。测量

频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量

迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。

电子计数器测频有两种方式:一是直接测频法,即在一定闸门时间内测量被

测信号的脉冲个数;二是间接测频法。如周期测频法。直接测频法适用于高

频信号的频率测量,间接测频法适用于低频信号的频率测量。本文阐述了基

于 VHDL 语言设计了一个简单的数字频率计的过程。

【关键字】: 数字频率计、信号、周期

2

�

【Abstract】:

Be one of the most fundamental parameter in electron technology

medium frequency, parameter measurement scheme, measurement result all

have very close something to do with a lot of electricity and, the

frequency measurement looks like being more important therefore right

away. The method measuring frequency has various, among them the

electronic counter measures frequency having accuracy height, usage

is convenient, measurement is prompt, easy to realize measurement

process automation waits for merit and, counter measures frequency

having two kinds way: sure frequency law first directly ,be to measure

the pulse number the signal is measured within certain sluice gate time;

Two is indirect measure frequency law, if the period measures frequency

law, Measure frequency law directly applying to the high frequency

signal's.

【Keyword】: Figure frequency meter、Signal、period

3

�

目录

绪论: .................................................................................................................................................... 5

第一章 概述.......................................................................................................................................... 6

1.1 设计概述......................................................................................................................................... 6

1.2 设计目的......................................................................................................................................... 6

1.3 设计内容......................................................................................................................................... 7

1.4 设计原理......................................................................................................................................... 7

1.5 设计功能......................................................................................................................................... 8

第二章 数字频率计的设计思路..........................................................................................................9

2.1 基本的设计.....................................................................................................................................9

2.2 计数器的设计...............................................................................................................................10

2.3 模块的划分...................................................................................................................................10

第三章 数字频率计各模块的设计和实现........................................................................................ 11

3.1 100 分频器的设计......................................................................................................................... 11

3.2 7 段译码器的设计.........................................................................................................................13

3.3 总控制器的设计...........................................................................................................................14

3.5 4 选 1 模块设计.............................................................................................................................16

3.6 锁存器的设计...............................................................................................................................17

第四章 总体框图................................................................................................................................19

总结...................................................................................................................................................... 20

附录...................................................................................................................................................... 21

附录 A MAX+PLUSⅡ简介 .................................................................................................................21

附录 B 软件组成............................................................................................................................. 22

附录 C 设计流程............................................................................................................................. 23

参考文献..........................................................................................................................................24

4

�

绪论:

随着电子技术的发展,当前数字系统的设计正朝着速度快、容量大、体

积小、重量轻的方向发展。推动该潮流迅猛发展的引擎就是日趋进步和完善

的设计技术。目前数字频率计的设计可以直接面向用户需求,根据系统的行

为和功能要求,自上至下的逐层完成相应的描述、综合、优化、仿真与验证,

直到生成器件。上述设计过程除了系统行为和功能描述以外,其余所有的设

计过程几乎都可以用计算机来自动地完成,也就是说做到了电子设计自动化

(EDA)。这样做可以大大地缩短系统的设计周期,以适应当今品种多、批量

小的电子市场的需求,提高产品的竞争能力。

电子设计自动化(EDA)的关键技术之一是要求用形式化方法来描述数

字系统的硬件电路,即要用所谓硬件描述语言来描述硬件电路。所以硬件描

述语言及相关的仿真、综合等技术的研究是当今电子设计自动化领域的一个

重要课题。

硬件描述语言的发展至今已有几十年的历史,并已成功地应用到系统的

仿真、验证和设计综合等方面。到本世纪 80 年代后期,已出现了上百种的硬

件描述语言,它们对设计自动化起到了促进和推动作用。但是,它们大多各

自针对特定设计领域,没有统一的标准,从而使一般用户难以使用。广大用

户所期盼的是一种面向设计的多层次、多领域且得到一致认同的标准的硬件

描述语言。80 年代后期由美国国防部开发的 VHDL 语言(VHSIC Hardware

Description Language)恰好满足了上述这样的要求,并在 1987 年 12 月由 IEEE

标准化(定为 IEEE std 1076--1987 标准,1993 年进一步修订,被定为

ANSI/IEEE std 1076--1993 标准)。它的出现为电子设计自动化(EDA)的普

及和推广奠定了坚实的基础。据 1991 年有关统计表明,VHDL 语言业已被广

大设计者所接受。另外,众多的 CAD 厂商也纷纷使自己新开发的电子设计软

件与 VHDL 语言兼容。由此可见,使用 VHDL 语言来设计数字系统是电子设

计技术的大势所趋。

5

�

第一章 概述

1.1 设计概述

所谓频率,就是周期性信号在单位时间(1s)里变化的次数。

本数字频率计的设计思路是:

1.根据频率计的测频原理,可以选择合适的时基信号即闸门时间,对输

入被测信号脉冲进行计数,实现测频的目的。

2.根据数字频率计的基本原理,本文设计方案的基本思想是分为五个模

块来实现其功能,即整个数字频率计系统分为分频模块、控制模块、计数模

块、译码模块和量程自动切换模块等几个单元,并且分别用 VHDL 对其进行编

程,实现了闸门控制信号、计数电路、锁存电路、显示电路等。

3.在进行设计之前,首先搞清楚在什么情况下是测频率,在什么情况下

是测周期,其实就是一个选择合适的时基信号的问题。在这个设计中,要在

频率计提供的时基信号和输入信号之间做出选择,充当时基信号即闸门时间。

当测频率的时候,要以输入信号作为时钟信号,因为输入信号的频率大于频

率计提供的基准频率,在频率计提供的基准信号周期内,计算输入信号的周

期数目,再乘以频率计基准频率,就是输入信号的频率值了。此时的时基信

号为频率计的基准信号。当测周期的时候,要以频率计提供的基准信号作为

时钟信号,因为频率计提供的时基频率大于输入信号的频率,在输入信号周

期内,计算频率计提供的基准信号的周期数目,再乘以基准信号频率,就是

输入信号的周期值了。此时的时基信号为输入信号。

1.2 设计目的

1.学会利用 MAX+PLUSⅡ进行层次化设计;

2.练习混合设计设计输入的方法;

6

�

3.巩固用试验箱验证设计的方法。

1.3 设计内容

分析数字频率计的功能,完成功能模块的划分,分别用 VHDL 语言完成底

层模块的设计和以原理图的方法完成顶层模块的设计,分别对各个模块以及

顶层模块进行仿真分析,最后在硬件开发平台上进行测试。

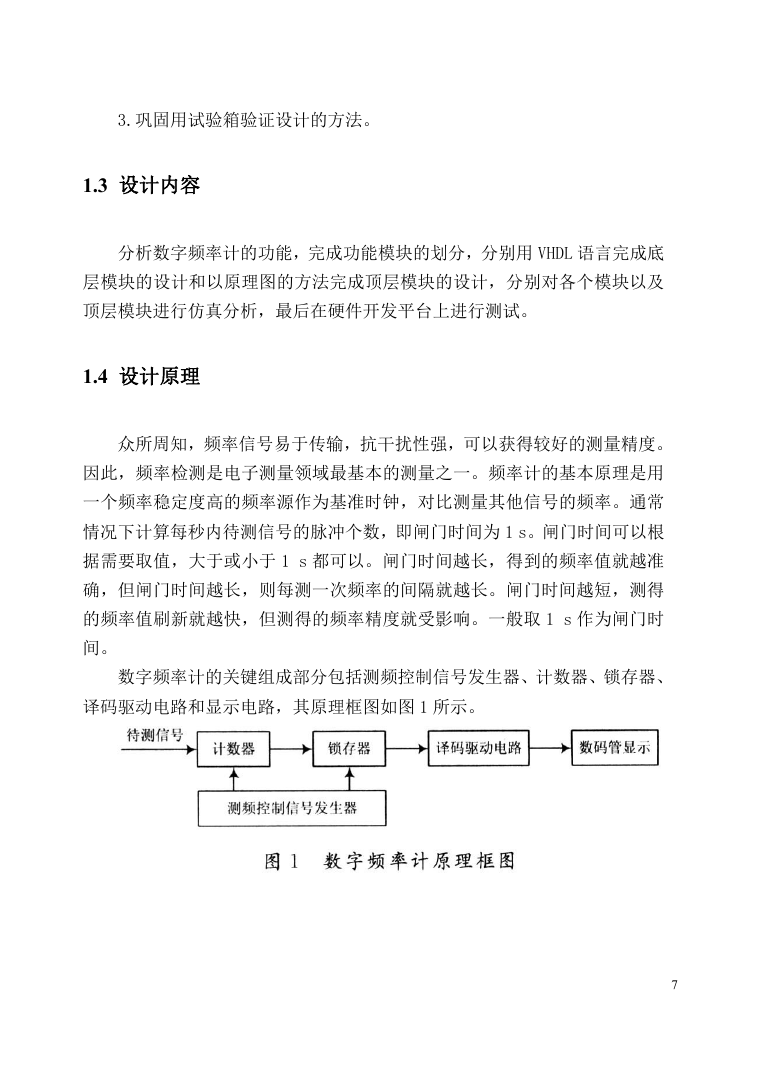

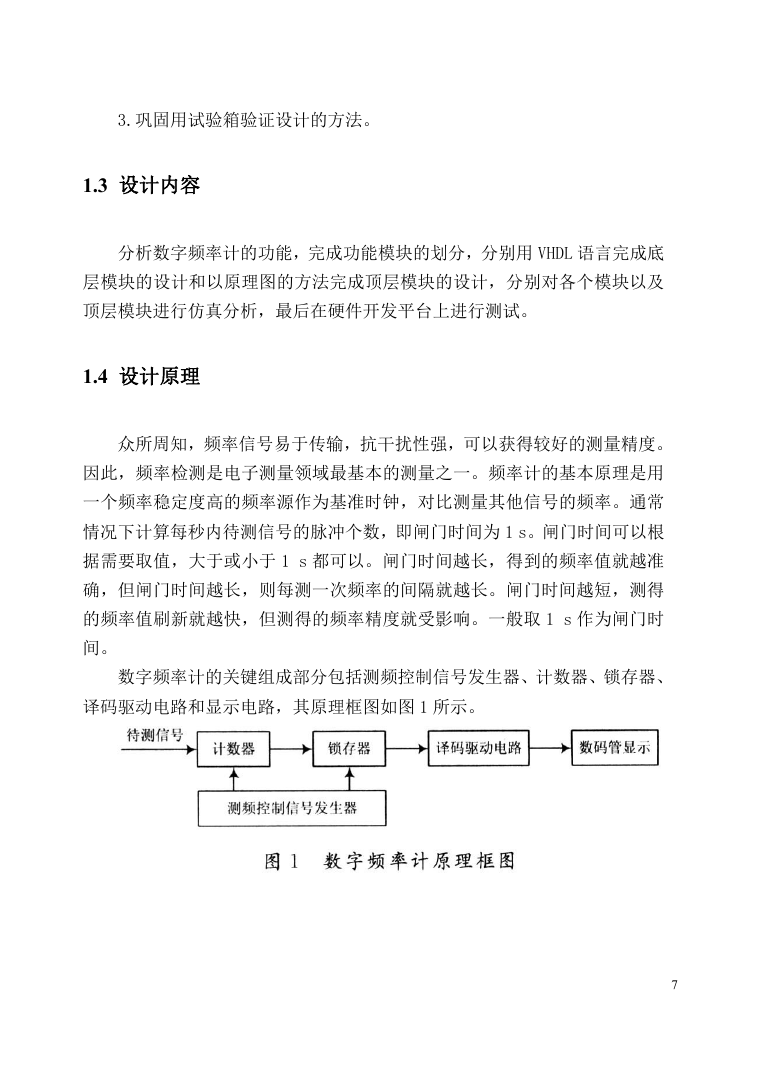

1.4 设计原理

众所周知,频率信号易于传输,抗干扰性强,可以获得较好的测量精度。

因此,频率检测是电子测量领域最基本的测量之一。频率计的基本原理是用

一个频率稳定度高的频率源作为基准时钟,对比测量其他信号的频率。通常

情况下计算每秒内待测信号的脉冲个数,即闸门时间为 1 s。闸门时间可以根

据需要取值,大于或小于 1 s 都可以。闸门时间越长,得到的频率值就越准

确,但闸门时间越长,则每测一次频率的间隔就越长。闸门时间越短,测得

的频率值刷新就越快,但测得的频率精度就受影响。一般取 1 s 作为闸门时

间。

数字频率计的关键组成部分包括测频控制信号发生器、计数器、锁存器、

译码驱动电路和显示电路,其原理框图如图 1 所示。

7

�

1.5 设计功能

3 位数字频率计是用 3 个十进制数字显示的数字式频率计,其频率测量范

围为 1MHz。为了提高测量精度,量程分别为 10kHz、100kHz 和 1MHz 三挡,即

最大读数分别为 9.99kHz,99.9kHz 和 999kHz。要求量程自动换挡。具体功能

如下:

1.当读数大于 999 时,频率计处于超量程状态,下一次测量时,量程自

动增大一挡。

2.当读数小雨 099 时,频率计处于欠量程状态,下一次测量时,量程自

动减少一挡。

3.当超出频率测量范围时,显示器显示溢出。

4.采用记忆显示方法,即测量过程中不显示数据,待测量过程结束以后,

显示测频结果,并将此结果保持到下次测量结束。显示时间不少于 1 秒。

5.小数点位置随量程变化自动移位。

6.增加测周期功能,就是当时钟频率低于 0.99kHz 的时候,显示的数值变成

周期,以毫秒为单位。

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc