16 位 CPU 设计

----基于 VHDL 状态机

学院:计信学院

专业:通信工程

班级:

姓名:

学号:

日期:2010 年 6 月

�

本设计基于 VHDL 状态机理论设计

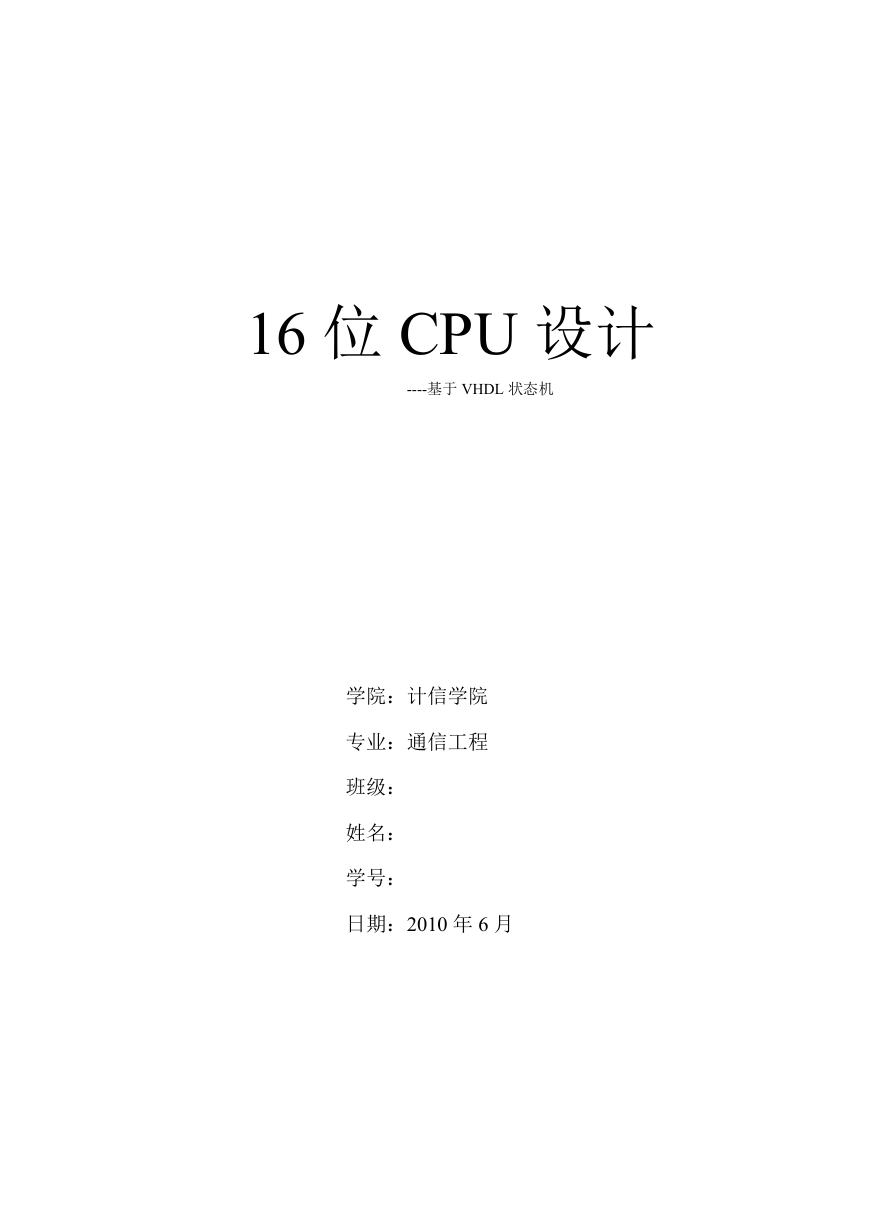

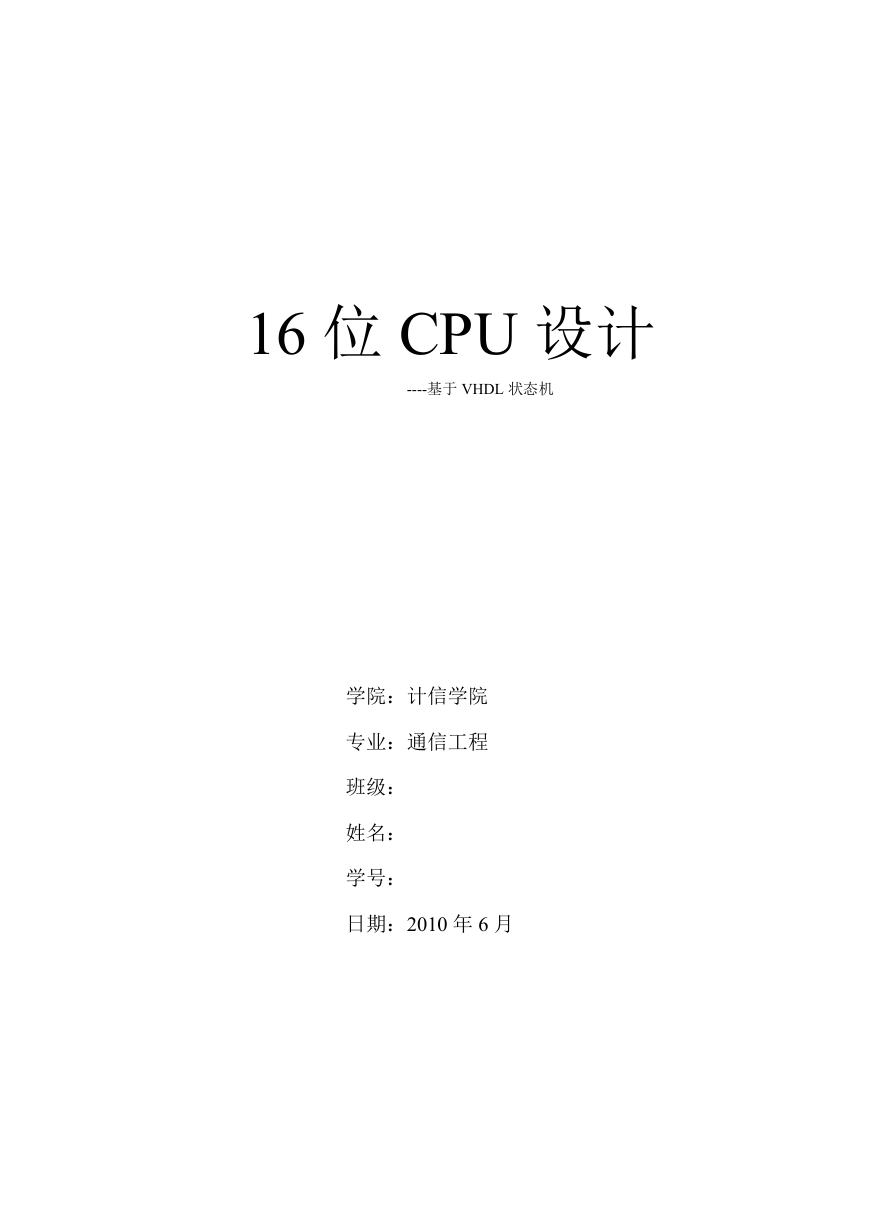

有限状态机 FSM(Finite State Machine)是一种典型的时序电路,其状

态需由若干个触发器的输出来表示。有限状态机电路有两种类型,分别是 Moore

类型和 Mealy 类型。Moore 类型状态机的输出仅由当前状态决定;而 Mealy 类型

状态机的输出由当前状态和输入信号决定。有限状态机的基本逻辑电路框图如图

2-50 所示。

图 2-50 有限状态机的逻辑电路框图

有限状态机 FSM 可以分为以下三部分:

(1) 当前状态电路。当前状态电路为时序电路时,由时钟信号和次态逻辑电

路控制状态的变化。

(2) 次态逻辑电路。次态逻辑电路为组合电路时,次态由输入信号和当前状

态决定。

(3) 输出逻辑电路。对于 Moore 类型状态机,输出仅由当前状态决定;对于

Mealy 类型状态机,输出分别由当前状态和输入信号决定。

有限状态机的状态需要用若干个触发器的输出来表示,每个状态对应一个编

码,状态的编码决定了保持状态所需要的触发器的数量,并且影响到输出所用到

的组合电路的复杂度。对有限状态机的状态编码主要有以下几种编码方式:

(1) 二进制编码(Binary Encoding)。

(2) 格雷码编码(Gray Encoding)。

(3) 独热编码(One-hot Encoding)。

(4) 独冷编码(One-cold Encoding)。

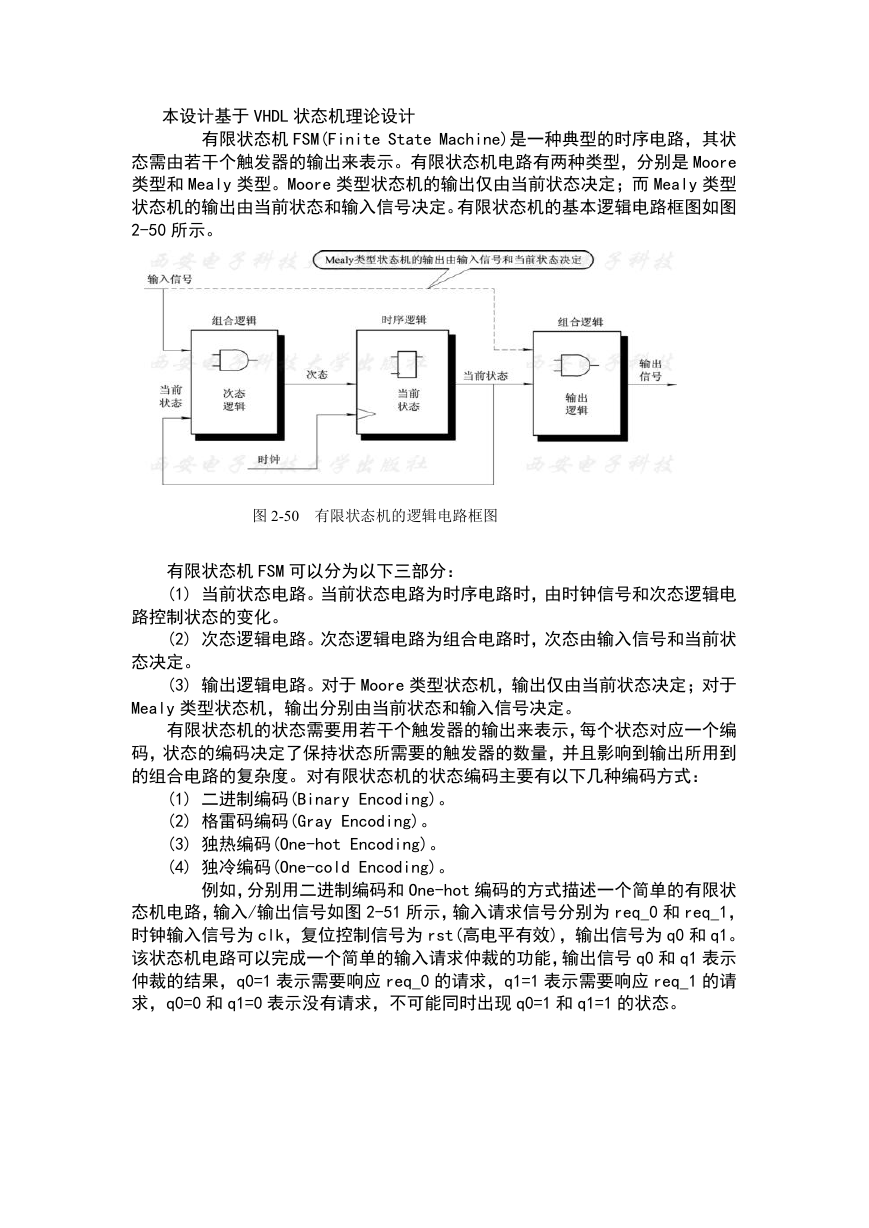

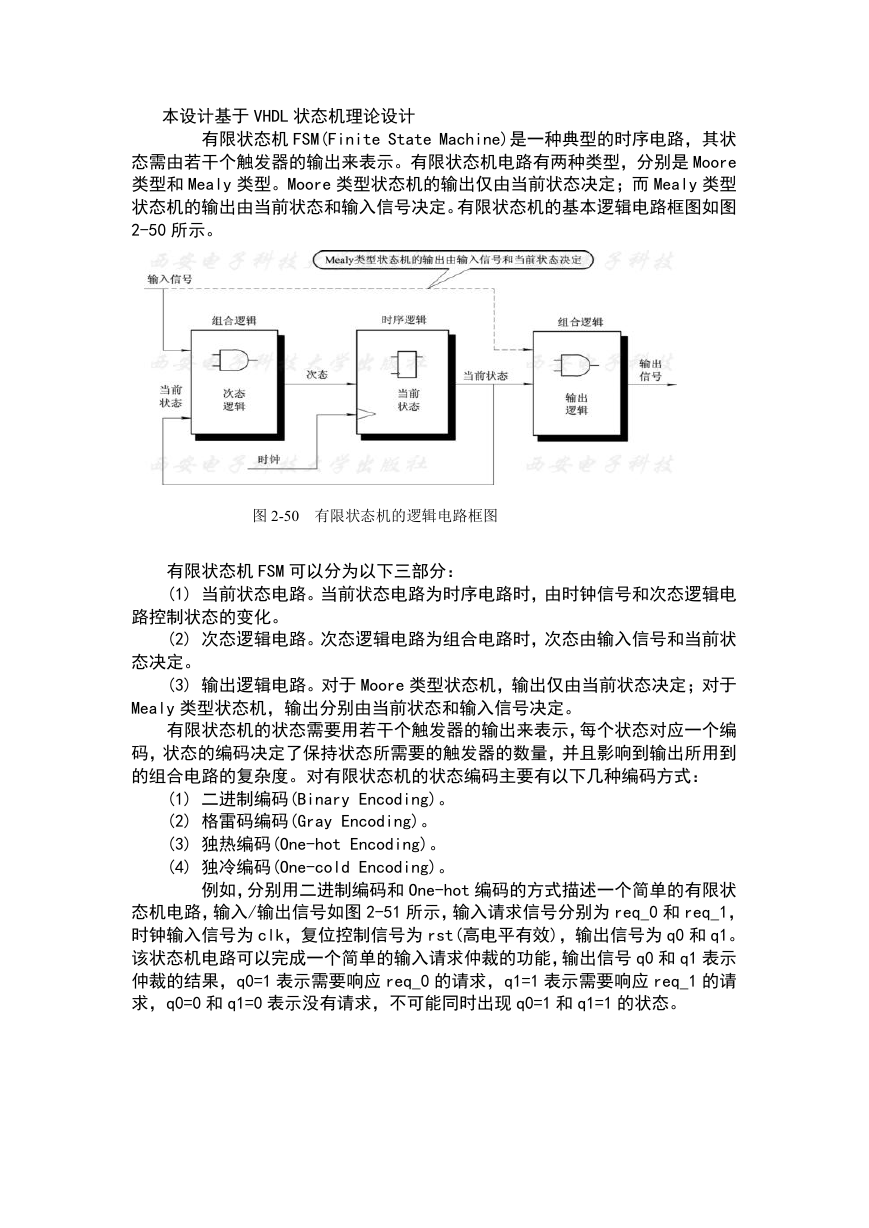

例如,分别用二进制编码和 One-hot 编码的方式描述一个简单的有限状

态机电路,输入/输出信号如图 2-51 所示,输入请求信号分别为 req_0 和 req_1,

时钟输入信号为 clk,复位控制信号为 rst(高电平有效),输出信号为 q0 和 q1。

该状态机电路可以完成一个简单的输入请求仲裁的功能,输出信号 q0 和 q1 表示

仲裁的结果,q0=1 表示需要响应 req_0 的请求,q1=1 表示需要响应 req_1 的请

求,q0=0 和 q1=0 表示没有请求,不可能同时出现 q0=1 和 q1=1 的状态。

�

图 2-51 状态机的输入/输出信号

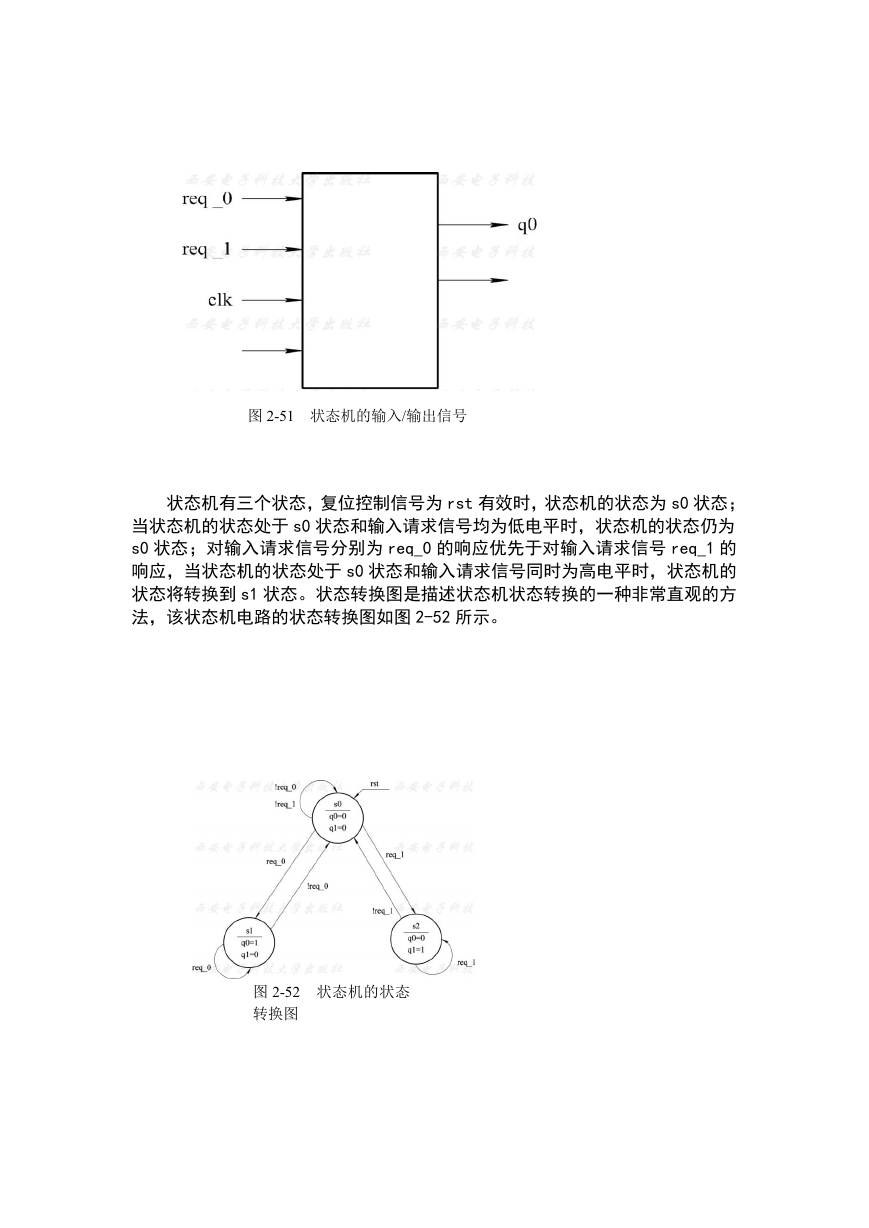

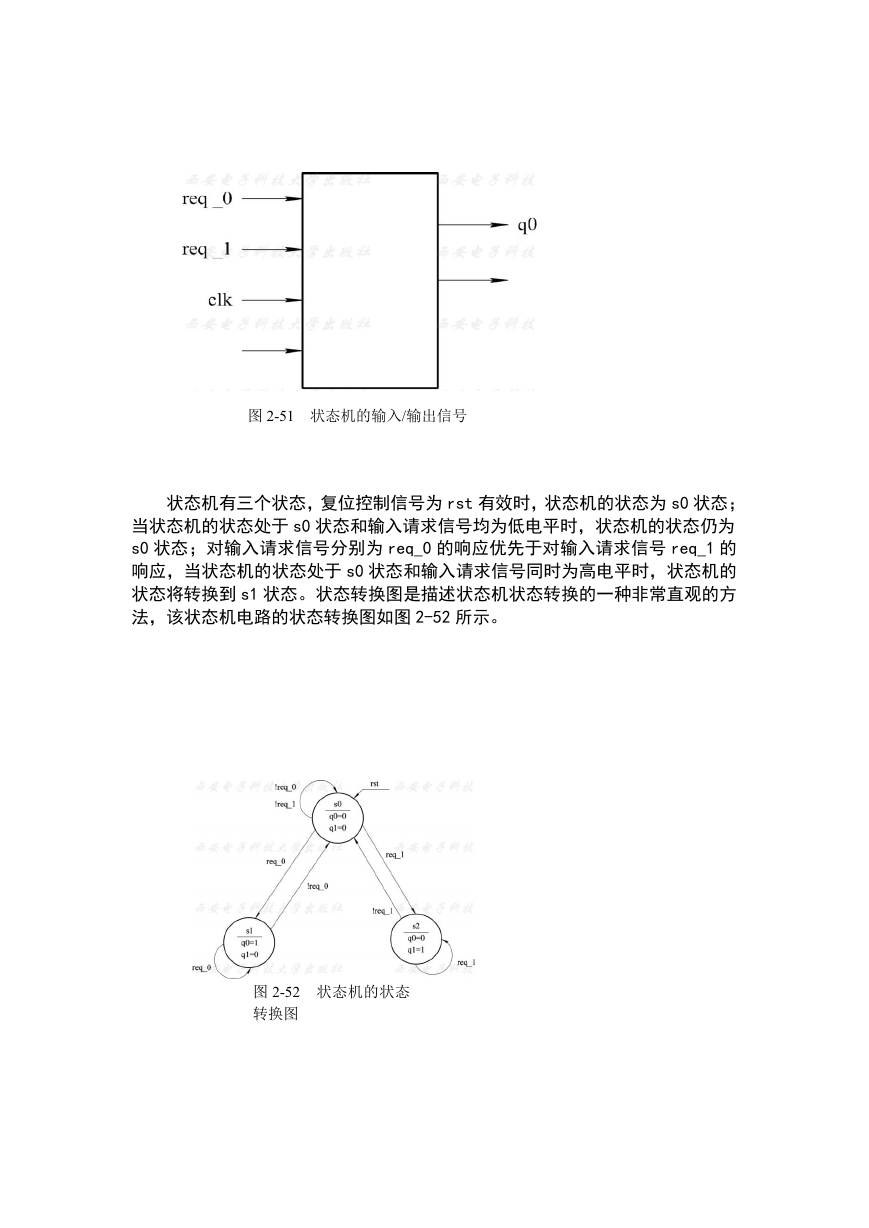

状态机有三个状态,复位控制信号为 rst 有效时,状态机的状态为 s0 状态;

当状态机的状态处于 s0 状态和输入请求信号均为低电平时,状态机的状态仍为

s0 状态;对输入请求信号分别为 req_0 的响应优先于对输入请求信号 req_1 的

响应,当状态机的状态处于 s0 状态和输入请求信号同时为高电平时,状态机的

状态将转换到 s1 状态。状态转换图是描述状态机状态转换的一种非常直观的方

法,该状态机电路的状态转换图如图 2-52 所示。

图 2-52 状态机的状态

转换图

�

设计过程采用层 次 化 设 计

所谓层次化设计,就是采用自顶向下分层设计的方法,将系统设计分成几个

子设计模块,对于每个子设计模块进行设计、调试和仿真。

将已经设计好的模块定义为一个元件并与当前的模块中指定的端口相连接。

如果把当前的设计模块看做一个电路系统,则该模块相当于该电路系统中的一个

元件。

在多层次的设计中,高层次的设计模块可以调用低层次的设计模块,用基本

的电路设计模块构成一个复杂的数字逻辑系统。

本次设计的内容为 16 位模型计算机的设计,单总线,采用微程序控制方式,

有四种寻址方式:直接寻址、寄存器寻址、寄存器间接寻址和变址寻址。

微程序控制方式由微指令译码产生。微程序中一条机器指令往往分成几步执

行,将每一步操作所需的若干为命令以代码编写在一条微指令中,若干条微指令

组成一段微程序,对应一条机器指令。然后根据系统的需要,事先编制各段微程

序,将它存入一个专用寄存器(即控制存储器)中。

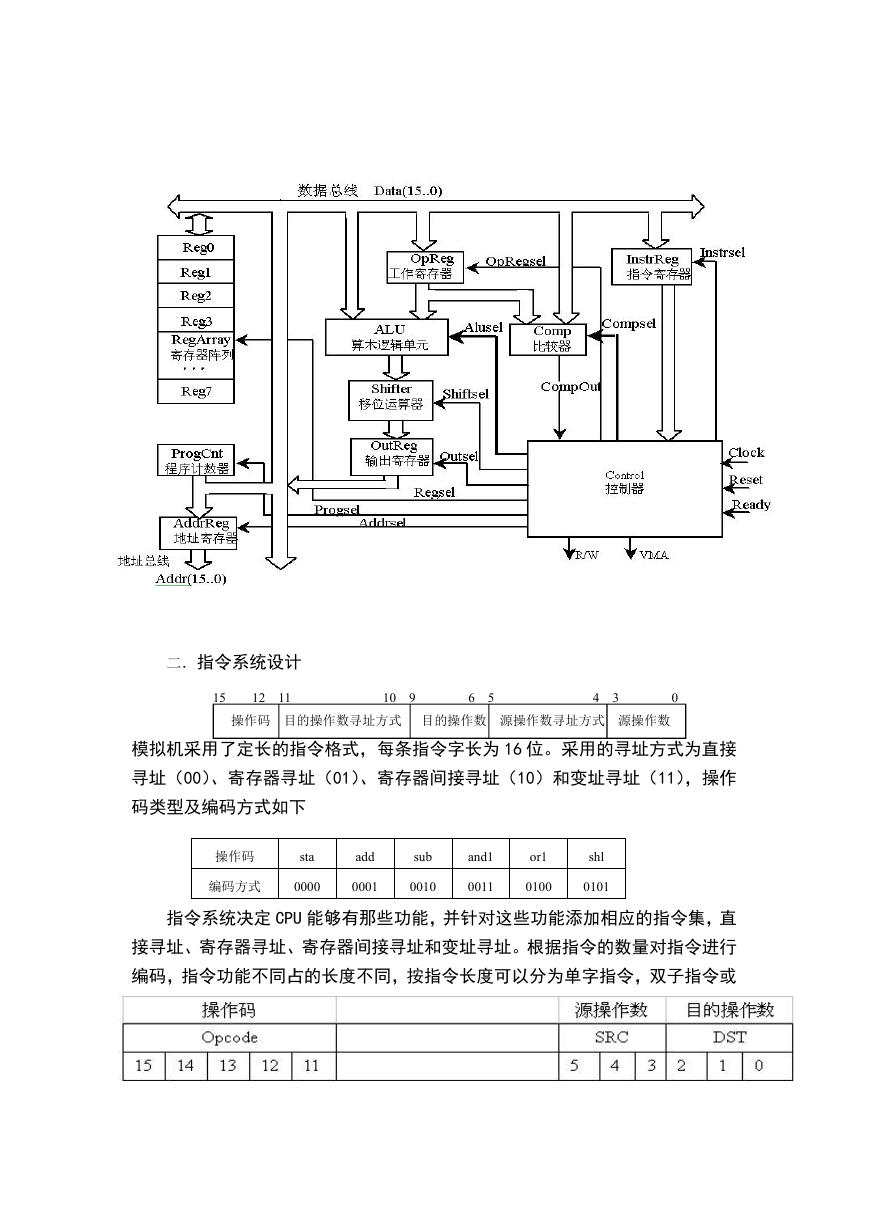

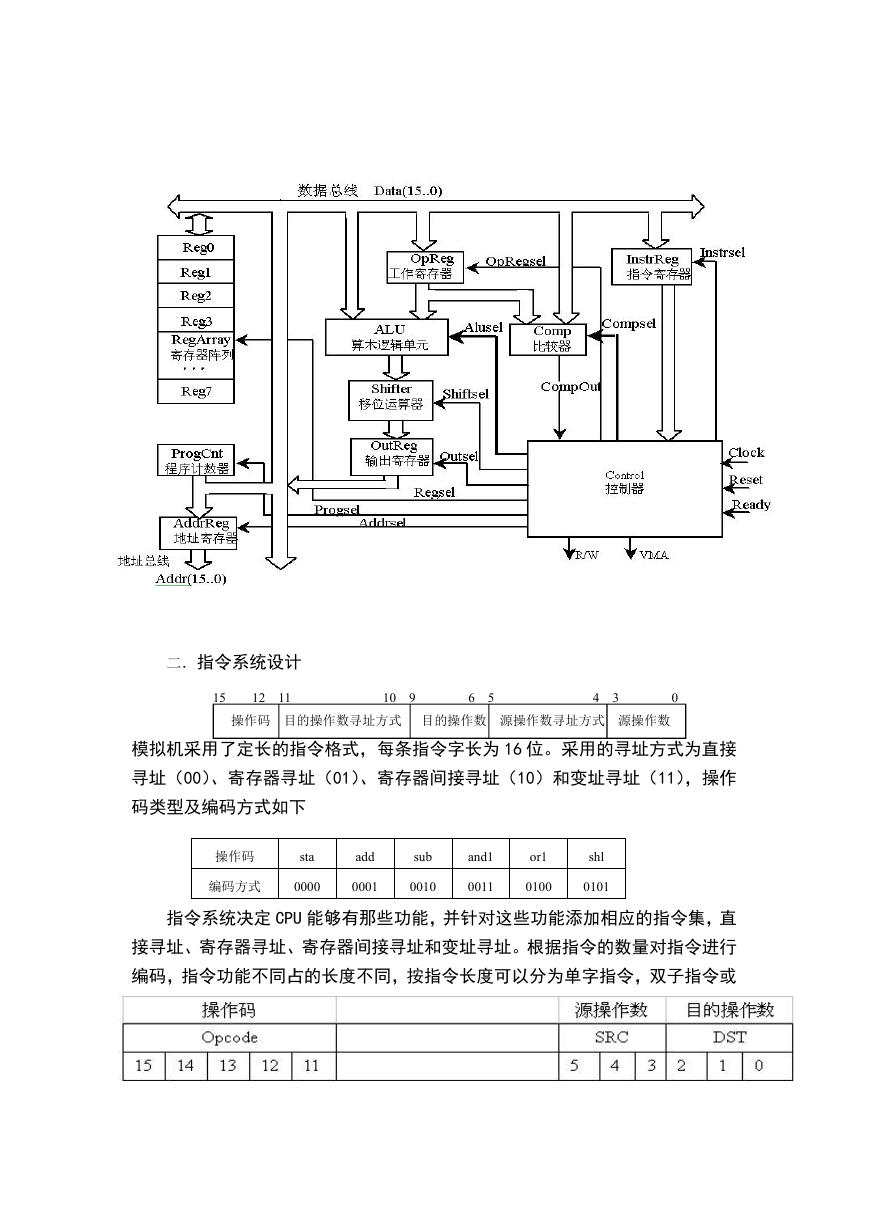

一. 16 位 CPU 的组成结构

CPU 的结构图如图 1-1 所示。这是一个采用单总线系统架构的复杂指令系

统架构 CISC 的 16 位 CPU。处理器包括各种基本模块,它们是 8 个 16 位的寄存

器 Reg0-Reg7,一个运算器 ALU,一个移位寄存器 Shifter,一个程序计数器

ProgCnt,一个指令寄存器 InstrReg,一个比较器 Comp,一个地址寄存器 AddrReg

和一个控制单元 Control。这些模块公用一组 1 位的三态数据总线。

该 CPU 运行时,要从指令存储器中读取指令,因此需要送出指令地址信

号 addr(15:0),读取指令信号,CPU 从双口数据存储器的数据总线 Data(15:0)

上读取数据,也能够将通用寄存器 A 的数据写到数据存储器中,CPU 送出数据地

址信号通过控制。信号控制对数据存储器进行读/写操作。

�

二.指令系统设计

15

12 11

10 9

6 5

4

3

0

操作码 目的操作数寻址方式 目的操作数 源操作数寻址方式 源操作数

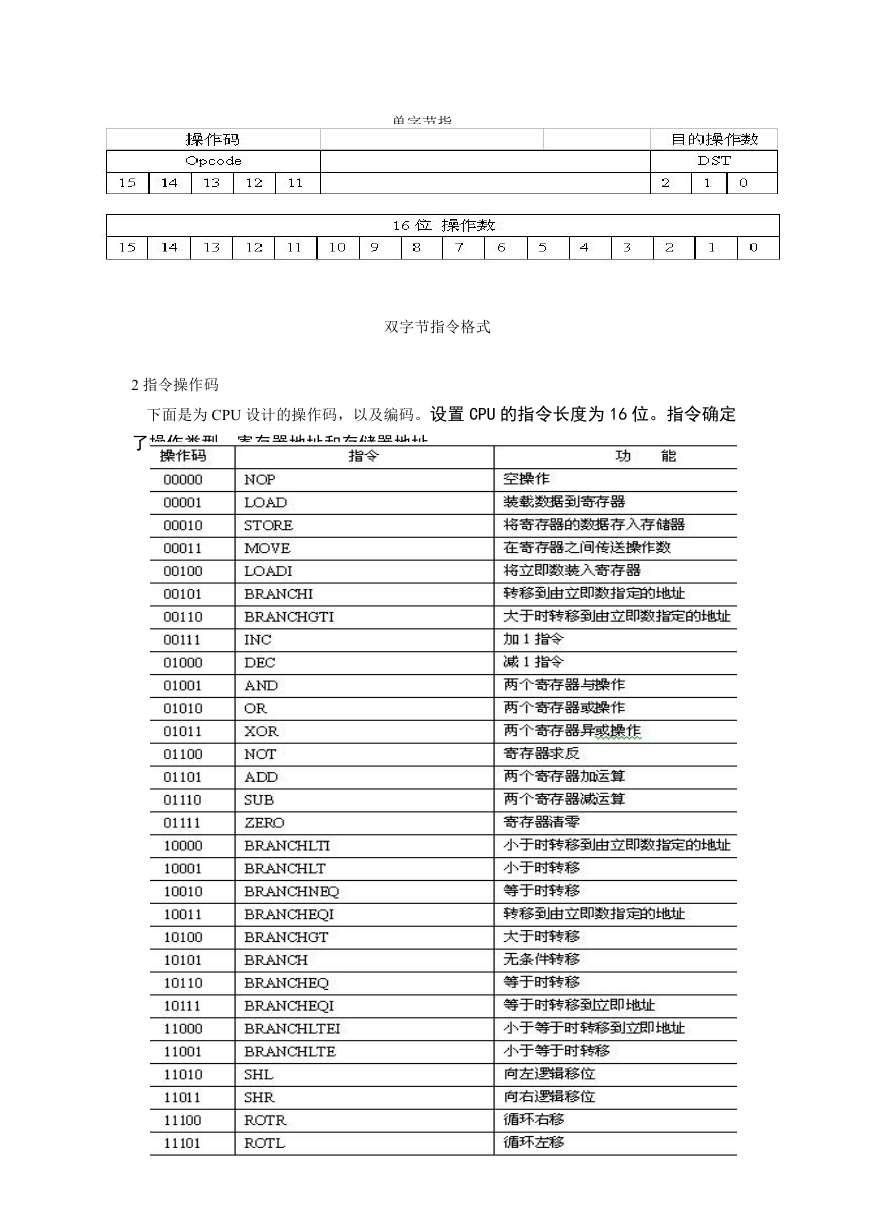

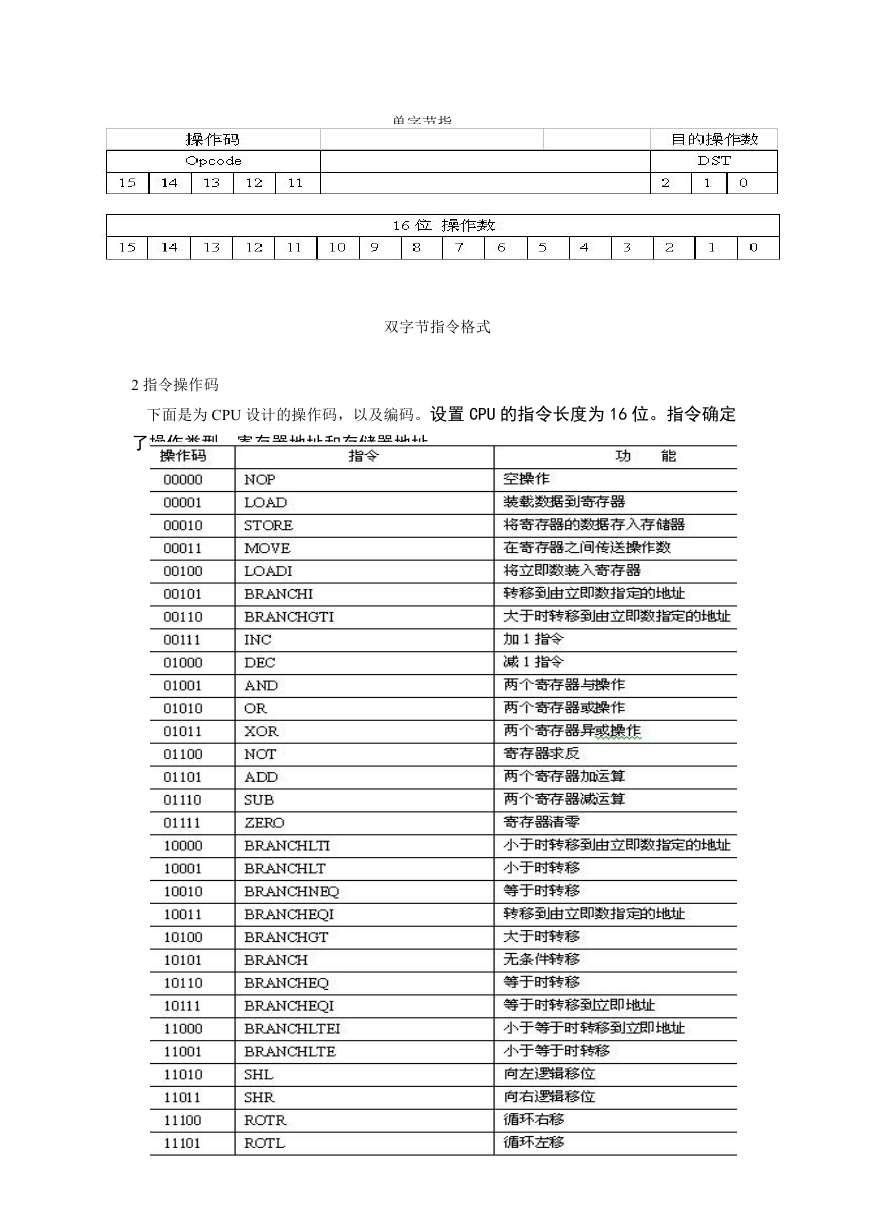

模拟机采用了定长的指令格式,每条指令字长为 16 位。采用的寻址方式为直接

寻址(00)、寄存器寻址(01)、寄存器间接寻址(10)和变址寻址(11),操作

码类型及编码方式如下

操作码

编码方式

sta

0000

add

0001

sub

0010

and1

0011

or1

0100

shl

0101

指令系统决定 CPU 能够有那些功能,并针对这些功能添加相应的指令集,直

接寻址、寄存器寻址、寄存器间接寻址和变址寻址。根据指令的数量对指令进行

编码,指令功能不同占的长度不同,按指令长度可以分为单字指令,双子指令或

多字指令。指令高 5 位为操作码后面跟操作数地址(如果有),如下图所示。

�

单字节指

双字节指令格式

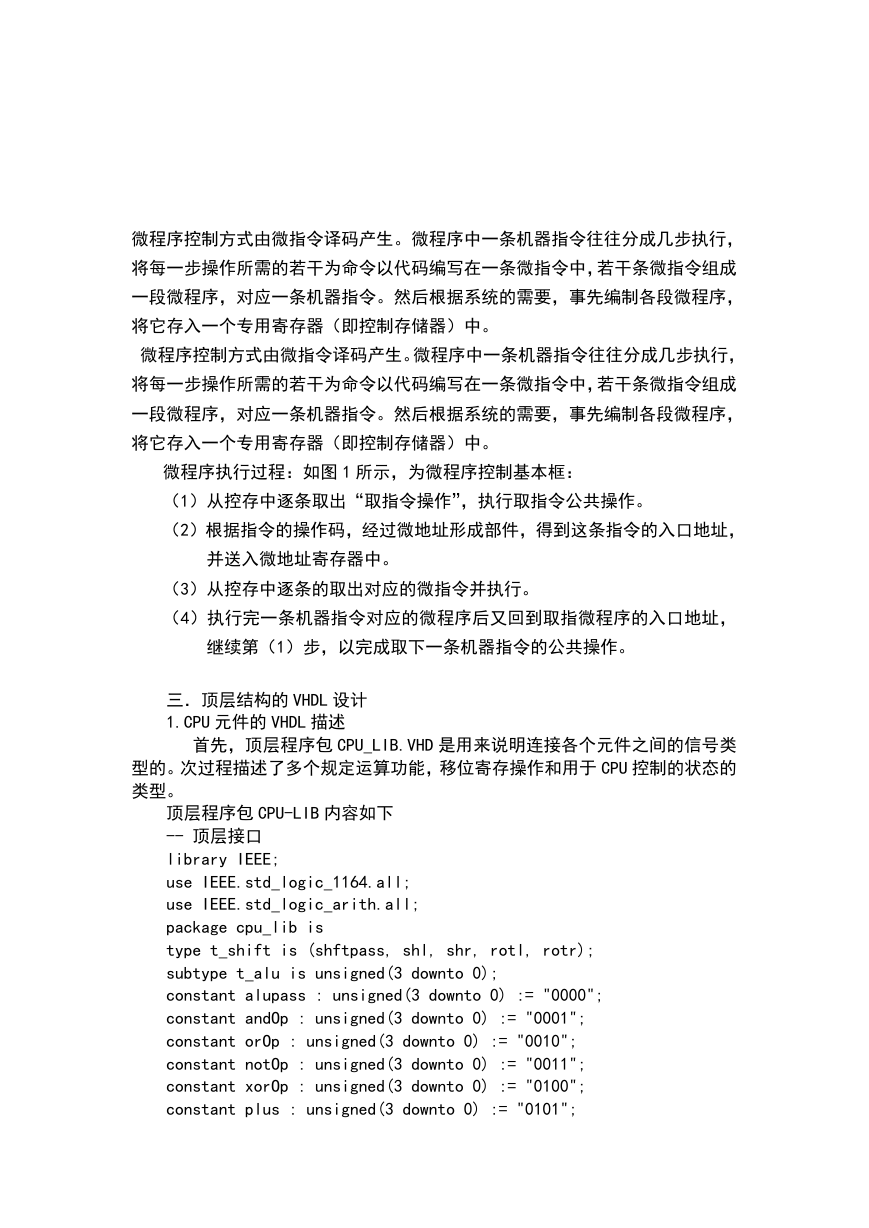

2 指令操作码

下面是为 CPU 设计的操作码,以及编码。设置 CPU 的指令长度为 16 位。指令确定

了操作类型、寄存器地址和存储器地址

�

微程序控制方式由微指令译码产生。微程序中一条机器指令往往分成几步执行,

将每一步操作所需的若干为命令以代码编写在一条微指令中,若干条微指令组成

一段微程序,对应一条机器指令。然后根据系统的需要,事先编制各段微程序,

将它存入一个专用寄存器(即控制存储器)中。

微程序控制方式由微指令译码产生。微程序中一条机器指令往往分成几步执行,

将每一步操作所需的若干为命令以代码编写在一条微指令中,若干条微指令组成

一段微程序,对应一条机器指令。然后根据系统的需要,事先编制各段微程序,

将它存入一个专用寄存器(即控制存储器)中。

微程序执行过程:如图 1 所示,为微程序控制基本框:

(1)从控存中逐条取出“取指令操作”,执行取指令公共操作。

(2)根据指令的操作码,经过微地址形成部件,得到这条指令的入口地址,

并送入微地址寄存器中。

(3)从控存中逐条的取出对应的微指令并执行。

(4)执行完一条机器指令对应的微程序后又回到取指微程序的入口地址,

继续第(1)步,以完成取下一条机器指令的公共操作。

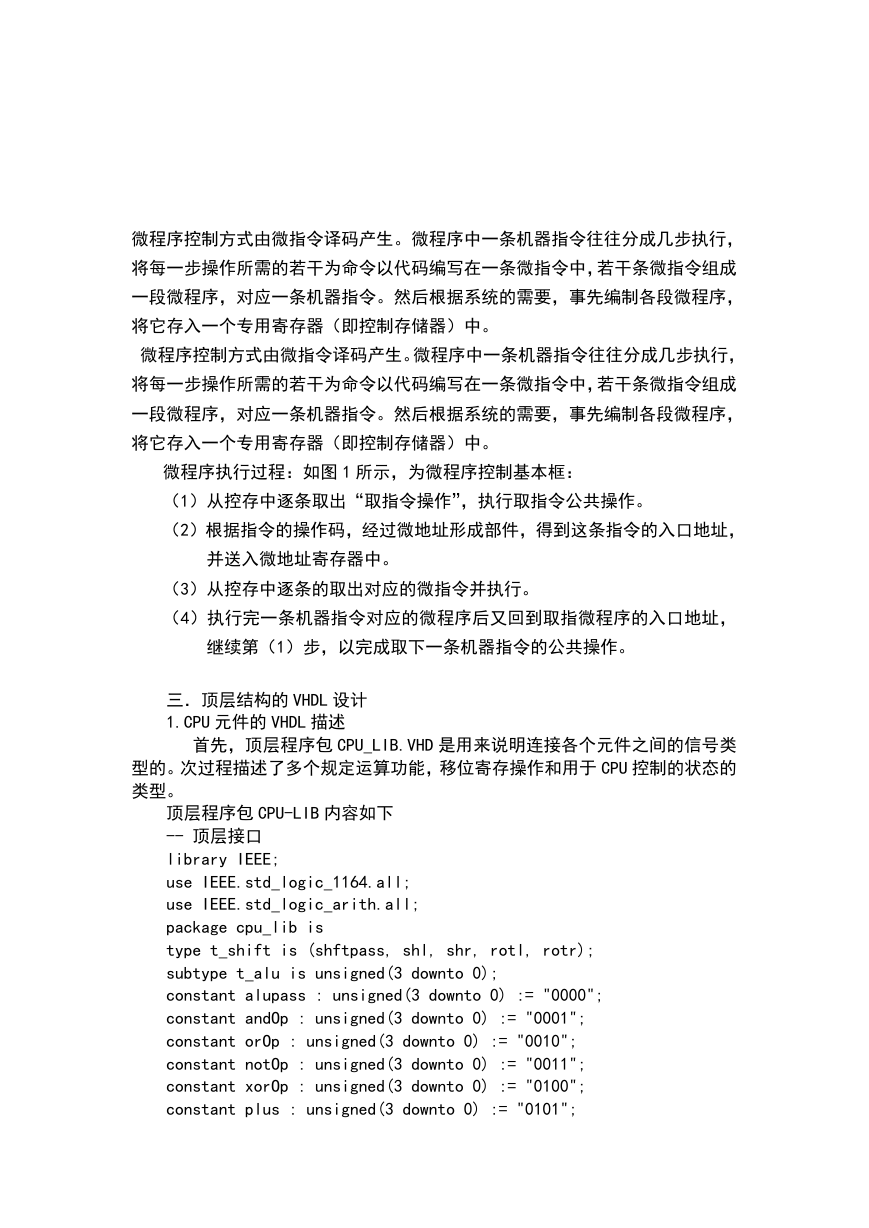

三.顶层结构的 VHDL 设计

1.CPU 元件的 VHDL 描述

首先,顶层程序包 CPU_LIB.VHD 是用来说明连接各个元件之间的信号类

型的。次过程描述了多个规定运算功能,移位寄存操作和用于 CPU 控制的状态的

类型。

顶层程序包 CPU-LIB 内容如下

-- 顶层接口

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

package cpu_lib is

type t_shift is (shftpass, shl, shr, rotl, rotr);

subtype t_alu is unsigned(3 downto 0);

constant alupass : unsigned(3 downto 0) := "0000";

constant andOp : unsigned(3 downto 0) := "0001";

constant orOp : unsigned(3 downto 0) := "0010";

constant notOp : unsigned(3 downto 0) := "0011";

constant xorOp : unsigned(3 downto 0) := "0100";

constant plus : unsigned(3 downto 0) := "0101";

�

constant alusub : unsigned(3 downto 0) := "0110";

constant inc : unsigned(3 downto 0) := "0111";

constant dec : unsigned(3 downto 0) := "1000";

constant zero : unsigned(3 downto 0) := "1001";

type t_comp is (eq, neq, gt, gte, lt, lte);

subtype t_reg is std_logic_vector(2 downto 0);

type state is (reset1, reset2, reset3, reset4, reset5,reset6, execute,

nop, load, store, move,

load2,

load3,

load4,

store2,

store3,store4,

move2,

move3,

move4,incPc, incPc2,

incPc3, incPc4, incPc5, incPc6, loadPc,loadPc2,loadPc3, loadPc4,

bgtI2, bgtI3,

bgtI4, bgtI5, bgtI6, bgtI7,bgtI8, bgtI9,bgtI10, braI2, braI3, braI4,

braI5, braI6,

loadI2,loadI3, loadI4, loadI5, loadI6,inc2, inc3, inc4);

subtype bit16 is std_logic_vector(15 downto 0);

end cpu_lib;

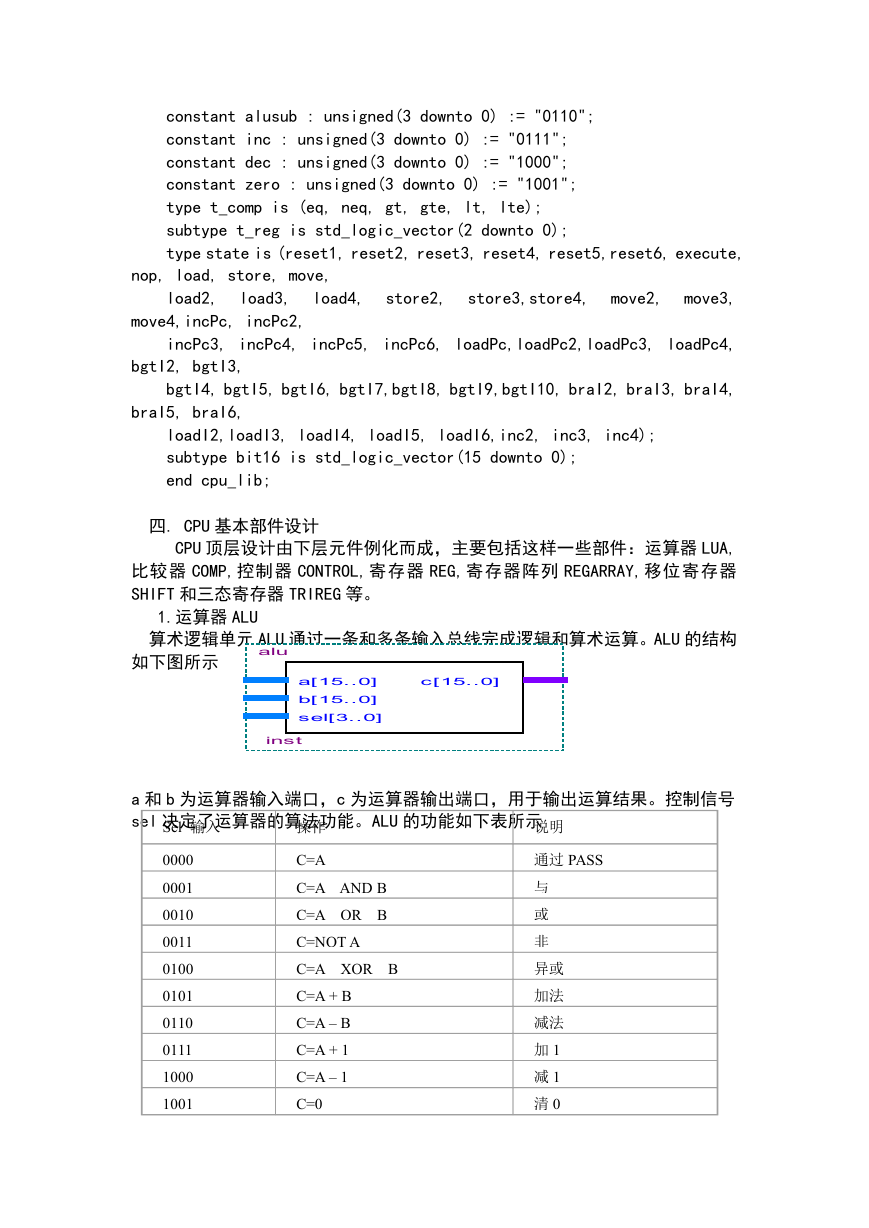

四. CPU 基本部件设计

CPU 顶层设计由下层元件例化而成,主要包括这样一些部件:运算器 LUA,

比较器 COMP,控制器 CONTROL,寄存器 REG,寄存器阵列 REGARRAY,移位寄存器

SHIFT 和三态寄存器 TRIREG 等。

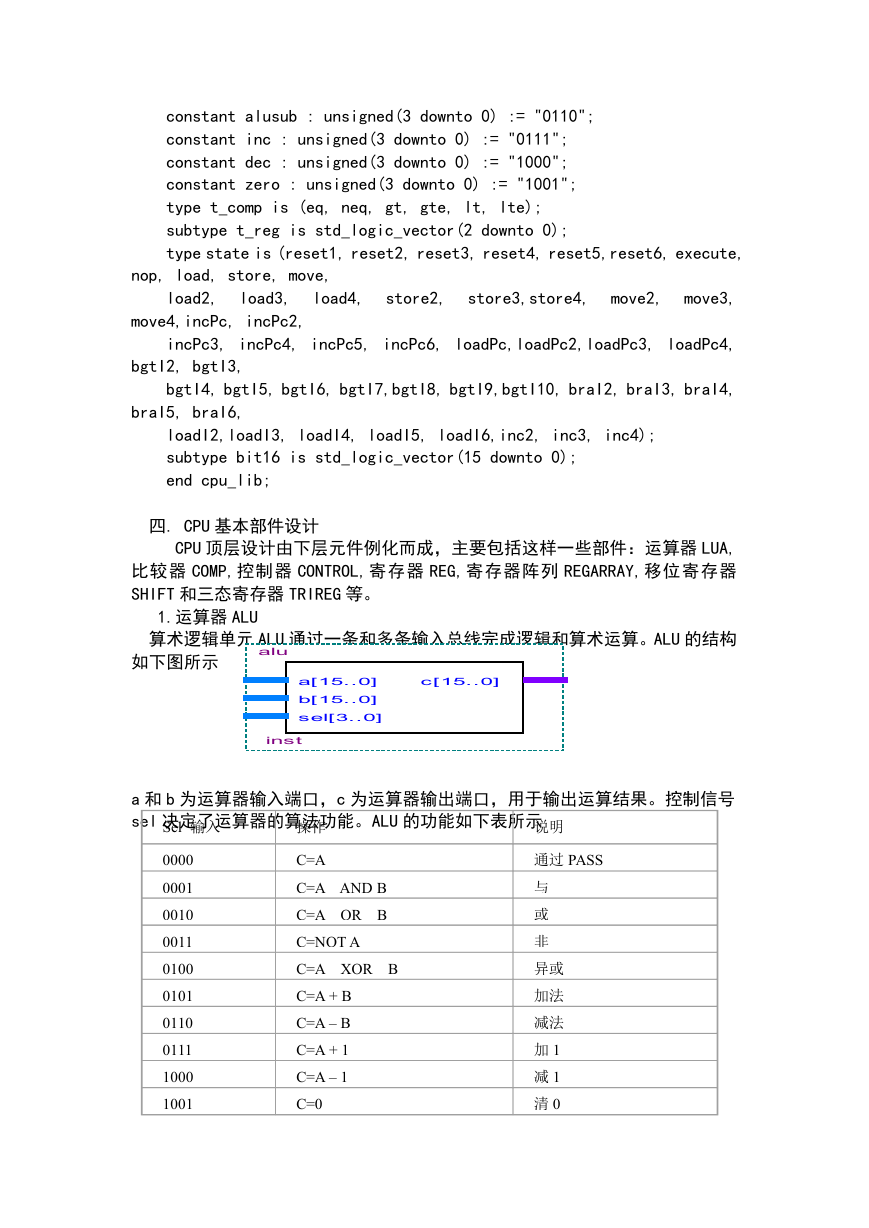

1.运算器 ALU

算术逻辑单元 ALU 通过一条和多条输入总线完成逻辑和算术运算。ALU 的结构

如下图所示

alu

c[15..0]

a[15..0]

b[15..0]

sel[3..0]

inst

a 和 b 为运算器输入端口,c 为运算器输出端口,用于输出运算结果。控制信号

sel 决定了运算器的算法功能。ALU 的功能如下表所示

说明

Sel 输入

操作

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

C=A

C=A AND B

C=A OR B

C=NOT A

C=A XOR B

C=A + B

C=A – B

C=A + 1

C=A – 1

C=0

通过 PASS

与

或

非

异或

加法

减法

加 1

减 1

清 0

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc