2007 年全国大学生电子设计竞赛一等奖作品——数字示波器

发布时间: 2007-11-27 20:28:37

作者:

责任编辑:

数字示波器

作者:黄霖宇、陈鹍、侯碧波

一等

摘要

奖作品

本数字示波器以单片机和 FPGA 为核心,对采样方式的选择和等效采样技术

的实现进行了重点设计,使作品不仅具有实时采样方式,而且采用随机等效采样

技术实现了利用实时采样速率为 1MHz 的 ADC 进行最大 200MHz 的等效采样。

同时系统还具有可测 2mV 小信号、波形存储回放、测频、触发沿选择、校准信

号输出等功能。

Abstract

This digital oscilloscope takes a MCU and FPGA as the core .We made

emphases on the choice of the sampling methods and the implement of equivalent

sampling, as a result, our design not only has the real-time sampling mode but also

can reach the highest equivalent sample rate of 200 MHz using the real-time sample

rate of 1 MHz, by way of random equivalent sampling. At the same time, this system

has many other functions, such as 2mV small-signal measuring, storage and

re-display of waveform, measuring frequency, selective trigger edge , output of the

correction signal and so on.

一、总体方案设计

�

1.方案比较与选择

仔细分析题目要求,以实时采样速率为 1MHz 的 ADC 实现最大 200MHz 的

等效采样,是本题的最大难点,也是设计的重点之一。此外,较宽的信号带宽

(10Hz~10MHz)和较大的幅度动态范围(1mV~8V)也给前级的信号调理电

路提出了很高的要求。对此,我们考虑了以下几种方案:

(1)核心处理器选择:

方案一:纯单片机方式。即完全由单片机来实现前级信号程控调理、采样保

持电路及 A/D 转换器的控制、数据的处理及存储、波形显示和控制电路等功能。

方案二:单片机与 FPGA 结合的方式。即由单片机来完成信号调理和人机界

面等顶层控制功能,而由 FPGA 来完成采集和信号处理等底层的核心计算。

方案一的最大特点是只用单片机,系统规模可以做得很小,成本较低。但是,

单片机在处理高速信号时略显吃力。而且在时序控制方面也显得精度不足。相比

之下,方案二则更加合理和可靠。FPGA 的应用已经相当的普遍和成熟。用其进

行采样时钟控制和信号处理,是提高系统性能和指标最有效的方法。因此,我们

选择单片机与 FPGA 的结合来作为系统的核心处理器。

(2)前级信号调理方案设计:

方案一:一路调理。即所有信号,都通过同一路信号调理电路,经过相应的

衰减或放大设计,将信号幅度控制在合适的范围内,以便后级的数据采样。

方案二:多路调理。即将不同频率范围或不同幅度范围的信号经过各自的电

路进行调理。示波器选择不同的档位,则选择了不同的信号通路。

方案一电路简洁,但是由于信号的频率和幅度跨度都很大,给硬件电路的调

试带来的较大的困难;方案二虽然可以对不同频率和幅度范围内的信号进行单独

调试,降低了每一路通道对硬件电路的要求,但造成电路规模大,结构非常繁琐,

同时如果每一路信号之间的隔离做得不好,也会对采集结果造成很大的影响。综

合考虑,我们选择了方案一,并精心设计了实现电路,使用了压控放大器 AD603

进行两级放大,前面还加了 BUFFER634 以提高系统的输入阻抗。最终很好的完

成了题目的要求。

2.系统总体框图 (图省)

�

本系统采用单片机和 FPGA 作为数据处理和控制核心,将设计任务划分为前

级通道信号调理、触发信号产生、保持与采样、数据处理与存储、波形显示、控

制面板等功能模块。

二、理论分析与参数计算

1.等效采样分析

等效采样的实现方式一般有顺序等效采样和随机等效采样两种,顺序采样要

求能够精确地测出输入信号的频率,而在现今的数字示波器中,大多数采用的是

随机等效采样技术。本系统也采用随机等效采样来实现题目要求。随机等效时间

采样的基本原理是,在每一轮的采集过程中测量每次信号触发时刻后与 A/D 的

第一个采样时钟的时间差,这个时间差表明了触发后的第一次采样时刻,因此,

它确定了本轮采样的数据序列在信号波形中的位置。由于时间差在一个采样周期

内是随机分布的,当多轮采样后,采集的数据序列就能在一定的时间内遍历所有

可能的取值。通过对分布在一段时间上的随机采样数据序列的排序,就能重构信

号的一个完整的采样波形。如图2所示是随机等效采样示意波形:(图省)

在随机等效采样技术中,关键是测出每次触发点与下一个采样时钟间的时间差。

但该时间极短,很难直接测量。一般可以借助时间轴展宽方法测量,时间轴展宽

是一电容充放电双斜率电路,要求充放电的时间比例很准确,本系统利用高主频

FPGA 计数来测量时间差。而等效采样的频率,则与实际的采样速率和存储深度

有关。例如,用 1MHz 的实时采样速率实现 200MHz 的等效采样,即等效倍数

为 200,则需要进行 200 轮采样,每轮采样 1 个点。采样结束后,根据测出的每

一点的时间差,将采样的数值进行重新排列,然后将重排后的数据顺序输出,用

于波形显示。用 1MHz 的采样速率实现等效倍数为 200 倍的随机采样,需要在

1us 的时间内测出 200 个不同的随机时间差,则 FPGA 至少应工作在 200MHz 的

主频上。

2.垂直灵敏度

根据题目要求,垂直分辨率为 8bits,显示屏的垂直刻度为 8div,因此使用 8

�

位 A/D 即可满足题目要求。即垂直方向共 256 点,显示分辨率为 32 点/div.因为

ADC 的参考电压为 5V(详见硬件电路设计中关于 ADC 部分),则示波器幅度

轴上的 8div 对应着峰-峰值为 5V 的信号,即 0.625V/div,由此可以计算出每一档

的垂直灵敏度所对应的信号放大倍数,如表 1 所示:

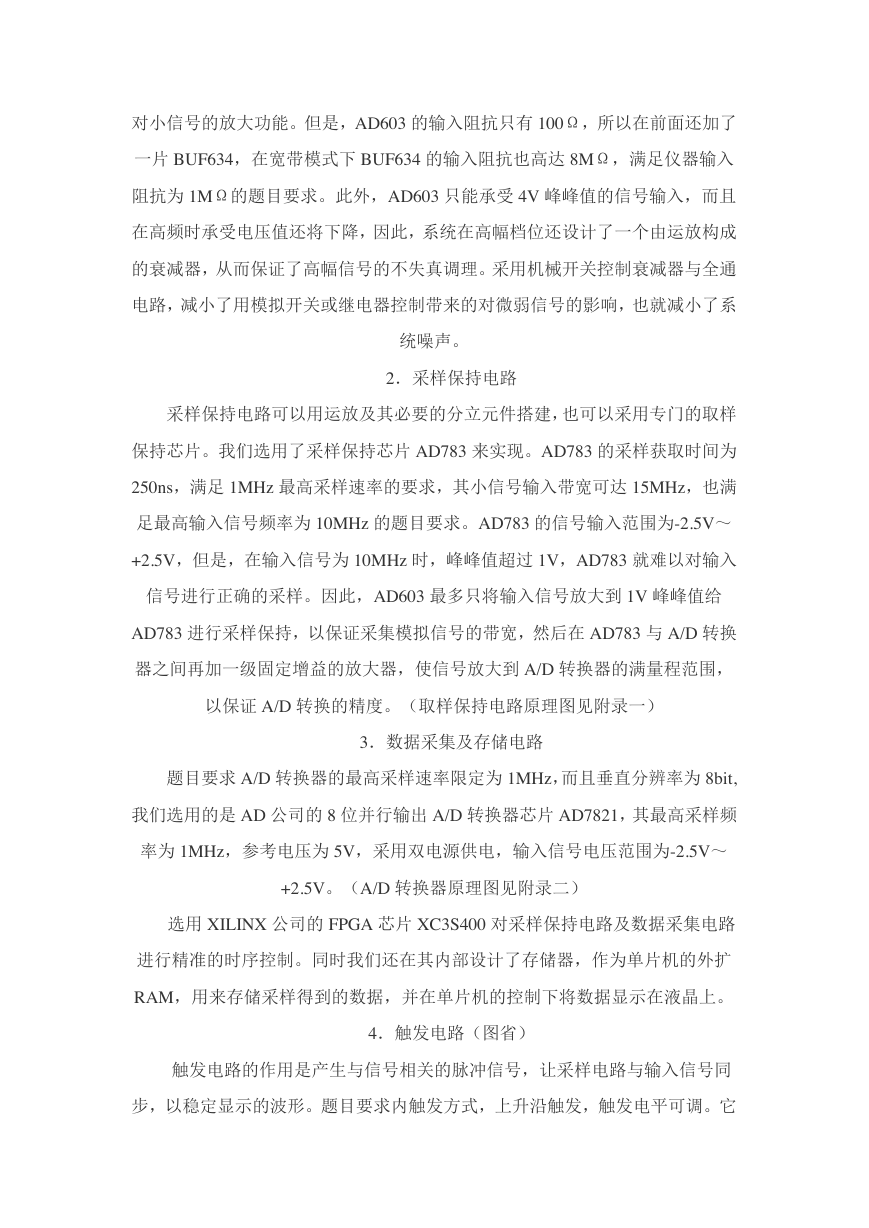

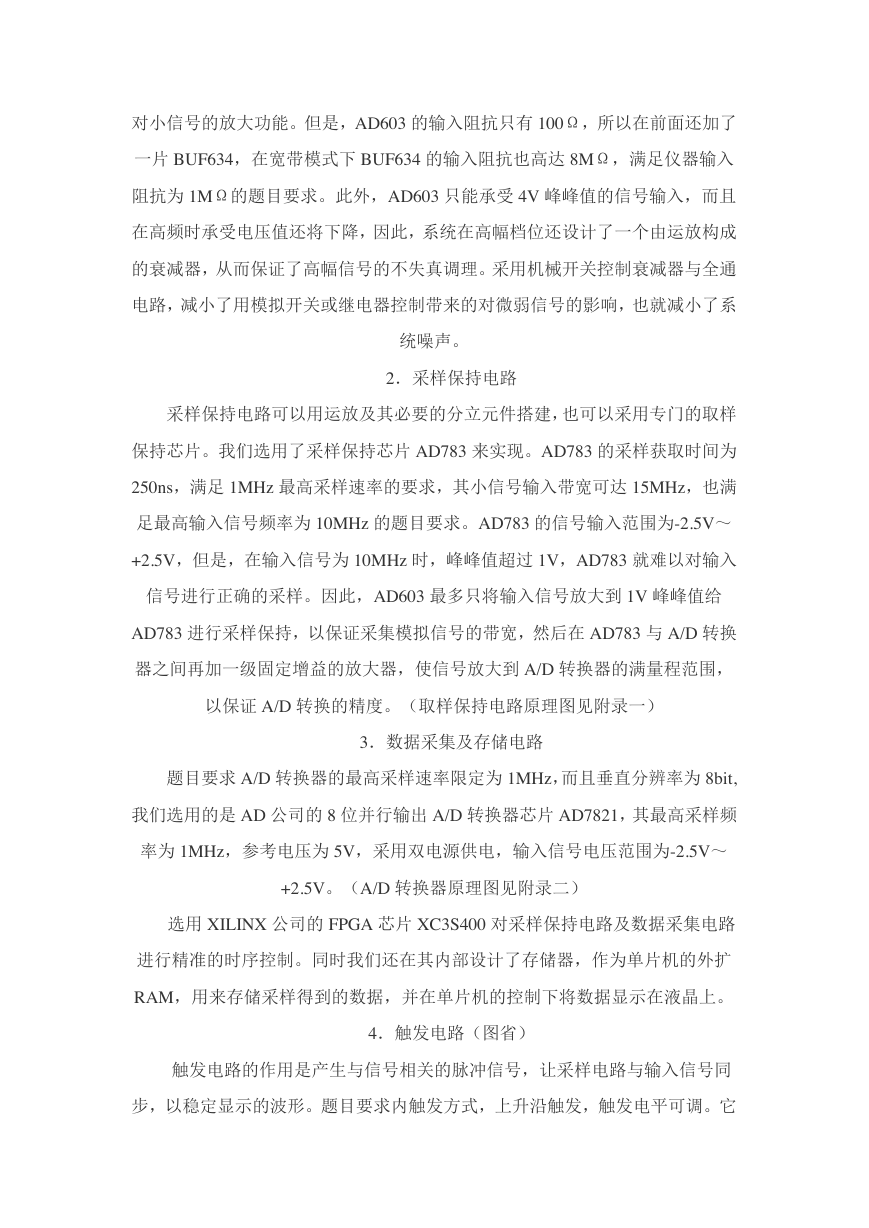

表 1 垂直灵敏度与信号放大倍数对应关系

垂直灵敏度

/(mV/div)

放大倍数

2

5

10

20

50

100

200

500 1000

312.5 125 62.5 31.25 12.5 6.25 3.125 1.25 0.625

根据不同的档位选择,通过单片机内置的 D/A 输出不同的直流电压,来控

制 AD603 的放大倍数,以完成信号的放大需求。

3 扫描速度

设计要求水平显示分辨率至少为 20 点/div,则存储深度 M 应至少为 200 点。

在固定的存储深度下,采样率 fs 与扫描速度 S 成反比,即 10*S*fs=M,系统取

M=200,则 fs=20/S。系统设定的扫描速度从 100ns/div~200ms/div,总共 20 档,

则可以计算出每一档的扫描速度所对应的采样速率,如表 2 所示。

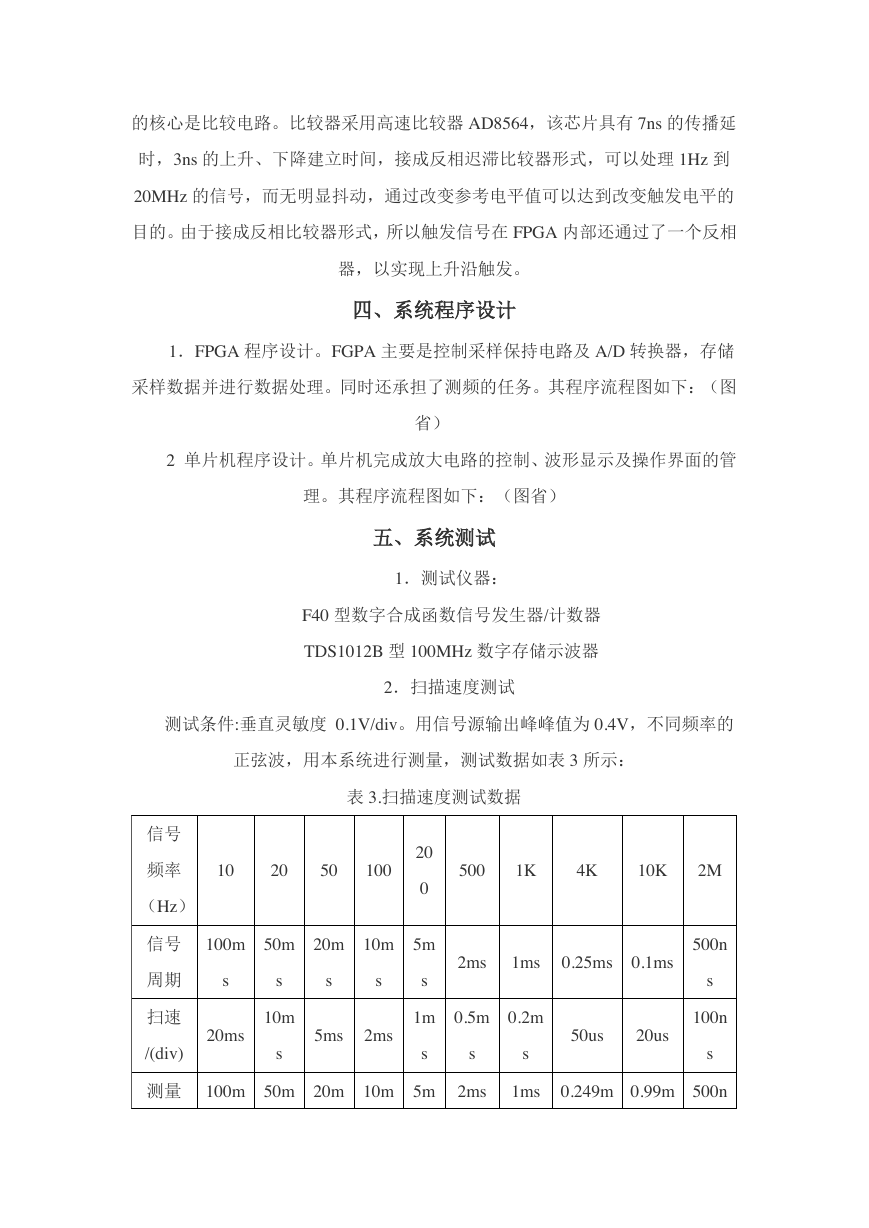

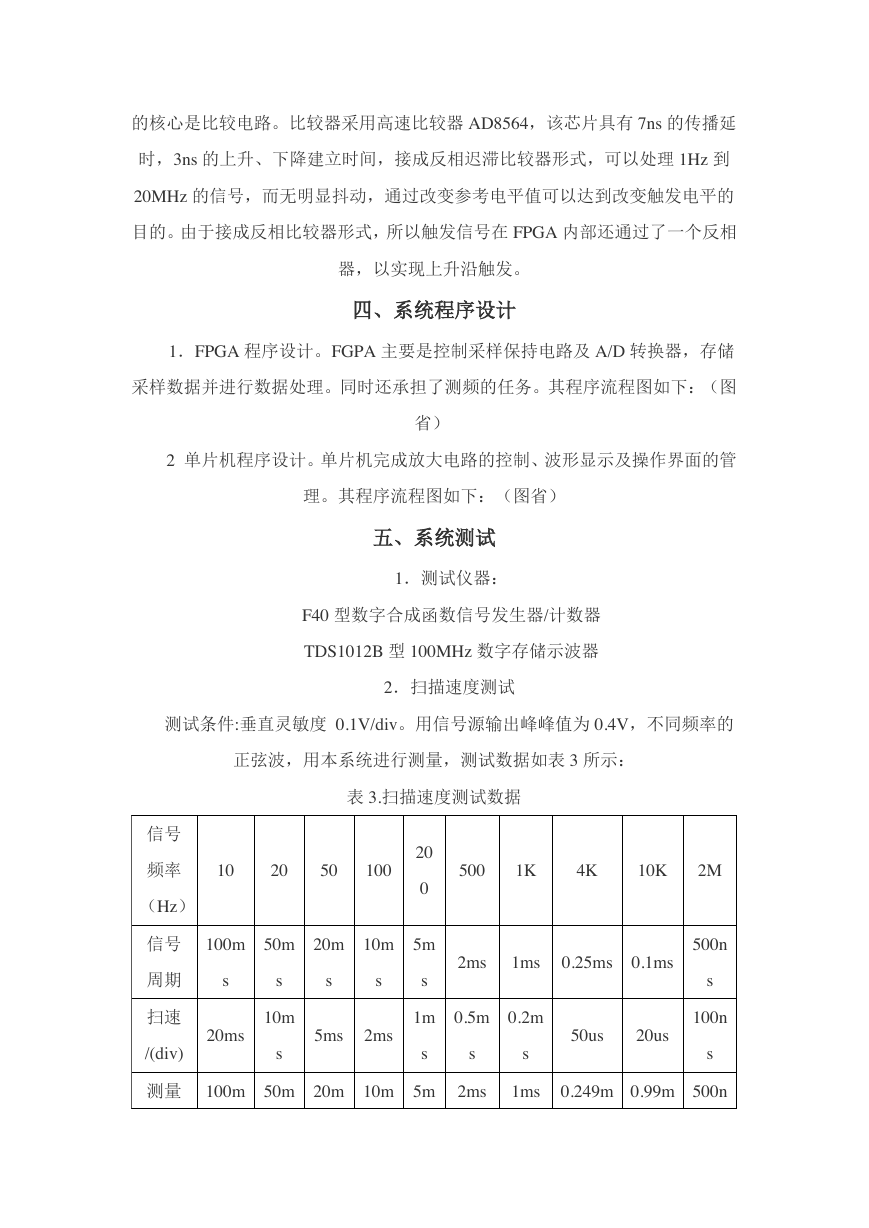

表 2 扫描速度与采样率的对应关系

扫描速度(/div) 100ns 2us

20us 50us 100us 200us 500us 1ms

采样率(Hz)

200M 10M

1M

400K 200K 100K

40K

20K

扫描速度(/div) 2ms

5ms 10ms 20ms 50ms 100ms 200ms

采样率(Hz)

10K

4K

2K

1K

400

200

100

题目要求 A/D 转换器的最高采样速率限定为 1MHz,由表 2 可知,扫描速度

高于 20us/div 的档位都应该使用等效采样。

三、电路分析与设计

1.输入通道调理电路

系统采用两片 AD603 级联方式完成信号的调理。AD603 在 90MHz 的带宽

下增益范围为-11dB~+31dB,两级级联后增益可达-20dB~+60dB,完全可以满足

�

对小信号的放大功能。但是,AD603 的输入阻抗只有 100Ω,所以在前面还加了

一片 BUF634,在宽带模式下 BUF634 的输入阻抗也高达 8MΩ,满足仪器输入

阻抗为 1MΩ的题目要求。此外,AD603 只能承受 4V 峰峰值的信号输入,而且

在高频时承受电压值还将下降,因此,系统在高幅档位还设计了一个由运放构成

的衰减器,从而保证了高幅信号的不失真调理。采用机械开关控制衰减器与全通

电路,减小了用模拟开关或继电器控制带来的对微弱信号的影响,也就减小了系

统噪声。

2.采样保持电路

采样保持电路可以用运放及其必要的分立元件搭建,也可以采用专门的取样

保持芯片。我们选用了采样保持芯片 AD783 来实现。AD783 的采样获取时间为

250ns,满足 1MHz 最高采样速率的要求,其小信号输入带宽可达 15MHz,也满

足最高输入信号频率为 10MHz 的题目要求。AD783 的信号输入范围为-2.5V~

+2.5V,但是,在输入信号为 10MHz 时,峰峰值超过 1V,AD783 就难以对输入

信号进行正确的采样。因此,AD603 最多只将输入信号放大到 1V 峰峰值给

AD783 进行采样保持,以保证采集模拟信号的带宽,然后在 AD783 与 A/D 转换

器之间再加一级固定增益的放大器,使信号放大到 A/D 转换器的满量程范围,

以保证 A/D 转换的精度。(取样保持电路原理图见附录一)

3.数据采集及存储电路

题目要求 A/D 转换器的最高采样速率限定为 1MHz,而且垂直分辨率为 8bit,

我们选用的是 AD 公司的 8 位并行输出 A/D 转换器芯片 AD7821,其最高采样频

率为 1MHz,参考电压为 5V,采用双电源供电,输入信号电压范围为-2.5V~

+2.5V。(A/D 转换器原理图见附录二)

选用 XILINX 公司的 FPGA 芯片 XC3S400 对采样保持电路及数据采集电路

进行精准的时序控制。同时我们还在其内部设计了存储器,作为单片机的外扩

RAM,用来存储采样得到的数据,并在单片机的控制下将数据显示在液晶上。

4.触发电路(图省)

触发电路的作用是产生与信号相关的脉冲信号,让采样电路与输入信号同

步,以稳定显示的波形。题目要求内触发方式,上升沿触发,触发电平可调。它

�

的核心是比较电路。比较器采用高速比较器 AD8564,该芯片具有 7ns 的传播延

时,3ns 的上升、下降建立时间,接成反相迟滞比较器形式,可以处理 1Hz 到

20MHz 的信号,而无明显抖动,通过改变参考电平值可以达到改变触发电平的

目的。由于接成反相比较器形式,所以触发信号在 FPGA 内部还通过了一个反相

器,以实现上升沿触发。

四、系统程序设计

1.FPGA 程序设计。FGPA 主要是控制采样保持电路及 A/D 转换器,存储

采样数据并进行数据处理。同时还承担了测频的任务。其程序流程图如下:(图

2 单片机程序设计。单片机完成放大电路的控制、波形显示及操作界面的管

省)

理。其程序流程图如下:(图省)

五、系统测试

1.测试仪器:

F40 型数字合成函数信号发生器/计数器

TDS1012B 型 100MHz 数字存储示波器

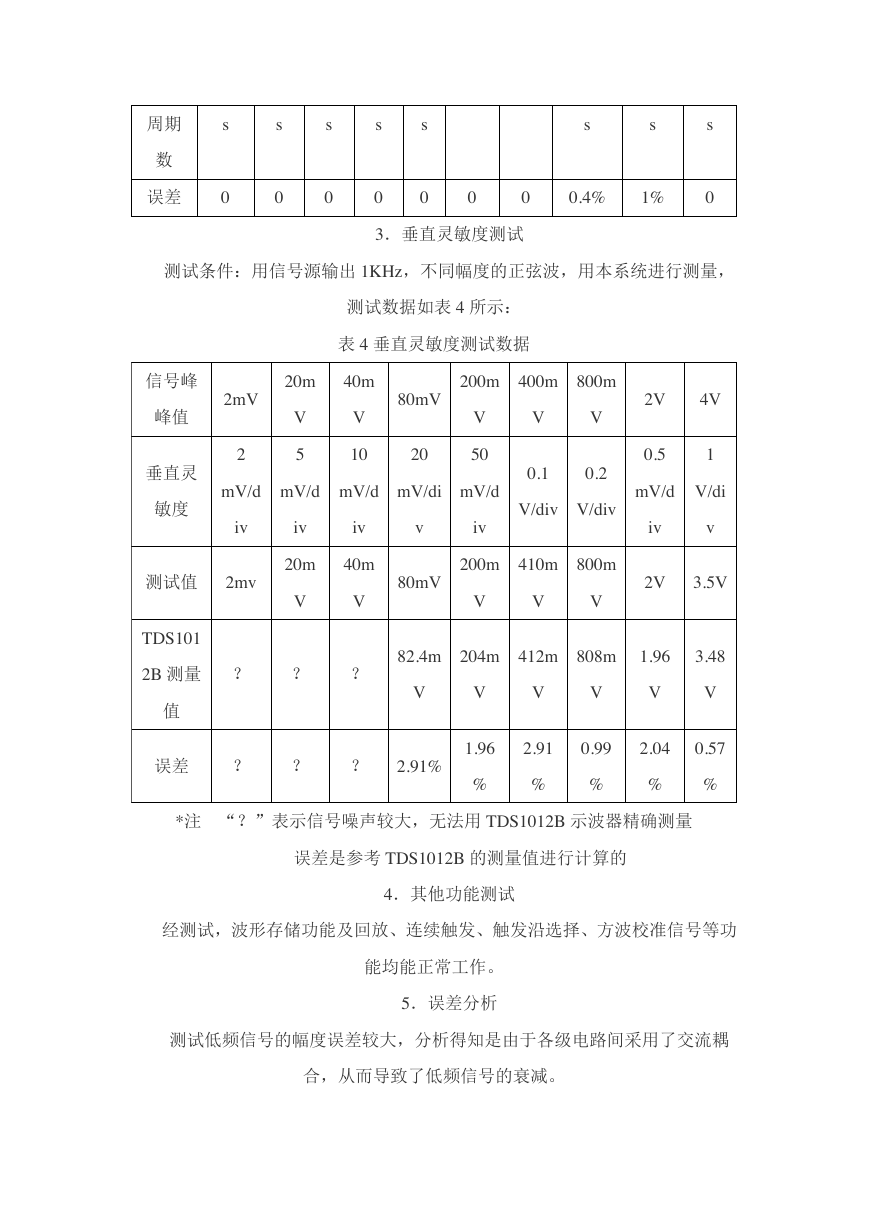

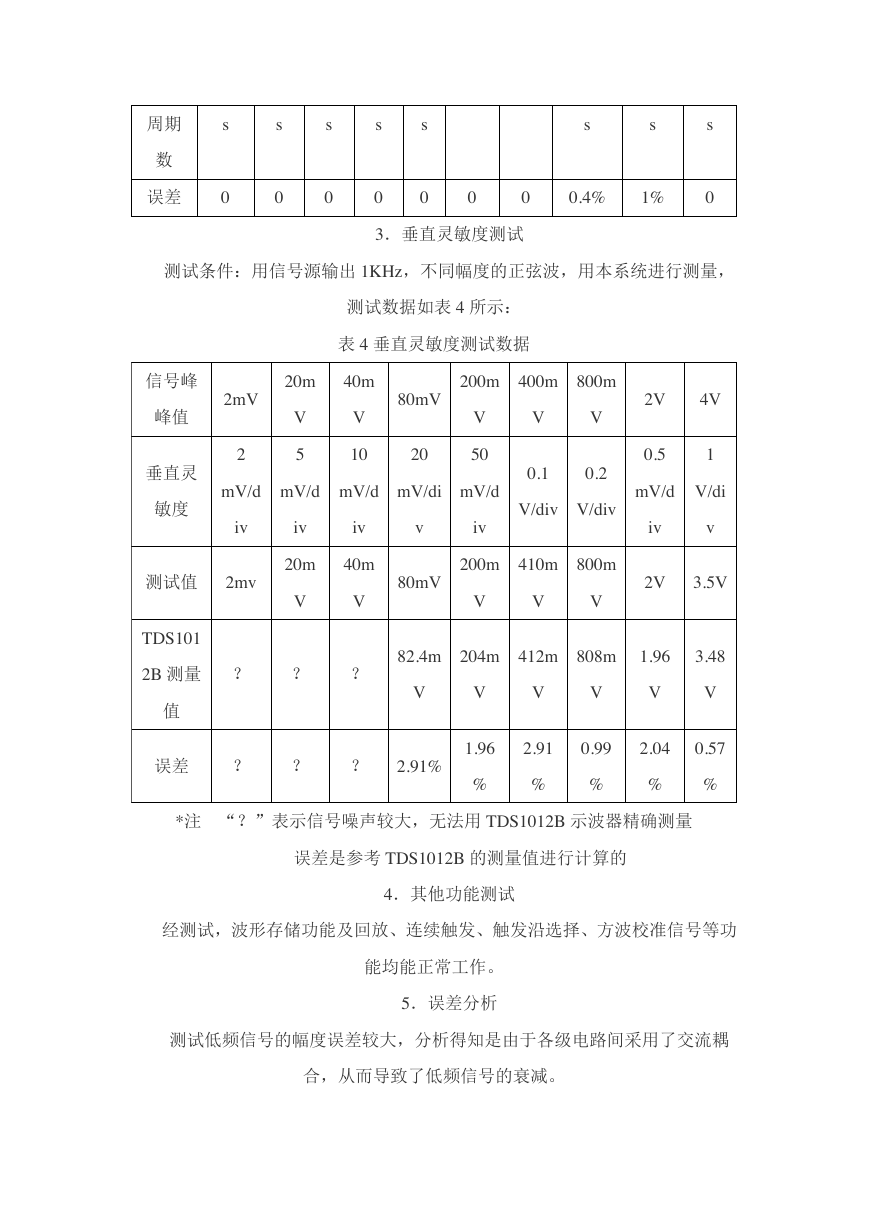

2.扫描速度测试

测试条件:垂直灵敏度 0.1V/div。用信号源输出峰峰值为 0.4V,不同频率的

正弦波,用本系统进行测量,测试数据如表 3 所示:

表 3.扫描速度测试数据

信号

频率

(Hz)

信号

周期

扫速

/(div)

10

20

50

100

20

0

500

1K

4K

10K

2M

100m

50m

20m

10m

5m

s

s

s

s

s

2ms

1ms 0.25ms 0.1ms

20ms

10m

s

1m

0.5m

0.2m

5ms 2ms

50us

20us

s

s

s

500n

s

100n

s

测量 100m 50m 20m 10m 5m 2ms

1ms 0.249m 0.99m 500n

�

周期

数

误差

s

s

s

s

s

s

s

s

0

0

0

0

0

0

0

0.4%

1%

0

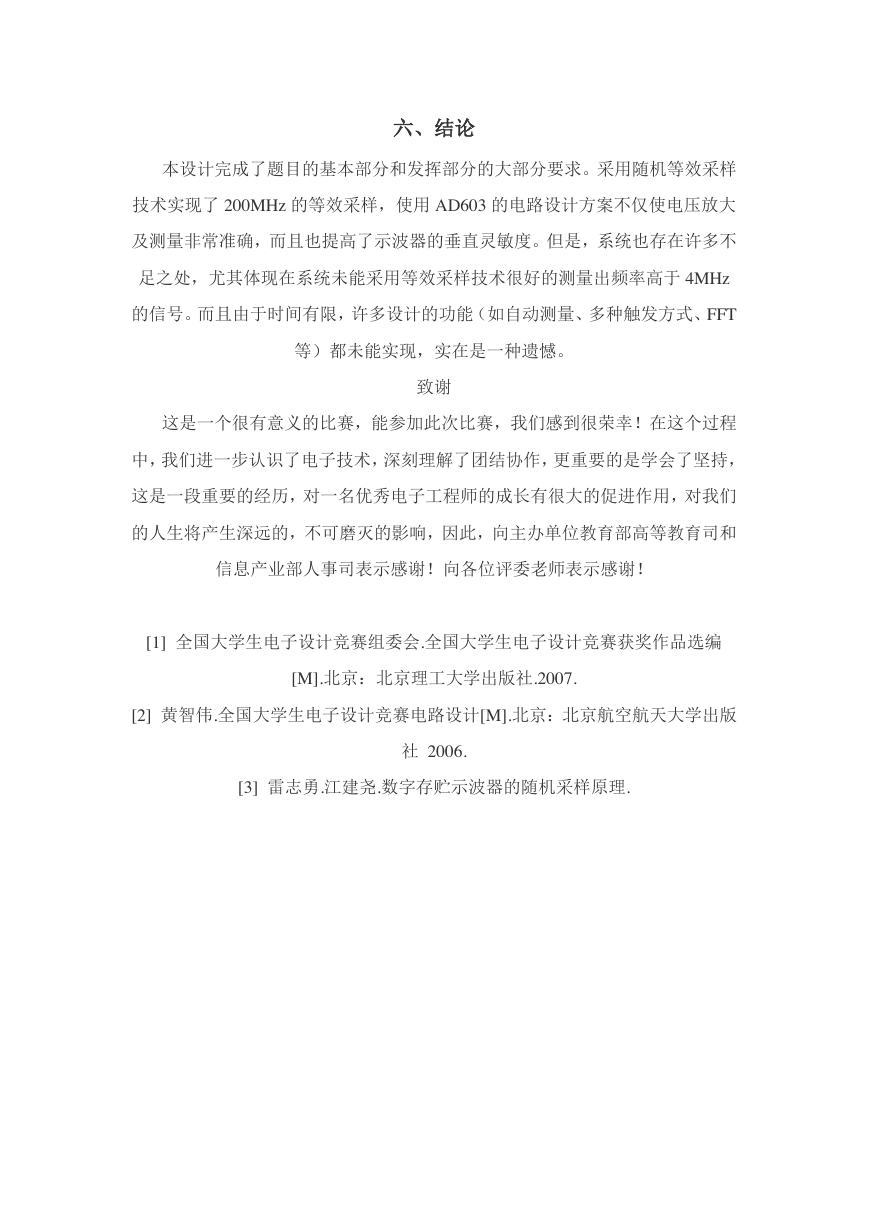

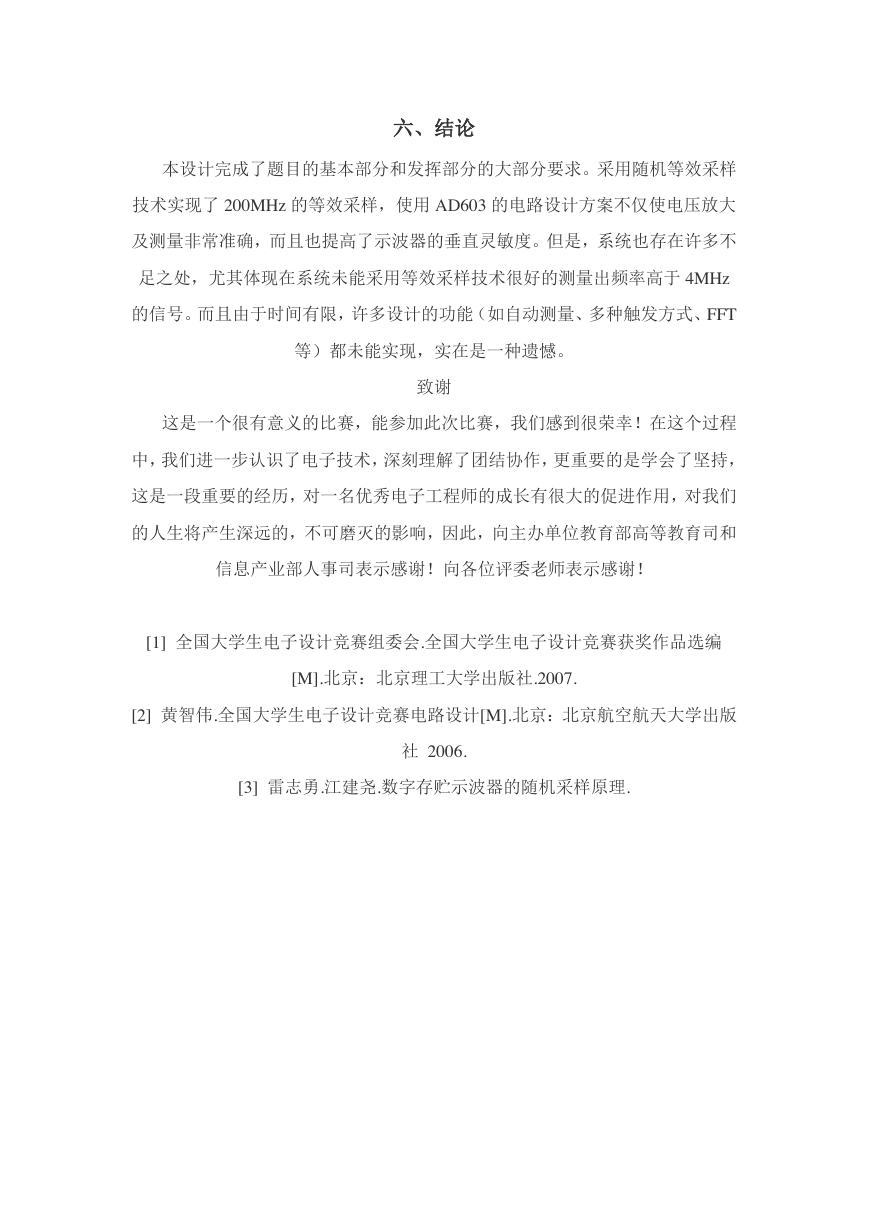

3.垂直灵敏度测试

测试条件:用信号源输出 1KHz,不同幅度的正弦波,用本系统进行测量,

测试数据如表 4 所示:

表 4 垂直灵敏度测试数据

信号峰

峰值

垂直灵

敏度

20m

40m

200m

400m

800m

2mV

2

V

5

V

10

80mV

20

V

50

mV/d

mV/d

mV/d

mV/di

mV/d

iv

iv

iv

v

iv

V

V

0.1

0.2

V/div

V/div

2V

4V

0.5

1

mV/d

V/di

iv

v

测试值

2mv

20m

40m

200m

410m

800m

80mV

2V

3.5V

V

V

V

V

V

TDS101

2B 测量

? ? ?

值

82.4m

204m

412m

808m

1.96

3.48

V

V

V

V

V

V

误差 ? ? ?

2.91%

1.96

2.91

0.99

2.04

0.57

%

%

%

%

%

*注 “?”表示信号噪声较大,无法用 TDS1012B 示波器精确测量

误差是参考 TDS1012B 的测量值进行计算的

4.其他功能测试

经测试,波形存储功能及回放、连续触发、触发沿选择、方波校准信号等功

能均能正常工作。

5.误差分析

测试低频信号的幅度误差较大,分析得知是由于各级电路间采用了交流耦

合,从而导致了低频信号的衰减。

�

六、结论

本设计完成了题目的基本部分和发挥部分的大部分要求。采用随机等效采样

技术实现了 200MHz 的等效采样,使用 AD603 的电路设计方案不仅使电压放大

及测量非常准确,而且也提高了示波器的垂直灵敏度。但是,系统也存在许多不

足之处,尤其体现在系统未能采用等效采样技术很好的测量出频率高于 4MHz

的信号。而且由于时间有限,许多设计的功能(如自动测量、多种触发方式、FFT

等)都未能实现,实在是一种遗憾。

致谢

这是一个很有意义的比赛,能参加此次比赛,我们感到很荣幸!在这个过程

中,我们进一步认识了电子技术,深刻理解了团结协作,更重要的是学会了坚持,

这是一段重要的经历,对一名优秀电子工程师的成长有很大的促进作用,对我们

的人生将产生深远的,不可磨灭的影响,因此,向主办单位教育部高等教育司和

信息产业部人事司表示感谢!向各位评委老师表示感谢!

[1] 全国大学生电子设计竞赛组委会.全国大学生电子设计竞赛获奖作品选编

[M].北京:北京理工大学出版社.2007.

[2] 黄智伟.全国大学生电子设计竞赛电路设计[M].北京:北京航空航天大学出版

社 2006.

[3] 雷志勇.江建尧.数字存贮示波器的随机采样原理.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc