5

4

3

2

1

D

C

B

A

D

C

B

A

ALINX Confidential

5

4

3

2

Http://www.heijin.org

Title

Title

Title

Size

Size

Size

Date:

Date:

Date:

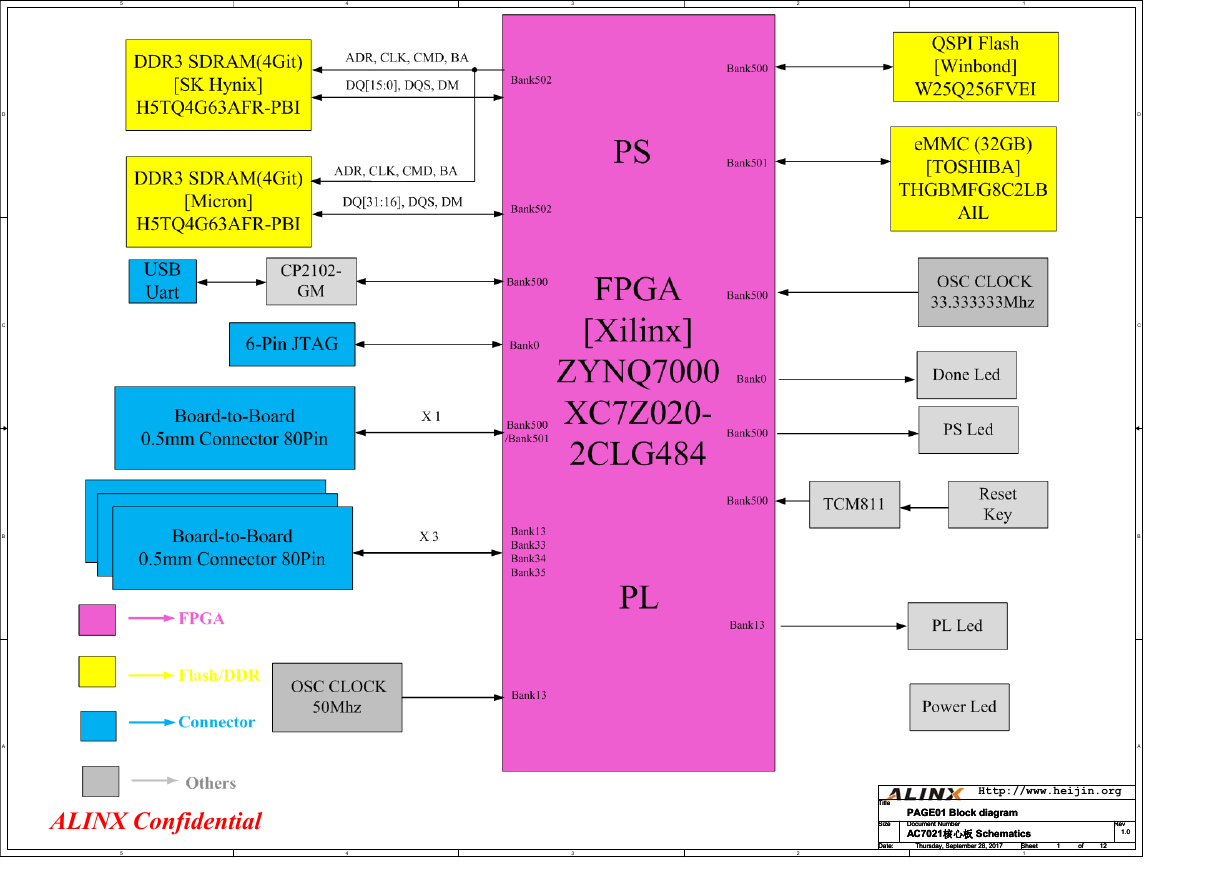

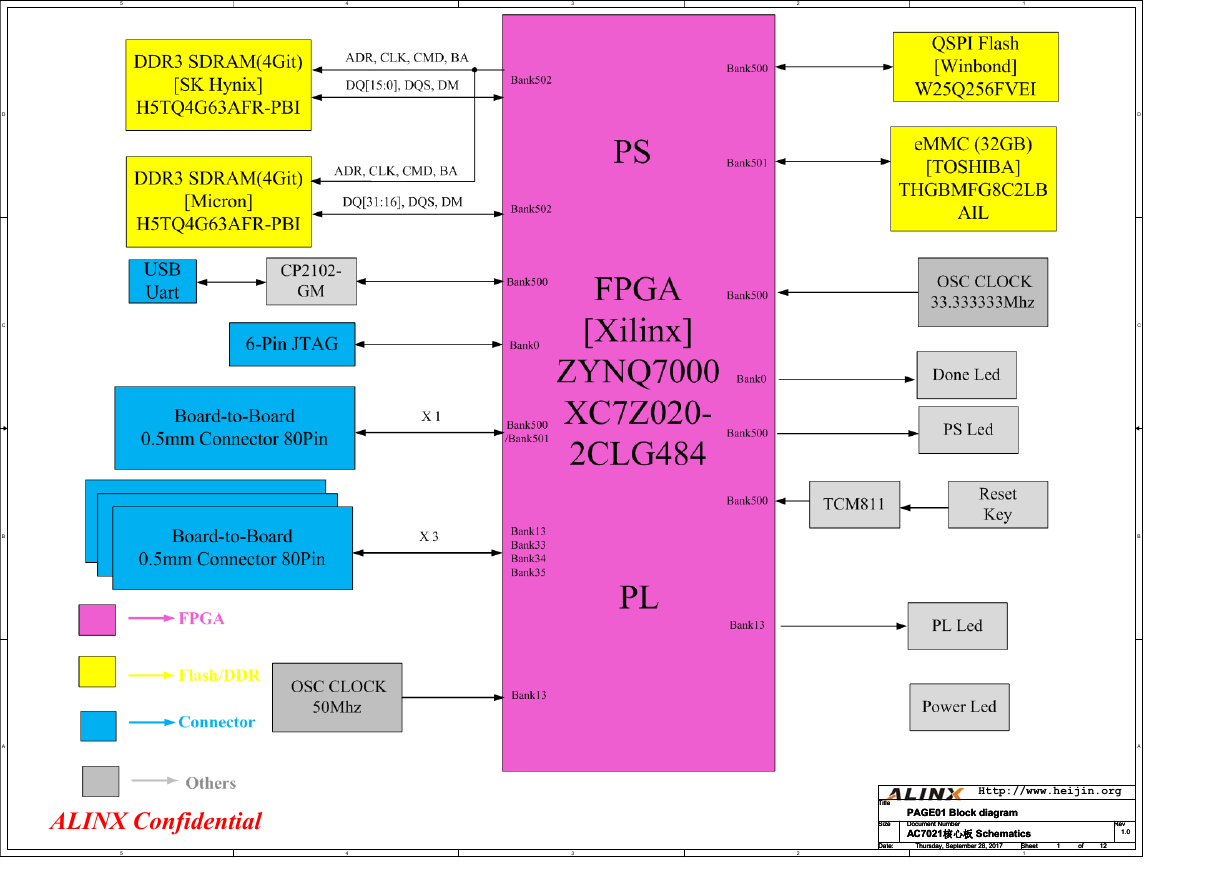

PAGE01 Block diagram

PAGE01 Block diagram

PAGE01 Block diagram

Document Number

Document Number

Document Number

AC7021核心板 Schematics

AC7021核心板 Schematics

AC7021核心板 Schematics

Sheet

Sheet

Sheet

1

Thursday, September 28, 2017

Thursday, September 28, 2017

Thursday, September 28, 2017

Rev

Rev

Rev

1.0

1.0

1.0

1

1

1

of

of

of

12

12

12

�

D

C

B

A

5

4

3

2

1

+3.3V

+1.8V

+3.3V

AVCC

+1.8V

BLM18SG121TN1

L1

C169

47uF

R12

G9

T7

T8

T10

G10

FPGA_DONE

T12

FPGA_PROG_B

T11

BANK0

U1A

VCCO_0

VCCBATT_0

RSVDVCC1

RSVDVCC2

RSVDVCC3

RSVDGND

DONE_0

VCCADC_0

VREFP_0

VREFN_0

VP_0

VN_0

DXP_0

DXN_0

PROGRAM_B_0

GNDADC_0

K11

M11

L12

L11

M12

N11

N12

K12

+3.3V

FPGA_TDI

FPGA_TDO

FPGA_TCK

FPGA_TMS

FPGA_TDI

FPGA_TDO

FPGA_TCK

FPGA_TMS

R2 4.7K

T13

H13

G14

G11

G12

T14

CFGBVS_0

TDI_0

TDO_0

TCK_0

TMS_0

INIT_B_0

XC7Z020-2CLG484

R1

4.7K

11

11

11

11

+3.3V

AGND

XADC_VP

XADC_VN

AGND

J1

1

2

3

4

5

6

CON6

FPGA_TMS

FPGA_TDI

FPGA_TDO

FPGA_TCK

+3.3V

C2

0.1uF

C3

470nf

AGND

XADC_VP

XADC_VN

11

11

L2 BLM18SG121TN1

AGND

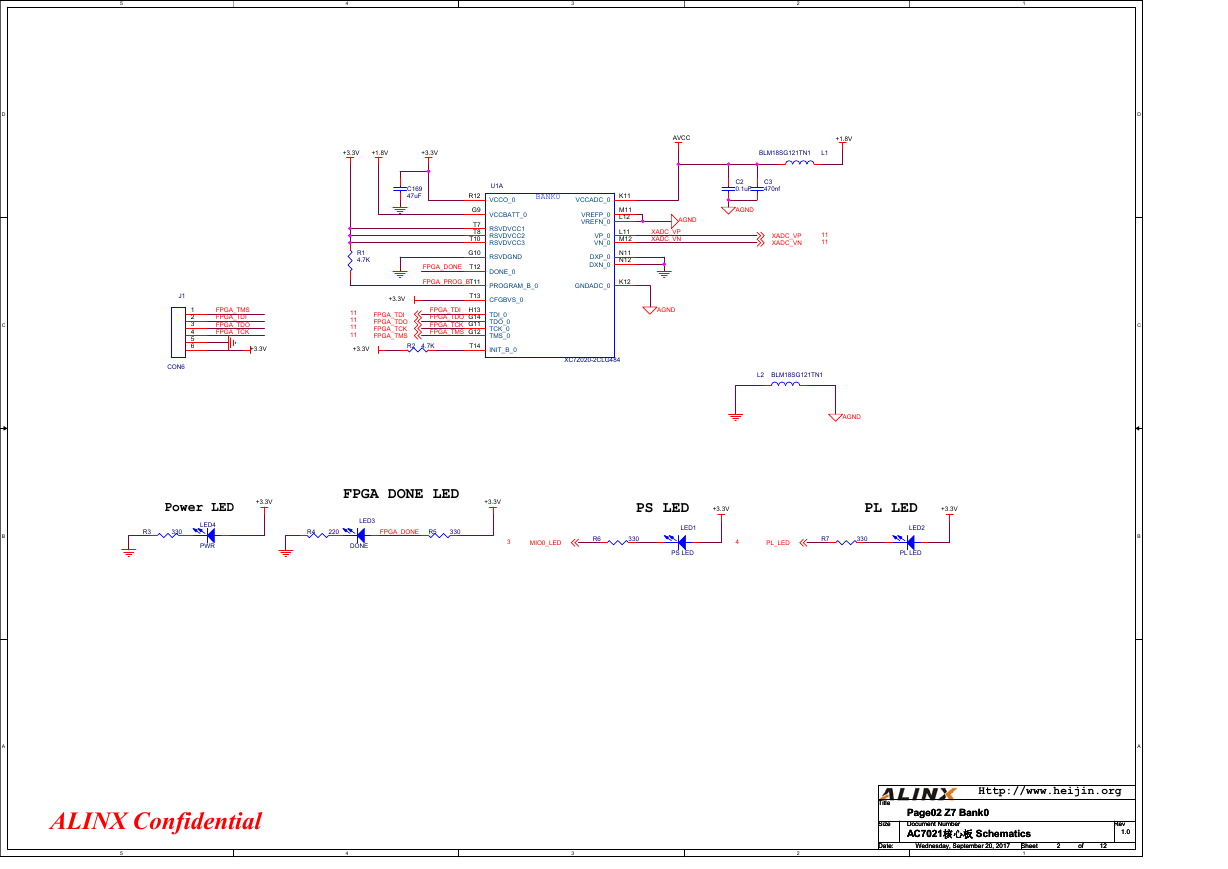

Power LED

+3.3V

R3

330

LED4

PWR

FPGA DONE LED

+3.3V

LED3

R4

220

FPGA_DONE

R5

330

DONE

PS LED

+3.3V

PL LED

+3.3V

3

MIO0_LED

R6

330

LED1

PS LED

4

PL_LED

R7

330

LED2

PL LED

D

C

B

A

ALINX Confidential

5

4

3

2

Http://www.heijin.org

Title

Title

Title

Size

Size

Size

Date:

Date:

Date:

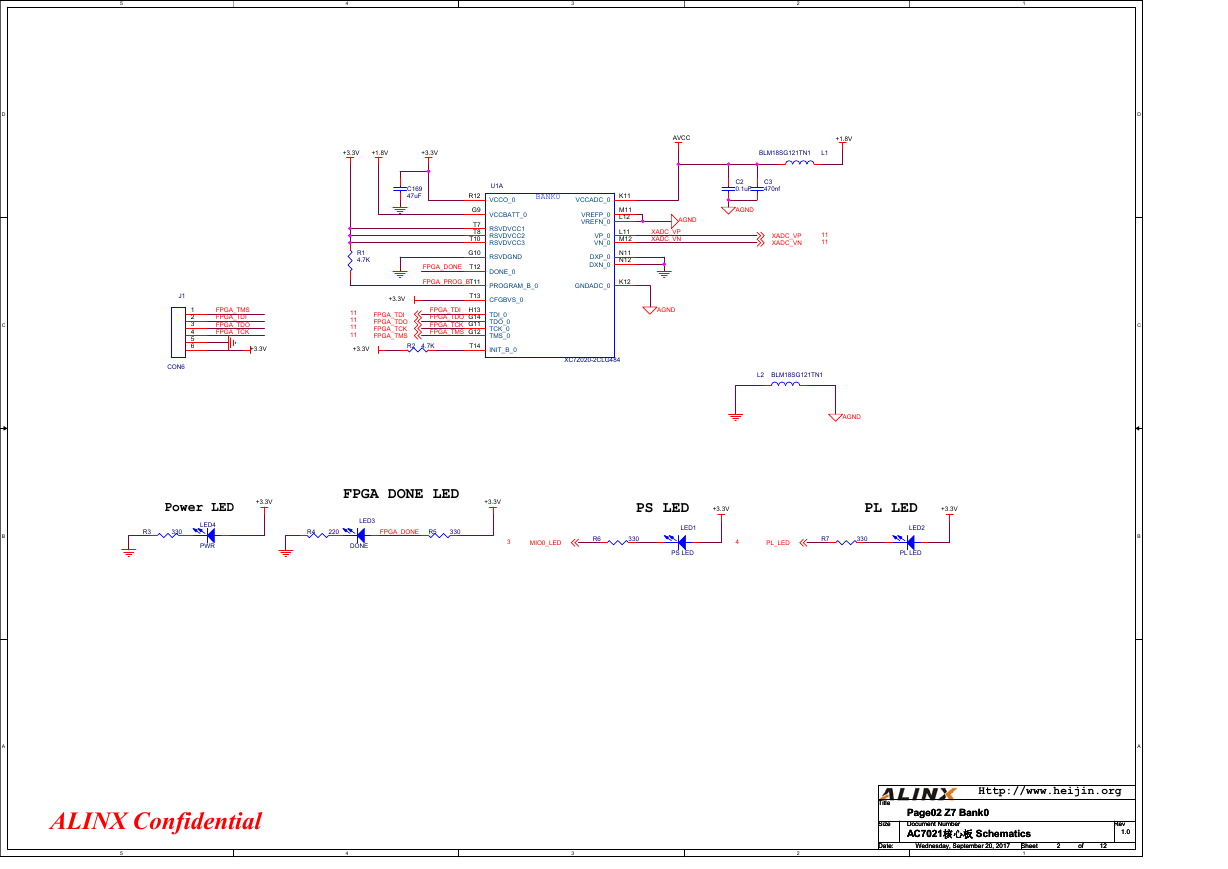

Page02 Z7 Bank0

Page02 Z7 Bank0

Page02 Z7 Bank0

Document Number

Document Number

Document Number

AC7021核心板 Schematics

AC7021核心板 Schematics

AC7021核心板 Schematics

Sheet

Sheet

Sheet

1

Wednesday, September 20, 2017

Wednesday, September 20, 2017

Wednesday, September 20, 2017

Rev

Rev

Rev

1.0

1.0

1.0

2

2

2

of

of

of

12

12

12

�

D

C

B

A

5

4

3

2

1

+3.3V

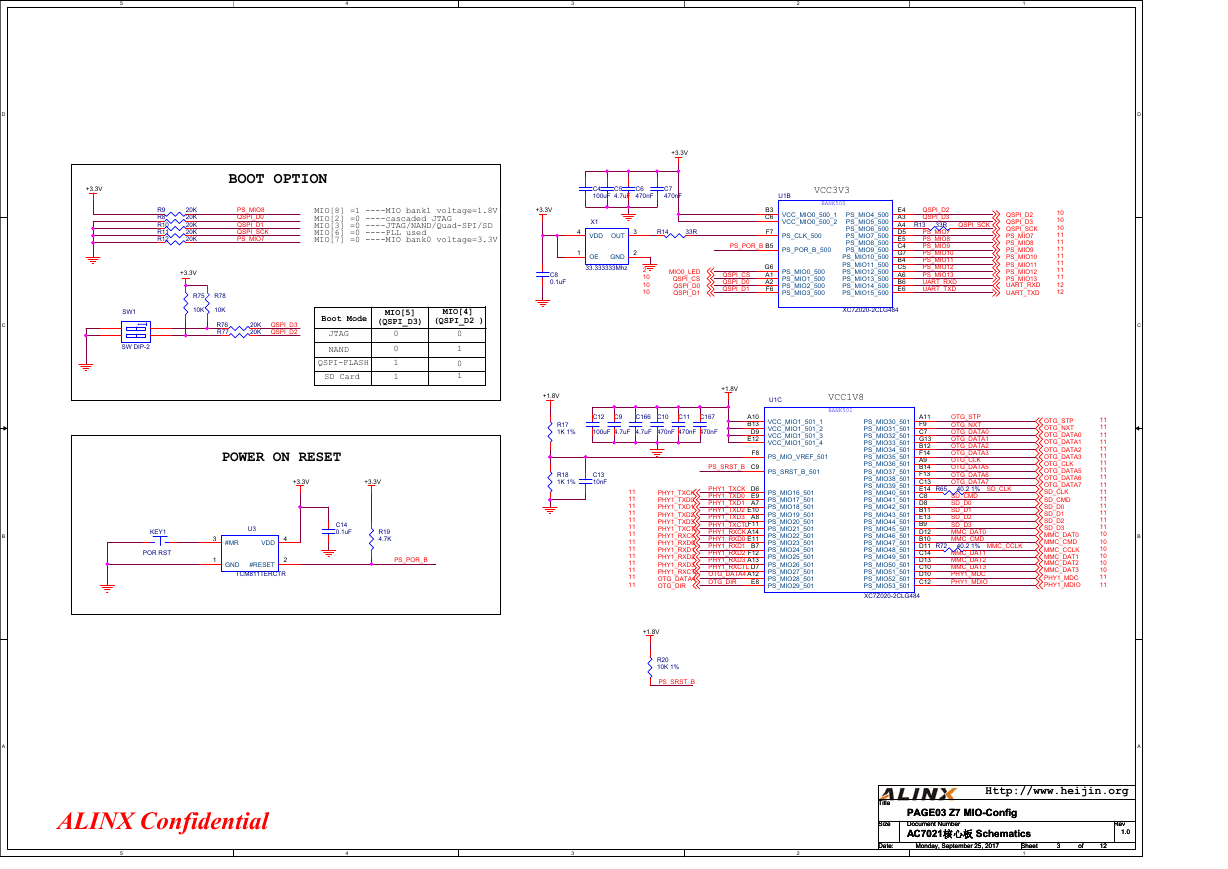

BOOT OPTION

+3.3V

C4

100uF

C5

4.7uF

C6

470nF

C7

470nF

PS_MIO8

QSPI_D0

QSPI_D1

QSPI_SCK

PS_MIO7

MIO[8] =1 ----MIO bank1 voltage=1.8V

MIO[2] =0 ----cascaded JTAG

MIO[3] =0 ----JTAG/NAND/Quad-SPI/SD

MIO[6] =0 ----PLL used

MIO[7] =0 ----MIO bank0 voltage=3.3V

R9

R8

R10

R11

R12

20K

20K

20K

20K

20K

+3.3V

+3.3V

C8

0.1uF

4

1

X1

VDD

OUT

OE

GND

33.333333Mhz

3

2

R14

33R

B3

C6

F7

PS_POR_B

B5

U1B

VCC3V3

BANK500

VCC_MIO0_500_1

VCC_MIO0_500_2

PS_CLK_500

PS_POR_B_500

2

10

10

10

MIO0_LED

QSPI_CS

QSPI_D0

QSPI_D1

QSPI_CS

QSPI_D0

QSPI_D1

G6

A1

A2

F6

PS_MIO0_500

PS_MIO1_500

PS_MIO2_500

PS_MIO3_500

PS_MIO4_500

PS_MIO5_500

PS_MIO6_500

PS_MIO7_500

PS_MIO8_500

PS_MIO9_500

PS_MIO10_500

PS_MIO11_500

PS_MIO12_500

PS_MIO13_500

PS_MIO14_500

PS_MIO15_500

QSPI_SCK

E4

A3

A4

D5

E5

C4

G7

B4

C5

A6

B6

E6

R13

QSPI_D2

QSPI_D3

33R

PS_MIO7

PS_MIO8

PS_MIO9

PS_MIO10

PS_MIO11

PS_MIO12

PS_MIO13

UART_RXD

UART_TXD

QSPI_D2

QSPI_D3

QSPI_SCK

PS_MIO7

PS_MIO8

PS_MIO9

PS_MIO10

PS_MIO11

PS_MIO12

PS_MIO13

UART_RXD

UART_TXD

10

10

10

11

11

11

11

11

11

11

12

12

R75

10K

R78

10K

R76

R77

20K

20K

QSPI_D3

QSPI_D2

SW1

SW DIP-2

Boot Mode

JTAG

NAND

QSPI-FLASH

SD Card

MIO[5]

(QSPI_D3)

0

0

1

1

POWER ON RESET

MIO[4]

(QSPI_D2 )

0

1

0

1

+3.3V

+3.3V

R18

1K 1%

C13

10nF

KEY1

POR RST

3

1

U3

#MR

VDD

GND

#RESET

4

2

TCM811TERCTR

C14

0.1uF

R19

4.7K

PS_POR_B

XC7Z020-2CLG484

VCC1V8

BANK501

A11

F9

C7

G13

B12

F14

A9

B14

F13

C13

E14

C8

D8

B11

E13

B9

D12

B10

D11

C14

D13

C10

D10

C12

PS_MIO30_501

PS_MIO31_501

PS_MIO32_501

PS_MIO33_501

PS_MIO34_501

PS_MIO35_501

PS_MIO36_501

PS_MIO37_501

PS_MIO38_501

PS_MIO39_501

PS_MIO40_501

PS_MIO41_501

PS_MIO42_501

PS_MIO43_501

PS_MIO44_501

PS_MIO45_501

PS_MIO46_501

PS_MIO47_501

PS_MIO48_501

PS_MIO49_501

PS_MIO50_501

PS_MIO51_501

PS_MIO52_501

PS_MIO53_501

XC7Z020-2CLG484

R65

R72

OTG_STP

OTG_NXT

OTG_DATA0

OTG_DATA1

OTG_DATA2

OTG_DATA3

OTG_CLK

OTG_DATA5

OTG_DATA6

OTG_DATA7

40.2 1%

SD_CMD

SD_D0

SD_D1

SD_D2

SD_D3

MMC_DAT0

MMC_CMD

40.2 1%

MMC_DAT1

MMC_DAT2

MMC_DAT3

PHY1_MDC

PHY1_MDIO

SD_CLK

MMC_CCLK

OTG_STP

OTG_NXT

OTG_DATA0

OTG_DATA1

OTG_DATA2

OTG_DATA3

OTG_CLK

OTG_DATA5

OTG_DATA6

OTG_DATA7

SD_CLK

SD_CMD

SD_D0

SD_D1

SD_D2

SD_D3

MMC_DAT0

MMC_CMD

MMC_CCLK

MMC_DAT1

MMC_DAT2

MMC_DAT3

PHY1_MDC

PHY1_MDIO

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

10

10

10

10

10

10

11

11

VCC_MIO1_501_1

VCC_MIO1_501_2

VCC_MIO1_501_3

VCC_MIO1_501_4

PS_MIO_VREF_501

PS_SRST_B_501

PS_MIO16_501

PS_MIO17_501

PS_MIO18_501

PS_MIO19_501

PS_MIO20_501

PS_MIO21_501

PS_MIO22_501

PS_MIO23_501

PS_MIO24_501

PS_MIO25_501

PS_MIO26_501

PS_MIO27_501

PS_MIO28_501

PS_MIO29_501

+1.8V

+1.8V

U1C

R17

1K 1%

C12

C9

C166

C10

C11

C167

100uF

4.7uF

4.7uF

470nF

470nF

470nF

A10

B13

D9

E12

F8

PS_SRST_B

C9

PHY1_TXCK

PHY1_TXD0

PHY1_TXD1

PHY1_TXD2

PHY1_TXD3

PHY1_TXCTL

PHY1_RXCK

PHY1_RXD0

PHY1_RXD1

PHY1_RXD2

PHY1_RXD3

PHY1_RXCTL

OTG_DATA4

OTG_DIR

D6

E9

A7

E10

A8

F11

A14

E11

B7

F12

A13

D7

A12

E8

11

11

11

11

11

11

11

11

11

11

11

11

11

11

PHY1_TXCK

PHY1_TXD0

PHY1_TXD1

PHY1_TXD2

PHY1_TXD3

PHY1_TXCTL

PHY1_RXCK

PHY1_RXD0

PHY1_RXD1

PHY1_RXD2

PHY1_RXD3

PHY1_RXCTL

OTG_DATA4

OTG_DIR

+1.8V

R20

10K 1%

PS_SRST_B

D

C

B

A

ALINX Confidential

5

4

3

2

Http://www.heijin.org

Title

Title

Title

Size

Size

Size

Date:

Date:

Date:

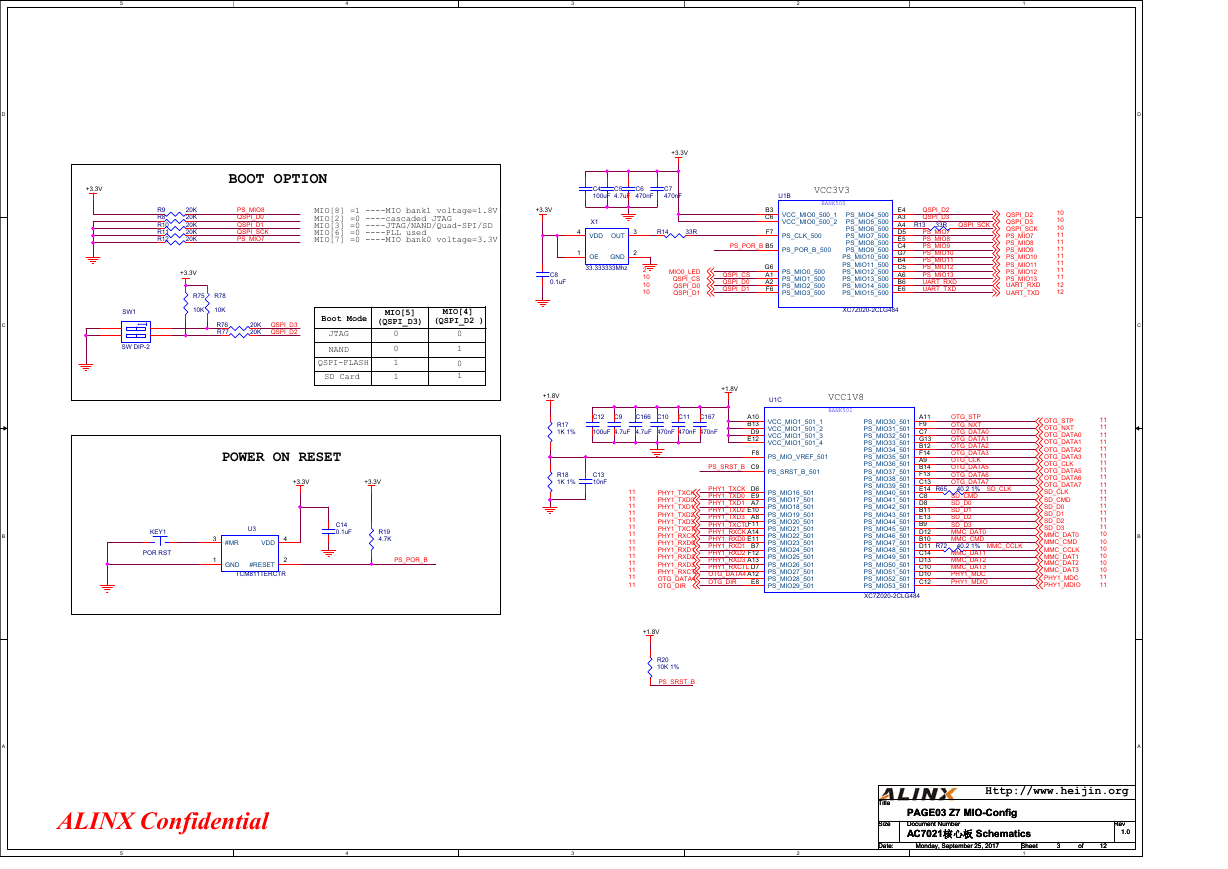

PAGE03 Z7 MIO-Config

PAGE03 Z7 MIO-Config

PAGE03 Z7 MIO-Config

Document Number

Document Number

Document Number

AC7021核心板 Schematics

AC7021核心板 Schematics

AC7021核心板 Schematics

Sheet

Sheet

Sheet

1

Monday, September 25, 2017

Monday, September 25, 2017

Monday, September 25, 2017

Rev

Rev

Rev

1.0

1.0

1.0

3

3

3

of

of

of

12

12

12

�

5

4

3

2

1

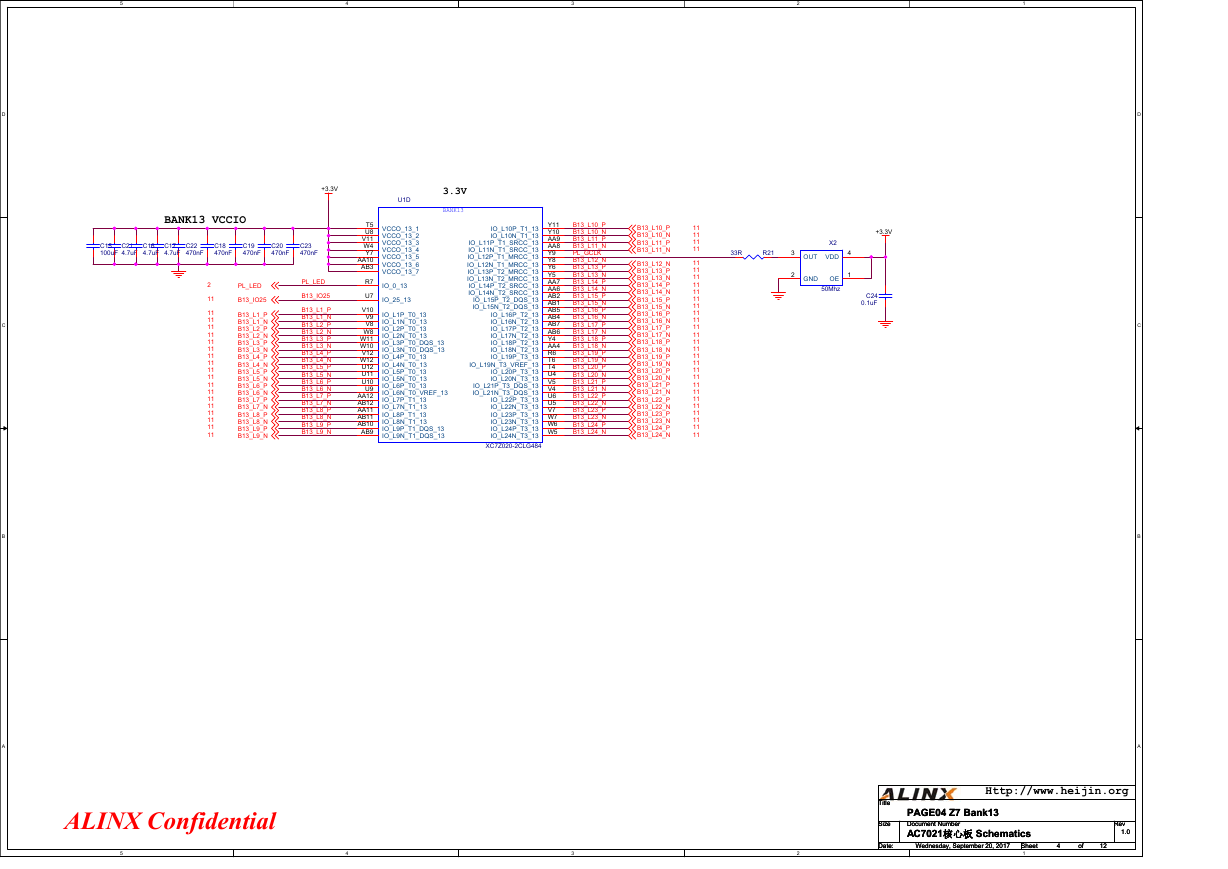

+3.3V

BANK13 VCCIO

C15

100uF

C21

4.7uF

C16

4.7uF

C17

4.7uF

C22

470nF

C18

470nF

C19

470nF

C20

470nF

C23

470nF

2

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

PL_LED

B13_IO25

B13_L1_P

B13_L1_N

B13_L2_P

B13_L2_N

B13_L3_P

B13_L3_N

B13_L4_P

B13_L4_N

B13_L5_P

B13_L5_N

B13_L6_P

B13_L6_N

B13_L7_P

B13_L7_N

B13_L8_P

B13_L8_N

B13_L9_P

B13_L9_N

PL_LED

B13_IO25

B13_L1_P

B13_L1_N

B13_L2_P

B13_L2_N

B13_L3_P

B13_L3_N

B13_L4_P

B13_L4_N

B13_L5_P

B13_L5_N

B13_L6_P

B13_L6_N

B13_L7_P

B13_L7_N

B13_L8_P

B13_L8_N

B13_L9_P

B13_L9_N

3.3V

BANK13

U1D

VCCO_13_1

VCCO_13_2

VCCO_13_3

VCCO_13_4

VCCO_13_5

VCCO_13_6

VCCO_13_7

IO_0_13

IO_25_13

IO_L1P_T0_13

IO_L1N_T0_13

IO_L2P_T0_13

IO_L2N_T0_13

IO_L3P_T0_DQS_13

IO_L3N_T0_DQS_13

IO_L4P_T0_13

IO_L4N_T0_13

IO_L5P_T0_13

IO_L5N_T0_13

IO_L6P_T0_13

IO_L6N_T0_VREF_13

IO_L7P_T1_13

IO_L7N_T1_13

IO_L8P_T1_13

IO_L8N_T1_13

IO_L9P_T1_DQS_13

IO_L9N_T1_DQS_13

T5

U8

V11

W4

Y7

AA10

AB3

R7

U7

V10

V9

V8

W8

W11

W10

V12

W12

U12

U11

U10

U9

AA12

AB12

AA11

AB11

AB10

AB9

IO_L10P_T1_13

IO_L10N_T1_13

IO_L11P_T1_SRCC_13

IO_L11N_T1_SRCC_13

IO_L12P_T1_MRCC_13

IO_L12N_T1_MRCC_13

IO_L13P_T2_MRCC_13

IO_L13N_T2_MRCC_13

IO_L14P_T2_SRCC_13

IO_L14N_T2_SRCC_13

IO_L15P_T2_DQS_13

IO_L15N_T2_DQS_13

IO_L16P_T2_13

IO_L16N_T2_13

IO_L17P_T2_13

IO_L17N_T2_13

IO_L18P_T2_13

IO_L18N_T2_13

IO_L19P_T3_13

IO_L19N_T3_VREF_13

IO_L20P_T3_13

IO_L20N_T3_13

IO_L21P_T3_DQS_13

IO_L21N_T3_DQS_13

IO_L22P_T3_13

IO_L22N_T3_13

IO_L23P_T3_13

IO_L23N_T3_13

IO_L24P_T3_13

IO_L24N_T3_13

XC7Z020-2CLG484

Y11

Y10

AA9

AA8

Y9

Y8

Y6

Y5

AA7

AA6

AB2

AB1

AB5

AB4

AB7

AB6

Y4

AA4

R6

T6

T4

U4

V5

V4

U6

U5

V7

W7

W6

W5

B13_L10_P

B13_L10_N

B13_L11_P

B13_L11_N

PL_GCLK

B13_L12_N

B13_L13_P

B13_L13_N

B13_L14_P

B13_L14_N

B13_L15_P

B13_L15_N

B13_L16_P

B13_L16_N

B13_L17_P

B13_L17_N

B13_L18_P

B13_L18_N

B13_L19_P

B13_L19_N

B13_L20_P

B13_L20_N

B13_L21_P

B13_L21_N

B13_L22_P

B13_L22_N

B13_L23_P

B13_L23_N

B13_L24_P

B13_L24_N

B13_L10_P

B13_L10_N

B13_L11_P

B13_L11_N

B13_L12_N

B13_L13_P

B13_L13_N

B13_L14_P

B13_L14_N

B13_L15_P

B13_L15_N

B13_L16_P

B13_L16_N

B13_L17_P

B13_L17_N

B13_L18_P

B13_L18_N

B13_L19_P

B13_L19_N

B13_L20_P

B13_L20_N

B13_L21_P

B13_L21_N

B13_L22_P

B13_L22_N

B13_L23_P

B13_L23_N

B13_L24_P

B13_L24_N

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

33R

R21

3

2

X2

OUT

VDD

GND

OE

50Mhz

4

1

+3.3V

C24

0.1uF

D

C

B

A

D

C

B

A

ALINX Confidential

5

4

3

2

Http://www.heijin.org

Title

Title

Title

Size

Size

Size

Date:

Date:

Date:

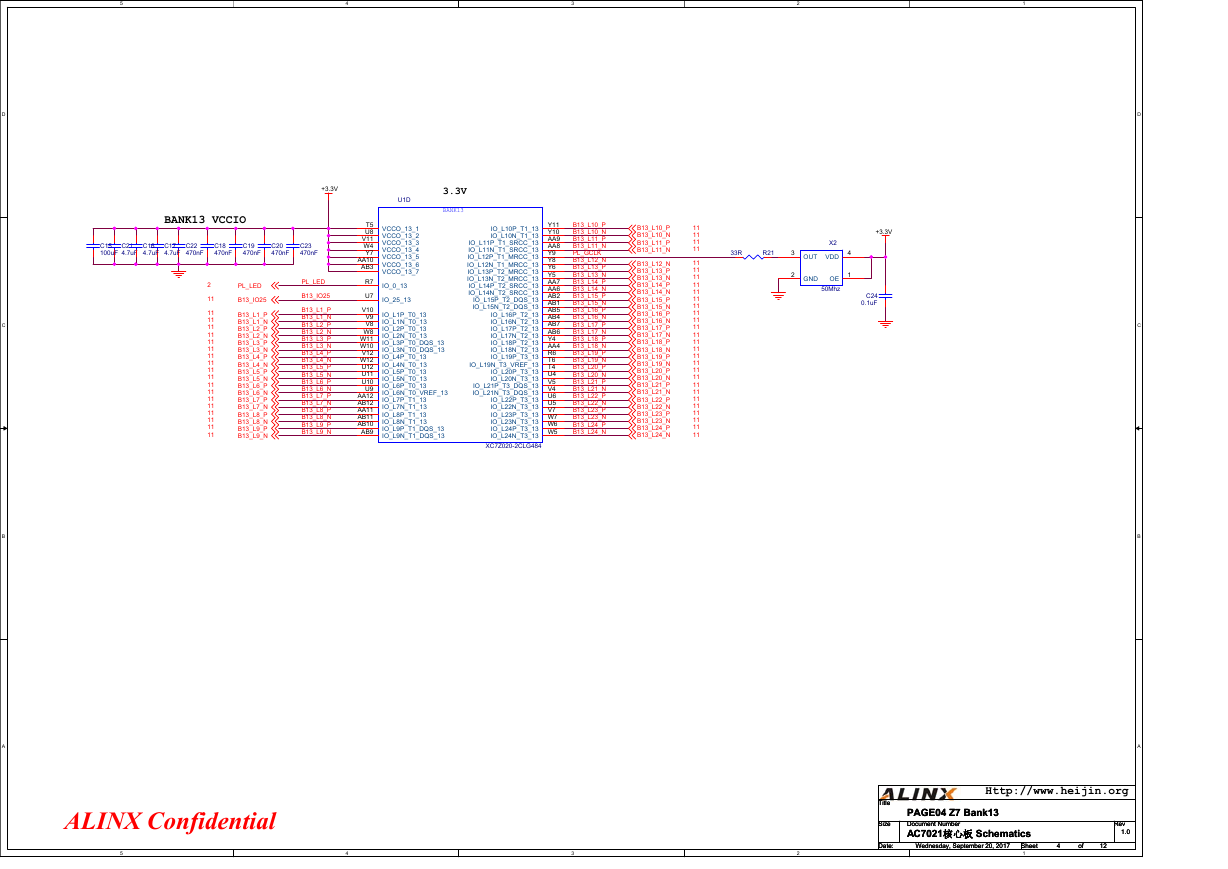

PAGE04 Z7 Bank13

PAGE04 Z7 Bank13

PAGE04 Z7 Bank13

Document Number

Document Number

Document Number

AC7021核心板 Schematics

AC7021核心板 Schematics

AC7021核心板 Schematics

Sheet

Sheet

Sheet

1

Wednesday, September 20, 2017

Wednesday, September 20, 2017

Wednesday, September 20, 2017

Rev

Rev

Rev

1.0

1.0

1.0

4

4

4

of

of

of

12

12

12

�

5

4

3

2

1

D

C

B

A

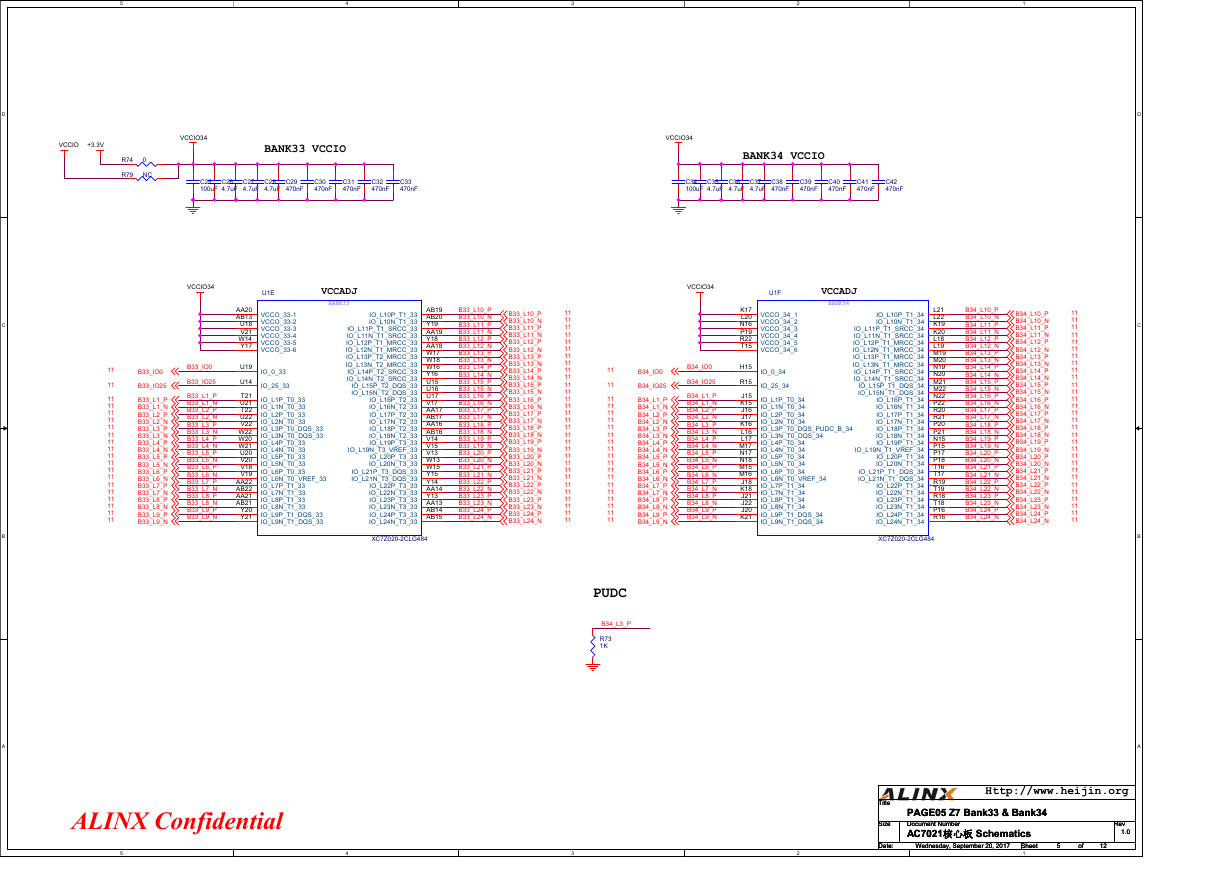

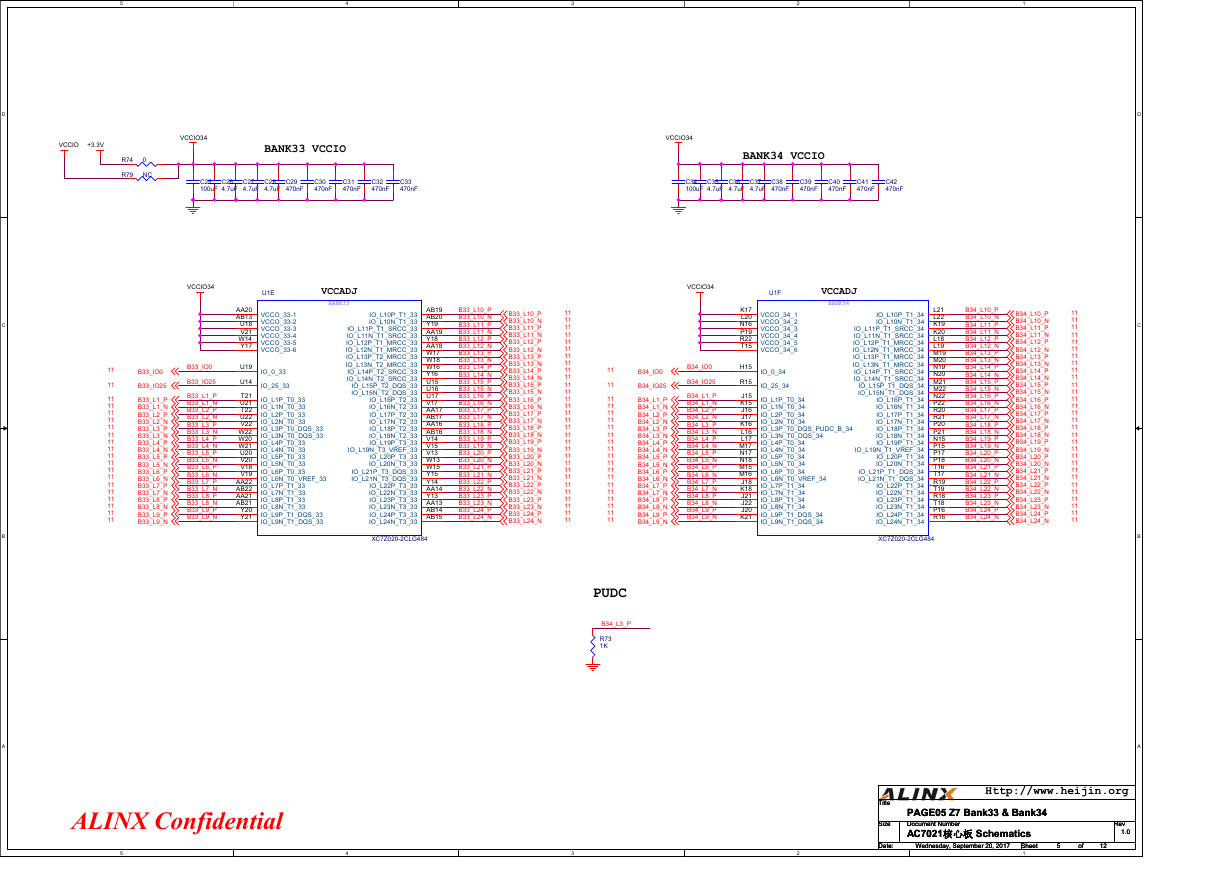

VCCIO +3.3V

VCCIO34

BANK33 VCCIO

R74

R79

0

NC

VCCIO34

BANK34 VCCIO

C25

100uF

C26

4.7uF

C27

4.7uF

C28

4.7uF

C29

470nF

C30

470nF

C31

470nF

C32

470nF

C33

470nF

C34

100uF

C35

4.7uF

C36

4.7uF

C37

4.7uF

C38

470nF

C39

470nF

C40

470nF

C41

470nF

C42

470nF

VCCADJ

BANK33

VCCIO34

B33_IO0

B33_IO25

B33_L1_P

B33_L1_N

B33_L2_P

B33_L2_N

B33_L3_P

B33_L3_N

B33_L4_P

B33_L4_N

B33_L5_P

B33_L5_N

B33_L6_P

B33_L6_N

B33_L7_P

B33_L7_N

B33_L8_P

B33_L8_N

B33_L9_P

B33_L9_N

AA20

AB13

U18

V21

W14

Y17

U19

U14

T21

U21

T22

U22

V22

W22

W20

W21

U20

V20

V18

V19

AA22

AB22

AA21

AB21

Y20

Y21

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

B33_IO0

B33_IO25

B33_L1_P

B33_L1_N

B33_L2_P

B33_L2_N

B33_L3_P

B33_L3_N

B33_L4_P

B33_L4_N

B33_L5_P

B33_L5_N

B33_L6_P

B33_L6_N

B33_L7_P

B33_L7_N

B33_L8_P

B33_L8_N

B33_L9_P

B33_L9_N

U1E

VCCO_33-1

VCCO_33-2

VCCO_33-3

VCCO_33-4

VCCO_33-5

VCCO_33-6

IO_0_33

IO_25_33

IO_L1P_T0_33

IO_L1N_T0_33

IO_L2P_T0_33

IO_L2N_T0_33

IO_L3P_T0_DQS_33

IO_L3N_T0_DQS_33

IO_L4P_T0_33

IO_L4N_T0_33

IO_L5P_T0_33

IO_L5N_T0_33

IO_L6P_T0_33

IO_L6N_T0_VREF_33

IO_L7P_T1_33

IO_L7N_T1_33

IO_L8P_T1_33

IO_L8N_T1_33

IO_L9P_T1_DQS_33

IO_L9N_T1_DQS_33

AB19

AB20

Y19

AA19

Y18

AA18

W17

W18

W16

Y16

U15

U16

U17

V17

AA17

AB17

AA16

AB16

V14

V15

V13

W13

W15

Y15

Y14

AA14

Y13

AA13

AB14

AB15

B33_L10_P

B33_L10_N

B33_L11_P

B33_L11_N

B33_L12_P

B33_L12_N

B33_L13_P

B33_L13_N

B33_L14_P

B33_L14_N

B33_L15_P

B33_L15_N

B33_L16_P

B33_L16_N

B33_L17_P

B33_L17_N

B33_L18_P

B33_L18_N

B33_L19_P

B33_L19_N

B33_L20_P

B33_L20_N

B33_L21_P

B33_L21_N

B33_L22_P

B33_L22_N

B33_L23_P

B33_L23_N

B33_L24_P

B33_L24_N

B33_L10_P

B33_L10_N

B33_L11_P

B33_L11_N

B33_L12_P

B33_L12_N

B33_L13_P

B33_L13_N

B33_L14_P

B33_L14_N

B33_L15_P

B33_L15_N

B33_L16_P

B33_L16_N

B33_L17_P

B33_L17_N

B33_L18_P

B33_L18_N

B33_L19_P

B33_L19_N

B33_L20_P

B33_L20_N

B33_L21_P

B33_L21_N

B33_L22_P

B33_L22_N

B33_L23_P

B33_L23_N

B33_L24_P

B33_L24_N

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

VCCIO34

B34_IO0

B34_IO25

B34_L1_P

B34_L1_N

B34_L2_P

B34_L2_N

B34_L3_P

B34_L3_N

B34_L4_P

B34_L4_N

B34_L5_P

B34_L5_N

B34_L6_P

B34_L6_N

B34_L7_P

B34_L7_N

B34_L8_P

B34_L8_N

B34_L9_P

B34_L9_N

K17

L20

N16

P19

R22

T15

H15

R15

J15

K15

J16

J17

K16

L16

L17

M17

N17

N18

M15

M16

J18

K18

J21

J22

J20

K21

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

B34_IO0

B34_IO25

B34_L1_P

B34_L1_N

B34_L2_P

B34_L2_N

B34_L3_P

B34_L3_N

B34_L4_P

B34_L4_N

B34_L5_P

B34_L5_N

B34_L6_P

B34_L6_N

B34_L7_P

B34_L7_N

B34_L8_P

B34_L8_N

B34_L9_P

B34_L9_N

IO_L10P_T1_33

IO_L10N_T1_33

IO_L11P_T1_SRCC_33

IO_L11N_T1_SRCC_33

IO_L12P_T1_MRCC_33

IO_L12N_T1_MRCC_33

IO_L13P_T2_MRCC_33

IO_L13N_T2_MRCC_33

IO_L14P_T2_SRCC_33

IO_L14N_T2_SRCC_33

IO_L15P_T2_DQS_33

IO_L15N_T2_DQS_33

IO_L16P_T2_33

IO_L16N_T2_33

IO_L17P_T2_33

IO_L17N_T2_33

IO_L18P_T2_33

IO_L18N_T2_33

IO_L19P_T3_33

IO_L19N_T3_VREF_33

IO_L20P_T3_33

IO_L20N_T3_33

IO_L21P_T3_DQS_33

IO_L21N_T3_DQS_33

IO_L22P_T3_33

IO_L22N_T3_33

IO_L23P_T3_33

IO_L23N_T3_33

IO_L24P_T3_33

IO_L24N_T3_33

VCCADJ

BANK34

U1F

VCCO_34_1

VCCO_34_2

VCCO_34_3

VCCO_34_4

VCCO_34_5

VCCO_34_6

IO_0_34

IO_25_34

IO_L10P_T1_34

IO_L10N_T1_34

IO_L11P_T1_SRCC_34

IO_L11N_T1_SRCC_34

IO_L12P_T1_MRCC_34

IO_L12N_T1_MRCC_34

IO_L13P_T1_MRCC_34

IO_L13N_T1_MRCC_34

IO_L14P_T1_SRCC_34

IO_L14N_T1_SRCC_34

IO_L15P_T1_DQS_34

IO_L15N_T1_DQS_34

IO_L16P_T1_34

IO_L16N_T1_34

IO_L17P_T1_34

IO_L17N_T1_34

IO_L18P_T1_34

IO_L18N_T1_34

IO_L19P_T1_34

IO_L19N_T1_VREF_34

IO_L20P_T1_34

IO_L20N_T1_34

IO_L21P_T1_DQS_34

IO_L21N_T1_DQS_34

IO_L22P_T1_34

IO_L22N_T1_34

IO_L23P_T1_34

IO_L23N_T1_34

IO_L24P_T1_34

IO_L24N_T1_34

L21

L22

K19

K20

L18

L19

M19

M20

N19

N20

M21

M22

N22

P22

R20

R21

P20

P21

N15

P15

P17

P18

T16

T17

R19

T19

R18

T18

P16

R16

B34_L10_P

B34_L10_N

B34_L11_P

B34_L11_N

B34_L12_P

B34_L12_N

B34_L13_P

B34_L13_N

B34_L14_P

B34_L14_N

B34_L15_P

B34_L15_N

B34_L16_P

B34_L16_N

B34_L17_P

B34_L17_N

B34_L18_P

B34_L18_N

B34_L19_P

B34_L19_N

B34_L20_P

B34_L20_N

B34_L21_P

B34_L21_N

B34_L22_P

B34_L22_N

B34_L23_P

B34_L23_N

B34_L24_P

B34_L24_N

B34_L10_P

B34_L10_N

B34_L11_P

B34_L11_N

B34_L12_P

B34_L12_N

B34_L13_P

B34_L13_N

B34_L14_P

B34_L14_N

B34_L15_P

B34_L15_N

B34_L16_P

B34_L16_N

B34_L17_P

B34_L17_N

B34_L18_P

B34_L18_N

B34_L19_P

B34_L19_N

B34_L20_P

B34_L20_N

B34_L21_P

B34_L21_N

B34_L22_P

B34_L22_N

B34_L23_P

B34_L23_N

B34_L24_P

B34_L24_N

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

IO_L1P_T0_34

IO_L1N_T0_34

IO_L2P_T0_34

IO_L2N_T0_34

IO_L3P_T0_DQS_PUDC_B_34

IO_L3N_T0_DQS_34

IO_L4P_T0_34

IO_L4N_T0_34

IO_L5P_T0_34

IO_L5N_T0_34

IO_L6P_T0_34

IO_L6N_T0_VREF_34

IO_L7P_T1_34

IO_L7N_T1_34

IO_L8P_T1_34

IO_L8N_T1_34

IO_L9P_T1_DQS_34

IO_L9N_T1_DQS_34

XC7Z020-2CLG484

XC7Z020-2CLG484

PUDC

B34_L3_P

R73

1K

ALINX Confidential

5

4

3

2

Http://www.heijin.org

Title

Title

Title

Size

Size

Size

Date:

Date:

Date:

PAGE05 Z7 Bank33 & Bank34

PAGE05 Z7 Bank33 & Bank34

PAGE05 Z7 Bank33 & Bank34

Document Number

Document Number

Document Number

AC7021核心板 Schematics

AC7021核心板 Schematics

AC7021核心板 Schematics

Sheet

Sheet

Sheet

1

Wednesday, September 20, 2017

Wednesday, September 20, 2017

Wednesday, September 20, 2017

Rev

Rev

Rev

1.0

1.0

1.0

5

5

5

of

of

of

12

12

12

D

C

B

A

�

5

4

3

2

1

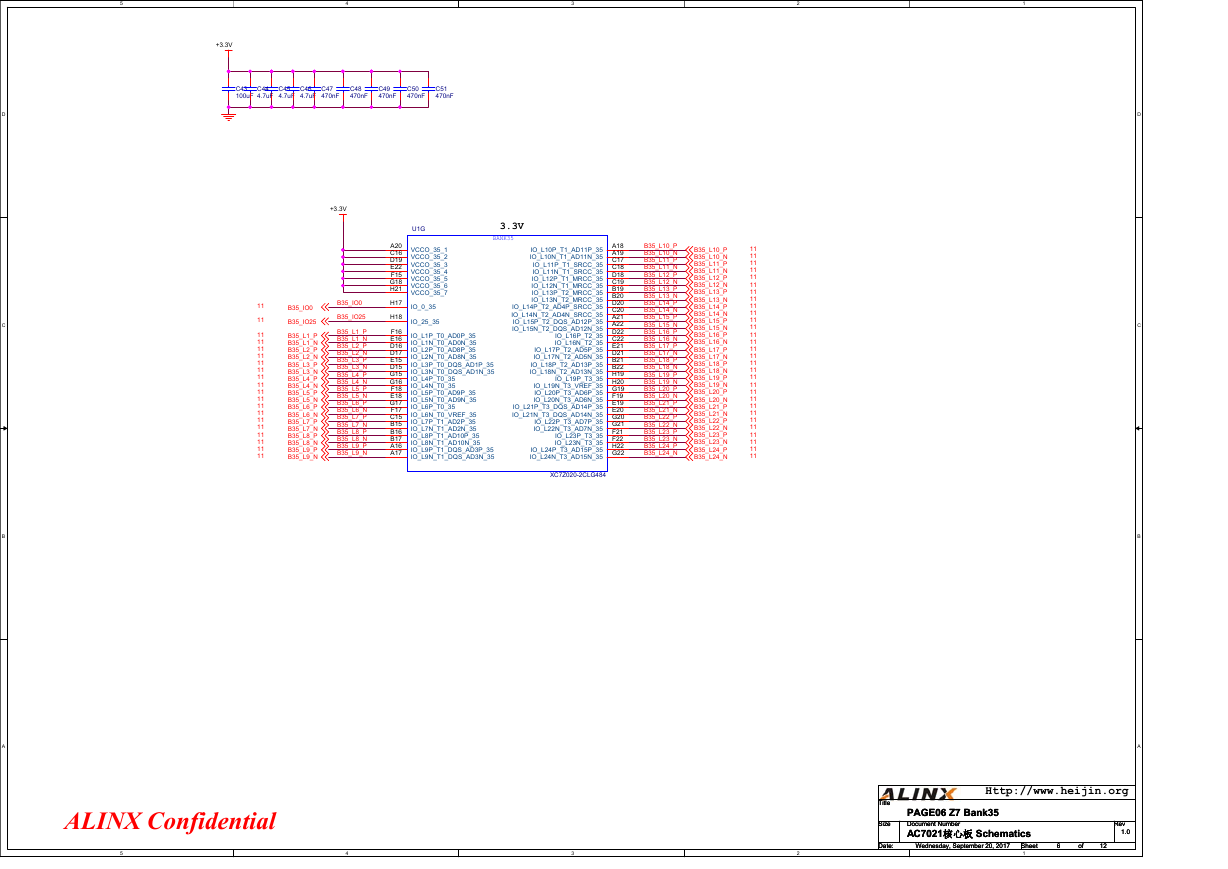

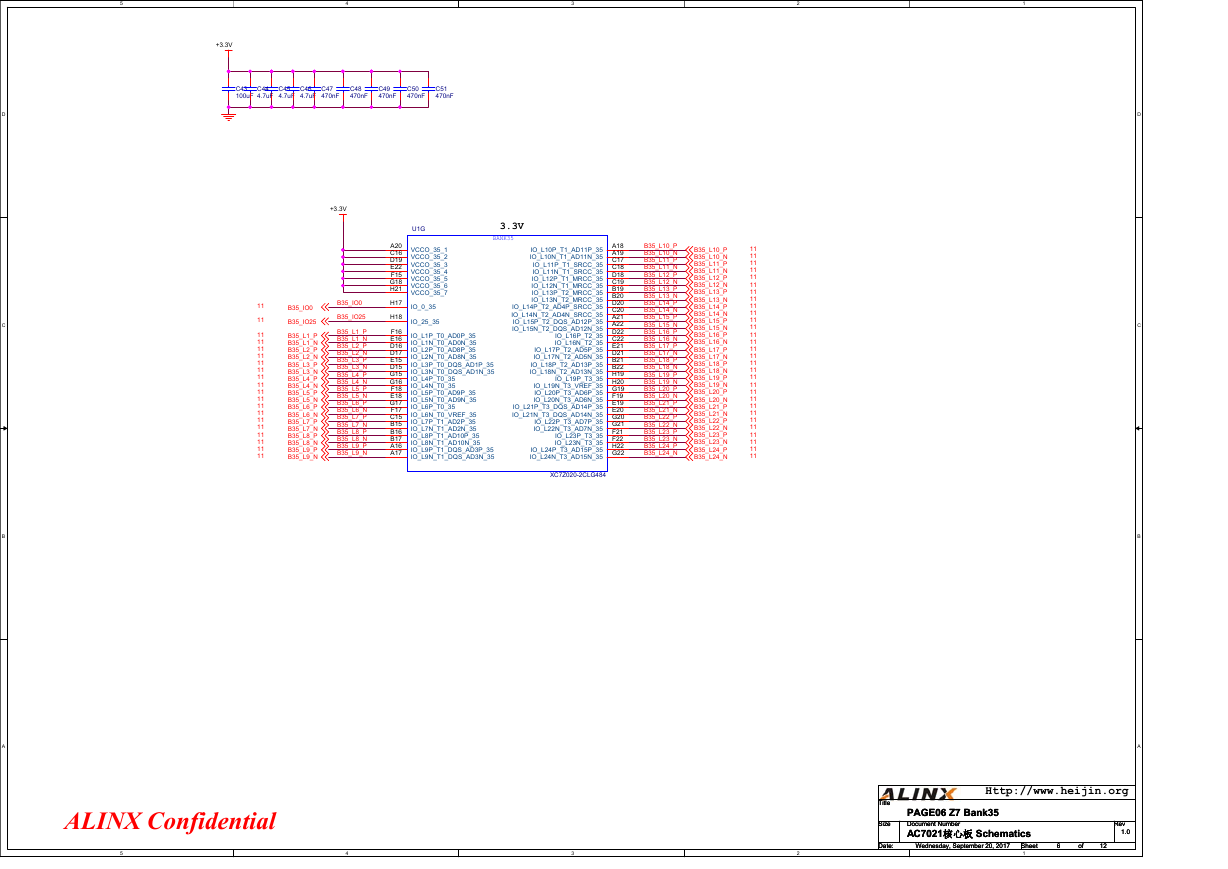

+3.3V

C43

100uF

C44

4.7uF

C45

4.7uF

C46

4.7uF

C47

470nF

C48

470nF

C49

470nF

C50

470nF

C51

470nF

+3.3V

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

B35_IO0

B35_IO25

B35_L1_P

B35_L1_N

B35_L2_P

B35_L2_N

B35_L3_P

B35_L3_N

B35_L4_P

B35_L4_N

B35_L5_P

B35_L5_N

B35_L6_P

B35_L6_N

B35_L7_P

B35_L7_N

B35_L8_P

B35_L8_N

B35_L9_P

B35_L9_N

B35_IO0

B35_IO25

B35_L1_P

B35_L1_N

B35_L2_P

B35_L2_N

B35_L3_P

B35_L3_N

B35_L4_P

B35_L4_N

B35_L5_P

B35_L5_N

B35_L6_P

B35_L6_N

B35_L7_P

B35_L7_N

B35_L8_P

B35_L8_N

B35_L9_P

B35_L9_N

A20

C16

D19

E22

F15

G18

H21

H17

H18

F16

E16

D16

D17

E15

D15

G15

G16

F18

E18

G17

F17

C15

B15

B16

B17

A16

A17

D

C

B

A

U1G

VCCO_35_1

VCCO_35_2

VCCO_35_3

VCCO_35_4

VCCO_35_5

VCCO_35_6

VCCO_35_7

IO_0_35

IO_25_35

IO_L1P_T0_AD0P_35

IO_L1N_T0_AD0N_35

IO_L2P_T0_AD8P_35

IO_L2N_T0_AD8N_35

IO_L3P_T0_DQS_AD1P_35

IO_L3N_T0_DQS_AD1N_35

IO_L4P_T0_35

IO_L4N_T0_35

IO_L5P_T0_AD9P_35

IO_L5N_T0_AD9N_35

IO_L6P_T0_35

IO_L6N_T0_VREF_35

IO_L7P_T1_AD2P_35

IO_L7N_T1_AD2N_35

IO_L8P_T1_AD10P_35

IO_L8N_T1_AD10N_35

IO_L9P_T1_DQS_AD3P_35

IO_L9N_T1_DQS_AD3N_35

3.3V

BANK35

IO_L10P_T1_AD11P_35

IO_L10N_T1_AD11N_35

IO_L11P_T1_SRCC_35

IO_L11N_T1_SRCC_35

IO_L12P_T1_MRCC_35

IO_L12N_T1_MRCC_35

IO_L13P_T2_MRCC_35

IO_L13N_T2_MRCC_35

IO_L14P_T2_AD4P_SRCC_35

IO_L14N_T2_AD4N_SRCC_35

IO_L15P_T2_DQS_AD12P_35

IO_L15N_T2_DQS_AD12N_35

IO_L16P_T2_35

IO_L16N_T2_35

IO_L17P_T2_AD5P_35

IO_L17N_T2_AD5N_35

IO_L18P_T2_AD13P_35

IO_L18N_T2_AD13N_35

IO_L19P_T3_35

IO_L19N_T3_VREF_35

IO_L20P_T3_AD6P_35

IO_L20N_T3_AD6N_35

IO_L21P_T3_DQS_AD14P_35

IO_L21N_T3_DQS_AD14N_35

IO_L22P_T3_AD7P_35

IO_L22N_T3_AD7N_35

IO_L23P_T3_35

IO_L23N_T3_35

IO_L24P_T3_AD15P_35

IO_L24N_T3_AD15N_35

XC7Z020-2CLG484

A18

A19

C17

C18

D18

C19

B19

B20

D20

C20

A21

A22

D22

C22

E21

D21

B21

B22

H19

H20

G19

F19

E19

E20

G20

G21

F21

F22

H22

G22

B35_L10_P

B35_L10_N

B35_L11_P

B35_L11_N

B35_L12_P

B35_L12_N

B35_L13_P

B35_L13_N

B35_L14_P

B35_L14_N

B35_L15_P

B35_L15_N

B35_L16_P

B35_L16_N

B35_L17_P

B35_L17_N

B35_L18_P

B35_L18_N

B35_L19_P

B35_L19_N

B35_L20_P

B35_L20_N

B35_L21_P

B35_L21_N

B35_L22_P

B35_L22_N

B35_L23_P

B35_L23_N

B35_L24_P

B35_L24_N

B35_L10_P

B35_L10_N

B35_L11_P

B35_L11_N

B35_L12_P

B35_L12_N

B35_L13_P

B35_L13_N

B35_L14_P

B35_L14_N

B35_L15_P

B35_L15_N

B35_L16_P

B35_L16_N

B35_L17_P

B35_L17_N

B35_L18_P

B35_L18_N

B35_L19_P

B35_L19_N

B35_L20_P

B35_L20_N

B35_L21_P

B35_L21_N

B35_L22_P

B35_L22_N

B35_L23_P

B35_L23_N

B35_L24_P

B35_L24_N

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

D

C

B

A

ALINX Confidential

5

4

3

2

Http://www.heijin.org

Title

Title

Title

Size

Size

Size

Date:

Date:

Date:

PAGE06 Z7 Bank35

PAGE06 Z7 Bank35

PAGE06 Z7 Bank35

Document Number

Document Number

Document Number

AC7021核心板 Schematics

AC7021核心板 Schematics

AC7021核心板 Schematics

Sheet

Sheet

Sheet

1

Wednesday, September 20, 2017

Wednesday, September 20, 2017

Wednesday, September 20, 2017

Rev

Rev

Rev

1.0

1.0

1.0

6

6

6

of

of

of

12

12

12

�

D

C

B

A

5

4

3

2

1

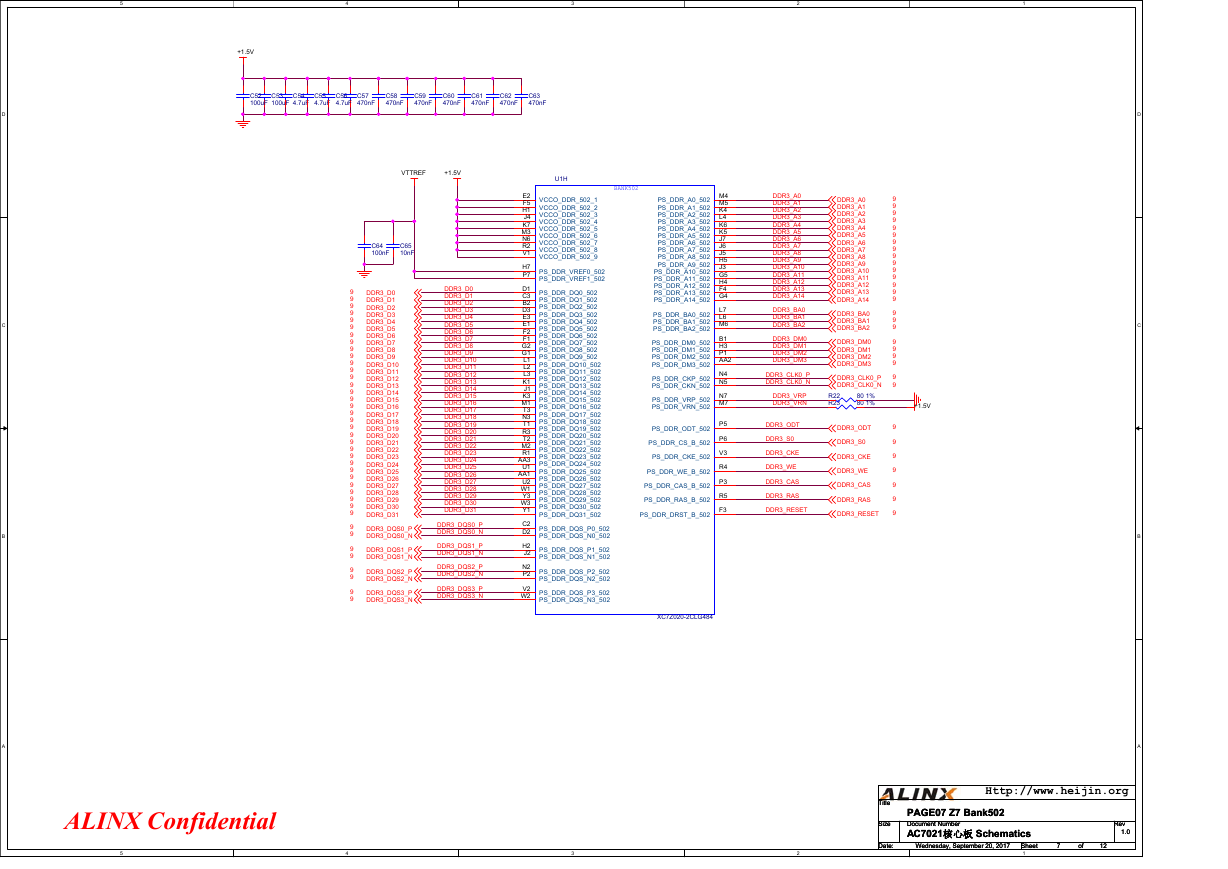

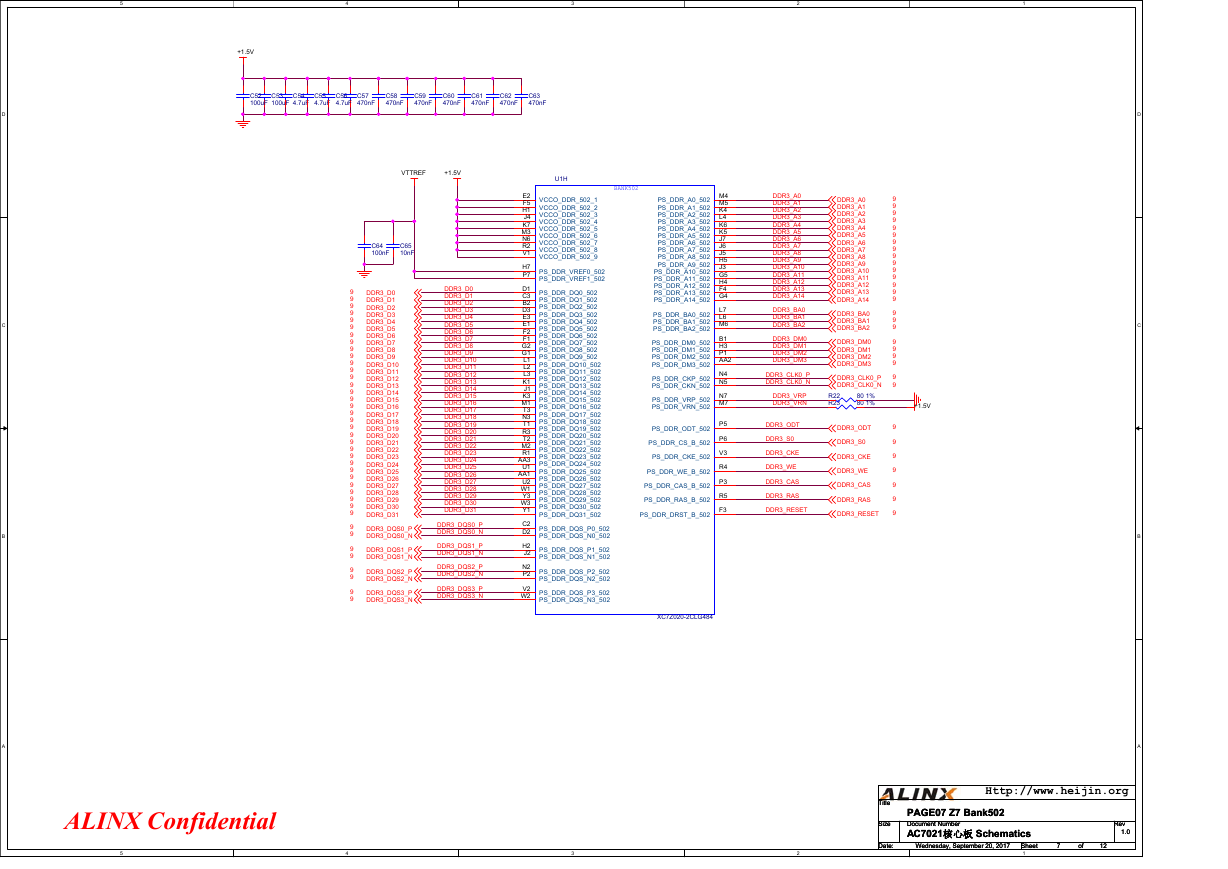

+1.5V

C52

100uF

C53

100uF

C54

4.7uF

C55

4.7uF

C56

4.7uF

C57

470nF

C58

470nF

C59

470nF

C60

470nF

C61

470nF

C62

470nF

C63

470nF

VTTREF

+1.5V

C64

100nF

C65

10nF

DDR3_D0

DDR3_D1

DDR3_D2

DDR3_D3

DDR3_D4

DDR3_D5

DDR3_D6

DDR3_D7

DDR3_D8

DDR3_D9

DDR3_D10

DDR3_D11

DDR3_D12

DDR3_D13

DDR3_D14

DDR3_D15

DDR3_D16

DDR3_D17

DDR3_D18

DDR3_D19

DDR3_D20

DDR3_D21

DDR3_D22

DDR3_D23

DDR3_D24

DDR3_D25

DDR3_D26

DDR3_D27

DDR3_D28

DDR3_D29

DDR3_D30

DDR3_D31

DDR3_D0

DDR3_D1

DDR3_D2

DDR3_D3

DDR3_D4

DDR3_D5

DDR3_D6

DDR3_D7

DDR3_D8

DDR3_D9

DDR3_D10

DDR3_D11

DDR3_D12

DDR3_D13

DDR3_D14

DDR3_D15

DDR3_D16

DDR3_D17

DDR3_D18

DDR3_D19

DDR3_D20

DDR3_D21

DDR3_D22

DDR3_D23

DDR3_D24

DDR3_D25

DDR3_D26

DDR3_D27

DDR3_D28

DDR3_D29

DDR3_D30

DDR3_D31

DDR3_DQS0_P

DDR3_DQS0_N

DDR3_DQS1_P

DDR3_DQS1_N

DDR3_DQS2_P

DDR3_DQS2_N

DDR3_DQS3_P

DDR3_DQS3_N

DDR3_DQS0_P

DDR3_DQS0_N

DDR3_DQS1_P

DDR3_DQS1_N

DDR3_DQS2_P

DDR3_DQS2_N

DDR3_DQS3_P

DDR3_DQS3_N

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

U1H

E2

VCCO_DDR_502_1

F5

VCCO_DDR_502_2

H1

VCCO_DDR_502_3

J4

VCCO_DDR_502_4

K7

VCCO_DDR_502_5

M3

VCCO_DDR_502_6

N6

VCCO_DDR_502_7

R2

V1 VCCO_DDR_502_8

VCCO_DDR_502_9

H7

P7

D1

C3

B2

D3

E3

E1

F2

F1

G2

G1

L1

L2

L3

K1

J1

K3

M1

T3

N3

T1

R3

T2

M2

R1

AA3

U1

AA1

U2

W1

Y3

W3

Y1

C2

D2

H2

J2

N2

P2

V2

W2

PS_DDR_VREF0_502

PS_DDR_VREF1_502

PS_DDR_DQ0_502

PS_DDR_DQ1_502

PS_DDR_DQ2_502

PS_DDR_DQ3_502

PS_DDR_DQ4_502

PS_DDR_DQ5_502

PS_DDR_DQ6_502

PS_DDR_DQ7_502

PS_DDR_DQ8_502

PS_DDR_DQ9_502

PS_DDR_DQ10_502

PS_DDR_DQ11_502

PS_DDR_DQ12_502

PS_DDR_DQ13_502

PS_DDR_DQ14_502

PS_DDR_DQ15_502

PS_DDR_DQ16_502

PS_DDR_DQ17_502

PS_DDR_DQ18_502

PS_DDR_DQ19_502

PS_DDR_DQ20_502

PS_DDR_DQ21_502

PS_DDR_DQ22_502

PS_DDR_DQ23_502

PS_DDR_DQ24_502

PS_DDR_DQ25_502

PS_DDR_DQ26_502

PS_DDR_DQ27_502

PS_DDR_DQ28_502

PS_DDR_DQ29_502

PS_DDR_DQ30_502

PS_DDR_DQ31_502

PS_DDR_DQS_P0_502

PS_DDR_DQS_N0_502

PS_DDR_DQS_P1_502

PS_DDR_DQS_N1_502

PS_DDR_DQS_P2_502

PS_DDR_DQS_N2_502

PS_DDR_DQS_P3_502

PS_DDR_DQS_N3_502

BANK502

PS_DDR_A0_502

PS_DDR_A1_502

PS_DDR_A2_502

PS_DDR_A3_502

PS_DDR_A4_502

PS_DDR_A5_502

PS_DDR_A6_502

PS_DDR_A7_502

PS_DDR_A8_502

PS_DDR_A9_502

PS_DDR_A10_502

PS_DDR_A11_502

PS_DDR_A12_502

PS_DDR_A13_502

PS_DDR_A14_502

PS_DDR_BA0_502

PS_DDR_BA1_502

PS_DDR_BA2_502

PS_DDR_DM0_502

PS_DDR_DM1_502

PS_DDR_DM2_502

PS_DDR_DM3_502

PS_DDR_CKP_502

PS_DDR_CKN_502

PS_DDR_VRP_502

PS_DDR_VRN_502

PS_DDR_ODT_502

PS_DDR_CS_B_502

PS_DDR_CKE_502

PS_DDR_WE_B_502

PS_DDR_CAS_B_502

PS_DDR_RAS_B_502

PS_DDR_DRST_B_502

M4

M5

K4

L4

K6

K5

J7

J6

J5

H5

J3

G5

H4

F4

G4

L7

L6

M6

B1

H3

P1

AA2

N4

N5

N7

M7

P5

P6

V3

R4

P3

R5

F3

XC7Z020-2CLG484

DDR3_A0

DDR3_A1

DDR3_A2

DDR3_A3

DDR3_A4

DDR3_A5

DDR3_A6

DDR3_A7

DDR3_A8

DDR3_A9

DDR3_A10

DDR3_A11

DDR3_A12

DDR3_A13

DDR3_A14

DDR3_BA0

DDR3_BA1

DDR3_BA2

DDR3_DM0

DDR3_DM1

DDR3_DM2

DDR3_DM3

DDR3_A0

DDR3_A1

DDR3_A2

DDR3_A3

DDR3_A4

DDR3_A5

DDR3_A6

DDR3_A7

DDR3_A8

DDR3_A9

DDR3_A10

DDR3_A11

DDR3_A12

DDR3_A13

DDR3_A14

DDR3_BA0

DDR3_BA1

DDR3_BA2

DDR3_DM0

DDR3_DM1

DDR3_DM2

DDR3_DM3

DDR3_CLK0_P

DDR3_CLK0_N

DDR3_CLK0_P

DDR3_CLK0_N

DDR3_VRP

DDR3_VRN

R22

R23

80 1%

80 1%

DDR3_ODT

DDR3_S0

DDR3_CKE

DDR3_WE

DDR3_CAS

DDR3_RAS

DDR3_ODT

DDR3_S0

DDR3_CKE

DDR3_WE

DDR3_CAS

DDR3_RAS

DDR3_RESET

DDR3_RESET

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

+1.5V

D

C

B

A

ALINX Confidential

5

4

3

2

Http://www.heijin.org

Title

Title

Title

Size

Size

Size

Date:

Date:

Date:

PAGE07 Z7 Bank502

PAGE07 Z7 Bank502

PAGE07 Z7 Bank502

Document Number

Document Number

Document Number

AC7021核心板 Schematics

AC7021核心板 Schematics

AC7021核心板 Schematics

Sheet

Sheet

Sheet

1

Wednesday, September 20, 2017

Wednesday, September 20, 2017

Wednesday, September 20, 2017

Rev

Rev

Rev

1.0

1.0

1.0

7

7

7

of

of

of

12

12

12

�

5

4

3

2

1

D

C

B

A

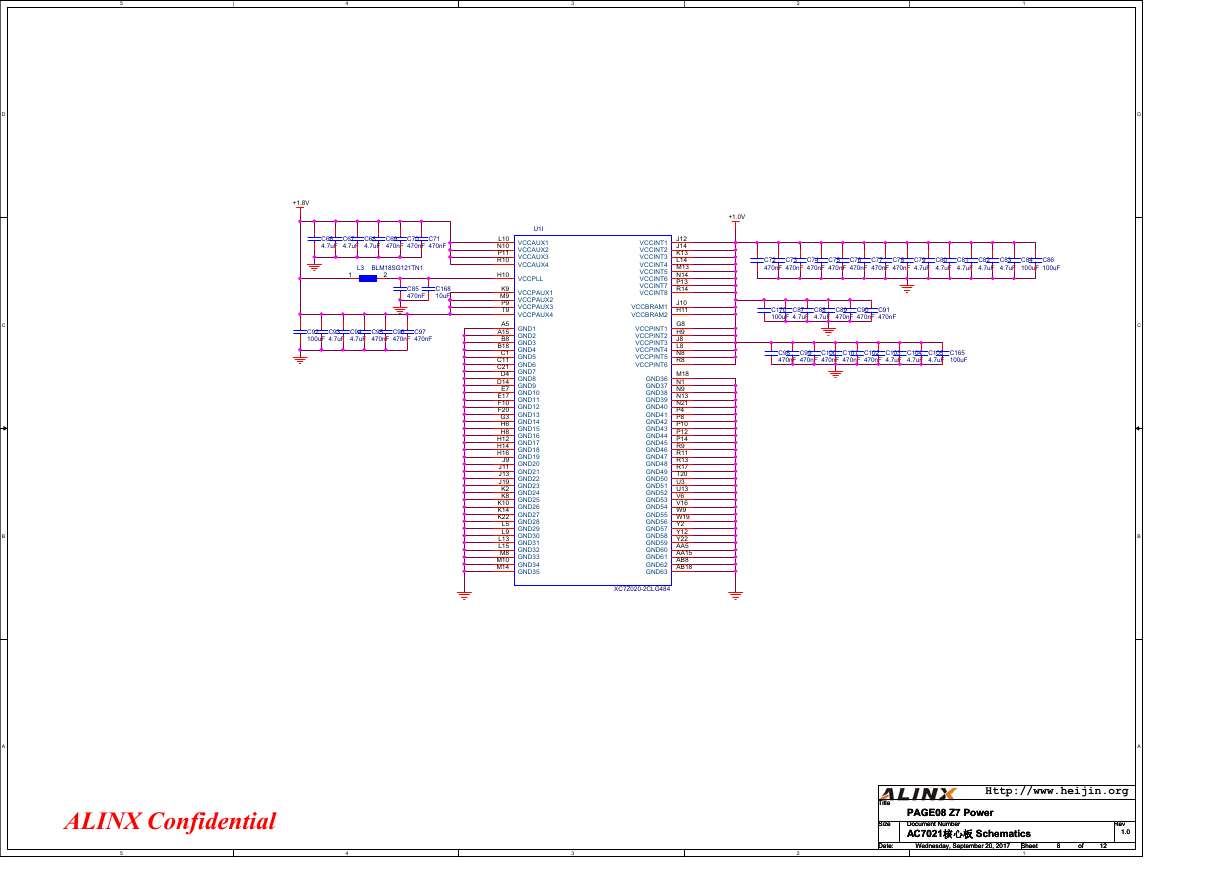

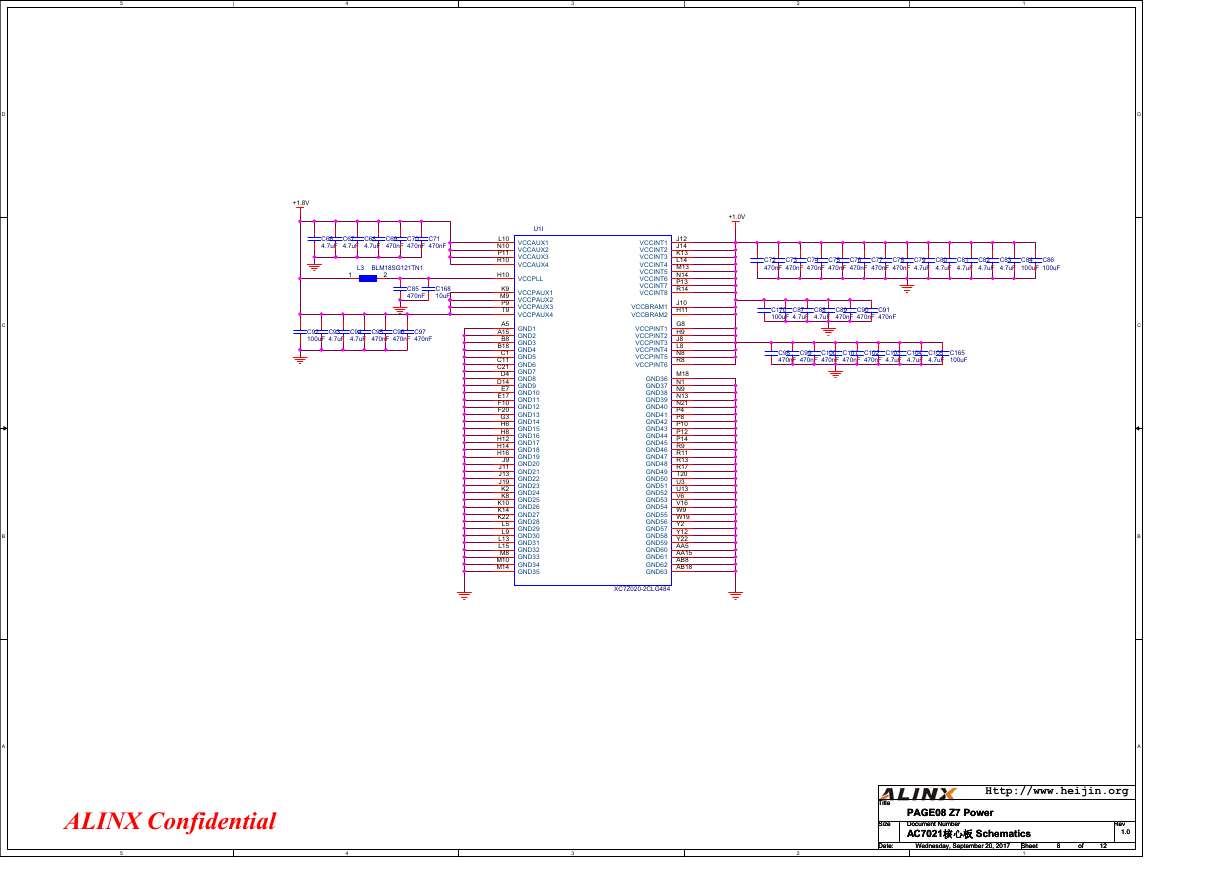

+1.0V

C72

470nF

C73

470nF

C74

470nF

C75

470nF

C76

470nF

C77

470nF

C78

470nF

C79

4.7uF

C80

4.7uF

C81

4.7uF

C82

4.7uF

C83

4.7uF

C84

100uF

C86

100uF

C170

100uF

C87

4.7uF

C88

4.7uF

C89

470nF

C90

470nF

C91

470nF

C98

470nF

C99

470nF

C100

470nF

C101

470nF

C102

470nF

C103

4.7uF

C104

4.7uF

C105

4.7uF

C165

100uF

+1.8V

C66

4.7uF

C67

4.7uF

C68

4.7uF

C69

470nF

C70

470nF

C71

470nF

L3 BLM18SG121TN1

2

1

C85

470nF

C168

10uF

C92

100uF

C93

4.7uF

C94

4.7uF

C95

470nF

C96

470nF

C97

470nF

L10

N10

P11

R10

H10

K9

M9

P9

T9

A5

A15

B8

B18

C1

C11

C21

D4

D14

E7

E17

F10

F20

G3

H6

H8

H12

H14

H16

J9

J11

J13

J19

K2

K8

K10

K14

K22

L5

L9

L13

L15

M8

M10

M14

U1I

VCCAUX1

VCCAUX2

VCCAUX3

VCCAUX4

VCCPLL

VCCPAUX1

VCCPAUX2

VCCPAUX3

VCCPAUX4

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

GND9

GND10

GND11

GND12

GND13

GND14

GND15

GND16

GND17

GND18

GND19

GND20

GND21

GND22

GND23

GND24

GND25

GND26

GND27

GND28

GND29

GND30

GND31

GND32

GND33

GND34

GND35

VCCINT1

VCCINT2

VCCINT3

VCCINT4

VCCINT5

VCCINT6

VCCINT7

VCCINT8

VCCBRAM1

VCCBRAM2

VCCPINT1

VCCPINT2

VCCPINT3

VCCPINT4

VCCPINT5

VCCPINT6

GND36

GND37

GND38

GND39

GND40

GND41

GND42

GND43

GND44

GND45

GND46

GND47

GND48

GND49

GND50

GND51

GND52

GND53

GND54

GND55

GND56

GND57

GND58

GND59

GND60

GND61

GND62

GND63

J12

J14

K13

L14

M13

N14

P13

R14

J10

H11

G8

H9

J8

L8

N8

R8

M18

N1

N9

N13

N21

P4

P8

P10

P12

P14

R9

R11

R13

R17

T20

U3

U13

V6

V16

W9

W19

Y2

Y12

Y22

AA5

AA15

AB8

AB18

XC7Z020-2CLG484

D

C

B

A

ALINX Confidential

5

4

3

2

Http://www.heijin.org

Title

Title

Title

Size

Size

Size

Date:

Date:

Date:

PAGE08 Z7 Power

PAGE08 Z7 Power

PAGE08 Z7 Power

Document Number

Document Number

Document Number

AC7021核心板 Schematics

AC7021核心板 Schematics

AC7021核心板 Schematics

Sheet

Sheet

Sheet

1

Wednesday, September 20, 2017

Wednesday, September 20, 2017

Wednesday, September 20, 2017

Rev

Rev

Rev

1.0

1.0

1.0

8

8

8

of

of

of

12

12

12

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc