高级FPGA设计——结构、实现和优化.pdf

发布时间:2022-05-30

发布人:admin

分类:说明书

资料大小:39.34M

资料格式:pdf

举报

版权申诉

第1页 / 共251页

第2页 / 共251页

第3页 / 共251页

第4页 / 共251页

第5页 / 共251页

第6页 / 共251页

第7页 / 共251页

第8页 / 共251页

前封面

背封面

高级FPGA设计:结构、实现和优化

版权页

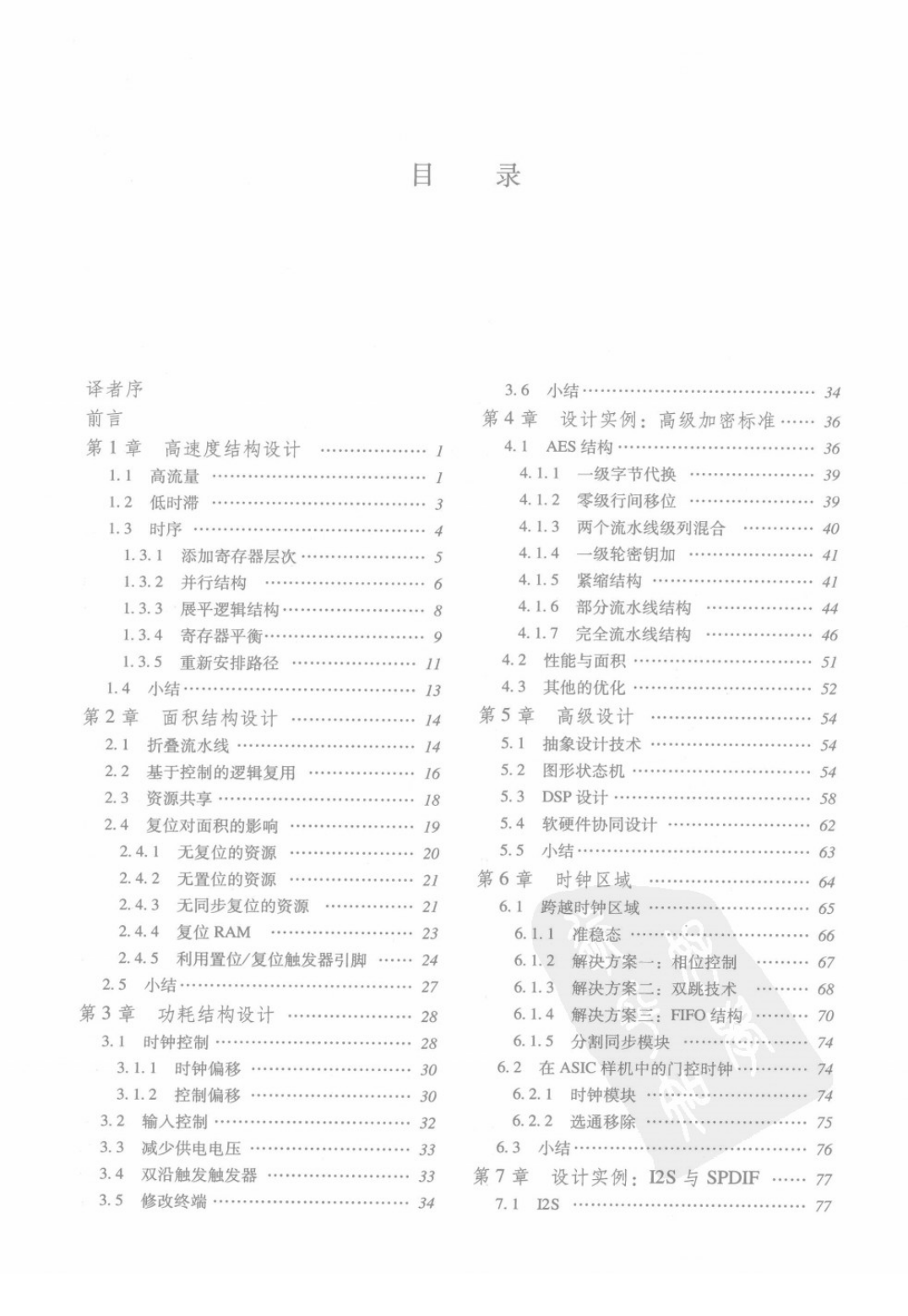

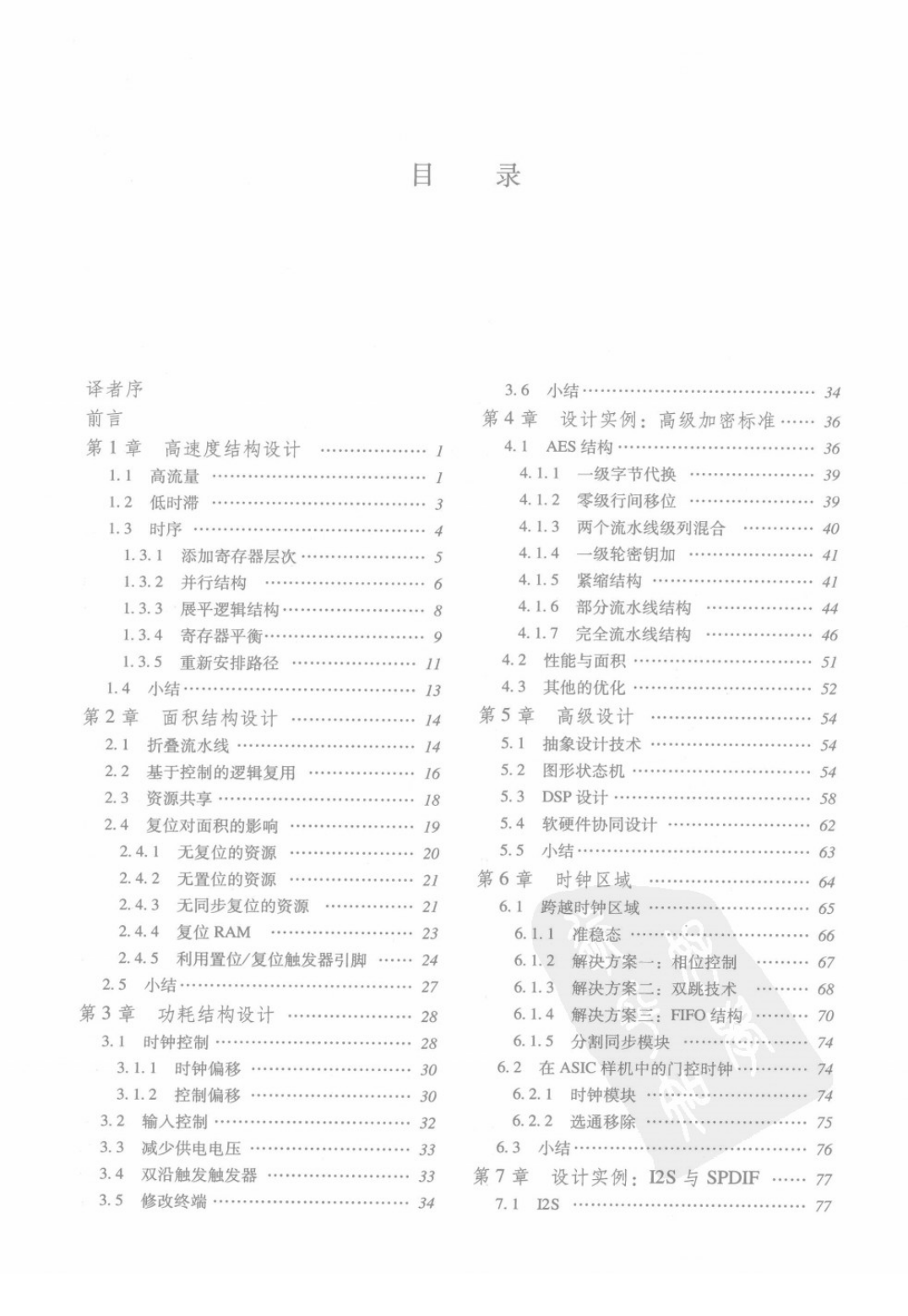

译者序

前言

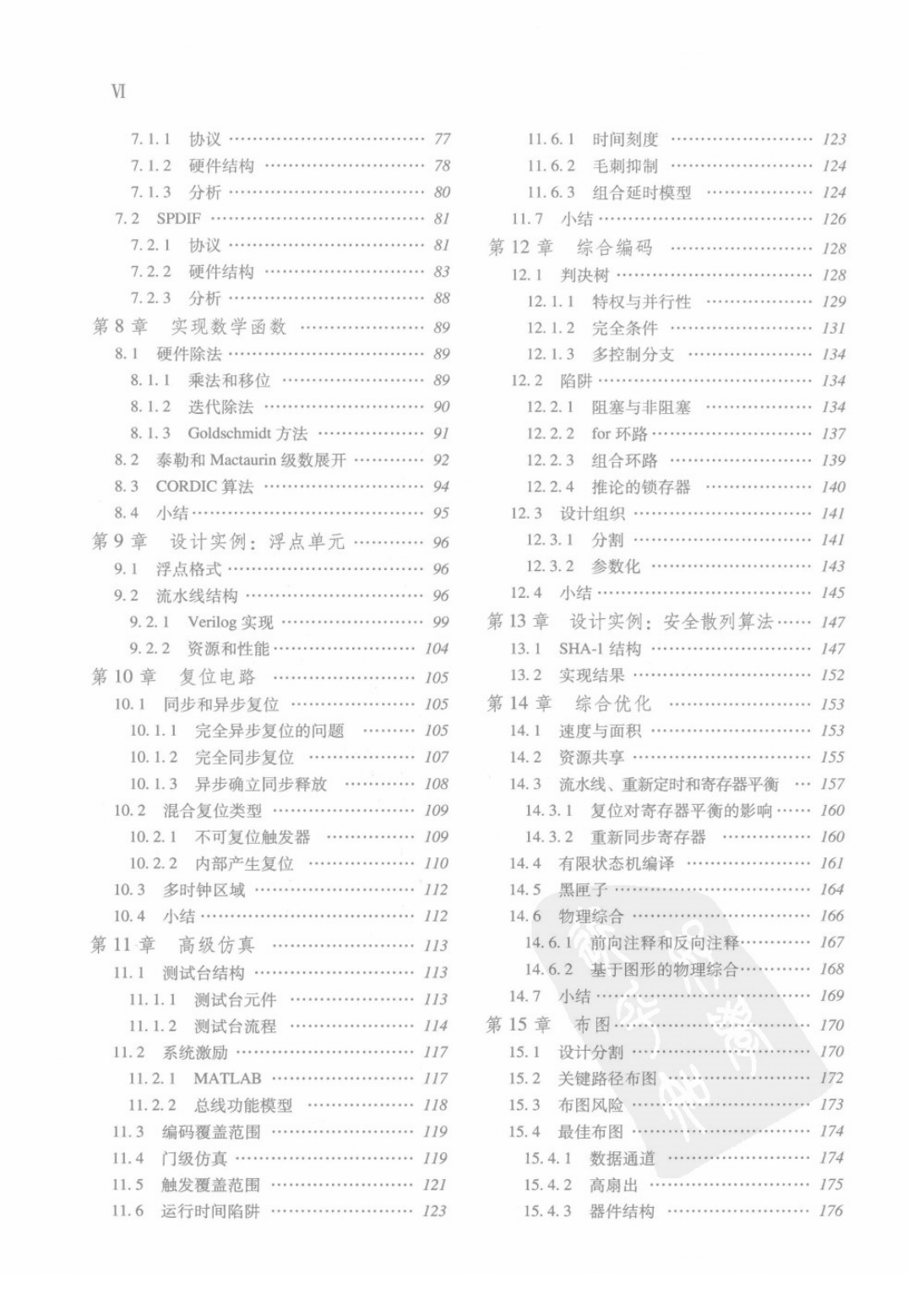

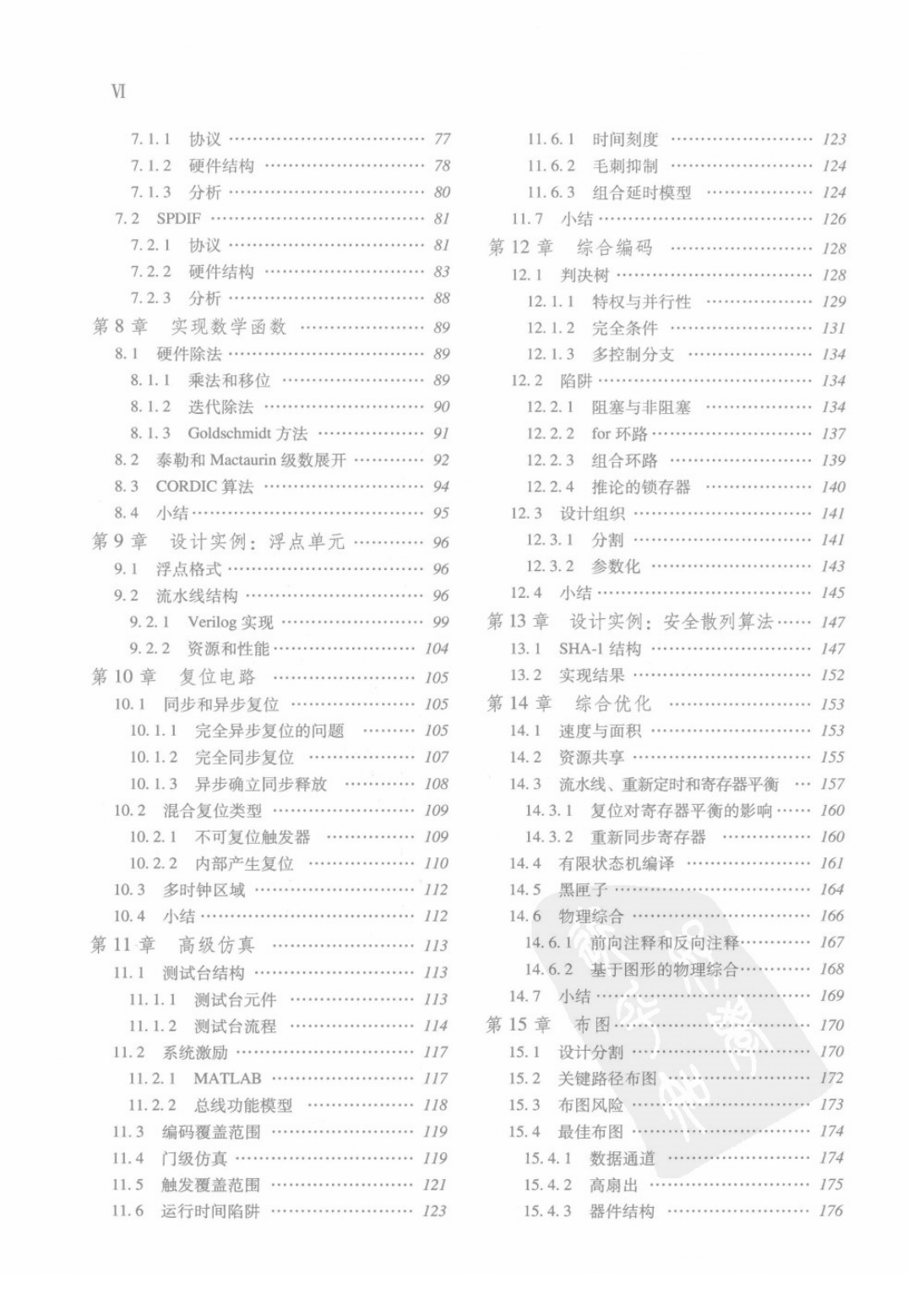

目录

第1章 高速度结构设计

1.1 高流量

1.2 低时滞

1.3 时序

1.3.1 添加寄存器层次

1.3.2 并行结构

1.3.3 展平逻辑结构

1.3.4 寄存器平衡

1.3.5 重新安排路径

1.4 小结

第2章 面积结构设计

2.1 折叠流水线

2.1 基于控制的逻辑复用

2.3 资源共享

2.4 复位对面积的影响

2.5 小结

第3章 功耗结构设计

3.1 时钟控制

3.2 输入控制

3.3 减少供电电压

3.4 双沿触发触发器

3.5 修改终端

3.6 小结

第4章 设计实例:高级加密标准

4.1 AES结构

4.2 性能与面积

4.3 其他的优化

第5章 高级设计

5.1 抽象设计技术

5.2 图形状态机

5.3 DSP 设计

5.4 软硬件协同设计

5.5 小结

第6章 时钟区域

6.1 跨越时钟区域

6.2 在ASIC样机中的门控时钟

6.3 小结

第7章 设计实例:I2S与SPDIF

7.1 I2S

7.2 SPDIF

第8章 实现数学函数

8.1 硬件除法

8.2 泰勒和Mactaurin级数展开

8.3 CORDIC算法

8.4 小结

第9章 设计实例:浮点单元

9.1 浮点格式

9.2 流水线结构

第10章 复位电路

10.1 同步和异步复位

10.2 混合复位类型

10.3 多时钟区域

10.4 小结

第11章 高级仿真

11.1 测试台结构

11.2 系统激励

11.3 编码覆盖范围

11.4 门级仿真

11.5 触发覆盖范围

11.6 运行时间陷阱

11.7 小结

第12章 综合编码

12.1 判决树

12.2 陷阱

12.3 设计组织

12.4 小结

第13章 设计实例:安全散列算法

13.1 SHA-1 结构

13.2 实现结果

第14章 综合优化

14.1 速度与面积

14.2 资源共享

14.3 流水线、重新定时和寄存器平衡

14.4 有限状态机编译

14.5 黑匣子

14.6 物理综合

14.7 小结

第15章 布 图

15.1 设计分割

15.2 关键路径布图

15.3 布图风险

15.4 最佳布图

15.5 减少功耗

15.6 小结

第16章 布局布线优化

16.1 优化约束

16.2 布局和布线之间的关系

16.3 逻辑复制

16.4 跨层次优化

16.5 I/O寄存器

16.7 映射逻辑到RAM

16.8 寄存器排序

16.9 布局种子

16.10 指导布局和布线

16.11 小结

第17章 设计实例:微处理器

17.1 SRC结构

17.2 综合优化

17.3 布图优化

第18章 静态时序分析

18.1 标准分析

18.2 锁存器

18.3 异步电路

18.4 小结

第19章 PCB 的问题

19.1 电源供电

19.2 去耦电容

19.3 小结

附录A AES 密码的流水线级

附录B SRC 处理器的顶层模块

参考文献

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc