科技广场

2008.10

基于

CPLD

的数字电压表的设计

Design of Digital Voltmeter Based on CPLD

孙艳菱

Sun Yanling

长江师范学院物理电子系

重庆 涪陵

,

408100)

(

(Department of Physics and Electronic Information Engineering, Yangtze Normal University, Chongqing Fuling 408100)

摘 要:本文以可编程逻辑器件

为核心,采用

(CPLD)

ADC0809

对硬件的测试表明:设计的数字电压表能测量

作为

A/D

转换器,使用

电压,测量精确度为

硬件描述语言设计了一种新

,所设计的数字电压表有较高

VHDL

0.02V

0~5V

。

型的数字电压表

的灵活性和可扩展性

关键词:CPLD

中图分类号:

TP331

。

;数字电压表

; VHDL

文献标识码:

B

文章编号:

1671-4792-(2008)10-0226-03

Abstract: A new kind of DVM is designed in this paper, The DVM takes CPLD as control unit,ADC0809 is selected for the A/D

converter, followed the hardware description language VHDL.Though test of the hardware:The digital voltmeter can measure voltage

with a range from the 0 to 5V and a resolving power 0.02V, It features DVM with high flexibility and better expansibility.

Keywords: CPLD; Digital Voltmeter; VHDL

0 引言

描显示

最终由

),

LED

数码管显示结果

。

传 统 的 数 字 电 压 表 采 用 模

/

数 转 换 器 件 和 通 用 集 成 逻

辑 器 件来 设 计

,

这样 的 设 计不 便 于 系统 的 修 改 和 升 级

缺 少

,

灵活性

接线复杂

体积大

,

。

核心 的 数 字电 压 表 的设 计 所 用器 件 少

,

,

故障率高

另外

以单片机为控制

,

使用 灵 活

,

,

是 目 前 使

用最为广泛的一种设计方式 [1]。

也出 现 了 一些 问 题

如工 作 速 度较 低

但是在设计和调试的过程中

,

功 能 修 改 及 调 试 都 需

,

,

要硬件电路的支持等

在一定程度上增加了功能修改及系统

,

图一 系统原理框图

调试的困难

。

用可编程逻辑器件

(CPLD)

设计的数字电压表

模

/

数转换电路用于接受外 部 直流 电 压

并且 进 行 模拟

,

除了能完成数字逻辑的基本功能之外

优势

。

用硬件描述语言决定系统功能

,

,

更具有系统级设计的

量向数字量的转换

,

将数字电压值送到控制电路以待运算和

可以在硬件不变的情

处理

;

控制电路由能够 完成 逻 辑 功能 兼 具 存储 功 能 的

况 下根 据 需 要修 改 程 序

以 更 新 和扩 展 功 能

其 灵 活 性 和 适

,

,

应性显著提高[2]。

1 系统设计

芯片担任

果及编码

收

CPLD

,CPLD

驱动显示

、

转换后的

;

包括控制

转换动作

接收

A/D

A/D

显示部分采用七段译码显示器

、

CPLD

转换结

用来接

,

BCD

数据并显示

。

整个系统可分为三大

基于

CPLD

的 数 字电 压 表 由 三 大 部 分 组 成 [3],

如 图 一 所

模块

:A/D

控制模块

、BCD

码转换模块以及扫描显示模块

。

直流 电 压 输入

A/D

转 换 器后 转 换 为数 字 量 送入

经 过

,

CPLD

的 逻 辑 控 制

(A/D

控 制

、BCD

CPLD

码 转 换 和 扫

2 模块设计与防真

2.1 A/D

控制模块设计

示

。

芯 片

226

�

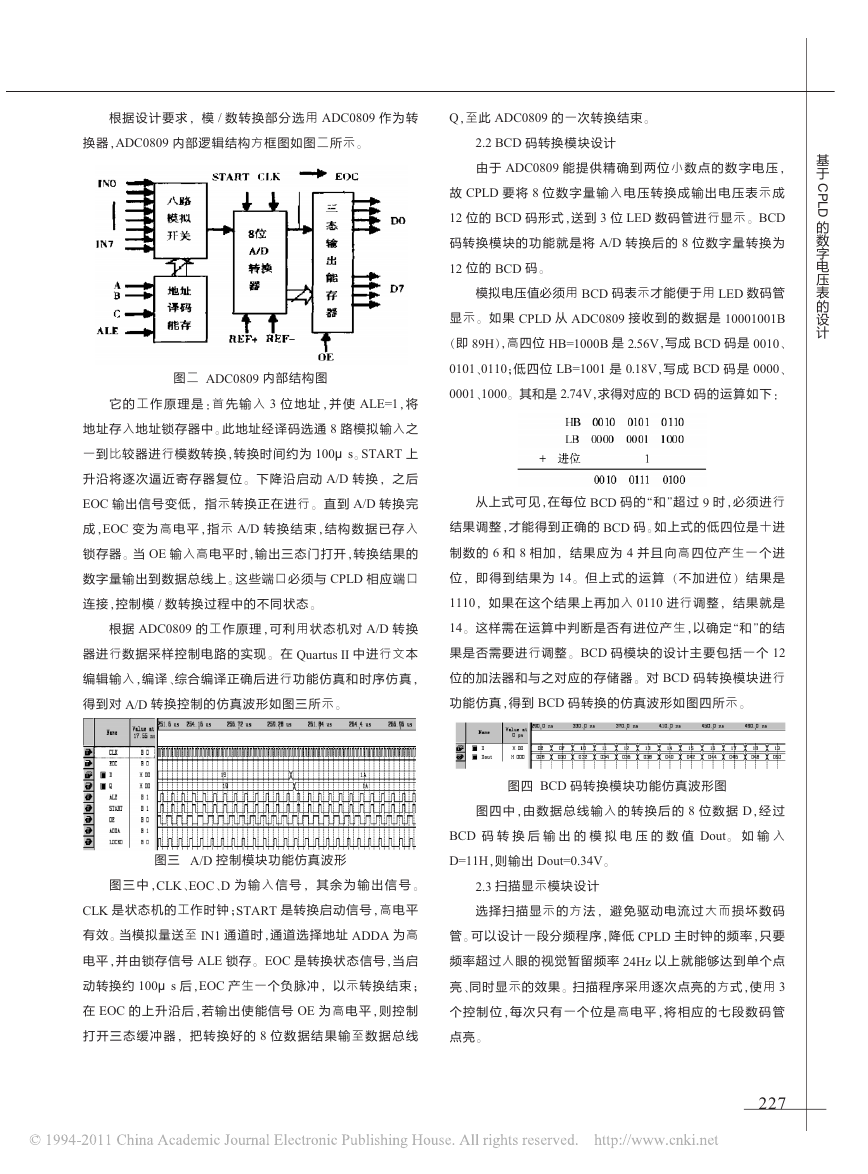

根据设计要求

模

/

,

数转换 部 分 选用

ADC0809

作 为 转

至此

Q,

ADC0809

的一次转换结束

。

换器

,ADC0809

内部逻辑结构方框图如图二所示

。

故

码转换模块设计

ADC0809

要 将

能 提 供 精 确 到 两 位 小 数 点 的 数 字 电 压

,

位 数 字 量 输 入 电 压 转 换 成 输 出 电 压 表 示 成

2.2 BCD

由于

CPLD

位的

8

码形式

送到

BCD

12

码转换模块的 功 能 就是 将

,

位

3

A/D

数码管进行显示

LED

转 换后 的

。 BCD

位 数字 量 转 换为

8

位的

BCD

码

。

12

模拟电压值必须用

BCD

码表示才能便于用

数码管

LED

显示

。

如果

CPLD

从

即

(

89H),

高四位

ADC0809

是

HB=1000B

接收到的 数据 是

2.56V,

写成

BCD

10001001B

码是

0010、

基

于

C

P

L

D

的

数

字

电

压

表

的

设

计

0101、0110;

低四位

LB=1001

是

0.18V,

求得对应的

写成

BCD

码 是

BCD

码的运算如下

0000、

:

0001、1000。

其和是

2.74V,

并 使

ALE=1,

将

路模拟输入之

8

图二

内部结构图

ADC0809

首 先 输 入

位 地 址

3

,

此地址经译码选通

它 的 工 作 原 理 是

:

地址存入地址锁存器中

。

一到比较器进行模数转换

转换时间约为

,

100μs。 START

上

升沿将逐次逼 近 寄 存器 复 位

下降 沿 启 动

。

输出信号变低

指示转换正在进行

EOC

成

,EOC

,

变 为 高 电 平

指 示

,

A/D

。

转 换 结 束

,

A/D

直到

转 换

A/D

之 后

,

转换完

结 构 数 据 已 存 入

锁存器

当

。

OE

输入高电平时

,

输出三态门打开

转换结果的

,

数字量输出到数据总线上

这些端口必须与

。

CPLD

相应端口

从上式可见

在每位

,

BCD

码的

才能得到正确的

码

BCD

和

”

超过

时

,

9

必须进行

如上式的低四位是十进

“

。

相加

,

8

结 果 应 为

4

并 且 向 高 四 位 产 生 一 个 进

结果调整

制数 的

6

,

和

位

,

即得到结果为

14。

但上 式 的 运算

1110,

如果在这个结果上再加入

0110

这样需在运算中判断是否有进位产生

不 加 进位

(

进行调整

,

以确定

,

结 果 是

)

结果就是

和

“

”

的结

。 BCD

码模块的设计主要包括一个

12

码转换模块进行

连接

控制模

数转换过程中的不同状态

。

/

,

根据

ADC0809

,

器进行数据采样控制电路的实现

的 工 作原 理

可 利用 状 态 机对

转 换

A/D

在

Quartus II

中进行文本

。

14。

果是否需要进行调整

编辑输入

编译

,

、

综合编译正确后进行功能仿真和时序仿真

,

位的加法器和与之对应的存储器

对

。

BCD

得到对

A/D

转换控制的仿真波形如图三所示

。

功能仿真

得到

,

BCD

码转换的仿真波形如图四所示

。

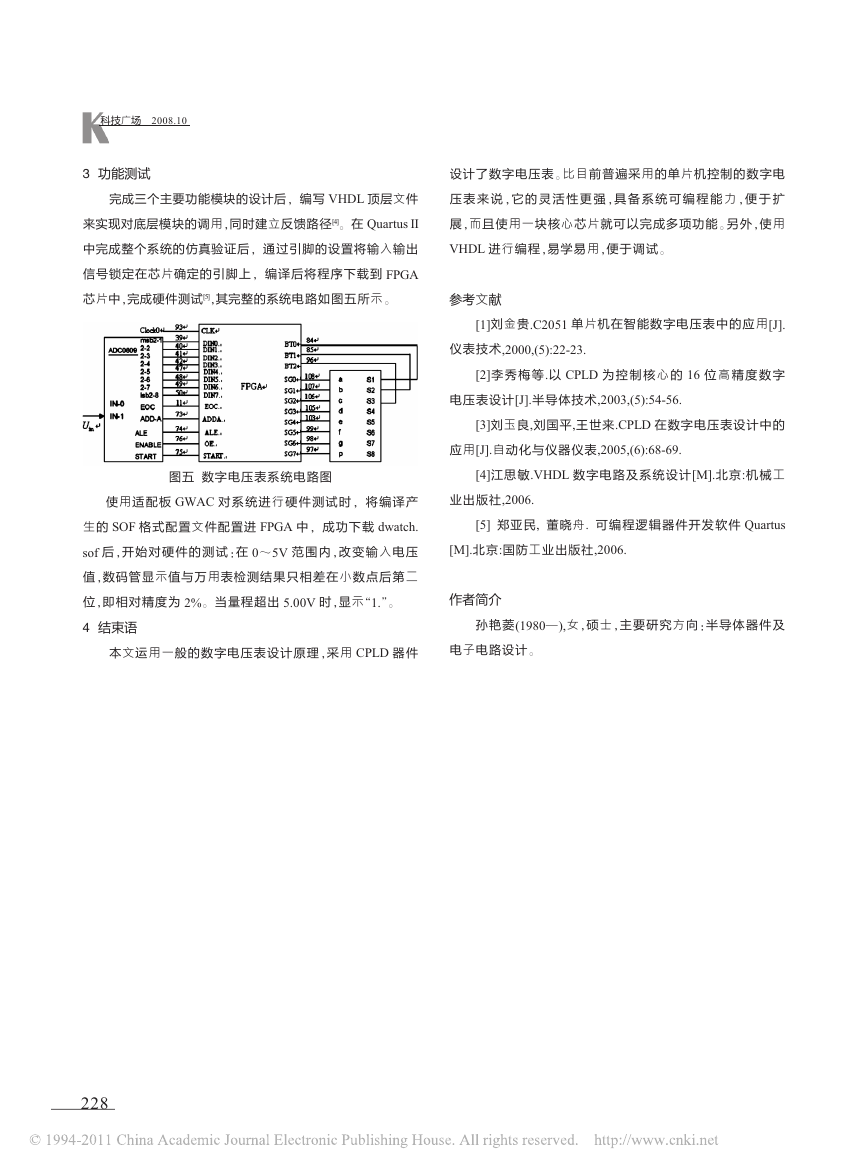

图四

BCD

码转换模块功能仿真波形图

图三

A/D

控制模块功能仿真波形

D=11H,

则输出

Dout=0.34V。

图四 中

由 数 据 总 线 输 入 的 转 换 后 的

8

码 转 换 后 输 出 的 模 拟 电 压 的 数 值

,

位 数 据

Dout。

经 过

D,

如 输 入

BCD

图 三 中

,CLK、EOC、D

是状态机的工作时钟

为 输 入 信 号

,

其 余 为 输 出 信 号

是转换启动信号

,

。

高电平

当模拟量送至

并由锁存信号

。

,

IN1

ALE

通道选择地址

ADDA

是转换状态信号

为高

当启

,

锁存

。 EOC

;START

通道时

,

CLK

有效

电平

扫描显示模块设计

2.3

选择 扫 描 显示 的 方 法

,

可以设计一段分频程序

,

管

。

避 免 驱 动 电 流 过 大 而 损 坏 数 码

降低

CPLD

主时钟的频率

只要

,

频率超过人眼的视觉暂留频率

以上就能够达到单个点

24Hz

动转换约

100μs

后

,EOC

产生一个负脉冲

以示转换结束

亮

、

同时显示的效果

。

扫描程序采用逐次点亮的方式

使用

,

为 高电 平

;

则 控制

,

OE

个控 制 位

,

每次 只 有 一个 位 是 高电 平

,

3

将 相 应 的 七 段 数 码 管

,

在

EOC

的上升沿后

若输出使能信号

,

把 转 换 好的

打 开 三态 缓 冲 器

,

位 数 据 结 果 输 至 数 据 总 线

8

点亮

。

227

�

科技广场

2008.10

3 功能测试

完成三个主要功能模块的设计后

编写

,

来实现对底层模块的调用

,

同时建立反馈路径[4]。

中完成整个系统的仿真验证后

,

信号锁定在芯片确定的引脚上

,

VHDL

在

Quartus II

通过引脚的设置将输入输出

编译后将程序下载到

芯片中

完成硬件测试[5],

,

其完整的系统电路如图五所示

设计了数字电压表

。

比目前普遍采用的单片机控制的数字电

顶层文件

压 表 来 说

,

它 的 灵 活 性 更 强

,

具 备 系 统 可 编 程 能 力

便 于 扩

,

展

,

而且使用一块核心芯片就可以完成多项功能

另外

使用

,

。

VHDL

进行编程

易学易用

便于调试

,

。

,

FPGA

。

参考文献

刘金贵

[1]

.C2051

单片机在智能数字电压表中的应用

[J].

仪表技术

,2000,(5):22-23.

李 秀 梅 等

以

.

CPLD

半导体技术

[2]

[3]

电压表设计

[J].

刘玉良

,2003,(5):54-56.

刘国平

王世来

,

.CPLD

在数字电压表设计中的

,

为 控 制 核 心 的

位 高 精 度 数 字

16

图五 数字电压表系统电路图

江思敏

[4]

.VHDL

数字电路及系统设计

[M].

北京

:

机 械 工

应用

[J].

自动化与仪器仪表

,2005,(6):68-69.

使用适配板

GWAC

对 系 统 进行 硬 件 测试 时

将 编译 产

,

生的

SOF

格式配置文件配置进

FPGA

中

,

成功下载

后

,

开始 对 硬 件的 测 试

在

:

0~5V

范 围 内

,

dwatch.

改 变 输 入电 压

数码管显示值与万用表检测结果只相差在小数点后第二

sof

值

,

业出版社

,2006.

郑亚民

董晓舟

[5]

北京

,

.

国防工业出版社

可编程逻辑器件开发软件

Quartus

,2006.

[M].

:

位

,

即相对精度为

2%。

当量程超出

5.00V

时

,

显示

“1.”。

作者简介

4 结束语

孙艳菱

(1980—),

女

,

硕士

,

主要研究方向

:

半导体 器件 及

本文运用一般的数字电压表设计原理

采用

,

CPLD

器件

电子电路设计

。

228

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc