2019/7/27

pg105-cordic.pdf.html

CORDIC v6.0

LogiCORE IP产品指南

Vivado设计套件

PG105 2017年12月20日

知识产权事实

1/56

�

2019/7/27

介绍

该Xilinx®LogiCORE™IP内核实现了一个

广义坐标旋转数字

计算机(CORDIC)算法。

特征

• 功能配置

• 可选粗调旋转模块

CORDIC的范围从第一个开始

象限(+ Pi / 4到-Pi / 4 Radians)到

完整的循环

可选的幅度补偿缩放

模块来补偿输出

CORDIC的幅度比例因子

算法

输出舍入模式:截断,舍入

Pos Posinity,Round to Pos / Neg Infinity,

最近的甚至是最近的

Word串行架构配置

小面积

高并行架构配置

吞吐量

•

•

•

•

• 控制内部add-sub精度

•

控制add-sub迭代次数

X和Y数据格式:签名分数,

•

无符号分数和无符号整数

• 相位数据格式:Radian,Pi Radian

• 完全同步设计使用单一

时钟

LogiCORE IP事实表

核心细节

支持的

器件系列(1)

支持的用户

接口

资源

设计文件

示例设计

T te st Bench

约束文件

模拟

模型

支持的

S / W驱动程序

设计入门

模拟

合成

UltraScale +™系列

UltraScale™架构

Zynq®-7000 All Programmable SoC

7系列

性能和资源利用率网页

提供核心

AXI4-流

加密RTL

不提供

VHDL

不提供

加密的VHDL

C模型

N / A

经过测试的设计流程(2)

Vivado®设计套件

System Generator for DSP

有关支持的模拟器,请参阅

Xilinx设计工具:版本说明指南。

Vivado综合

支持

Xilinx在Xilinx支持网页上提供

笔记:

1.有关支持的设备的完整列表,请参阅Vivado IP

目录。

2.有关支持的工具版本,请参阅

Xilinx设计工具:版本说明指南。

CORDIC v6.0

PG105 2017年12月20日

www.xilinx.com

产品规格

4

第1章

概观

CORDIC核心实现了广义坐标旋转数字计算机

(CORDIC)算法,最初由Volder [Ref 1] 开发,以迭代求解三角函数

方程式,后来由Walther [参考文献2] 推广以求解更广泛的方程,

包括双曲方程和平方根方程。CORDIC核心实现了

file:///C:/Users/jh/AppData/Local/Temp/Rar$EXa6876.39438/pg105-cordic.pdf.html

2/56

�

2019/7/27

pg105-cordic.pdf.html

矩形< - >极坐标转换

三角函数

以下等式类型:

•

•

• 夸张的

• 平方根

CORDIC核心有两种架构配置:

•

具有单周期数据吞吐量的完全并行配置,代价是

硅片面积

具有多周期吞吐量但占用量小的串行实现

硅片面积

•

执行粗略旋转以将输入样本从整圆旋转到第一圆

象限。(粗调旋转阶段是必需的,因为CORDIC算法仅有效

第一象限)。反向粗旋转台将输出样本旋转到

正确的象限。

CORDIC算法将比例因子引入结果的幅度,并且

CORDIC内核提供自动补偿CORDIC标度的选项

因子。

CORDIC算法可用于解决如上所述的若干功能。这些

函数采用笛卡尔和极坐标操作数的不同组合。操作数X_IN

和Y_IN使用S_AXIS_CARTESIAN通道输入,PHASE_IN操作数为

使用S_AXIS_PHASE输入进行输入。

CORDIC v6.0

PG105 2017年12月20日

www.xilinx.com

五

第1章:概述

功能摘要

• 矢量旋转(极坐标到矩形)

•

矢量平移(矩形到极坐标)

Sin和Cos

•

•

Sinh和Cosh

• 晒黑

• ATANH

•

平方根

应用

CORDIC核心可用于实现中列出的任何通用功能

功能摘要。

file:///C:/Users/jh/AppData/Local/Temp/Rar$EXa6876.39438/pg105-cordic.pdf.html

3/56

�

2019/7/27

pg105-cordic.pdf.html

许可和订购

XilinxVivado®免费提供Xilinx®LogiCOREIP模块

根据Xilinx最终用户许可条款的设计套件。关于这个和的信息

其它Xilinx LogiCORE IP核模块s是可在Xilinx的知识产权属性页。对于

有关其他Xilinx LogiCORE IP模块和工具的定价和可用性的信息,

联系您当地的Xilinx销售代表。

CORDIC v6.0

PG105 2017年12月20日

www.xilinx.com

6

第2章

产品规格

用于定义CORDIC的公式在功能描述中有详细说明

第3章。

性能

核心的延迟和吞吐量受并行或串行选择的影响

建筑。并行 描述了最终的基本延迟和吞吐量

架构配置和Word串行架构配置,尽管它应该

请注意,延迟受所选AXI4-Stream协议形式的影响。CORDIC

在Vivado用户界面® 集成设计环境(IDE)示出了用于延迟

选定的配置。应该说明当选择AXI阻塞模式时,延迟

不应该是主要的设计考虑因素,因为AXI协议管理数据

交通动态。

CORDIC核心有两种架构配置:

• 并行,具有单周期数据吞吐量和大硅面积

•

该选择与AXI4-Stream行为相关的选择无关。

Word Serial,具有多周期吞吐量和更小的硅面积。

file:///C:/Users/jh/AppData/Local/Temp/Rar$EXa6876.39438/pg105-cordic.pdf.html

4/56

�

2019/7/27

pg105-cordic.pdf.html

并行架构配置

CORDIC算法每个位需要大约一个shift-addsub操作

准确性。具有并行架构配置的CORDIC核心实现了这些功能

使用shift-addsub阶段数组并行shift-addsub操作。

具有N位输出宽度的并行CORDIC内核具有N个周期的延迟并产生a

每个周期的新输出。该并联电路的实现尺寸是直接的

与内部精度成正比乘以迭代次数。

Word串行架构配置

CORDIC算法每个位需要大约一个shift-addsub操作

准确性。使用串行架构配置一词实现的CORDIC核心,

CORDIC v6.0

PG105 2017年12月20日

www.xilinx.com

7

第2章:产品规格

使用单个shift-addsub阶段和串行实现这些shift-addsub操作

反馈输出。

具有N位输出宽度的字串行CORDIC内核具有N个周期的延迟并产生

每N个循环一次新输出。这个迭代电路的实现大小是直接的

与内部精度成正比。

资源利用率

有关性能的详细信息,请访问性能和资源利用率。

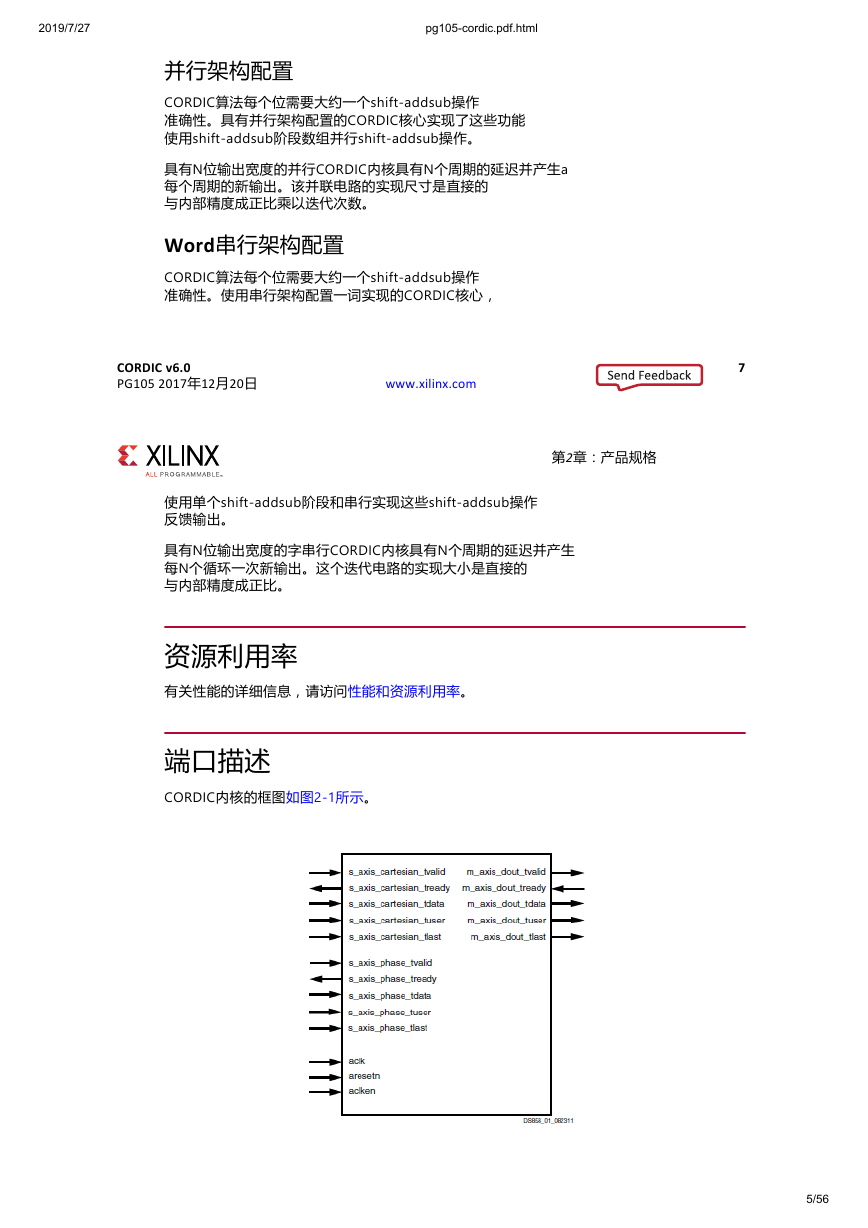

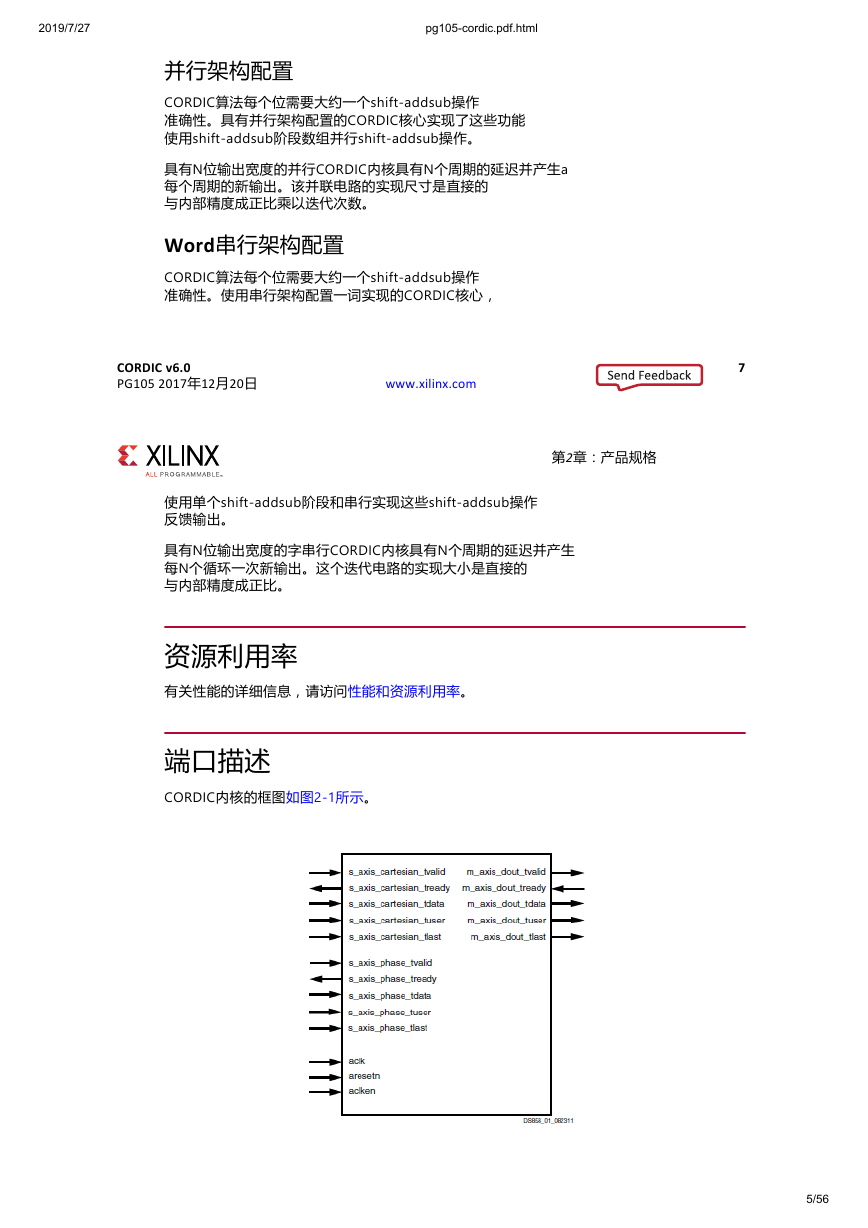

端口描述

CORDIC内核的框图如图2-1所示。

5/56

�

2019/7/27

CORDIC v6.0

PG105 2017年12月20日

www.xilinx.com

8

第2章:产品规格

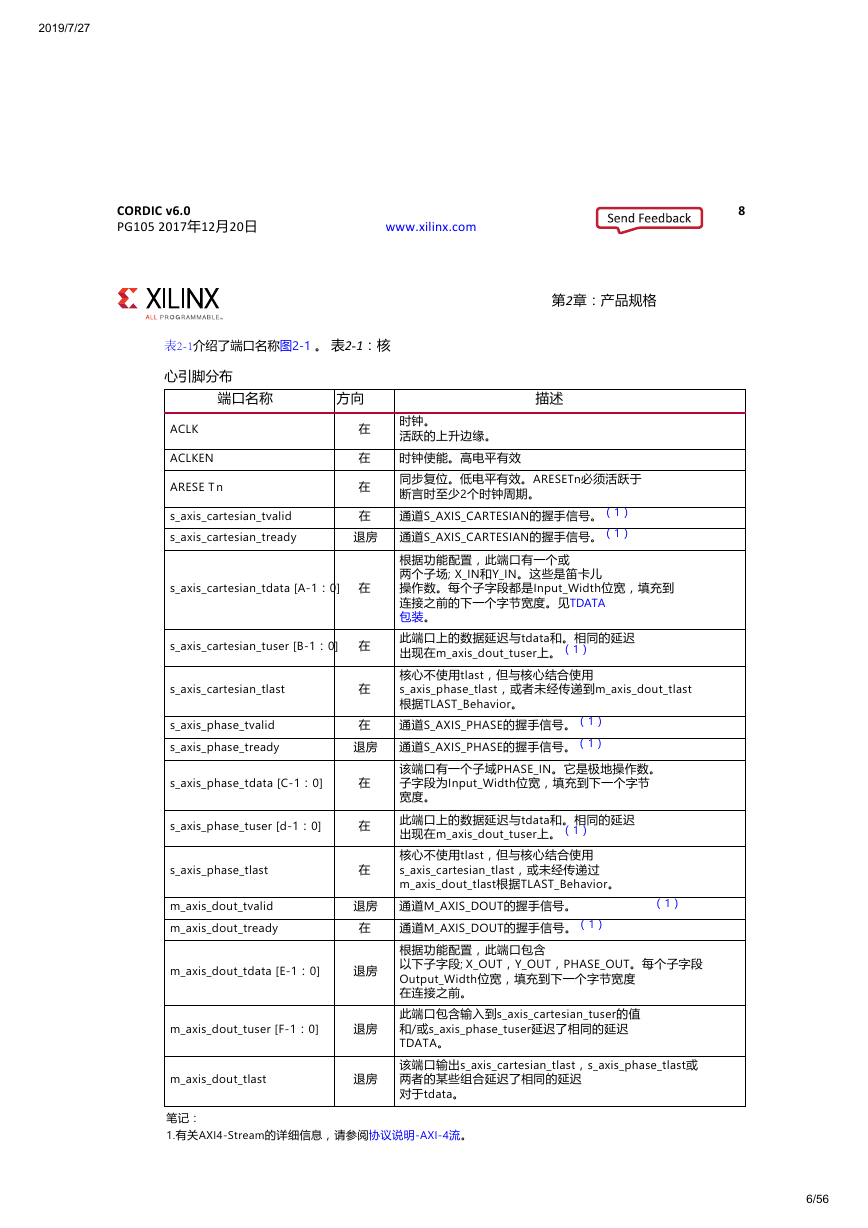

描述

时钟。

活跃的上升边缘。

时钟使能。高电平有效

同步复位。低电平有效。ARESETn必须活跃于

断言时至少2个时钟周期。

通道S_AXIS_CARTESIAN的握手信号。(1)

通道S_AXIS_CARTESIAN的握手信号。(1)

根据功能配置,此端口有一个或

两个子场; X_IN和Y_IN。这些是笛卡儿

操作数。每个子字段都是Input_Width位宽,填充到

连接之前的下一个字节宽度。见TDATA

包装。

此端口上的数据延迟与tdata和。相同的延迟

出现在m_axis_dout_tuser上。(1)

核心不使用tlast,但与核心结合使用

s_axis_phase_tlast,或者未经传递到m_axis_dout_tlast

根据TLAST_Behavior。

通道S_AXIS_PHASE的握手信号。(1)

通道S_AXIS_PHASE的握手信号。(1)

该端口有一个子域PHASE_IN。它是极地操作数。

子字段为Input_Width位宽,填充到下一个字节

宽度。

此端口上的数据延迟与tdata和。相同的延迟

出现在m_axis_dout_tuser上。(1)

核心不使用tlast,但与核心结合使用

s_axis_cartesian_tlast,或未经传递过

m_axis_dout_tlast根据TLAST_Behavior。

通道M_AXIS_DOUT的握手信号。

通道M_AXIS_DOUT的握手信号。(1)

根据功能配置,此端口包含

以下子字段; X_OUT,Y_OUT,PHASE_OUT。每个子字段

Output_Width位宽,填充到下一个字节宽度

在连接之前。

此端口包含输入到s_axis_cartesian_tuser的值

和/或s_axis_phase_tuser延迟了相同的延迟

TDATA。

该端口输出s_axis_cartesian_tlast,s_axis_phase_tlast或

(1)

对于tdata。

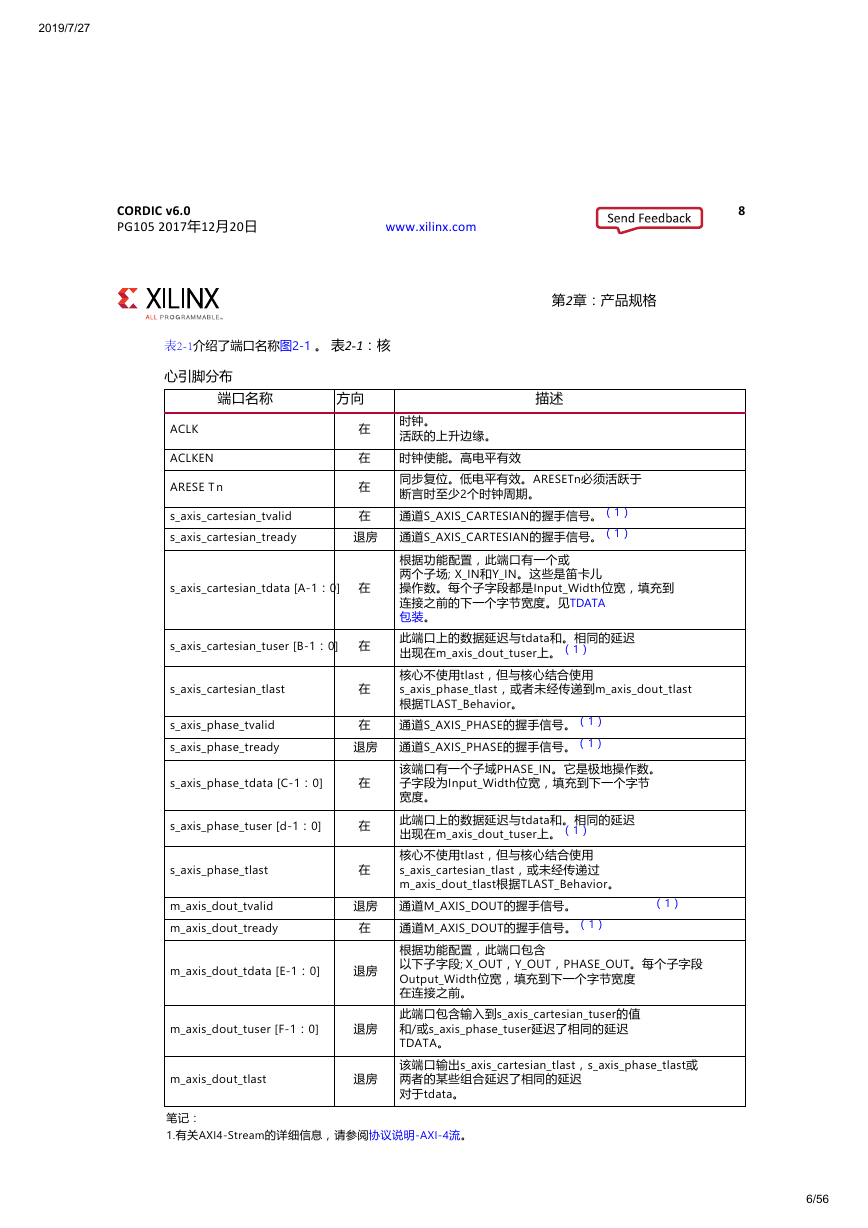

表2-1介绍了端口名称图2-1 。 表2-1:核

心引脚分布

端口名称

方向

ACLK

ACLKEN

ARESE T n

s_axis_cartesian_tvalid

s_axis_cartesian_tready

在

在

在

在

退房

s_axis_cartesian_tdata [A-1:0] 在

s_axis_cartesian_tuser [B-1:0]

在

s_axis_cartesian_tlast

s_axis_phase_tvalid

s_axis_phase_tready

s_axis_phase_tdata [C-1:0]

s_axis_phase_tuser [d-1:0]

s_axis_phase_tlast

m_axis_dout_tvalid

m_axis_dout_tready

在

在

退房

在

在

在

退房

在

m_axis_dout_tdata [E-1:0]

退房

m_axis_dout_tuser [F-1:0]

退房

m_axis_dout_tlast

退房 两者的某些组合延迟了相同的延迟

笔记:

1.有关AXI4-Stream的详细信息,请参阅协议说明-AXI-4流。

6/56

�

2019/7/27

CORDIC v6.0

PG105 2017年12月20日

pg105-cordic.pdf.html

www.xilinx.com

9

第2章:产品规格

宽度常量A到F是任意值,由CORDIC Vivado IDE确定

参数。许多引脚是可选的。如果选择的功能有输入通道,则不存在输入通道

不要求有关频道携带的操作数。例如,平方根

函数不需要PHASE_IN,因此该函数不存在S_AXIS_PHASE。

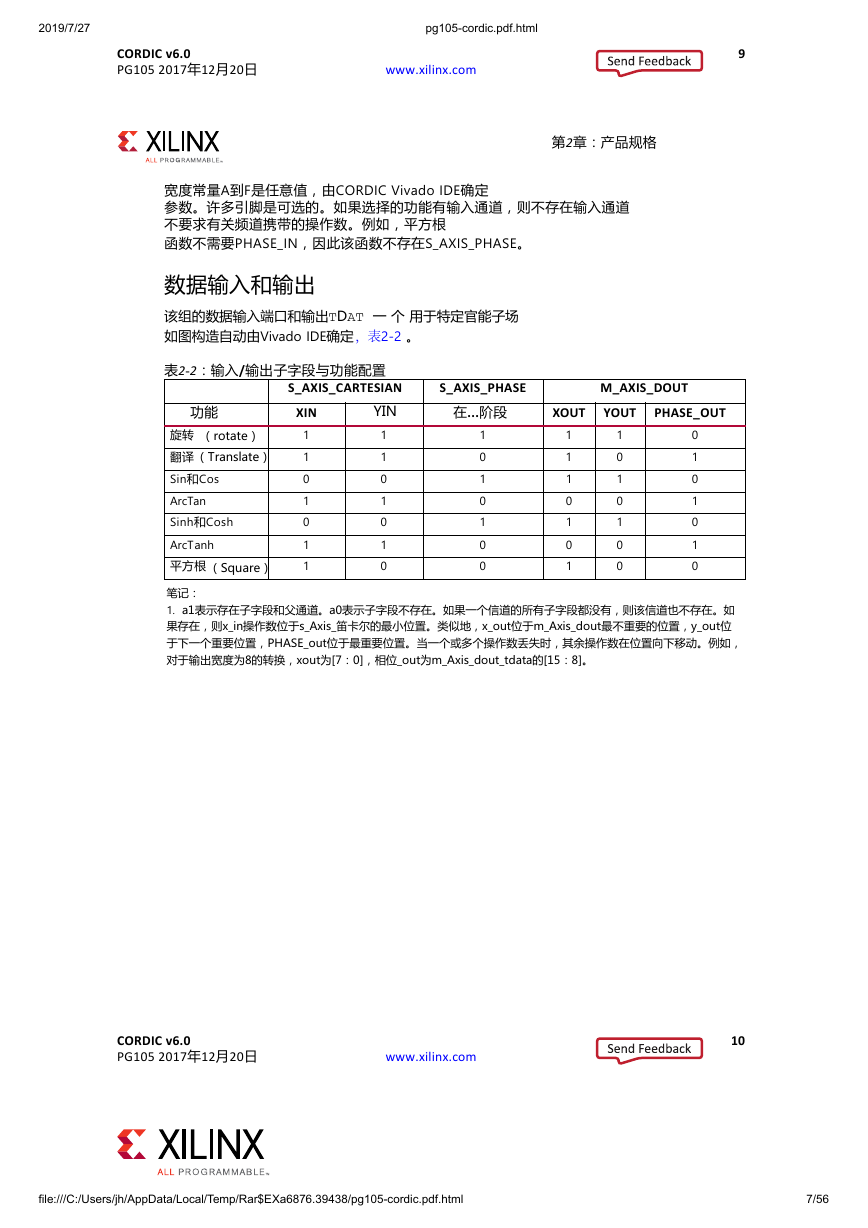

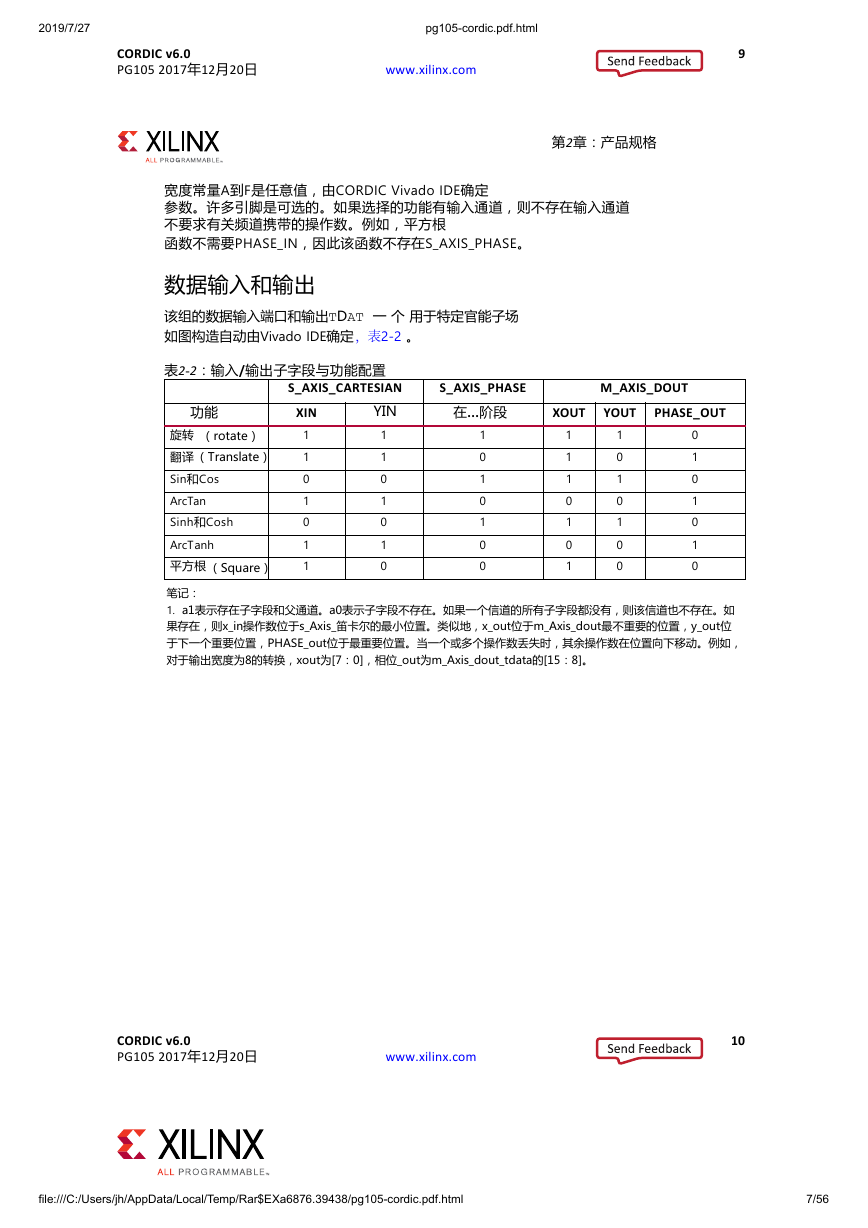

数据输入和输出

该组的数据输入端口和输出TDAT 一 个 用于特定官能子场

如图构造自动由Vivado IDE确定,表2-2 。

表2-2:输入/输出子字段与功能配置

功能

S_AXIS_PHASE

在...阶段

XOUT

M_AXIS_DOUT

YOUT

PHASE_OUT

S_AXIS_CARTESIAN

YIN

XIN

1

1

1

1

0

0

1

1

0

0

1

1

0

1

(rotate)

(Translate)

旋转

翻译

Sin和Cos

ArcTan

Sinh和Cosh

ArcT anh

平方根

笔记:

1. a1表示存在子字段和父通道。a0表示子字段不存在。如果一个信道的所有子字段都没有,则该信道也不存在。如

果存在,则x_in操作数位于s_Axis_笛卡尔的最小位置。类似地,x_out位于m_Axis_dout最不重要的位置,y_out位

于下一个重要位置,PHASE_out位于最重要位置。当一个或多个操作数丢失时,其余操作数在位置向下移动。例如,

对于输出宽度为8的转换,xout为[7:0],相位_out为m_Axis_dout_tdata的[15:8]。

1

0

1

0

1

0

0

1

0

1

0

1

0

0

1

1

1

0

1

0

1

(Square)

0

1

0

1

0

1

0

CORDIC v6.0

PG105 2017年12月20日

www.xilinx.com

10

file:///C:/Users/jh/AppData/Local/Temp/Rar$EXa6876.39438/pg105-cordic.pdf.html

7/56

�

2019/7/27

pg105-cordic.pdf.html

第3章

用核心设计

本章包括指导和附加信息,以便于设计

核心。

计时

CORDIC内核使用单个时钟,称为aclk 。所有输入和输出接口和

内部状态受这个单一时钟的影响。

复位

CORDIC内核使用一个名为ARESETn的可选复位输入。这个信号是

active-Low,必须处于活动或非活动状态至少两个时钟周期才能确保

正确的操作。ARESETn 是一个全局同步复位,它复位所有控制状态

核心; 当断言ARESET n 时,通过核心传输的所有数据都将丢失。

协议描述-AXI-4流

转换为AXI4-Stream接口带来了标准化和增强

Xilinx®LogiCORE™IP解决方案的互操作性。除了一般控制信号之外

作为aclk ,ACLKEN 和ARESETn ,传送CORDIC内核的所有输入和输出

使用AXI4-Stream频道。一个通道包括tvali d 和tdat a always,加上几个

可选的端口和字段。在CORDIC核心中,支持的可选端口是tready ,

tlas t 和tuser 。T o gether ,tvali d 和tread y 执行握手以转移a

消息,其中有效载荷是tdata ,tuse r 和tlast 。CORDIC核心运行

包含在操作数TDAT 一 个 字段和结果在输出TDAT 一 个 领域

输出通道。CORDIC核心不使用输入,tuse r 和tlas t ,但是

core提供了传输这些字段的工具,其延迟与tdata 相同。这个

从输入到输出传递tlas t 和tuse r 的 设施旨在方便使用

系统中的CORDIC核心。例如,CORDIC核心可能在流式传输上运行

打包数据。在此示例中,核心可被配置为传递TLAS 吨 的

打包数据通道,从而节省系统设计人员构建的工作量

CORDIC v6.0

PG105 2017年12月20日

www.xilinx.com

11

第3章:使用核心进行设计

绕过此信息的路径。有关AXI4-Stream接口的更多信息,请参阅

[参考3] 和[参考4] 。

基本握手

图3-1 显示了AXI4-Stream通道中的数据传输。tvali d 是由

通道的源(主)侧和踏板y 由接收器(从属)驱动。tvalid

表示有效负载字段(tdata ,tuse r 和tlast )中的值有效。TREADY

表示从站已准备好接收数据。当tvali d 和tread y 都为TRUE时

file:///C:/Users/jh/AppData/Local/Temp/Rar$EXa6876.39438/pg105-cordic.pdf.html

8/56

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc