利用 MAX II CPLD 实现电压电

平转换器

2007 年 12 月, 1.0 版

应用笔记 490

引言

本设计实例介绍怎样使用 Altera® MAX® II CPLD 来实现混合电压设计环

境中不同器件之间的电压电平转换。

多电压系统

利用 MAX II

CPLD 实现电平

转换器

电路板上的器件有可能使用不同的供电电压,例如 5V、 3.3V、 2.5V、

1.8V 和 1.5V。因此,和系统连接的总线采用不同的电压标准会导致电压电

平冲突。 MAX II CPLD 实现了和 1.5-V、 1.8-V、 2.5-V、 3.3-V 信号的

直接接口,避免了这类电压冲突。

MAX II CPLD的内核供电电压(VCCINT)和CPLD输出电压(VCCIO)分开,因

此能够连接使用不同电压的器件。电压电平转换的应用有:

■ 连接微处理器和采用不同 I/O 标准以及电平工作的外设器件、定时器

和收发器等。

■ 驱动采用不同 I/O 标准的多组 GPIO 引脚。

MAX II CPLD 可承受所有类型的上电排序,适合多电压系统,在这些系

统中维持一定的上电顺序非常关键。

利用 VCCIO 引脚,配置每一 I/O 块,使其工作在某一电压下。器件可以

支持 1.5-V、 1.8-V、 2.5-V 和 3.3-V 接口,每一独立块可支持不同的标

准。此外,每一 I/O 块的输入输出引脚采用相同的 VCCIO,支持多种标

准。 MAX II 器件 I/O 块的数量和型号有关。内部 LDO 电压稳压器为器

件提供必须的 1.8-V 内部电压供电 (MAX IIG 和 MAX IIZ 除外 )。电压稳

压器输入支持 3.3V 或者 2.5-V 供电,提供 1.8-V 内部电压。

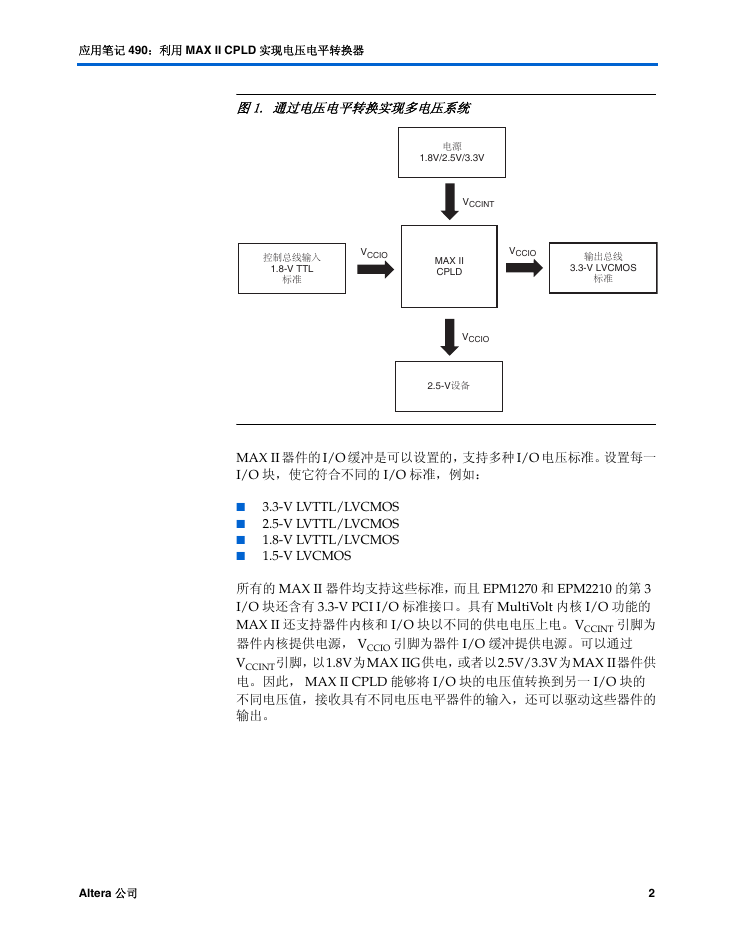

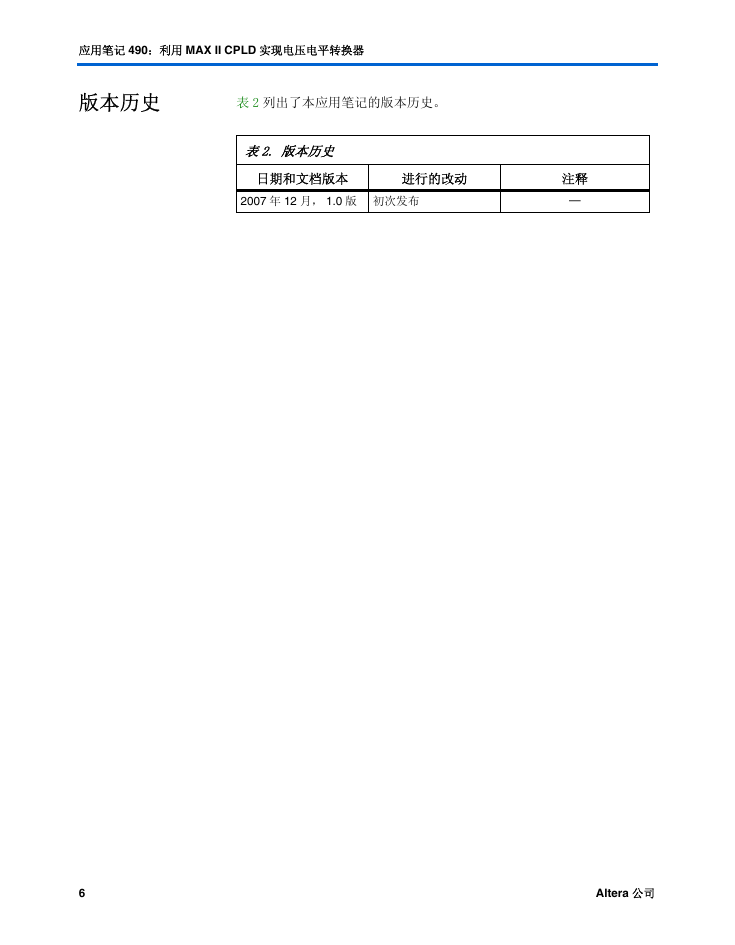

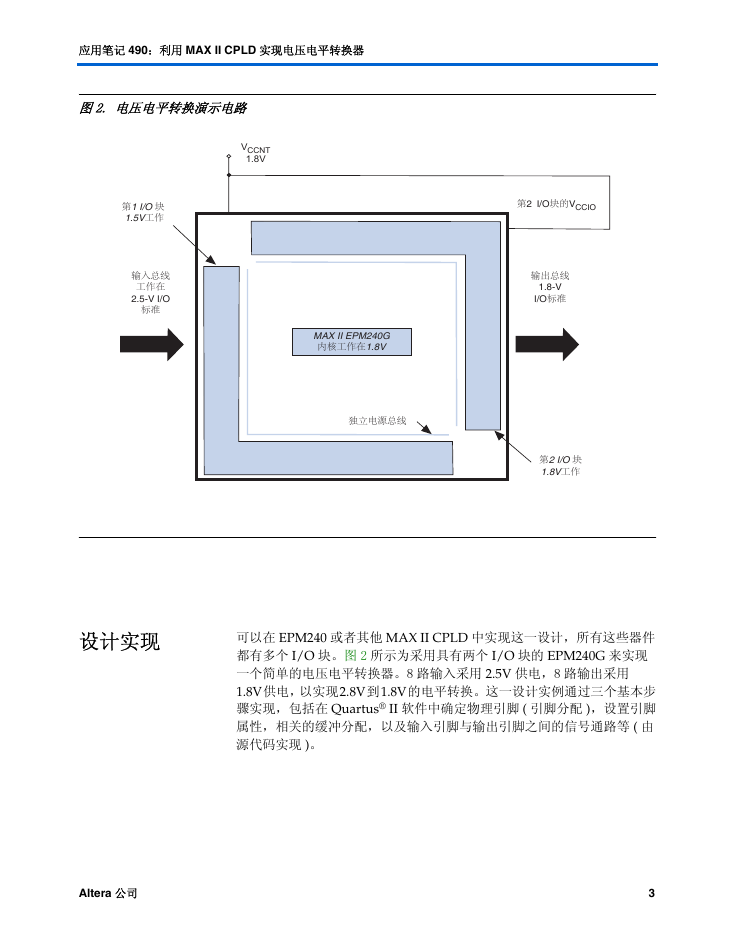

图 1 所示为电压电平转换器实现的多电压系统。

Altera 公司

AN-490-1.0

1

�

应用笔记 490:利用 MAX II CPLD 实现电压电平转换器

图1. 通过电压电平转换实现多电压系统

电源

1.8V/2.5V/3.3V

VCCINT

控制总线输入

1.8-V TTL

标准

VCCIO

MAX II

CPLD

VCCIO

输出总线

3.3-V LVCMOS

标准

VCCIO

2.5-V设备

MAX II 器件的 I/O 缓冲是可以设置的,支持多种 I/O 电压标准。设置每一

I/O 块,使它符合不同的 I/O 标准,例如:

■ 3.3-V LVTTL/LVCMOS

■ 2.5-V LVTTL/LVCMOS

■ 1.8-V LVTTL/LVCMOS

■ 1.5-V LVCMOS

所有的 MAX II 器件均支持这些标准,而且 EPM1270 和 EPM2210 的第 3

I/O 块还含有 3.3-V PCI I/O 标准接口。具有 MultiVolt 内核 I/O 功能的

MAX II 还支持器件内核和 I/O 块以不同的供电电压上电。VCCINT 引脚为

器件内核提供电源, VCCIO 引脚为器件 I/O 缓冲提供电源。可以通过

VCCINT引脚,以1.8V为MAX IIG供电,或者以2.5V/3.3V为MAX II器件供

电。因此, MAX II CPLD 能够将 I/O 块的电压值转换到另一 I/O 块的

不同电压值,接收具有不同电压电平器件的输入,还可以驱动这些器件的

输出。

Altera 公司

2

�

应用笔记 490:利用 MAX II CPLD 实现电压电平转换器

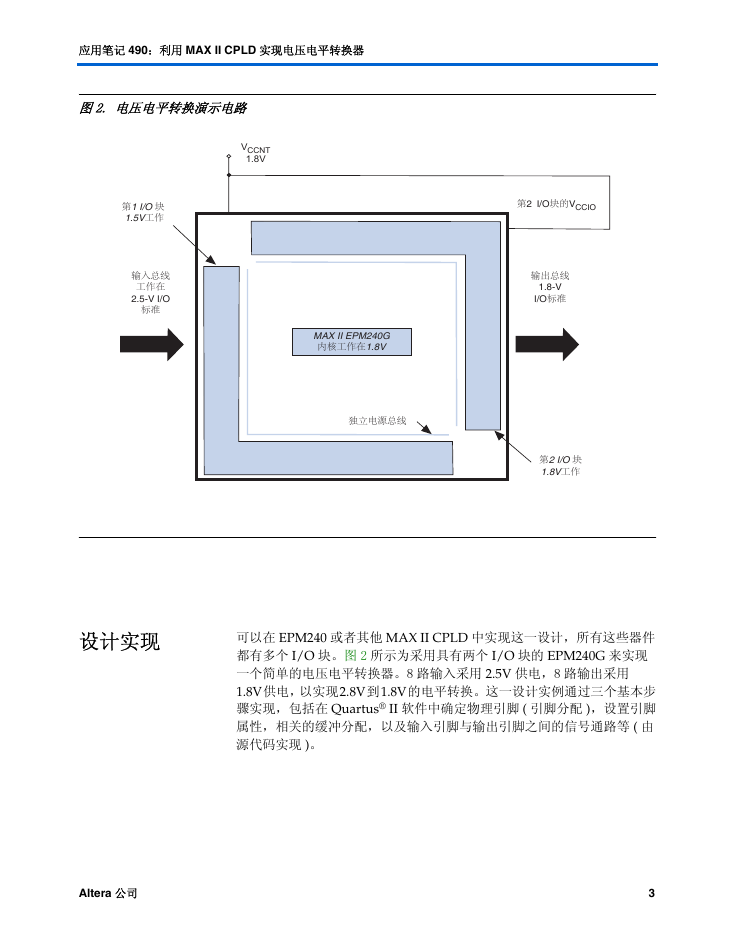

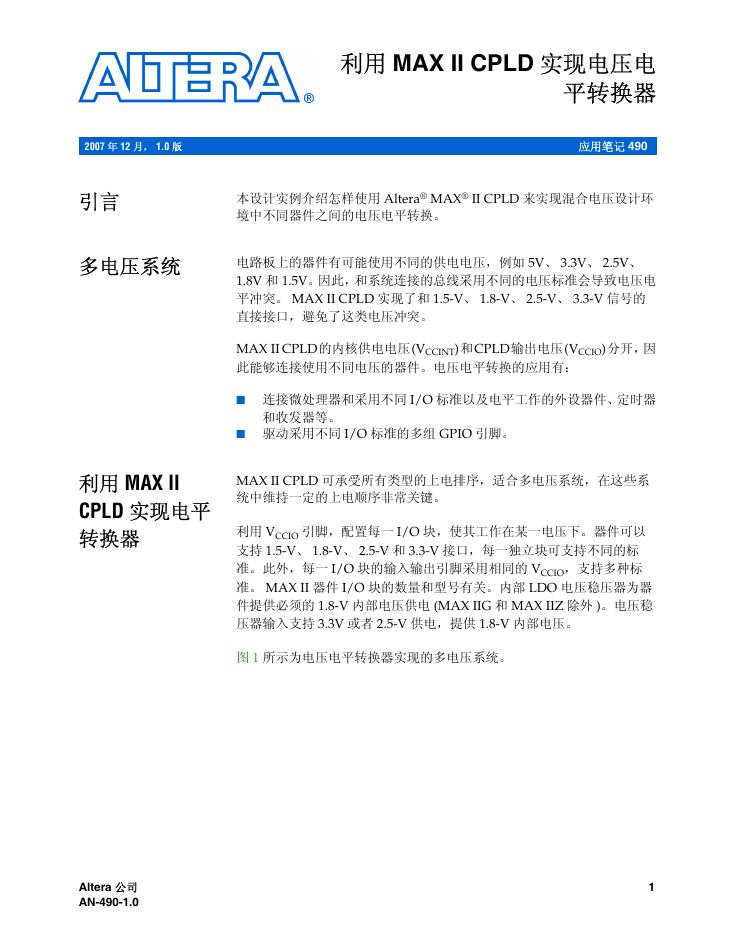

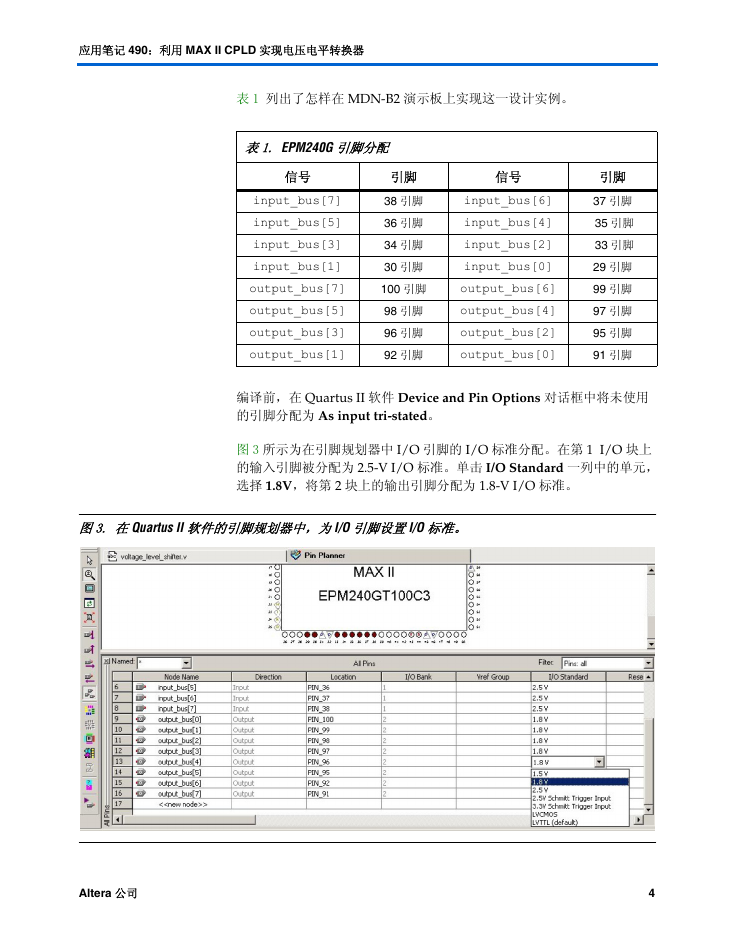

图2. 电压电平转换演示电路

VCCNT

1.8V

第1 I/O 块

1.5V工作

输入总线

工作在

2.5-V I/O

标准

MAX II EPM240G

内核工作在1.8V

独立电源总线

第2 I/O块的VCCIO

输出总线

1.8-V

I/O标准

第2 I/O 块

1.8V工作

设计实现

可以在 EPM240 或者其他 MAX II CPLD 中实现这一设计,所有这些器件

都有多个 I/O 块。图 2 所示为采用具有两个 I/O 块的 EPM240G 来实现

一个简单的电压电平转换器。8 路输入采用 2.5V 供电,8 路输出采用

1.8V供电,以实现2.8V到1.8V的电平转换。 这一设计实例通过三个基本步

骤实现,包括在 Quartus® II 软件中确定物理引脚 ( 引脚分配 ),设置引脚

属性,相关的缓冲分配,以及输入引脚与输出引脚之间的信号通路等 ( 由

源代码实现 )。

Altera 公司

3

�

应用笔记 490:利用 MAX II CPLD 实现电压电平转换器

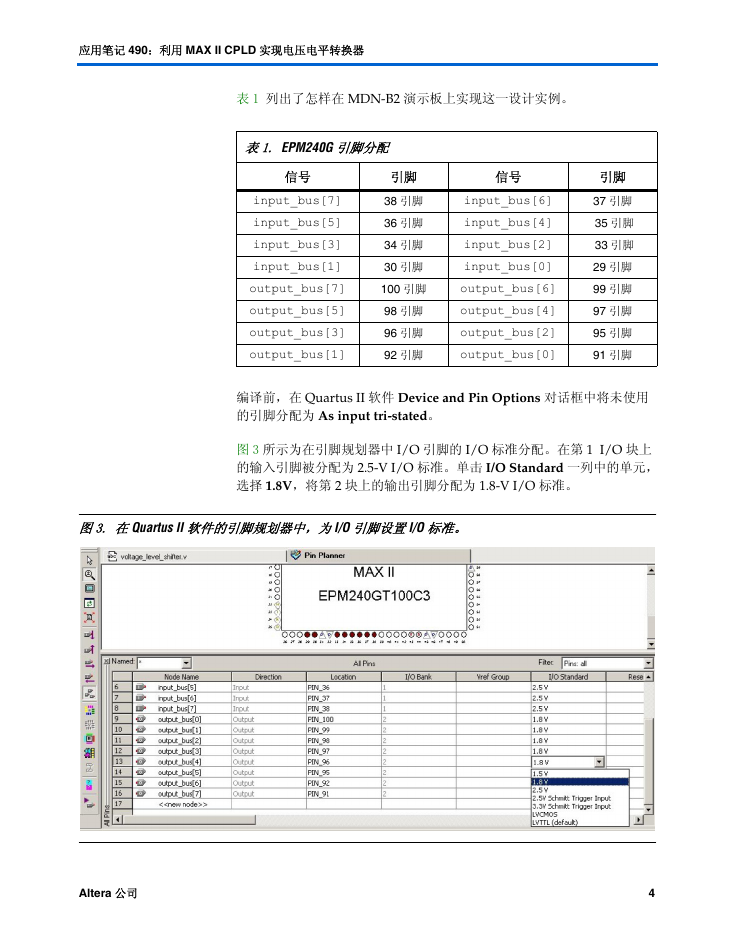

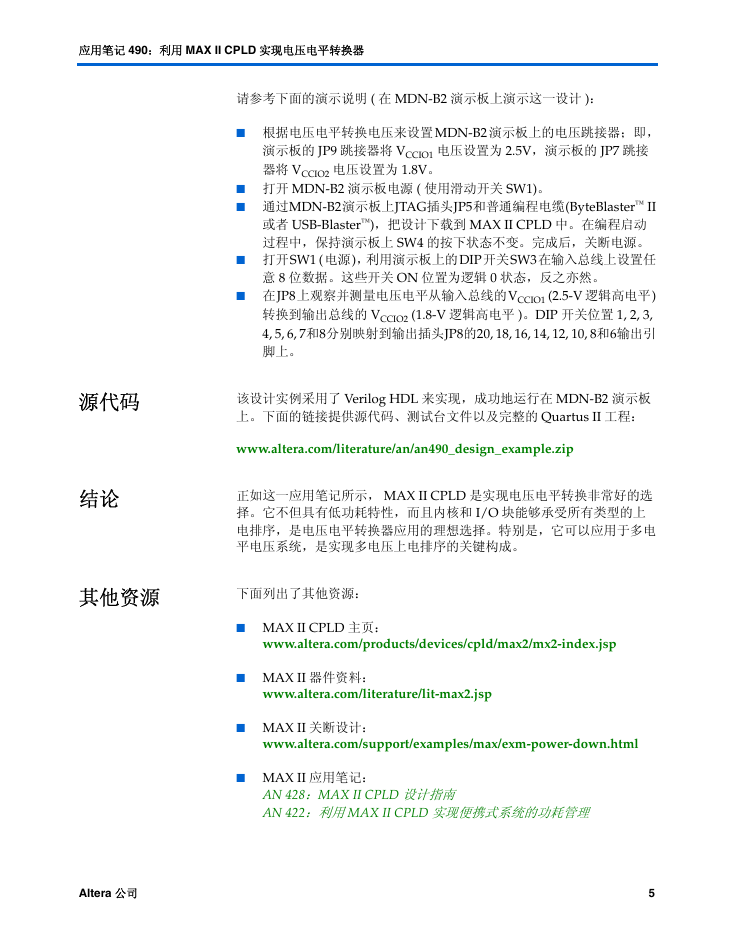

表 1 列出了怎样在 MDN-B2 演示板上实现这一设计实例。

表1. EPM240G 引脚分配

信号

input_bus[7]

input_bus[5]

input_bus[3]

input_bus[1]

output_bus[7]

output_bus[5]

output_bus[3]

output_bus[1]

引脚

38 引脚

36 引脚

34 引脚

30 引脚

100 引脚

98 引脚

96 引脚

92 引脚

信号

input_bus[6]

input_bus[4]

input_bus[2]

input_bus[0]

output_bus[6]

output_bus[4]

output_bus[2]

output_bus[0]

引脚

37 引脚

35 引脚

33 引脚

29 引脚

99 引脚

97 引脚

95 引脚

91 引脚

编译前,在 Quartus II 软件 Device and Pin Options 对话框中将未使用

的引脚分配为 As input tri-stated。

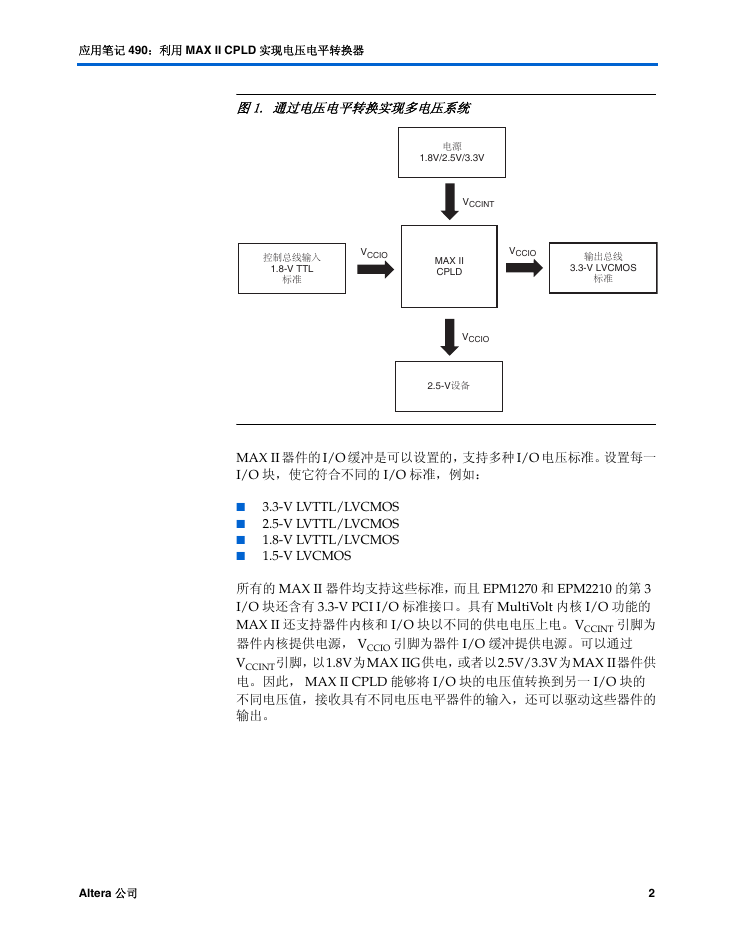

图 3 所示为在引脚规划器中 I/O 引脚的 I/O 标准分配。在第 1 I/O 块上

的输入引脚被分配为 2.5-V I/O 标准。单击 I/O Standard 一列中的单元,

选择 1.8V,将第 2 块上的输出引脚分配为 1.8-V I/O 标准。

图3. 在Quartus II 软件的引脚规划器中,为I/O 引脚设置I/O 标准。

Altera 公司

4

�

应用笔记 490:利用 MAX II CPLD 实现电压电平转换器

请参考下面的演示说明 ( 在 MDN-B2 演示板上演示这一设计 ):

■ 根据电压电平转换电压来设置 MDN-B2 演示板上的电压跳接器;即,

演示板的 JP9 跳接器将 VCCIO1 电压设置为 2.5V,演示板的 JP7 跳接

器将 VCCIO2 电压设置为 1.8V。

■ 打开 MDN-B2 演示板电源 ( 使用滑动开关 SW1)。

■ 通过MDN-B2演示板上JTAG插头JP5和普通编程电缆(ByteBlaster™ II

或者 USB-Blaster™),把设计下载到 MAX II CPLD 中。在编程启动

过程中,保持演示板上 SW4 的按下状态不变。完成后,关断电源。

■ 打开SW1 (电源),利用演示板上的DIP开关SW3在输入总线上设置任

意 8 位数据。这些开关 ON 位置为逻辑 0 状态,反之亦然。

■ 在JP8 上观察并测量电压电平从输入总线的VCCIO1 (2.5-V 逻辑高电平)

转换到输出总线的 VCCIO2 (1.8-V 逻辑高电平 )。DIP 开关位置 1, 2, 3,

4, 5, 6, 7和8分别映射到输出插头JP8的20, 18, 16, 14, 12, 10, 8和6输出引

脚上。

源代码

该设计实例采用了 Verilog HDL 来实现,成功地运行在 MDN-B2 演示板

上。下面的链接提供源代码、测试台文件以及完整的 Quartus II 工程:

www.altera.com/literature/an/an490_design_example.zip

结论

正如这一应用笔记所示, MAX II CPLD 是实现电压电平转换非常好的选

择。它不但具有低功耗特性,而且内核和 I/O 块能够承受所有类型的上

电排序,是电压电平转换器应用的理想选择。特别是,它可以应用于多电

平电压系统,是实现多电压上电排序的关键构成。

其他资源

下面列出了其他资源:

■ MAX II CPLD 主页:

www.altera.com/products/devices/cpld/max2/mx2-index.jsp

■ MAX II 器件资料:

www.altera.com/literature/lit-max2.jsp

■ MAX II 关断设计:

www.altera.com/support/examples/max/exm-power-down.html

■ MAX II 应用笔记:

AN 428:MAX II CPLD 设计指南

AN 422:利用MAX II CPLD 实现便携式系统的功耗管理

Altera 公司

5

�

应用笔记 490:利用 MAX II CPLD 实现电压电平转换器

版本历史

表 2 列出了本应用笔记的版本历史。

表2. 版本历史

日期和文档版本

进行的改动

2007 年 12 月, 1.0 版 初次发布

注释

—

6

Altera 公司

�

应用笔记 490:利用 MAX II CPLD 实现电压电平转换器

101 Innovation Drive

San Jose, CA 95134

www.altera.com

Literature Services:

literature@altera.com

版权 © 2007 Altera 公司。保留所有版权。Altera、可编程解决方案公司、程式

化 Altera 标识、专用器件名称和所有其他专有商标或者服务标记,除非特别声

明,均为 Altera 公司在美国和其他国家的商标和服务标记。所有其他产品或者

服务名称的所有权属于其各自持有人。 Altera 产品受美国和其他国家多种专

利、未决应用、模板著作权和版权的保护。Altera 保证当前规范下的半导体产

品性能与 Altera 标准质保一致,但是保留对产品和服务在没有事先通知时的升

级变更权利。除非与 Altera 公司的书面条款完全一致,否则 Altera 不承担由此

处所述信息、产品或者服务导致的责任。Altera 建议客户在决定购买产品或者

服务,以及确信任何公开信息之前,阅读 Altera 最新版的器件规范说明。

Altera 公司

7

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc