编号:010X007

基于 FPGA 的数字示波器

参赛学校:山东大学

所在院系:信息科学与工程学院

参赛队员:刘希彤 15216407513

杨鑫阳 18769785073

李海金 18769780239

�

摘要:

本系统主要由宽带直流放大器、A/D、D/A、FPGA、VGA 组成,前级运算放大

器将0~20mv 的小信号放大后,送入 A/D 进行模数转换,FPGA 接收 A/D 送出的

数字信号后进行处理,驱动 VGA 显示输入信号的波形,同时进行频率和峰峰值

的测量。最后,将数字信号输出给 D/A 还原波形。经测试,系统整体工作稳定,

效果良好。

关键字:宽带直流放大;FPGA;VGA;数字示波器;

Abstract:

This system is mainly composed of broadband DC amplifier ,ADC, DAC ,FPGA and

VGA. The DC amplifier amplifys the analog signal and send it to the ADC to be

converted into digital signal. Then FPGA receives the signal and process it,driving

the VGA to display waveforms, and at the same time, measuring frequency and

peak-to-peak voltage value. Finally,DAC gets the processed data and restore the

analog signal (waveform which has the half peak-to-peak voltage value compared

with the amplifier). After tested, the whole system operates stably and produce

excellent effects.

Key words:Small-signal amplification; FPGA;VGA; Digital oscilloscope;

1

�

一、 系统方案

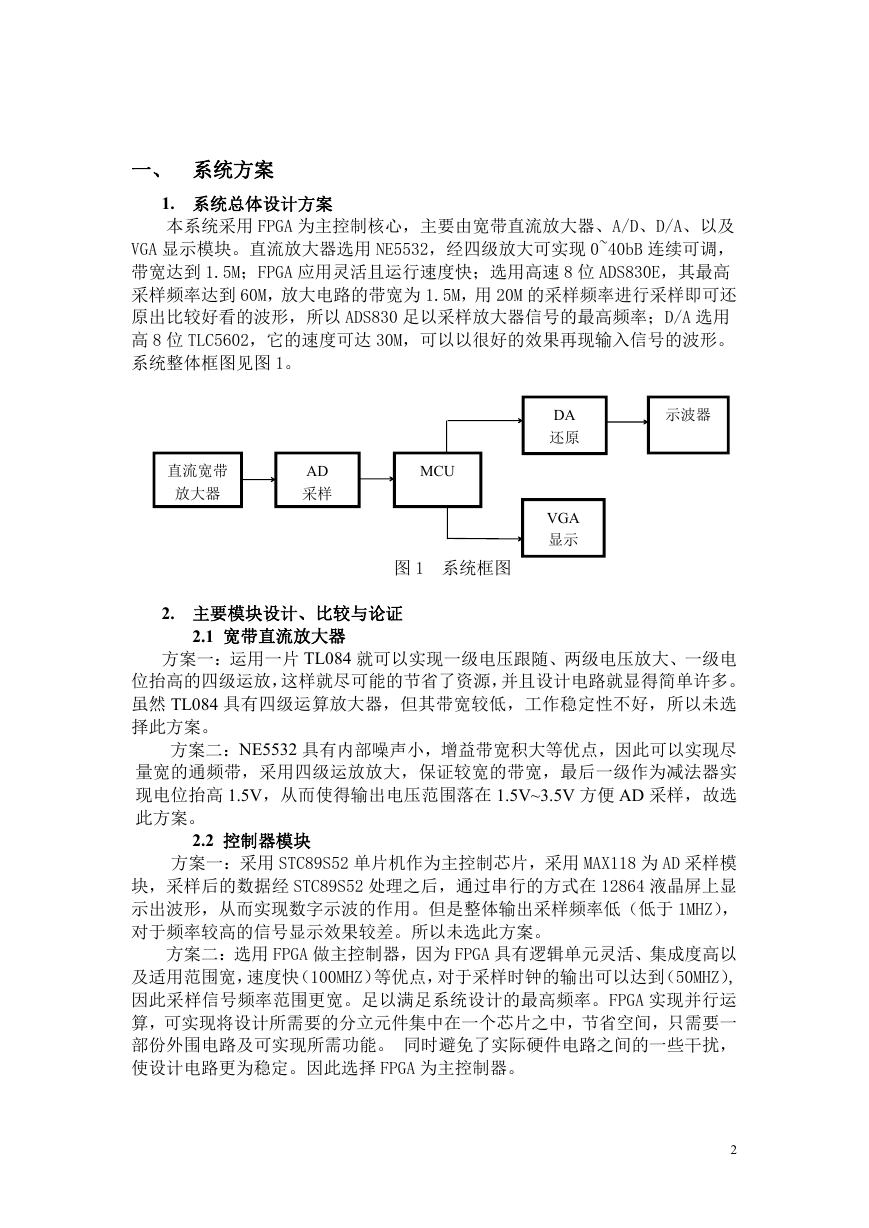

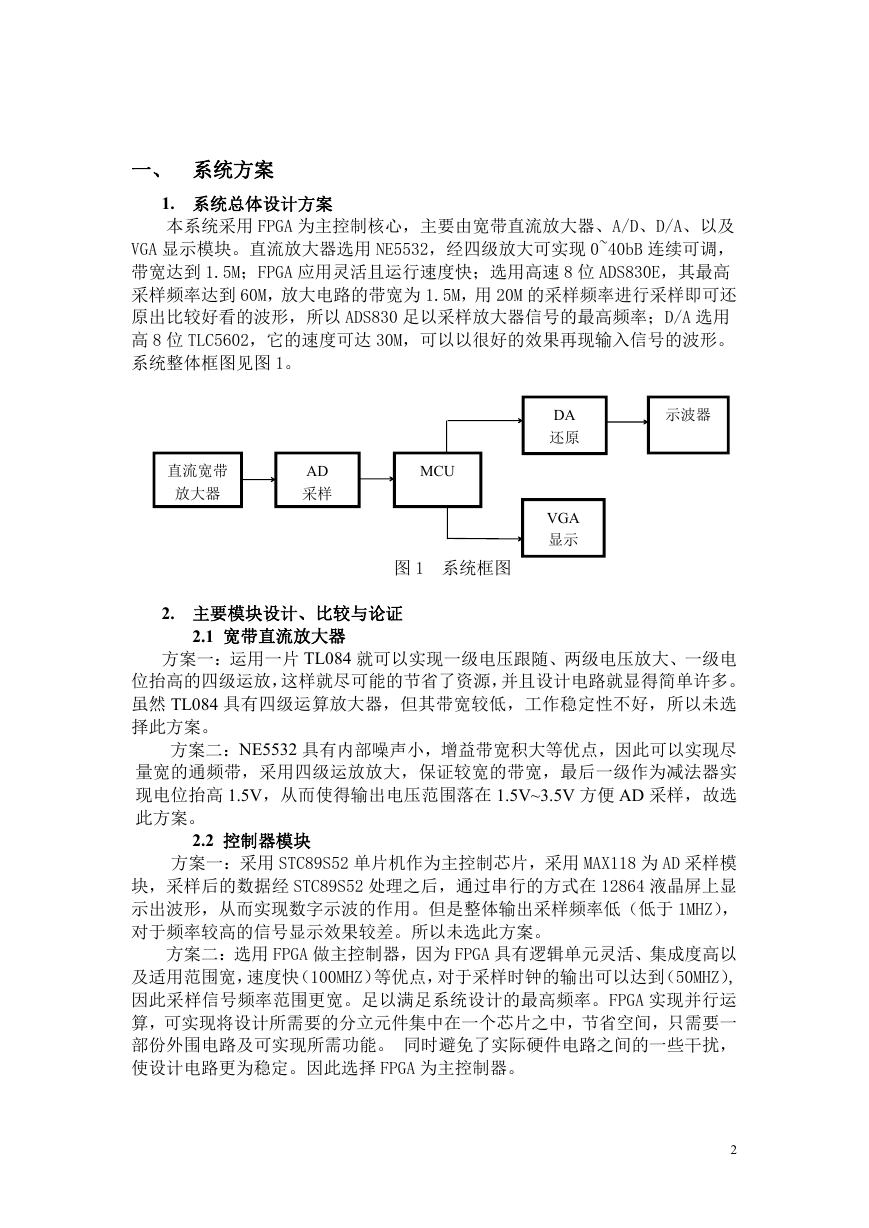

1. 系统总体设计方案

本系统采用 FPGA 为主控制核心,主要由宽带直流放大器、A/D、D/A、以及

VGA 显示模块。直流放大器选用 NE5532,经四级放大可实现 0~40bB 连续可调,

带宽达到 1.5M;FPGA 应用灵活且运行速度快;选用高速 8 位 ADS830E,其最高

采样频率达到 60M,放大电路的带宽为 1.5M,用 20M 的采样频率进行采样即可还

原出比较好看的波形,所以 ADS830 足以采样放大器信号的最高频率;D/A 选用

高 8 位 TLC5602,它的速度可达 30M,可以以很好的效果再现输入信号的波形。

系统整体框图见图 1。

直流宽带

放大器

AD

采样

MCU

图 1 系统框图

示波器

DA

还原

VGA

显示

2. 主要模块设计、比较与论证

2.1 宽带直流放大器

方案一:运用一片 TL084 就可以实现一级电压跟随、两级电压放大、一级电

位抬高的四级运放,这样就尽可能的节省了资源,并且设计电路就显得简单许多。

虽然 TL084 具有四级运算放大器,但其带宽较低,工作稳定性不好,所以未选

择此方案。

方案二:NE5532 具有内部噪声小,增益带宽积大等优点,因此可以实现尽

量宽的通频带,采用四级运放放大,保证较宽的带宽,最后一级作为减法器实

现电位抬高 1.5V,从而使得输出电压范围落在 1.5V~3.5V 方便 AD 采样,故选

此方案。

2.2 控制器模块

方案一:采用 STC89S52 单片机作为主控制芯片,采用 MAX118 为 AD 采样模

块,采样后的数据经 STC89S52 处理之后,通过串行的方式在 12864 液晶屏上显

示出波形,从而实现数字示波的作用。但是整体输出采样频率低(低于 1MHZ),

对于频率较高的信号显示效果较差。所以未选此方案。

方案二:选用 FPGA 做主控制器,因为 FPGA 具有逻辑单元灵活、集成度高以

及适用范围宽,速度快(100MHZ)等优点,对于采样时钟的输出可以达到(50MHZ),

因此采样信号频率范围更宽。足以满足系统设计的最高频率。FPGA 实现并行运

算,可实现将设计所需要的分立元件集中在一个芯片之中,节省空间,只需要一

部份外围电路及可实现所需功能。 同时避免了实际硬件电路之间的一些干扰,

使设计电路更为稳定。因此选择 FPGA 为主控制器。

2

�

2.3 AD 芯片的选择

方案一:ADC0809 是一款 8 位逐次逼近式 A/D 转换芯片 ,它体积小,兼

容性好,性价比高,但是比同类并行 A/D 速度较慢,工作频率为 10KHZ,转换

时间为 100μS ,工作频率太低,转换速度慢对于要求的最高 20M,其远远不

能胜任。

方案二:A/D 选用 ADS830E ,性价比较高,采样工作频率可达 65MHZ,足

以采集本系统的最高频率,且由于 FPGA 丰富的 IO 资源,采用并行输出,输出

速度快。时序简单,控制器 verilog 编程较易,因此选择此方案。

2.4 DA 芯片的选择

方案一:采用 MAX518 芯片是一种采用二线串行接口的 8 位 D/A 转换芯片,

采用单 5V 供电,具有两路 8 位模拟量输出口。MAX518 是 8 位电压输出型数摸

转换器,但其速度慢,不能还原频率较高的信号。

方案二:采用 TLC5602 是一款高速 8 位电压输出 DA 转换器,其最高速度

可达 30M,供电电压为 5V,用系统电源供电即可。使用方便,电路简单,故选

此方案。

二、 理论分析与参数设计

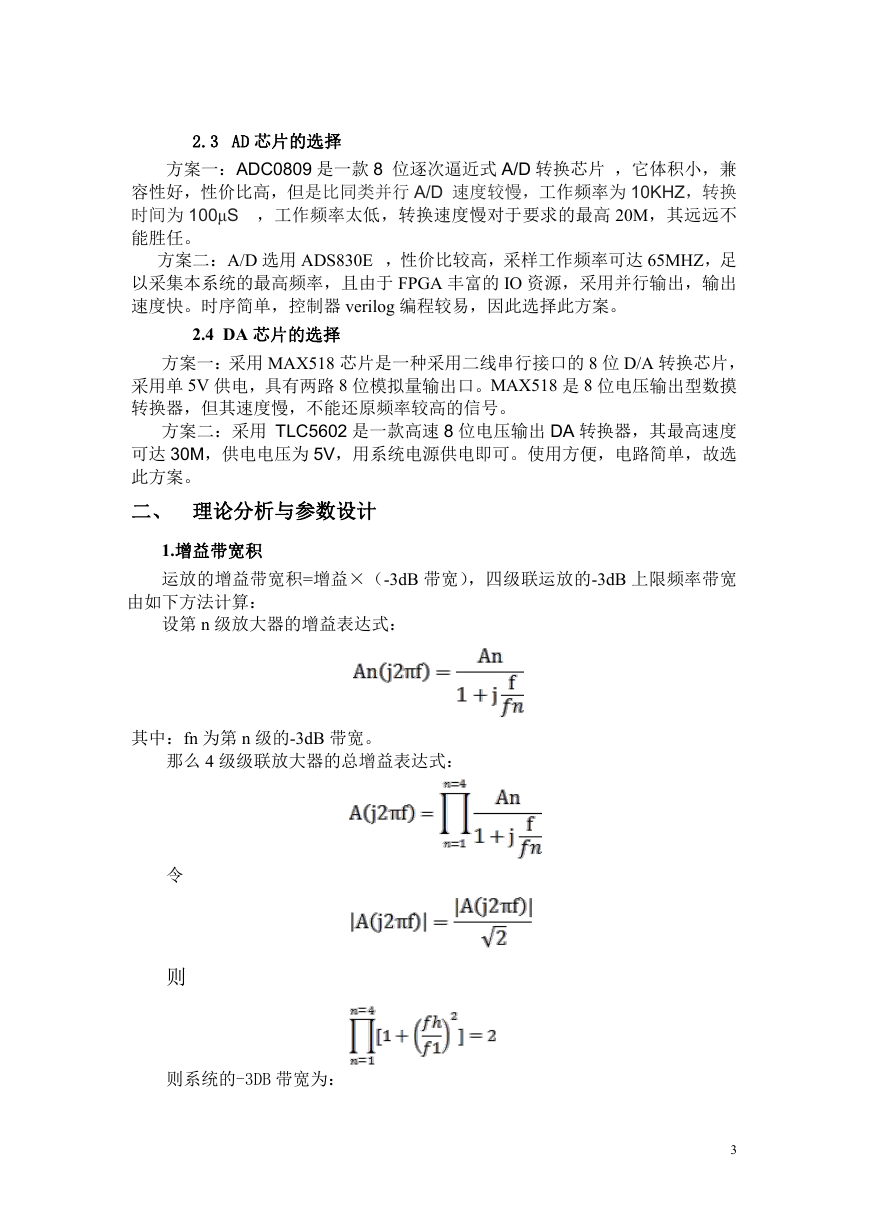

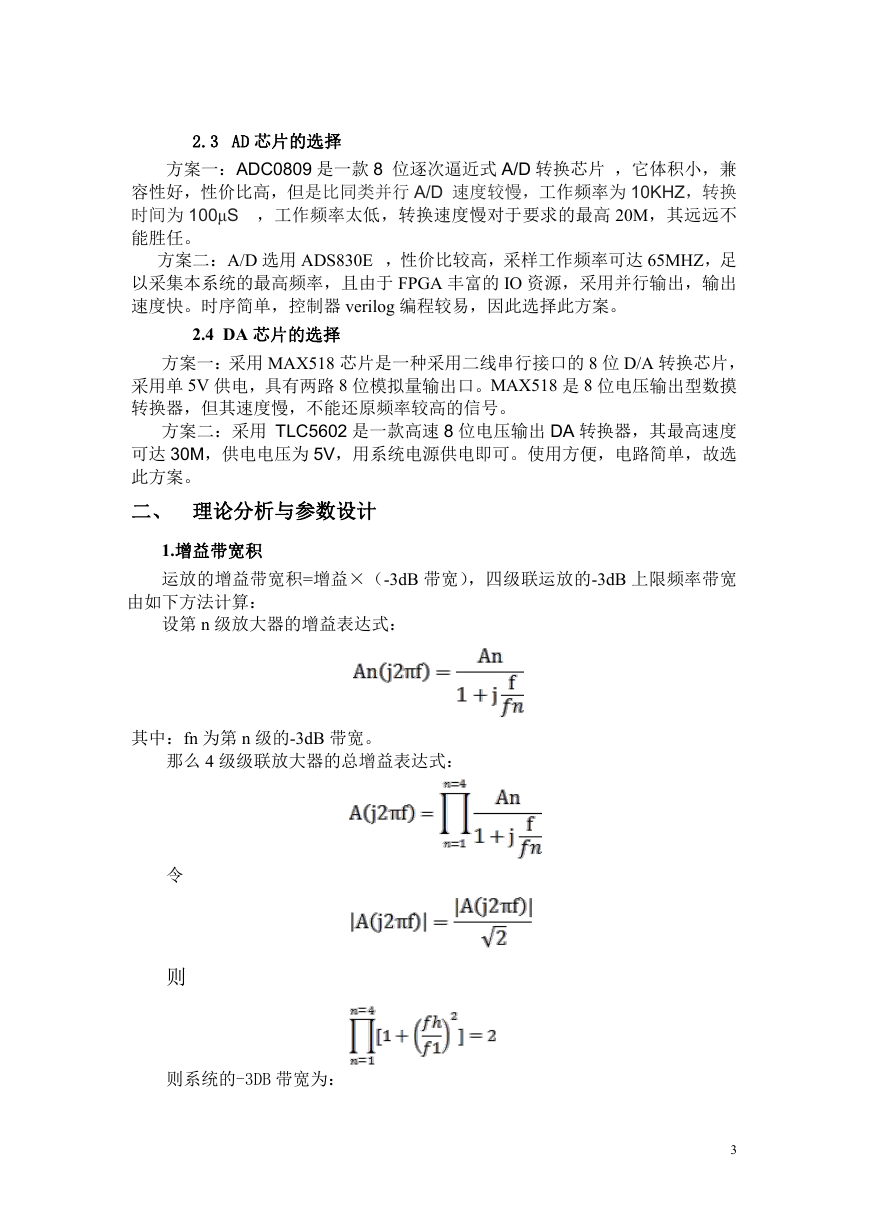

1.增益带宽积

运放的增益带宽积=增益×(-3dB 带宽),四级联运放的-3dB 上限频率带宽

由如下方法计算:

设第 n 级放大器的增益表达式:

其中:fn 为第 n 级的-3dB 带宽。

那么 4 级级联放大器的总增益表达式:

令

则

则系统的-3DB 带宽为:

3

�

经测试,本设计的 3db 带宽可达到 1.5MH

三、功能测试与结果分析

1. 10mv 输入测试指标

表 1

10mv 输入测试指标

10DB

20DB

30DB

40DB

10mv 输

入

1DB 带宽

3DB 带宽

1334 KHz

1548 KHz

1380 KHz

1513KHz

1341 KHz

1517 KHz

增益带宽积

4.89MHz

15.13MHz

47.94MHz

1264KHz

1503 KHz

150.3MHz

2.1mv 输入测试指标

表 2

1mv 输入测试指标

1mv 输入

10DB

不可测

1DB 带宽

3DB 带宽

不可测

增益带宽积 不可测

20DB

1670KHz

1832 KHz

18.32MHz

30DB

40DB

1663 KHz

1759 KHz

55.58MHz

1773 KHz

1901 KHz

190.1MHz

3. 输入电阻测量

调节信号发生器,测得信号发生器的开路输出为 220mv,将信号发生器

的输出端连接到直流放大器的输入端,测得此时的输入信号大小 116mv。

已知信号发生器的输出电阻为 50 欧,根据电阻分压原理的放大器的输入

电阻为:49.989Ω。

4. 输出电阻测量

调节信号发生器,使其输出一个 20mv,测得放大器的开路输出为 2.04V,

在放大器的输出端接一个 33Ω的电阻测得电阻两端的电压为 2.01V,估

的放大器的输出电阻约为 0Ω。

5. 幅值测量

1mV 输入幅值测量

表 3

1mv 输入

10DB

数字显示值 不可测

实际测量值 不可测

20DB

11mv

14mv

表 4

10mV 输入幅值测量

10mv 输入 10DB

数字显示值 32.5mv

实际测量值 34mv

20DB

103mv

96mv

30DB

33mv

28mv

30DB

310mv

301mv

40DB

103mv

95mv

40DB

1012mv

1023mv

4

�

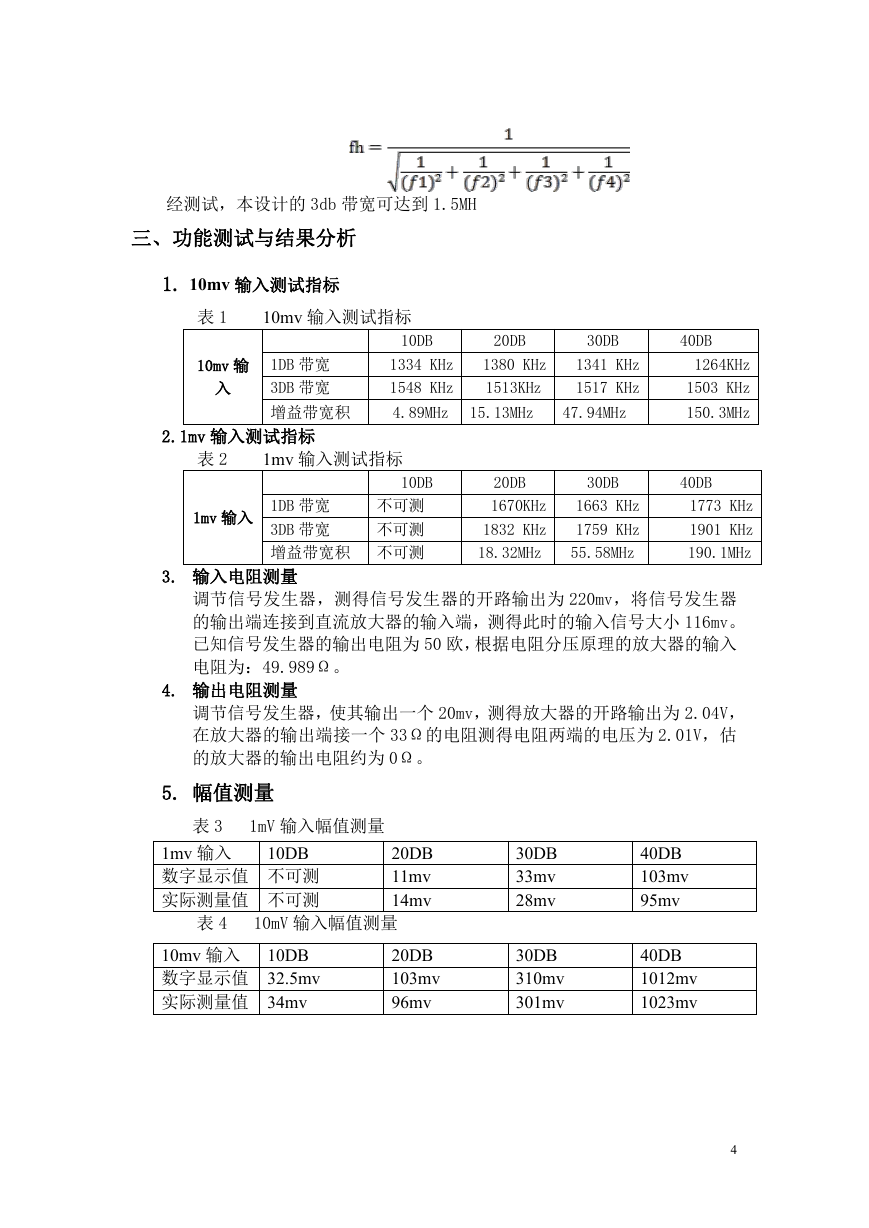

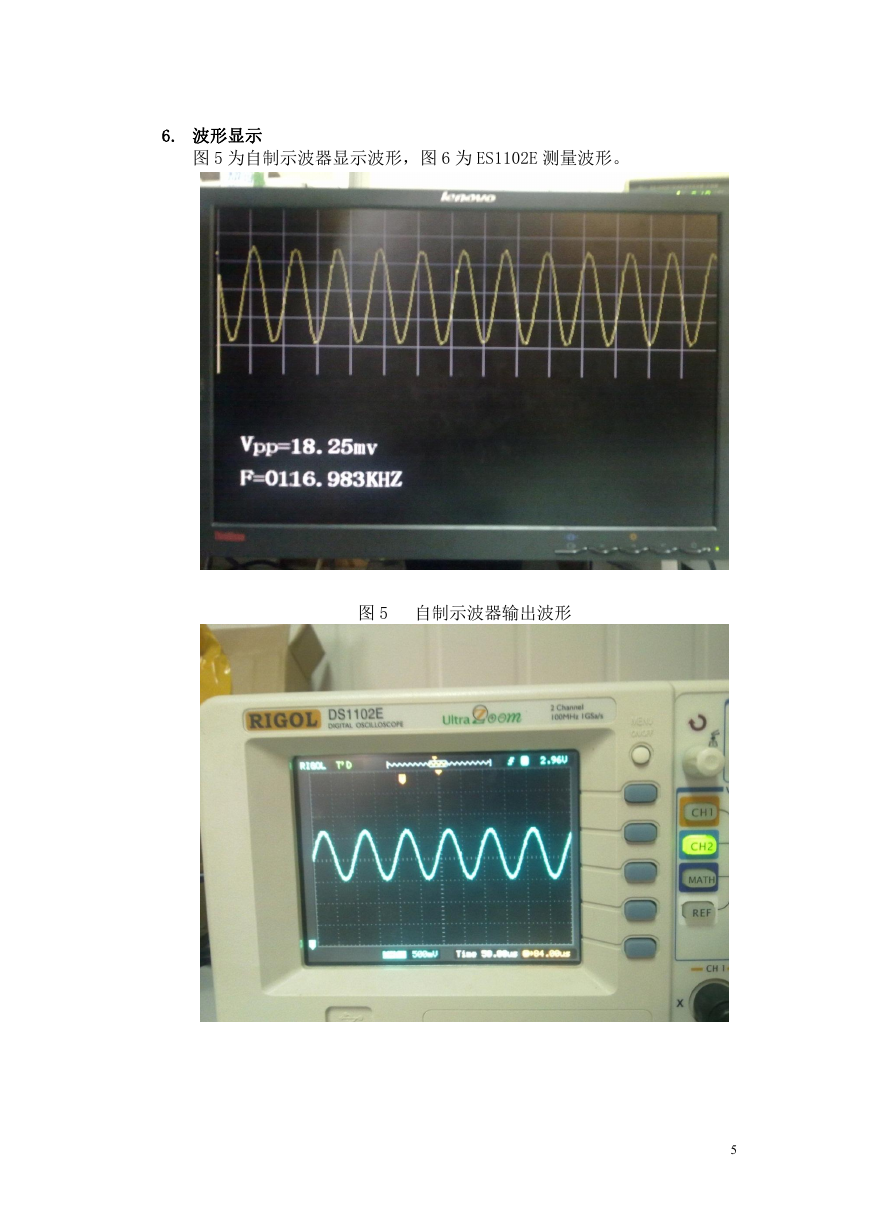

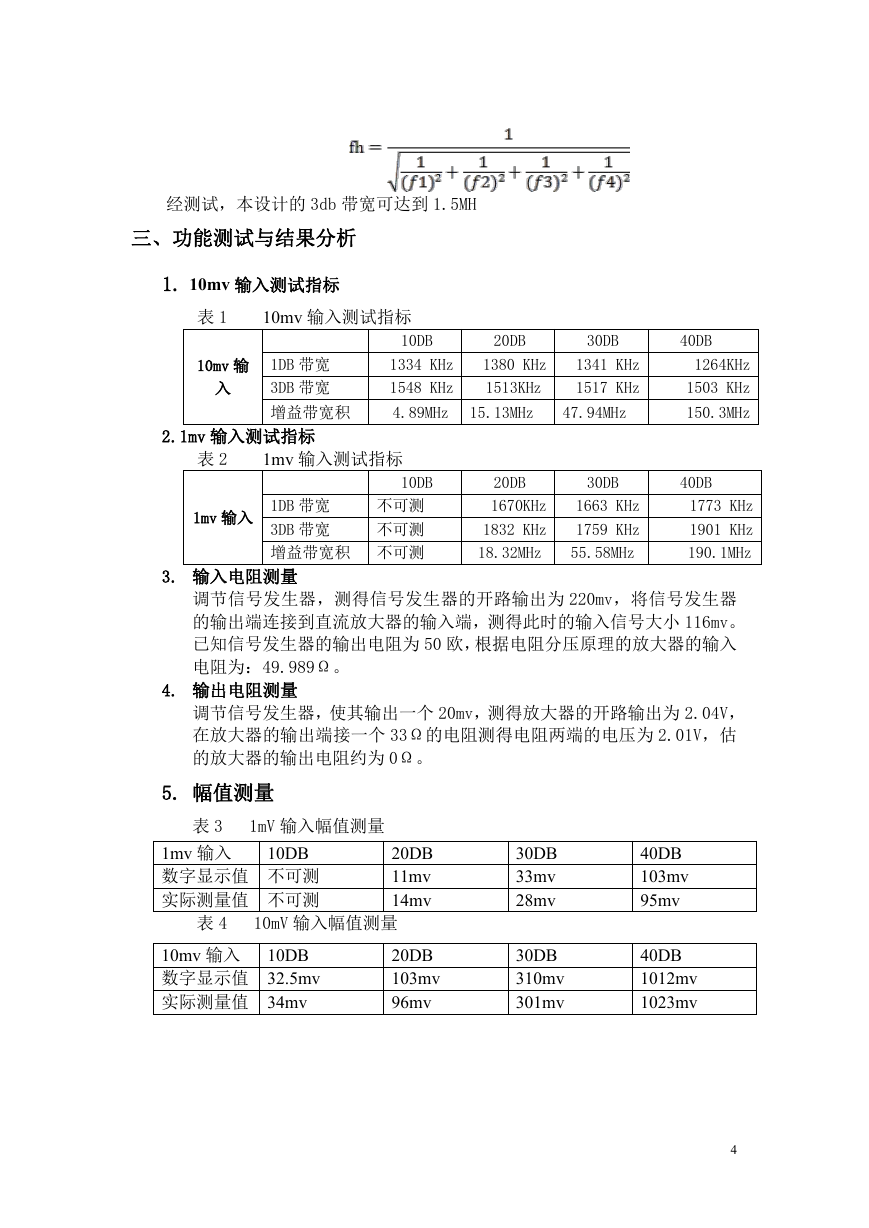

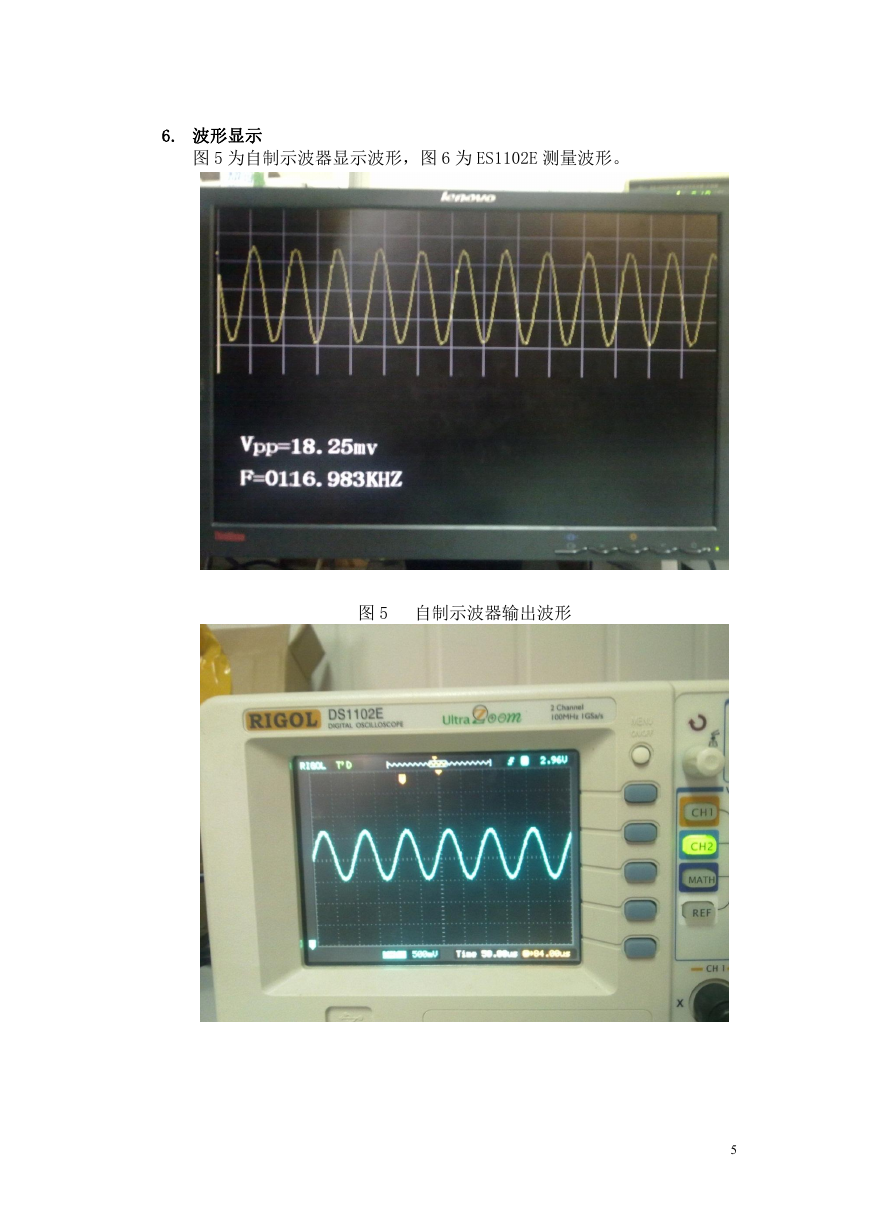

6. 波形显示

图 5 为自制示波器显示波形,图 6 为 ES1102E 测量波形。

图 5 自制示波器输出波形

5

�

图 6

ES1102E 测量波形

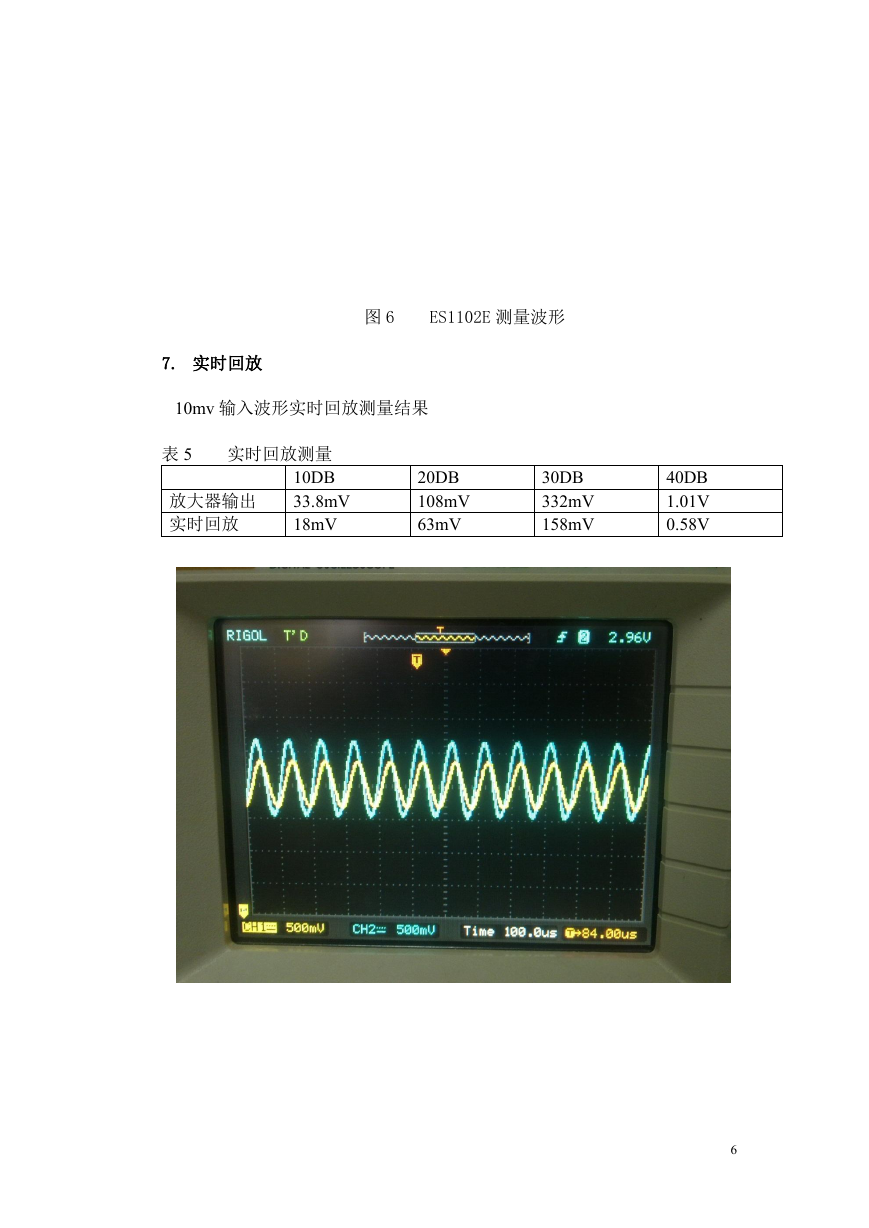

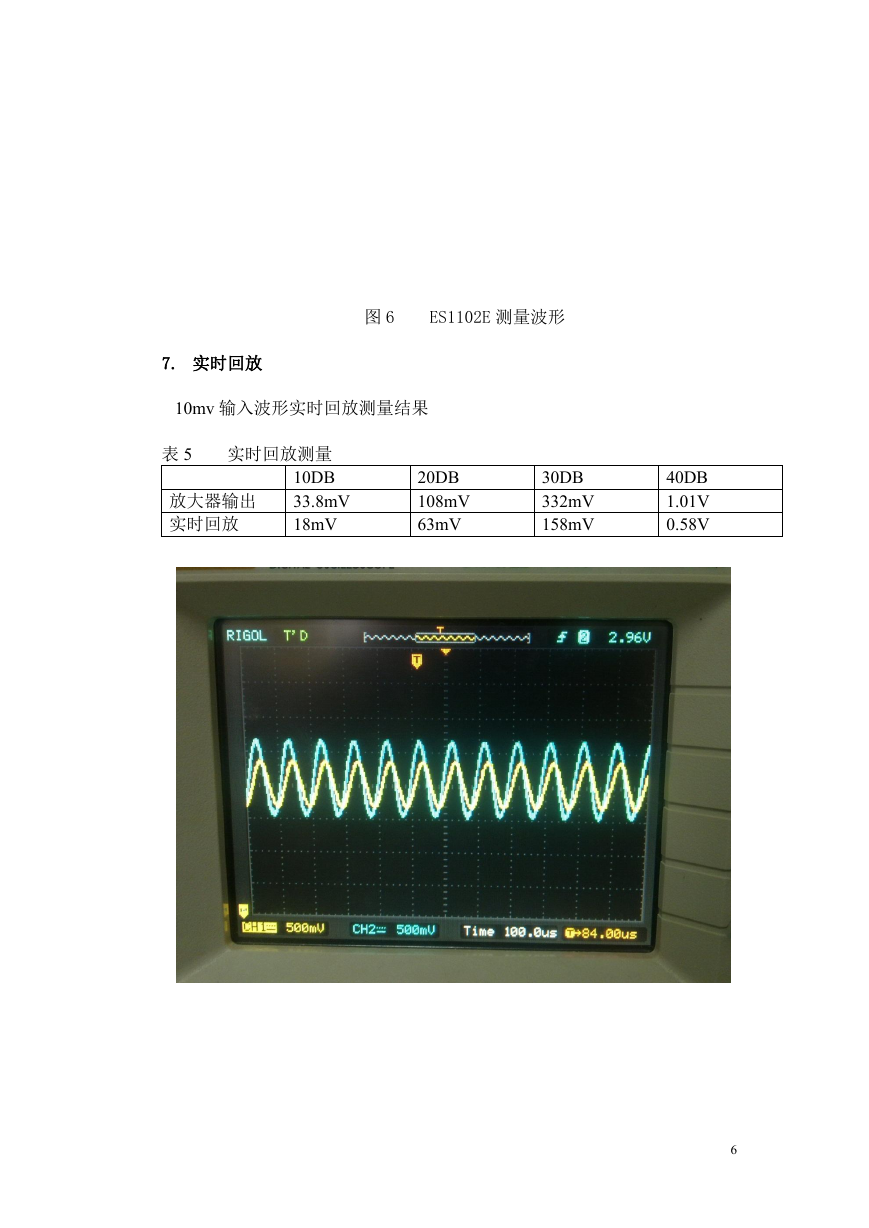

7. 实时回放

10mv 输入波形实时回放测量结果

表 5

实时回放测量

10DB

33.8mV

18mV

放大器输出

实时回放

20DB

108mV

63mV

30DB

332mV

158mV

40DB

1.01V

0.58V

6

�

三、 结论与收获

图 7 实时回放波形

本系统充分应用 FPGA 的高速处理能力,是整个系统可以完美的还原 2M 的波

形,我们熟练使用了 ISE 的 Verilog 编程,并经过电路部分的设计与调试,

最终完成了整个系统的制作,每位队员都有很大的收获。系统测试运行效果

良好,工作稳定。

四、参考文献

[1]. 王金明. Verilog HDL 程序设计教程 2004.0.1

[2]. 孙肖子,等.模拟电子电路及基础技术 2008.02

[3]. Richard E.Haskell Darrin M.Hanna.FPGA 数字逻辑设计教程

[4]. 阎石. 数字电子技术基础

五、附录

1. 宽带直流放大器模块电路

7

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc