Omni

ision ®

Advanced Information

Preliminary Datasheet

OV2640 Color CMOS UXGA (2.0 MegaPixel) CAMERACHIPTM Sensor

with OmniPixel2TM Technology

Applications

General Description

The OV2640 CAMERACHIP™ image sensor is a low voltage

CMOS device that provides the full functionality of a

single-chip UXGA (1632x1232) camera and image processor

in a small footprint package. The OV2640 provides full-frame,

sub-sampled, scaled or windowed 8-bit/10-bit images in a

wide range of formats, controlled through the Serial Camera

Control Bus (SCCB) interface.

This product has an image array capable of operating at up

to 15 frames per second (fps) in UXGA resolution with

complete user control over image quality, formatting and

output data transfer. All required image processing functions,

including exposure control, gamma, white balance, color

saturation, hue control, white pixel canceling, noise

canceling, and more, are also programmable through the

SCCB interface. The OV2640 also includes a compression

engine

In addition,

OmniVision CAMERACHIP sensors use proprietary sensor

technology

image quality by reducing or

eliminating common lighting/electrical sources of image

contamination, such as fixed pattern noise, smearing, etc., to

produce a clean, fully stable color image.

increased processing power.

for

to

improve

Pb

Note: The OV2640 uses a lead-free

package.

Features

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

High sensitivity for low-light operation

Low operating voltage for embedded portable apps

Standard SCCB interface

Output support for Raw RGB, RGB (RGB565/555),

GRB422, YUV (422/420) and YCbCr (4:2:2) formats

Supports image sizes: UXGA, SXGA, SVGA, and any

size scaling down from SXGA to 40x30

VarioPixel® method for sub-sampling

Automatic image control functions including Automatic

Exposure Control (AEC), Automatic Gain Control

(AGC), Automatic White Balance (AWB), Automatic

Band Filter (ABF), and Automatic Black-Level

Calibration (ABLC)

Image quality controls including color saturation,

gamma, sharpness (edge enhancement), lens

correction, white pixel canceling, noise canceling, and

50/60 Hz luminance detection

Line optical black level output capability

Video or snapshot operation

Zooming, panning, and windowing functions

Internal/external frame synchronization

Variable frame rate control

Supports LED and flash strobe mode

Supports scaling

Supports compression

Embedded microcontroller

Ordering Information

Product

Package

OV02640-VL9A (Color, lead-free)

38-pin CSP2

•

•

•

•

Cellular and Camera Phones

Toys

PC Multimedia

Digital Still Cameras

Key Specifications

Array Size

Power Supply

UXGA 1600 x 1200

Core 1.3VDC + 5%

Analog 2.5 ~ 3.0VDC

I/O 1.7V to 3.3V

125 mW (for 15 fps, UXGA

YUV mode)

140 mW (for 15 fps, UXGA

compressed mode)

Power

Requirements

Active

Standby 900 µA

Temperature

Range Stable Image 0°C to 50°C

Output Formats (8-bit)

• YUV(422/420)/YCbCr422

• RGB565/555

• 8-bit compressed data

• 8-/10-bit Raw RGB data

Lens Size 1/4"

Chief Ray Angle 25° non-linear

Maximum

Image

Transfer Rate

UXGA/SXGA 15 fps

SVGA 30 fps

CIF 60 fps

Sensitivity 0.6 V/Lux-sec

S/N Ratio 40 dB

Dynamic Range 50 dB

Scan Mode Progressive

Maximum Exposure Interval 1247 x tROW

Gamma Correction Programmable

Pixel Size 2.2 µm x 2.2 µm

Dark Current 15 mV/s at 60°C

Well Capacity 12 Ke

Fixed Pattern Noise <1% of VPEAK-TO-PEAK

Image Area 3590 µm x 2684 µm

Package Dimensions 5725 µm x 6285 µm

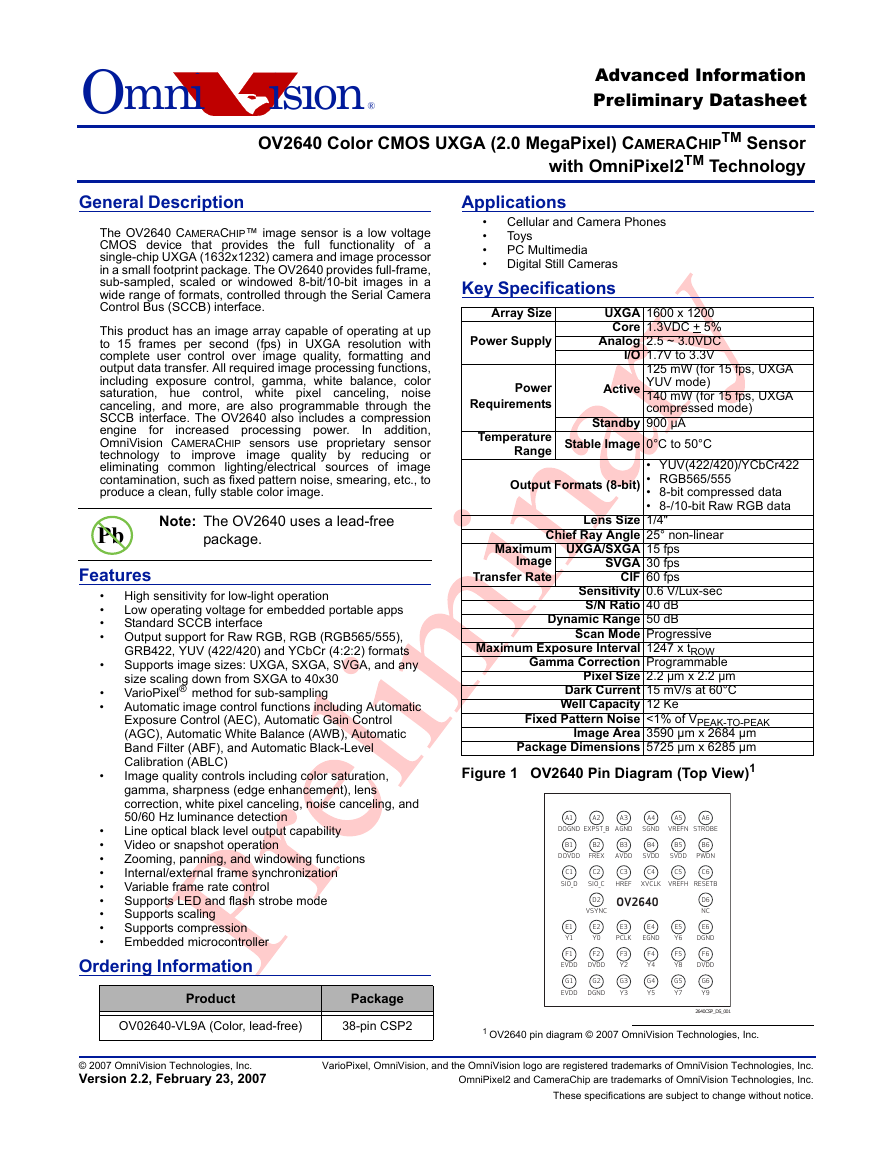

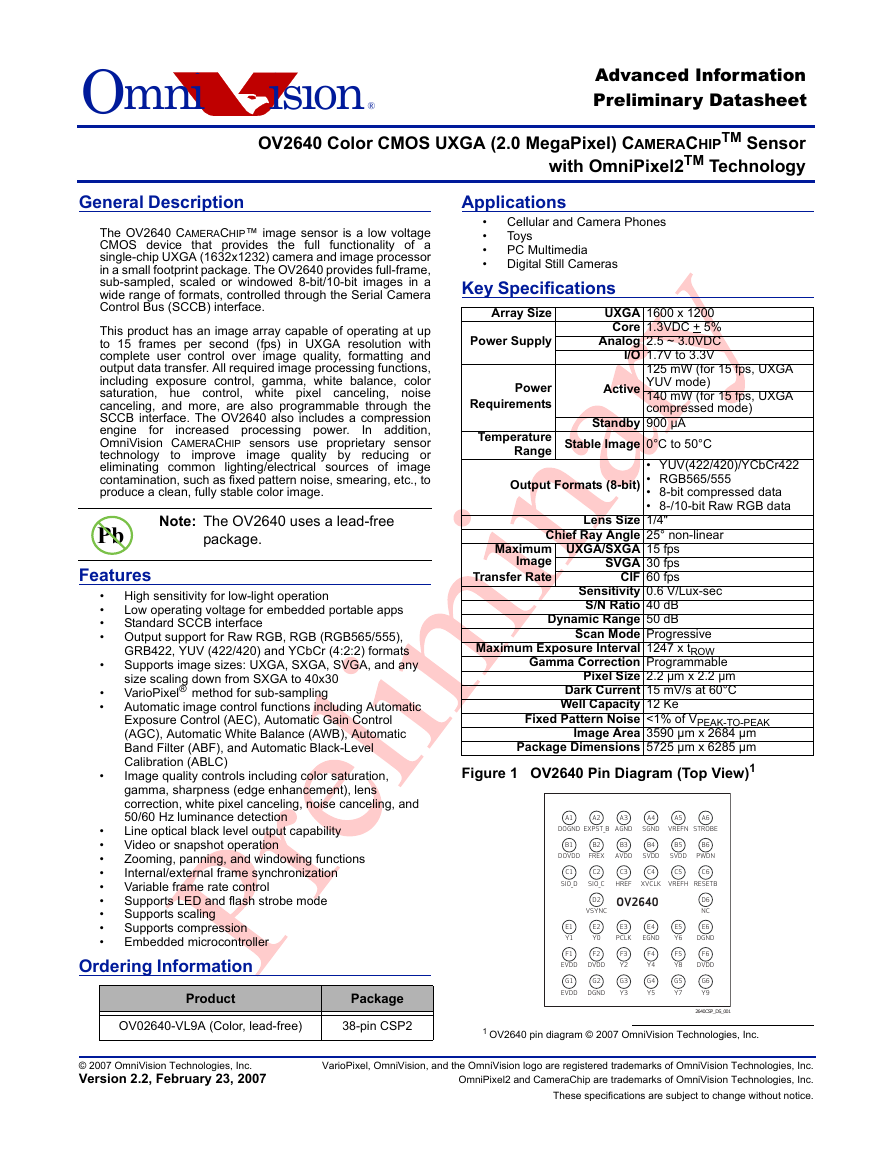

Figure 1 OV2640 Pin Diagram (Top View)1

A1

A2

A3

A4

A5

A6

DOGND

EXPST_B

AGND

SGND

VREFN

STROBE

B1

DOVDD

B2

FREX

B3

B4

B5

B6

AVDD

SVDD

SVDD

PWDN

C1

C2

C3

C4

C5

C6

SIO_D

SIO_C

HREF

XVCLK

VREFH

RESETB

D2

VSYNC

OV2640

E1

Y1

F1

E2

Y0

F2

EVDD

DVDD

G1

G2

EVDD

DGND

E3

PCLK

E4

EGND

F3

Y2

G3

Y3

F4

Y4

G4

Y5

E5

Y6

F5

Y8

G5

Y7

D6

NC

E6

DGND

F6

DVDD

G6

Y9

1 OV2640 pin diagram © 2007 OmniVision Technologies, Inc.

2640CSP_DS_001

© 2007 OmniVision Technologies, Inc.

Version 2.2, February 23, 2007

VarioPixel, OmniVision, and the OmniVision logo are registered trademarks of OmniVision Technologies, Inc.

OmniPixel2 and CameraChip are trademarks of OmniVision Technologies, Inc.

These specifications are subject to change without notice.

�

OV2640

Color CMOS UXGA (2.0 MegaPixel) OmniPixel2™ CAMERACHIP™ Sensor

Omni

ision

Functional Description

Image Sensor Array (1632 x 1232 total image array)

Analog Signal Processor

10-Bit A/D Converters

Digital Signal Processor (DSP)

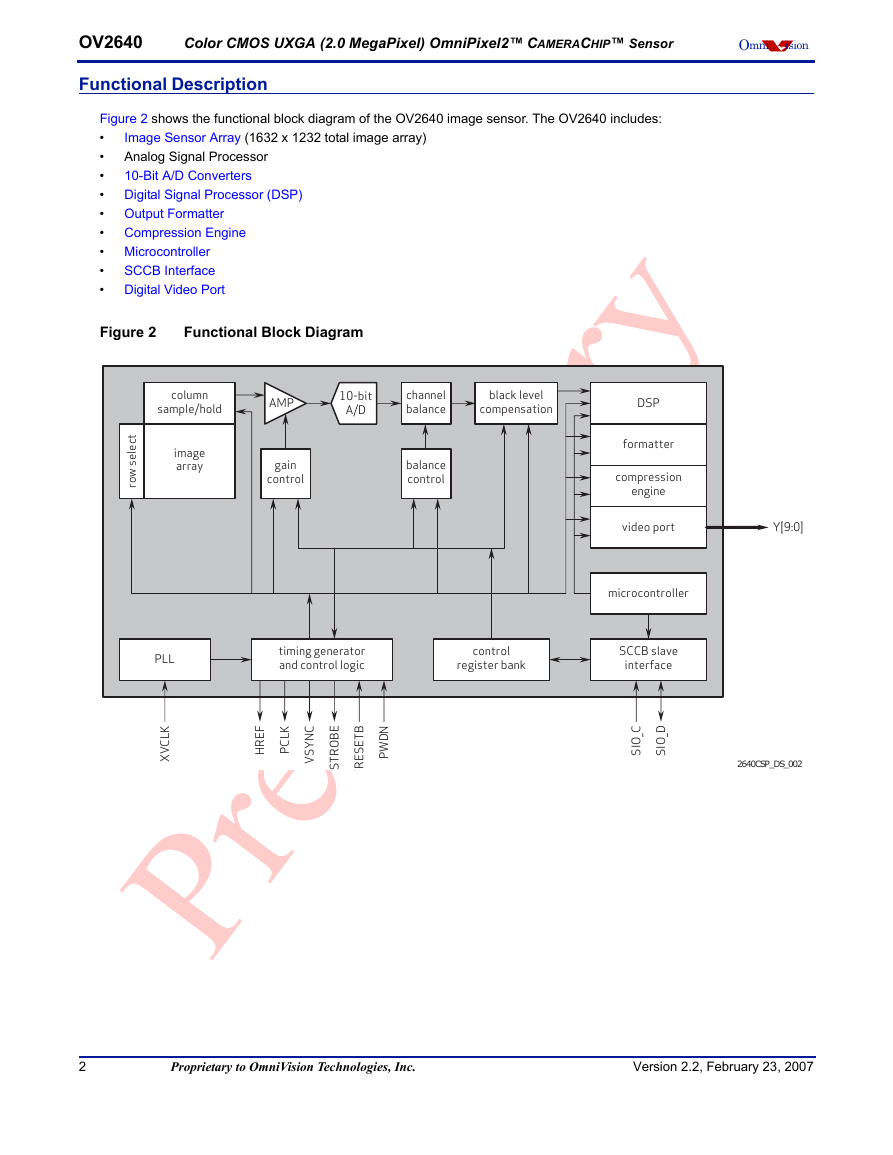

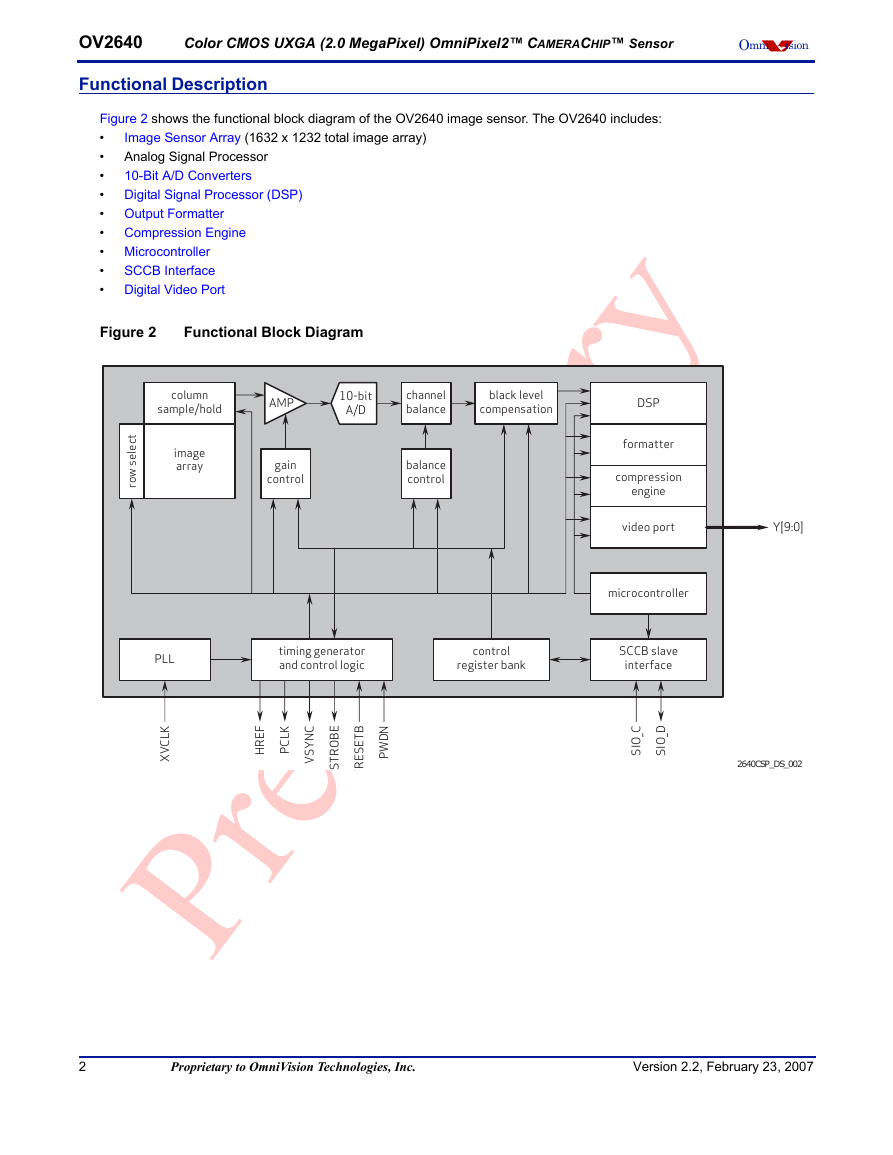

Figure 2 shows the functional block diagram of the OV2640 image sensor. The OV2640 includes:

•

•

•

•

• Output Formatter

•

• Microcontroller

•

SCCB Interface

Digital Video Port

•

Compression Engine

Figure 2 Functional Block Diagram

column

sample/hold

AMP

10-bit

A/D

channel

balance

black level

compensation

t

c

e

l

e

s

w

o

r

image

array

gain

control

balance

control

DSP

formatter

compression

engine

video port

Y[9:0]

microcontroller

timing generator

and control logic

control

register bank

SCCB slave

interface

F

E

R

H

K

L

C

P

C

N

Y

S

V

E

B

O

R

T

S

B

T

E

S

E

R

N

D

W

P

_

C

O

S

I

_

D

O

S

I

2640CSP_DS_002

PLL

K

L

C

V

X

2

Proprietary to OmniVision Technologies, Inc.

Version 2.2, February 23, 2007

�

Omni

ision

Functional Description

Image Sensor Array

10-Bit A/D Converters

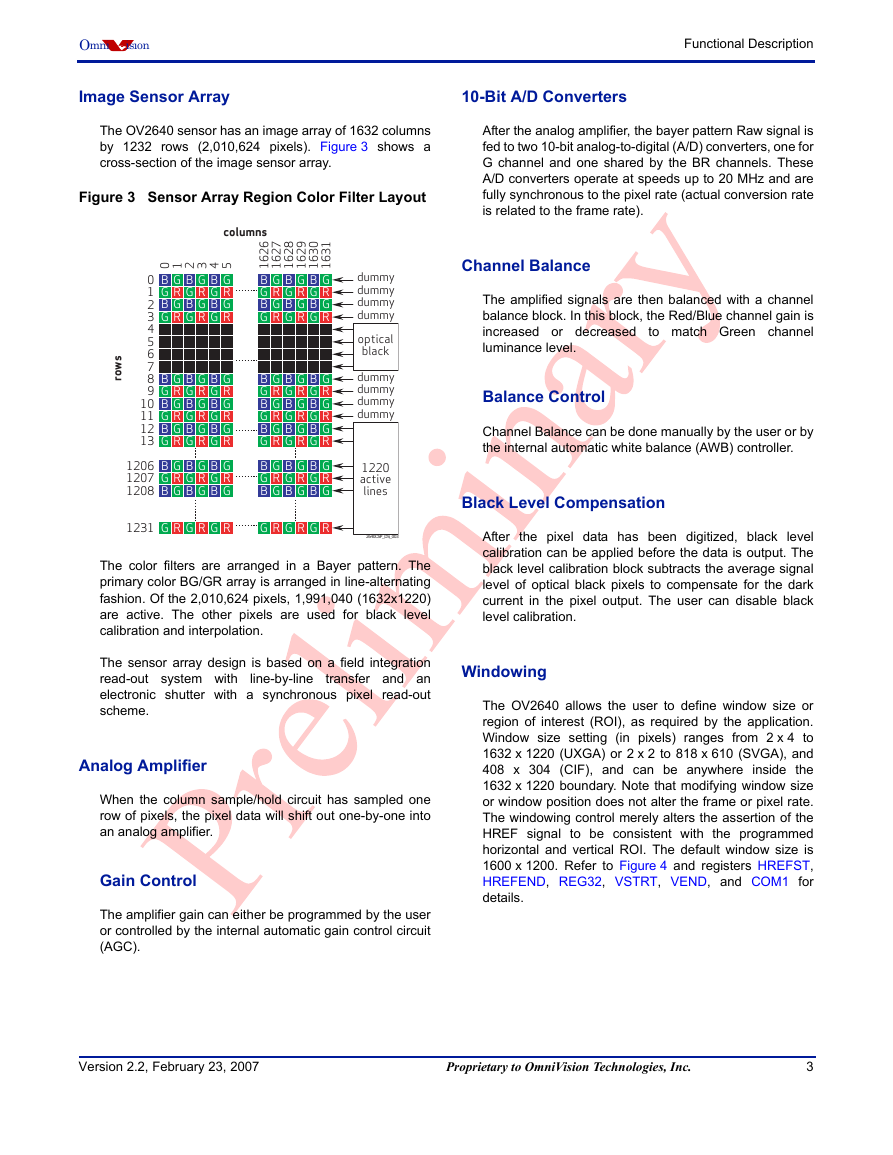

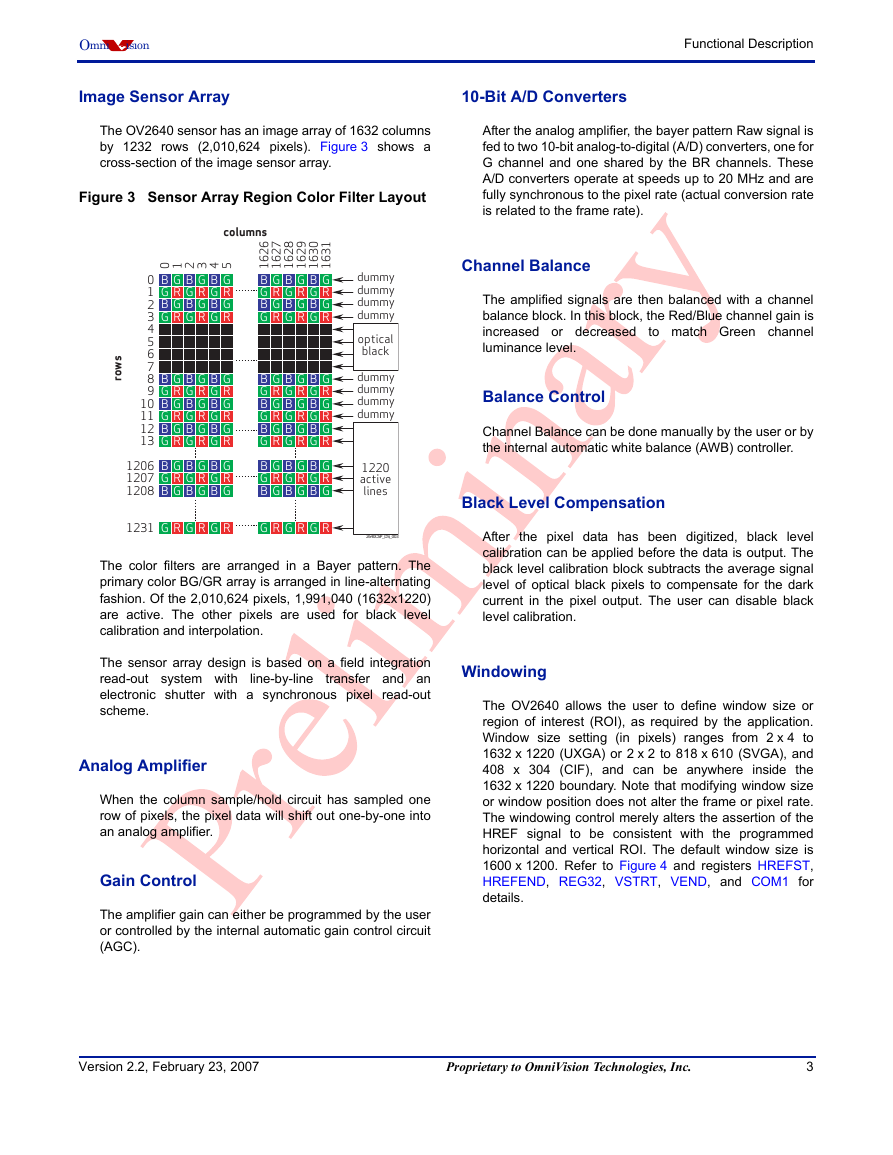

The OV2640 sensor has an image array of 1632 columns

by 1232 rows (2,010,624 pixels). Figure 3 shows a

cross-section of the image sensor array.

Figure 3 Sensor Array Region Color Filter Layout

After the analog amplifier, the bayer pattern Raw signal is

fed to two 10-bit analog-to-digital (A/D) converters, one for

G channel and one shared by the BR channels. These

A/D converters operate at speeds up to 20 MHz and are

fully synchronous to the pixel rate (actual conversion rate

is related to the frame rate).

columns

6

2

6

012345 1

7

2

6

1

8

2

6

1

9

2

6

1

0

3

6

1

1

3

6

1

s

w

o

r

0

1

2

3

4

5

6

7

8

9

10

11

12

13

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

1206

1207

1208

B G

G R

B G

B G

G R

G R

B G B G B G

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

B G

G R

G R

B G B G B G

1231

G R G R G R

G R G R G R

dummy

dummy

dummy

dummy

optical

black

dummy

dummy

dummy

dummy

1220

active

lines

2640CSP_DS_003

The color filters are arranged in a Bayer pattern. The

primary color BG/GR array is arranged in line-alternating

fashion. Of the 2,010,624 pixels, 1,991,040 (1632x1220)

are active. The other pixels are used for black level

calibration and interpolation.

The sensor array design is based on a field integration

read-out system with

transfer and an

electronic shutter with a synchronous pixel read-out

scheme.

line-by-line

Analog Amplifier

When the column sample/hold circuit has sampled one

row of pixels, the pixel data will shift out one-by-one into

an analog amplifier.

Gain Control

The amplifier gain can either be programmed by the user

or controlled by the internal automatic gain control circuit

(AGC).

Channel Balance

The amplified signals are then balanced with a channel

balance block. In this block, the Red/Blue channel gain is

increased or decreased

to match Green channel

luminance level.

Balance Control

Channel Balance can be done manually by the user or by

the internal automatic white balance (AWB) controller.

Black Level Compensation

After the pixel data has been digitized, black level

calibration can be applied before the data is output. The

black level calibration block subtracts the average signal

level of optical black pixels to compensate for the dark

current in the pixel output. The user can disable black

level calibration.

Windowing

The OV2640 allows the user to define window size or

region of interest (ROI), as required by the application.

Window size setting (in pixels) ranges from 2 x 4 to

1632 x 1220 (UXGA) or 2 x 2 to 818 x 610 (SVGA), and

408 x 304 (CIF), and can be anywhere inside the

1632 x 1220 boundary. Note that modifying window size

or window position does not alter the frame or pixel rate.

The windowing control merely alters the assertion of the

HREF signal to be consistent with the programmed

horizontal and vertical ROI. The default window size is

1600 x 1200. Refer to Figure 4 and registers HREFST,

HREFEND, REG32, VSTRT, VEND, and COM1 for

details.

Version 2.2, February 23, 2007

Proprietary to OmniVision Technologies, Inc.

3

�

OV2640

Color CMOS UXGA (2.0 MegaPixel) OmniPixel2™ CAMERACHIP™ Sensor

Omni

ision

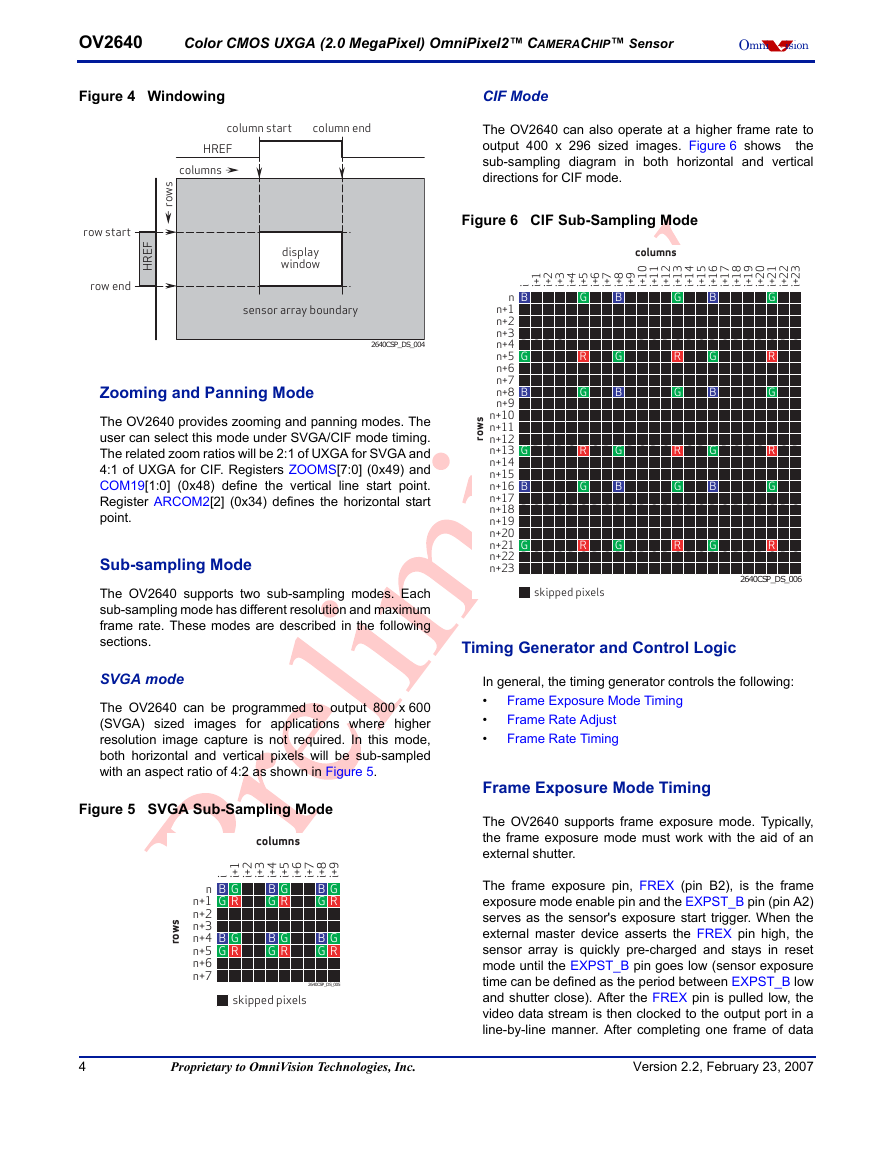

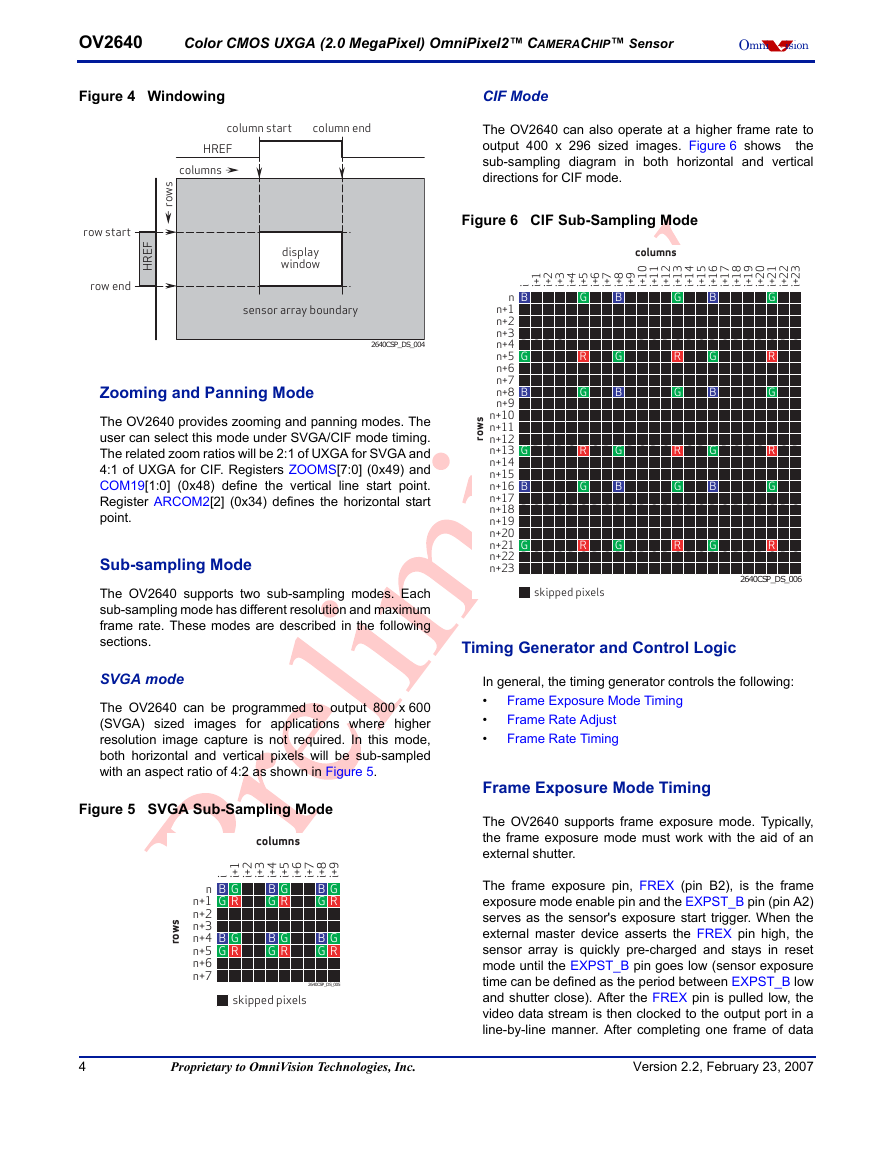

Figure 4 Windowing

CIF Mode

column start

column end

HREF

columns

s

w

o

r

row start

row end

F

E

R

H

display

window

sensor array boundary

2640CSP_DS_004

Zooming and Panning Mode

The OV2640 provides zooming and panning modes. The

user can select this mode under SVGA/CIF mode timing.

The related zoom ratios will be 2:1 of UXGA for SVGA and

4:1 of UXGA for CIF. Registers ZOOMS[7:0] (0x49) and

COM19[1:0] (0x48) define the vertical line start point.

Register ARCOM2[2] (0x34) defines the horizontal start

point.

Sub-sampling Mode

The OV2640 supports two sub-sampling modes. Each

sub-sampling mode has different resolution and maximum

frame rate. These modes are described in the following

sections.

SVGA mode

The OV2640 can be programmed to output 800 x 600

(SVGA) sized images for applications where higher

resolution image capture is not required. In this mode,

both horizontal and vertical pixels will be sub-sampled

with an aspect ratio of 4:2 as shown in Figure 5.

Figure 5 SVGA Sub-Sampling Mode

columns

1

+

ii

2

+

i

3

+

i

4

+

i

5

+

i

6

+

i

7

+

i

8

+

i

9

+

i

s

w

o

r

n

n+1

n+2

n+3

n+4

n+5

n+6

n+7

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

2640CSP_DS_005

B skipped pixels

The OV2640 can also operate at a higher frame rate to

output 400 x 296 sized images. Figure 6 shows the

sub-sampling diagram in both horizontal and vertical

directions for CIF mode.

Figure 6 CIF Sub-Sampling Mode

columns

1

+

ii

2

+

i

3

+

i

4

+

i

5

+

i

6

+

i

7

+

i

8

+

i

9

+

i

0

1

+

i

1

1

+

i

2

1

+

i

3

1

+

i

4

1

+

i

5

1

+

i

6

1

+

i

7

1

+

i

8

1

+

i

9

1

+

i

0

2

+

i

1

2

+

i

2

2

+

i

3

2

+

i

s

w

o

r

n

n+1

n+2

n+3

n+4

n+5

n+6

n+7

n+8

n+9

n+10

n+11

n+12

n+13

n+14

n+15

n+16

n+17

n+18

n+19

n+20

n+21

n+22

n+23

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B skipped pixels

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

B G

G R

2640CSP_DS_006

Timing Generator and Control Logic

In general, the timing generator controls the following:

•

•

•

Frame Exposure Mode Timing

Frame Rate Adjust

Frame Rate Timing

Frame Exposure Mode Timing

The OV2640 supports frame exposure mode. Typically,

the frame exposure mode must work with the aid of an

external shutter.

The frame exposure pin, FREX (pin B2), is the frame

exposure mode enable pin and the EXPST_B pin (pin A2)

serves as the sensor's exposure start trigger. When the

external master device asserts the FREX pin high, the

sensor array is quickly pre-charged and stays in reset

mode until the EXPST_B pin goes low (sensor exposure

time can be defined as the period between EXPST_B low

and shutter close). After the FREX pin is pulled low, the

video data stream is then clocked to the output port in a

line-by-line manner. After completing one frame of data

4

Proprietary to OmniVision Technologies, Inc.

Version 2.2, February 23, 2007

�

Omni

ision

Functional Description

output, the OV2640 will output continuous live video data

unless in single frame transfer mode. Figure 16 and

Figure 17 show the detailed timing and Table 11 shows

the timing specifications for this mode.

Frame Rate Adjust

The OV2640 offers three methods for frame rate

adjustment:

•

Clock prescaler: (see “CLKRC” on page 22)

By changing the system clock divide ratio and PLL,

the frame rate and pixel rate will change together.

This method can be used for dividing the frame/pixel

rate by: 1/2, 1/3, 1/4 … 1/64 of the input clock rate.

Line adjustment: (see “REG2A” on page 24 and

“FRARL” on page 24)

By adding a dummy pixel timing in each line

(between HREF and pixel data out), the frame rate

can be changed while leaving the pixel rate as is.

Vertical sync adjustment:

By adding dummy line periods to the vertical sync

period (see “ADDVSL” on page 24 and “ADDVSH”

on page 25 or see “FLL” on page 25 and “FLH” on

page 25), the frame rate can be altered while the

pixel rate remains the same.

•

•

Frame Rate Timing

Output Formatter

This block controls all output and data formatting required

prior to sending the image out.

Scaling Image Output

The OV2640 is capable of scaling down the image size

from CIF to 40x30. By using SCCB registers, the user can

output the desired image size. At certain image sizes,

HREF is not consistent in a frame.

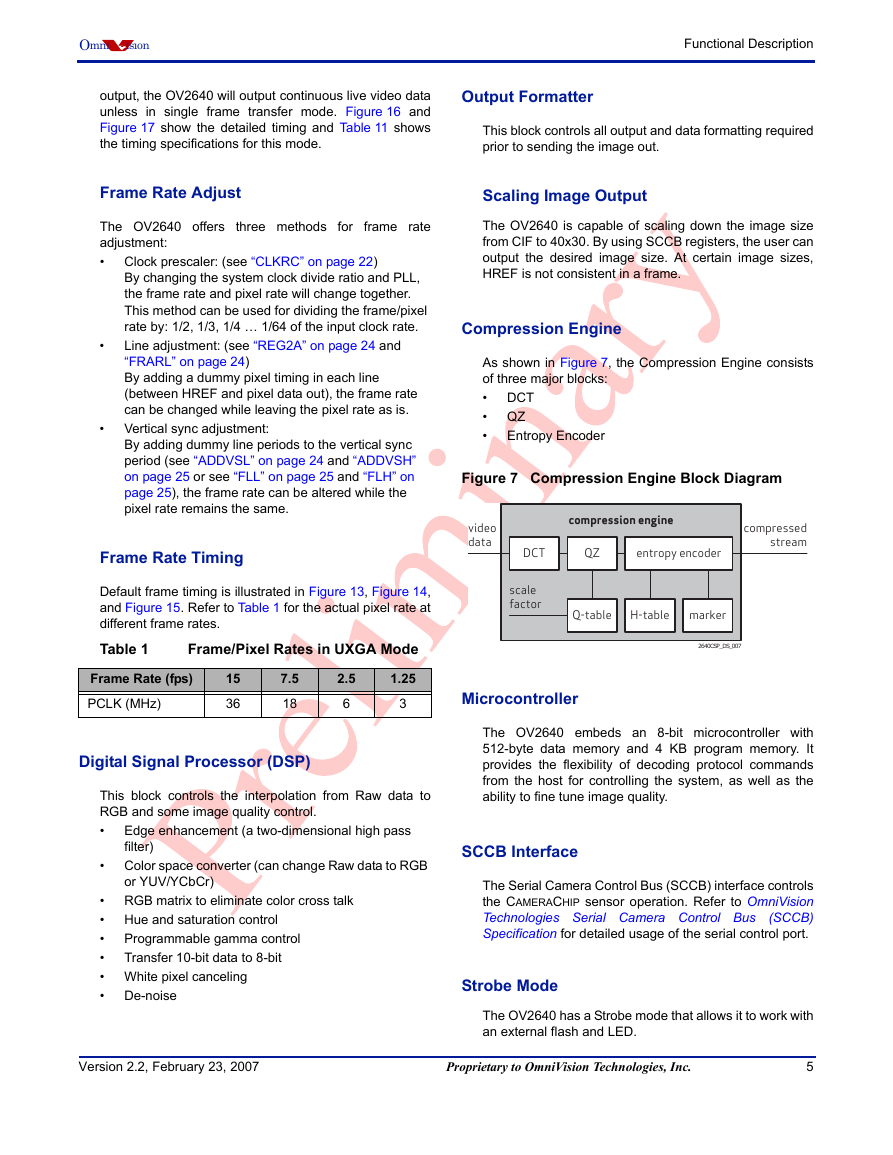

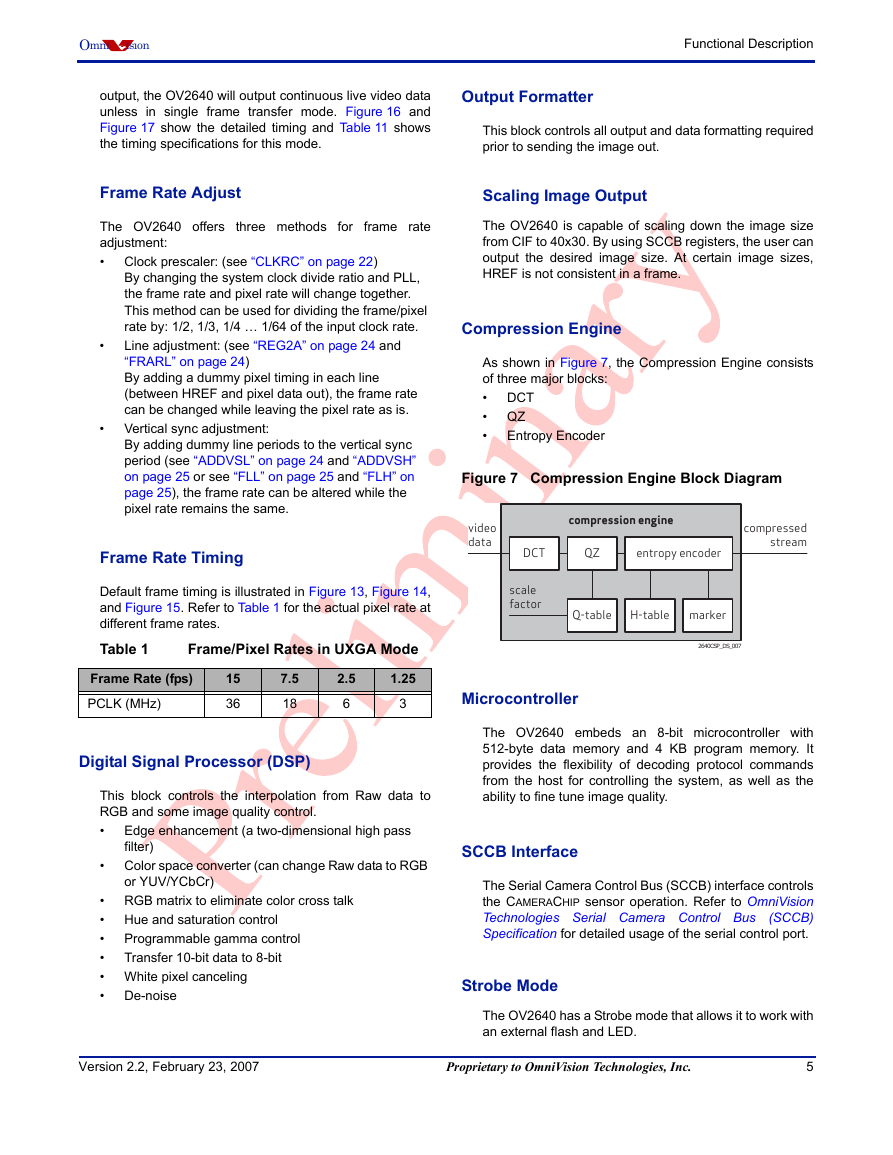

Compression Engine

As shown in Figure 7, the Compression Engine consists

of three major blocks:

•

• QZ

•

Entropy Encoder

DCT

Figure 7 Compression Engine Block Diagram

video

data

compression engine

DCT

QZ

entropy encoder

compressed

stream

Default frame timing is illustrated in Figure 13, Figure 14,

and Figure 15. Refer to Table 1 for the actual pixel rate at

different frame rates.

Table 1

Frame/Pixel Rates in UXGA Mode

scale

factor

Q-table

H-table

marker

2640CSP_DS_007

Frame Rate (fps)

PCLK (MHz)

15

36

7.5

18

2.5

6

1.25

3

Microcontroller

Digital Signal Processor (DSP)

•

This block controls the interpolation from Raw data to

RGB and some image quality control.

•

Edge enhancement (a two-dimensional high pass

filter)

Color space converter (can change Raw data to RGB

or YUV/YCbCr)

RGB matrix to eliminate color cross talk

Hue and saturation control

Programmable gamma control

Transfer 10-bit data to 8-bit

•

•

•

•

• White pixel canceling

•

De-noise

The OV2640 embeds an 8-bit microcontroller with

512-byte data memory and 4 KB program memory. It

provides the flexibility of decoding protocol commands

from the host for controlling the system, as well as the

ability to fine tune image quality.

SCCB Interface

The Serial Camera Control Bus (SCCB) interface controls

the CAMERACHIP sensor operation. Refer to OmniVision

Technologies Serial Camera Control Bus

(SCCB)

Specification for detailed usage of the serial control port.

Strobe Mode

The OV2640 has a Strobe mode that allows it to work with

an external flash and LED.

Version 2.2, February 23, 2007

Proprietary to OmniVision Technologies, Inc.

5

�

Color CMOS UXGA (2.0 MegaPixel) OmniPixel2™ CAMERACHIP™ Sensor

Omni

ision

OV2640

Reset

The OV2640 includes a RESETB pin (pin C6) that forces

a complete hardware reset when it is pulled low (GND).

The OV2640 clears all registers and resets them to their

default values when a hardware reset occurs. A reset can

also be initiated through the SCCB interface.

Power Down Mode

Two methods are available to place the OV2640 into

power-down mode: hardware power-down and SCCB

software power-down.

To initiate hardware power-down, the PWDN pin (pin B6)

must be tied to high. When this occurs, the OV2640

internal device clock is halted and all internal counters are

reset.

Executing a software power-down through the SCCB

interface suspends internal circuit activity but does not

halt the device clock. All register content is maintained in

standby mode.

Digital Video Port

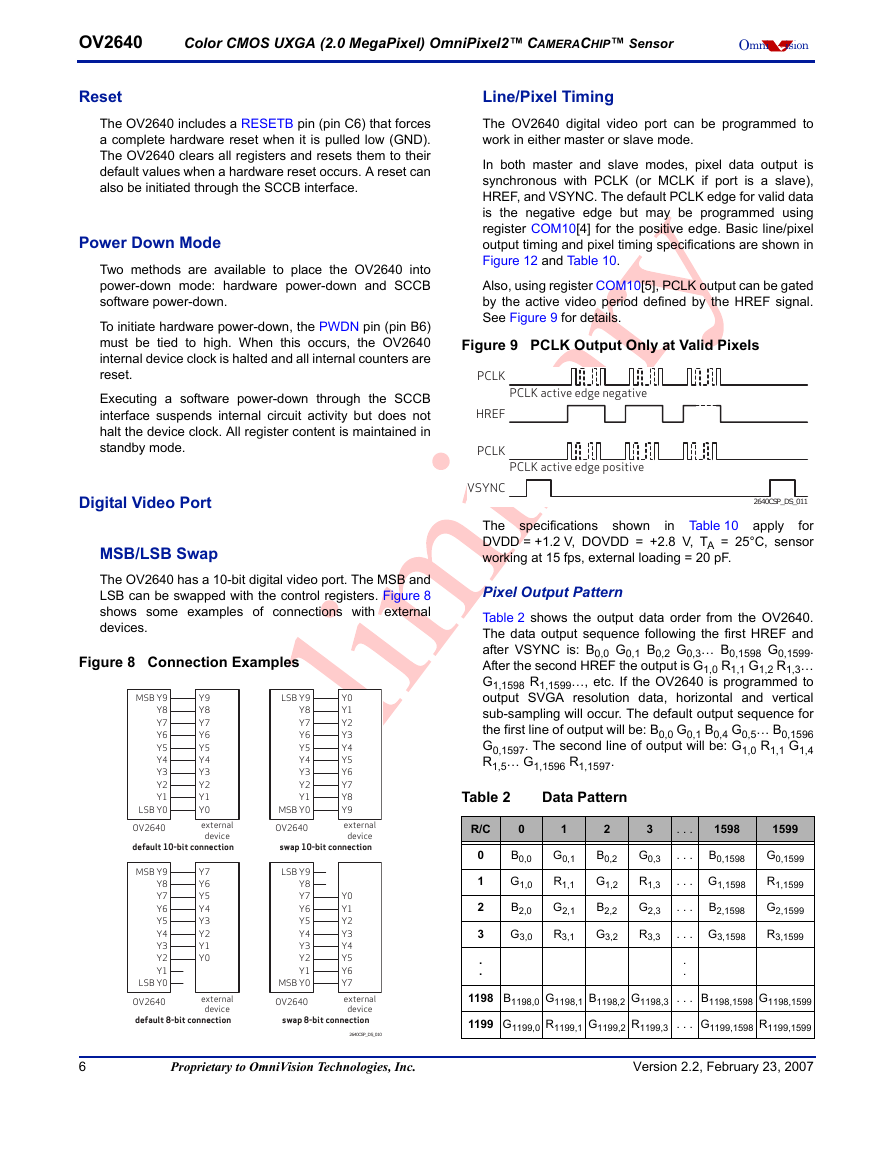

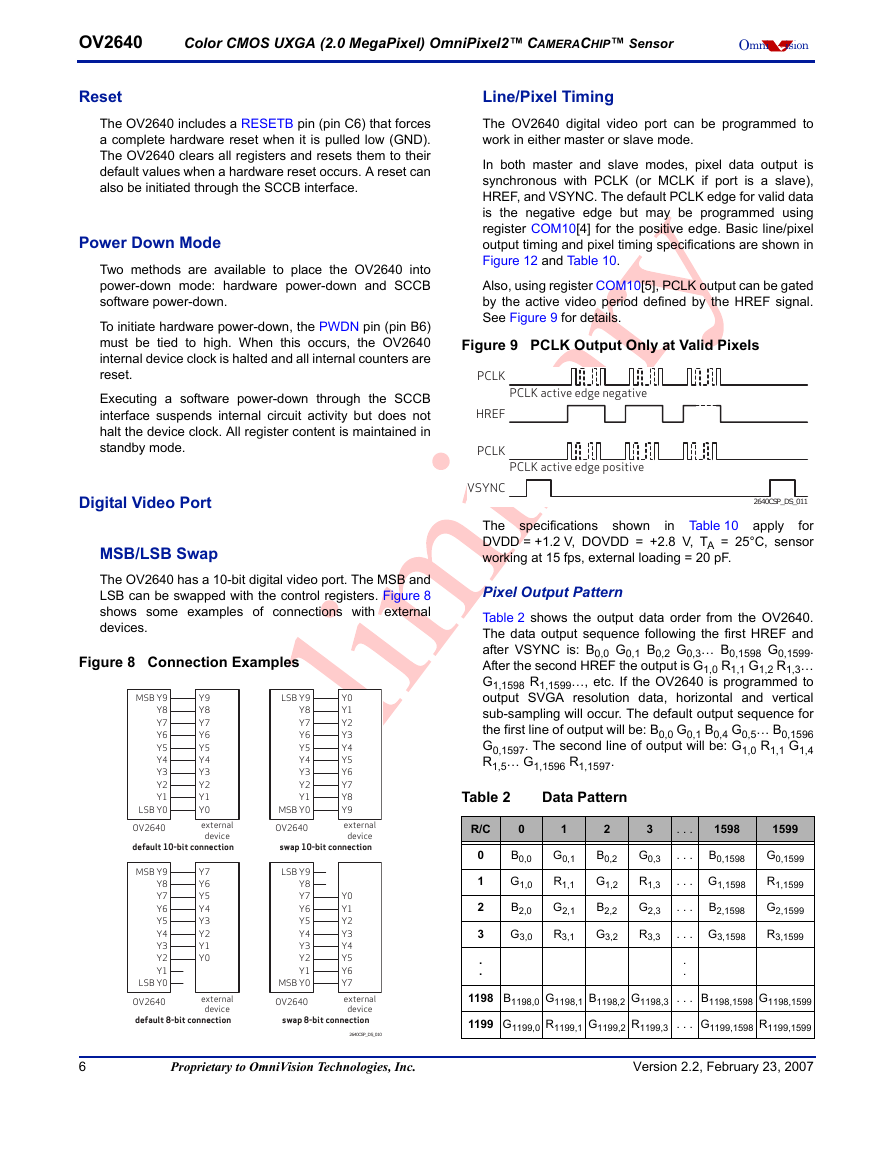

MSB/LSB Swap

The OV2640 has a 10-bit digital video port. The MSB and

LSB can be swapped with the control registers. Figure 8

shows some examples of connections with external

devices.

Figure 8 Connection Examples

MSB Y9

Y8

Y7

Y6

Y5

Y4

Y3

Y2

Y1

LSB Y0

Y9

Y8

Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

external

device

default 10-bit connection

OV2640

Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

MSB Y9

Y8

Y7

Y6

Y5

Y4

Y3

Y2

Y1

LSB Y0

OV2640

external

device

default 8-bit connection

LSB Y9

Y8

Y7

Y6

Y5

Y4

Y3

Y2

Y1

MSB Y0

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

Y8

Y9

external

device

swap 10-bit connection

OV2640

LSB Y9

Y8

Y7

Y6

Y5

Y4

Y3

Y2

Y1

MSB Y0

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

external

device

swap 8-bit connection

OV2640

2640CSP_DS_010

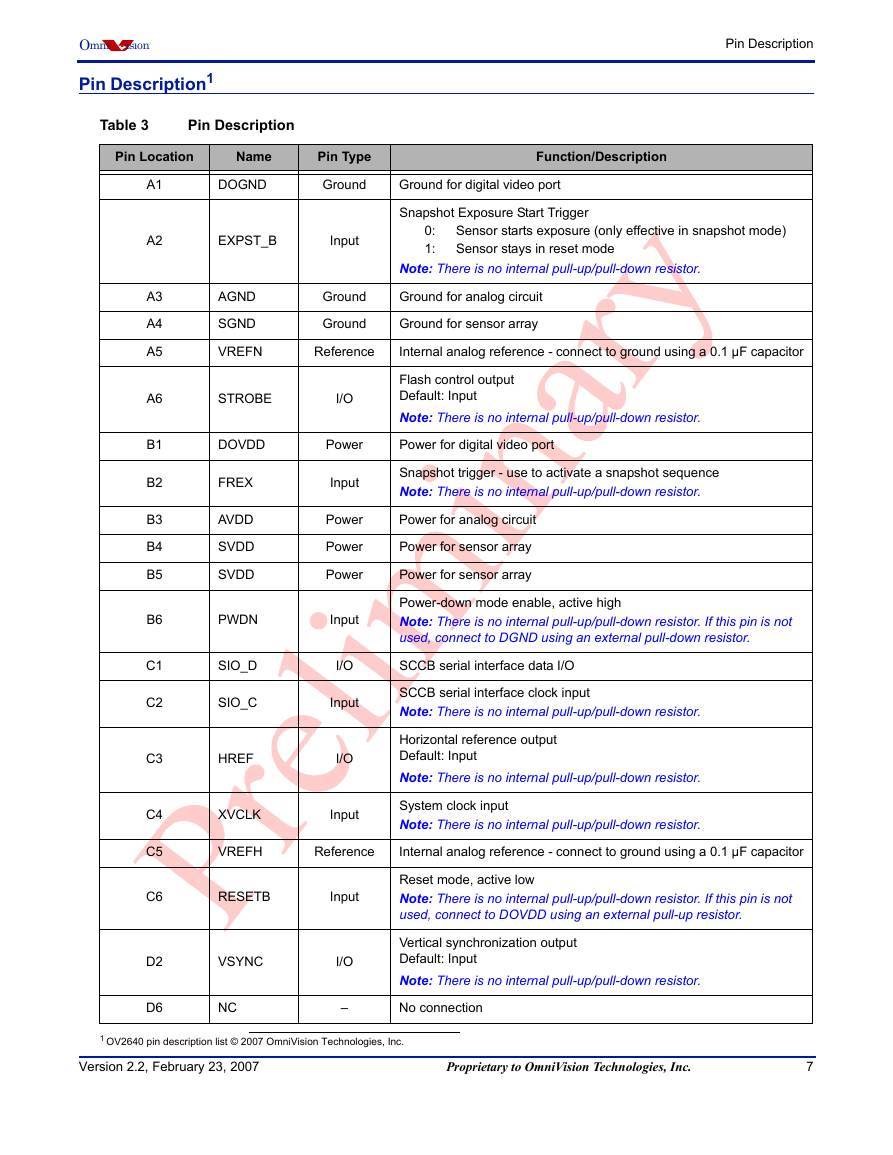

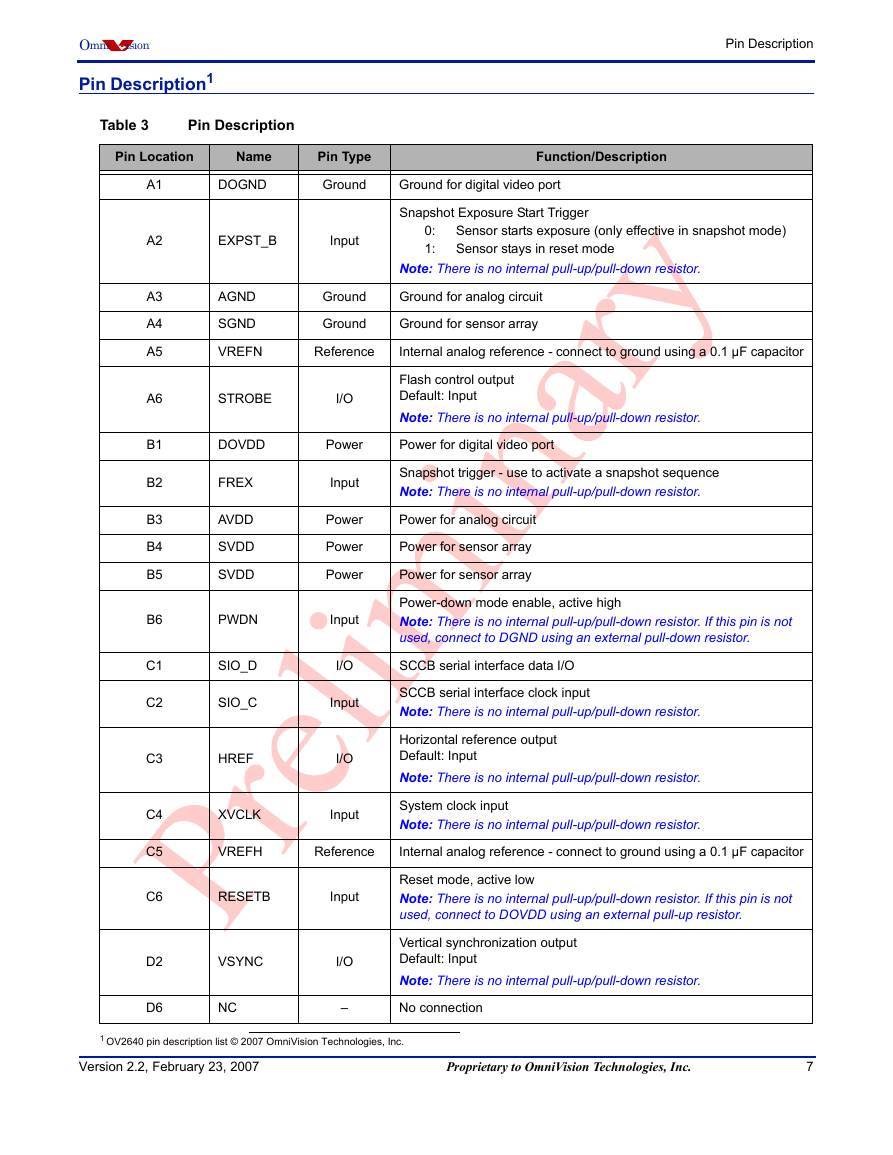

Line/Pixel Timing

The OV2640 digital video port can be programmed to

work in either master or slave mode.

In both master and slave modes, pixel data output is

synchronous with PCLK (or MCLK if port is a slave),

HREF, and VSYNC. The default PCLK edge for valid data

is the negative edge but may be programmed using

register COM10[4] for the positive edge. Basic line/pixel

output timing and pixel timing specifications are shown in

Figure 12 and Table 10.

Also, using register COM10[5], PCLK output can be gated

by the active video period defined by the HREF signal.

See Figure 9 for details.

Figure 9 PCLK Output Only at Valid Pixels

PCLK

HREF

PCLK

VSYNC

PCLK active edge negative

PCLK active edge positive

2640CSP_DS_011

The specifications shown

for

DVDD = +1.2 V, DOVDD = +2.8 V, TA = 25°C, sensor

working at 15 fps, external loading = 20 pF.

in Table 10 apply

Pixel Output Pattern

Table 2 shows the output data order from the OV2640.

The data output sequence following the first HREF and

after VSYNC is: B0,0 G0,1 B0,2 G0,3… B0,1598 G0,1599.

After the second HREF the output is G1,0 R1,1 G1,2 R1,3…

G1,1598 R1,1599…, etc. If the OV2640 is programmed to

output SVGA resolution data, horizontal and vertical

sub-sampling will occur. The default output sequence for

the first line of output will be: B0,0 G0,1 B0,4 G0,5… B0,1596

G0,1597. The second line of output will be: G1,0 R1,1 G1,4

R1,5… G1,1596 R1,1597.

Table 2

Data Pattern

1

G0,1

R1,1

G2,1

R3,1

2

B0,2

G1,2

B2,2

G3,2

R/C

0

B0,0

G1,0

B2,0

G3,0

0

1

2

3

.

.

3

. . .

1598

1599

G0,3

R1,3

G2,3

R3,3

. . .

B0,1598

. . . G1,1598

. . .

B2,1598

. . . G3,1598

.

.

G0,1599

R1,1599

G2,1599

R3,1599

1198 B1198,0 G1198,1 B1198,2 G1198,3 . . . B1198,1598 G1198,1599

1199 G1199,0 R1199,1 G1199,2 R1199,3 . . . G1199,1598 R1199,1599

6

Proprietary to OmniVision Technologies, Inc.

Version 2.2, February 23, 2007

�

ision

Omni

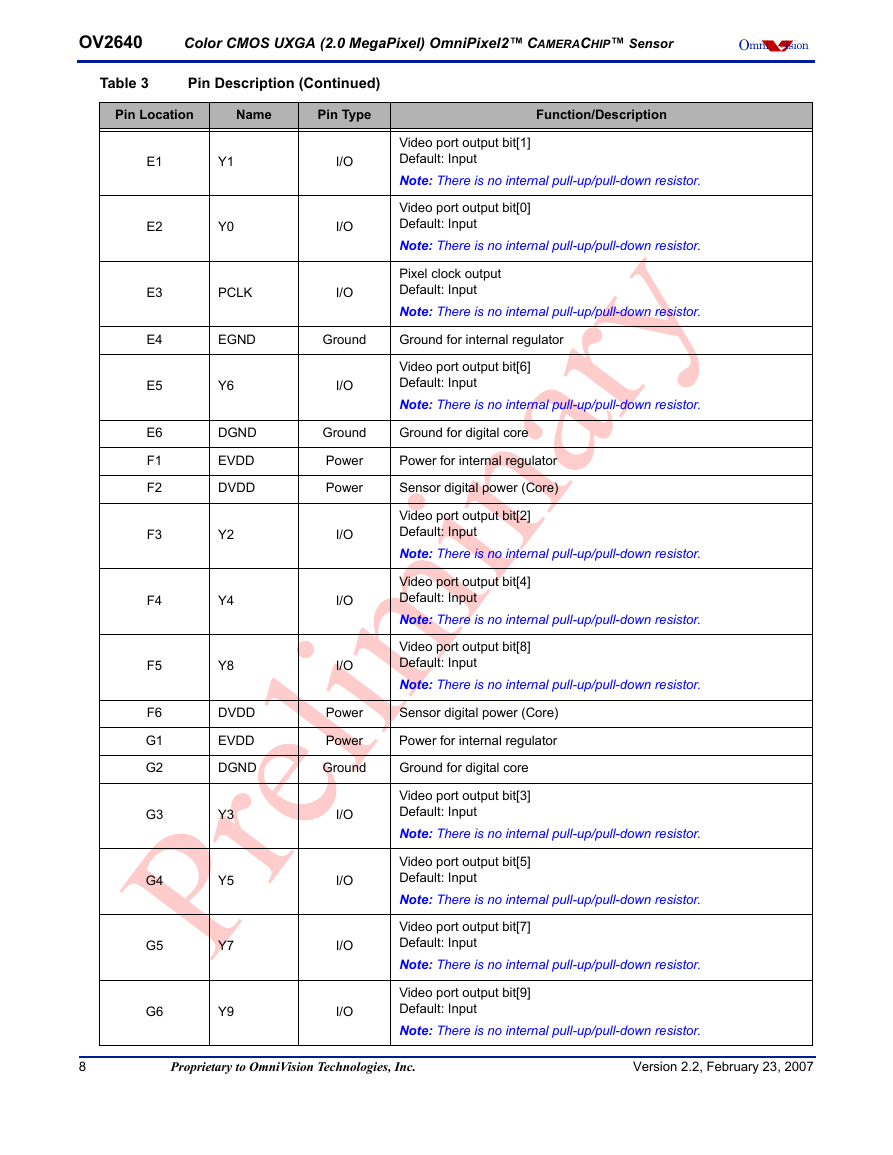

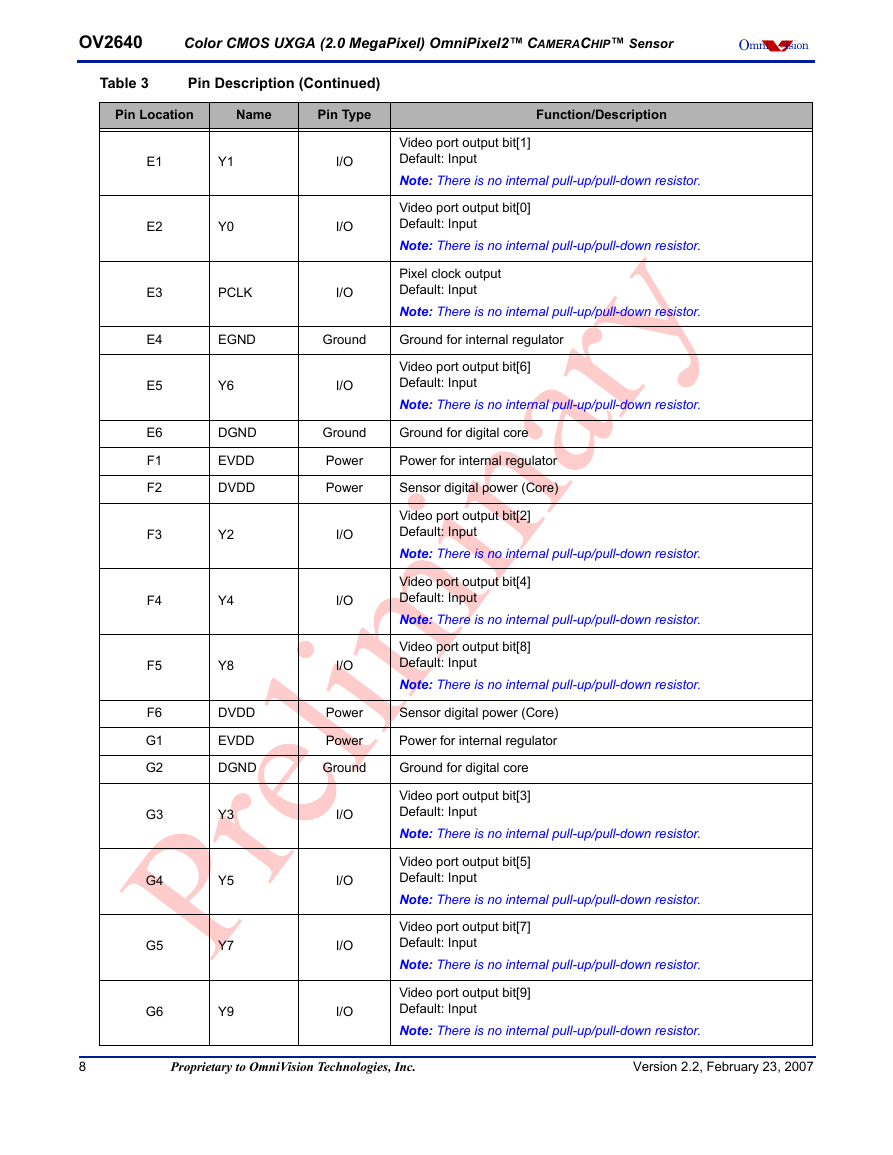

Pin Description1

Pin Description

Table 3

Pin Description

Pin Location

Name

Pin Type

Function/Description

A1

A2

A3

A4

A5

A6

B1

B2

B3

B4

B5

B6

C1

C2

C3

C4

C5

C6

D2

D6

DOGND

Ground

Ground for digital video port

EXPST_B

Input

Snapshot Exposure Start Trigger

0:

1:

Sensor starts exposure (only effective in snapshot mode)

Sensor stays in reset mode

Note: There is no internal pull-up/pull-down resistor.

AGND

SGND

VREFN

Ground

Ground

Ground for analog circuit

Ground for sensor array

Reference

Internal analog reference - connect to ground using a 0.1 µF capacitor

STROBE

I/O

Flash control output

Default: Input

Note: There is no internal pull-up/pull-down resistor.

DOVDD

Power

Power for digital video port

FREX

AVDD

SVDD

SVDD

PWDN

SIO_D

SIO_C

HREF

XVCLK

VREFH

Input

Power

Power

Power

Input

I/O

Input

I/O

Input

Snapshot trigger - use to activate a snapshot sequence

Note: There is no internal pull-up/pull-down resistor.

Power for analog circuit

Power for sensor array

Power for sensor array

Power-down mode enable, active high

Note: There is no internal pull-up/pull-down resistor. If this pin is not

used, connect to DGND using an external pull-down resistor.

SCCB serial interface data I/O

SCCB serial interface clock input

Note: There is no internal pull-up/pull-down resistor.

Horizontal reference output

Default: Input

Note: There is no internal pull-up/pull-down resistor.

System clock input

Note: There is no internal pull-up/pull-down resistor.

Reference

Internal analog reference - connect to ground using a 0.1 µF capacitor

RESETB

Input

Reset mode, active low

Note: There is no internal pull-up/pull-down resistor. If this pin is not

used, connect to DOVDD using an external pull-up resistor.

VSYNC

NC

I/O

–

Vertical synchronization output

Default: Input

Note: There is no internal pull-up/pull-down resistor.

No connection

1 OV2640 pin description list © 2007 OmniVision Technologies, Inc.

Version 2.2, February 23, 2007

Proprietary to OmniVision Technologies, Inc.

7

�

OV2640

Color CMOS UXGA (2.0 MegaPixel) OmniPixel2™ CAMERACHIP™ Sensor

Omni

ision

Table 3

Pin Description (Continued)

Pin Location

Name

Pin Type

Function/Description

E1

E2

E3

E4

E5

E6

F1

F2

F3

F4

F5

F6

G1

G2

G3

G4

G5

G6

Y1

Y0

PCLK

I/O

I/O

I/O

Video port output bit[1]

Default: Input

Note: There is no internal pull-up/pull-down resistor.

Video port output bit[0]

Default: Input

Note: There is no internal pull-up/pull-down resistor.

Pixel clock output

Default: Input

Note: There is no internal pull-up/pull-down resistor.

EGND

Ground

Ground for internal regulator

Y6

DGND

EVDD

DVDD

Y2

Y4

Y8

DVDD

EVDD

DGND

Y3

Y5

Y7

Y9

I/O

Video port output bit[6]

Default: Input

Note: There is no internal pull-up/pull-down resistor.

Ground

Ground for digital core

Power

Power

Power for internal regulator

Sensor digital power (Core)

I/O

I/O

I/O

Video port output bit[2]

Default: Input

Note: There is no internal pull-up/pull-down resistor.

Video port output bit[4]

Default: Input

Note: There is no internal pull-up/pull-down resistor.

Video port output bit[8]

Default: Input

Note: There is no internal pull-up/pull-down resistor.

Power

Power

Sensor digital power (Core)

Power for internal regulator

Ground

Ground for digital core

I/O

I/O

I/O

I/O

Video port output bit[3]

Default: Input

Note: There is no internal pull-up/pull-down resistor.

Video port output bit[5]

Default: Input

Note: There is no internal pull-up/pull-down resistor.

Video port output bit[7]

Default: Input

Note: There is no internal pull-up/pull-down resistor.

Video port output bit[9]

Default: Input

Note: There is no internal pull-up/pull-down resistor.

8

Proprietary to OmniVision Technologies, Inc.

Version 2.2, February 23, 2007

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc