TCAD Tutorial and Examples Volume 1

Introduction

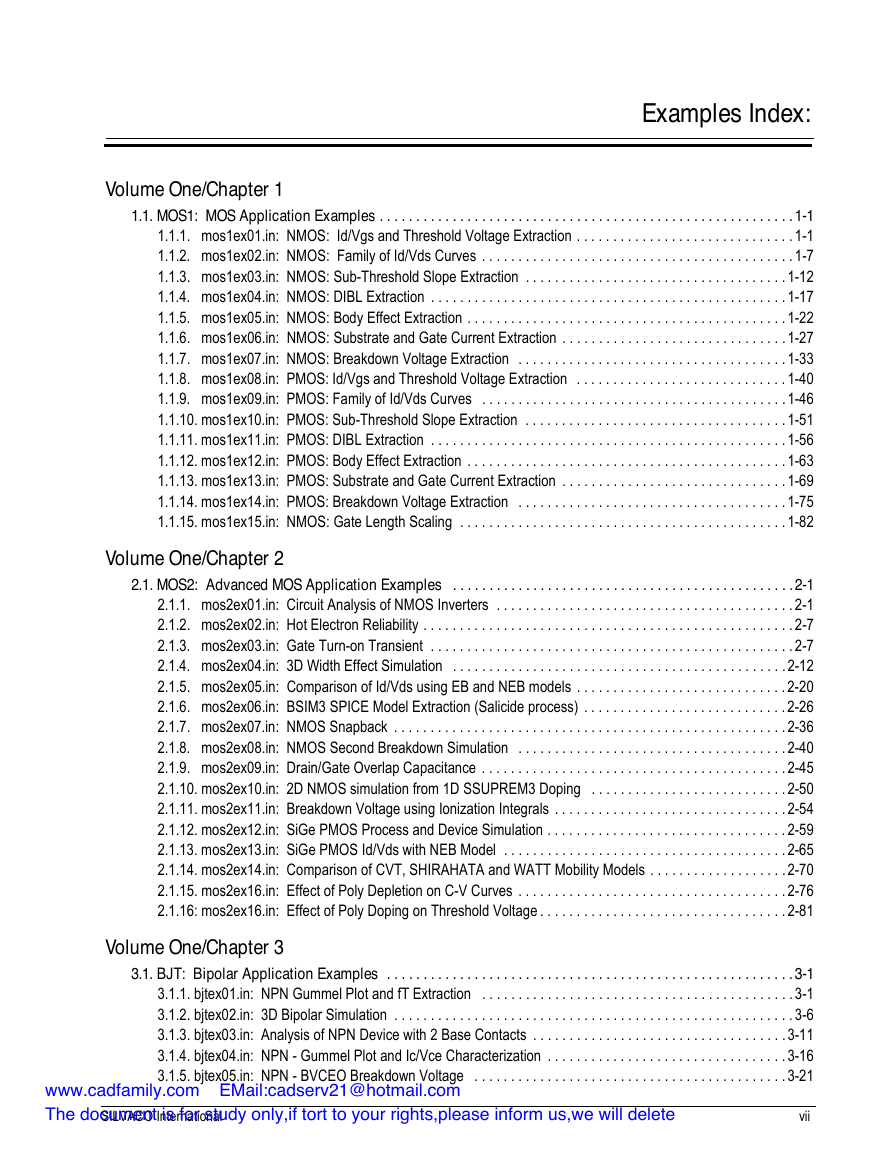

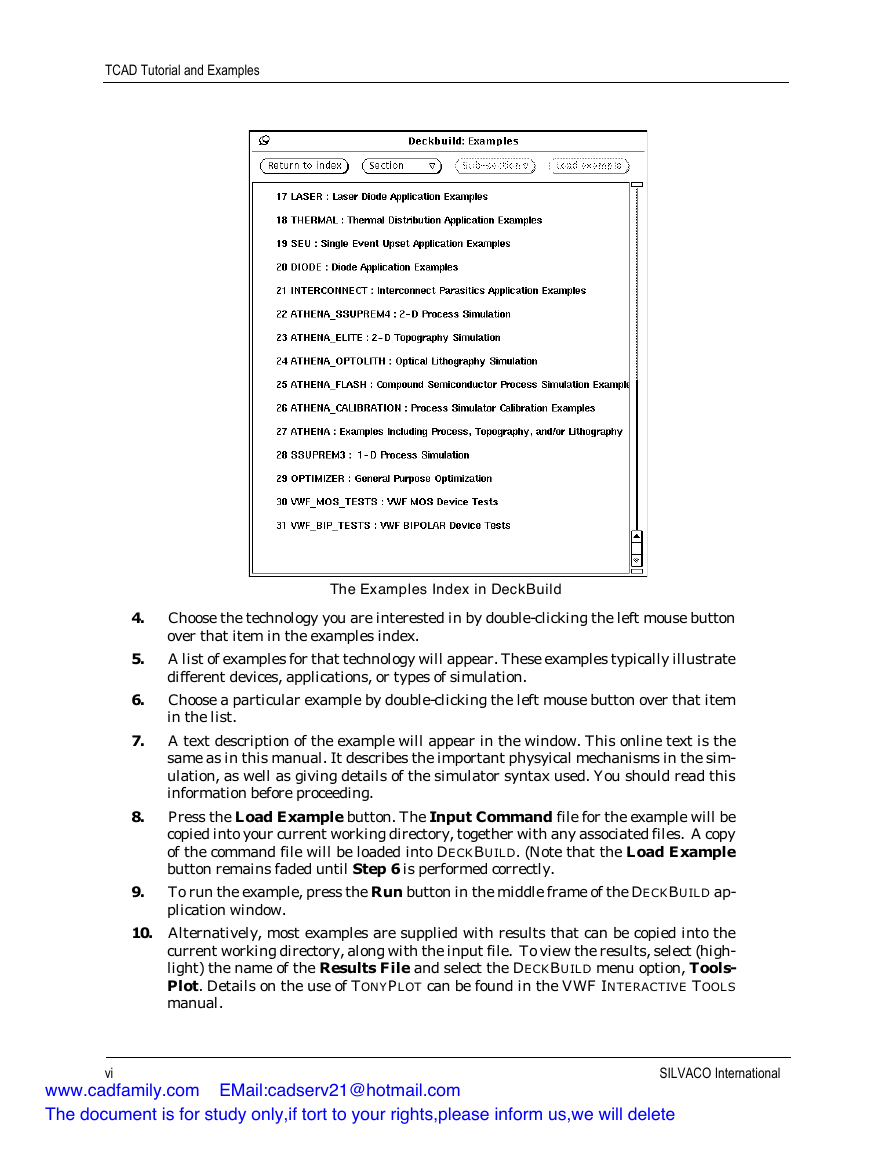

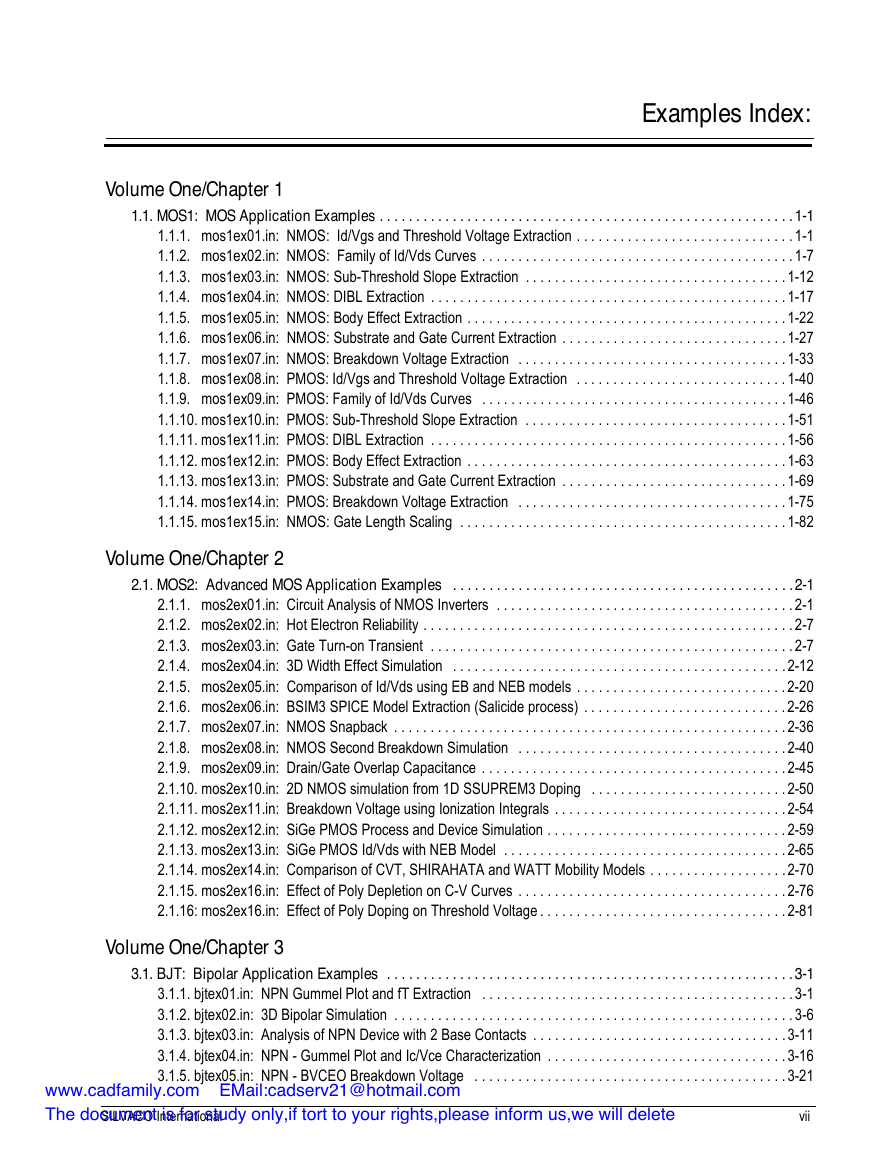

Examples Index:

List of Figures:

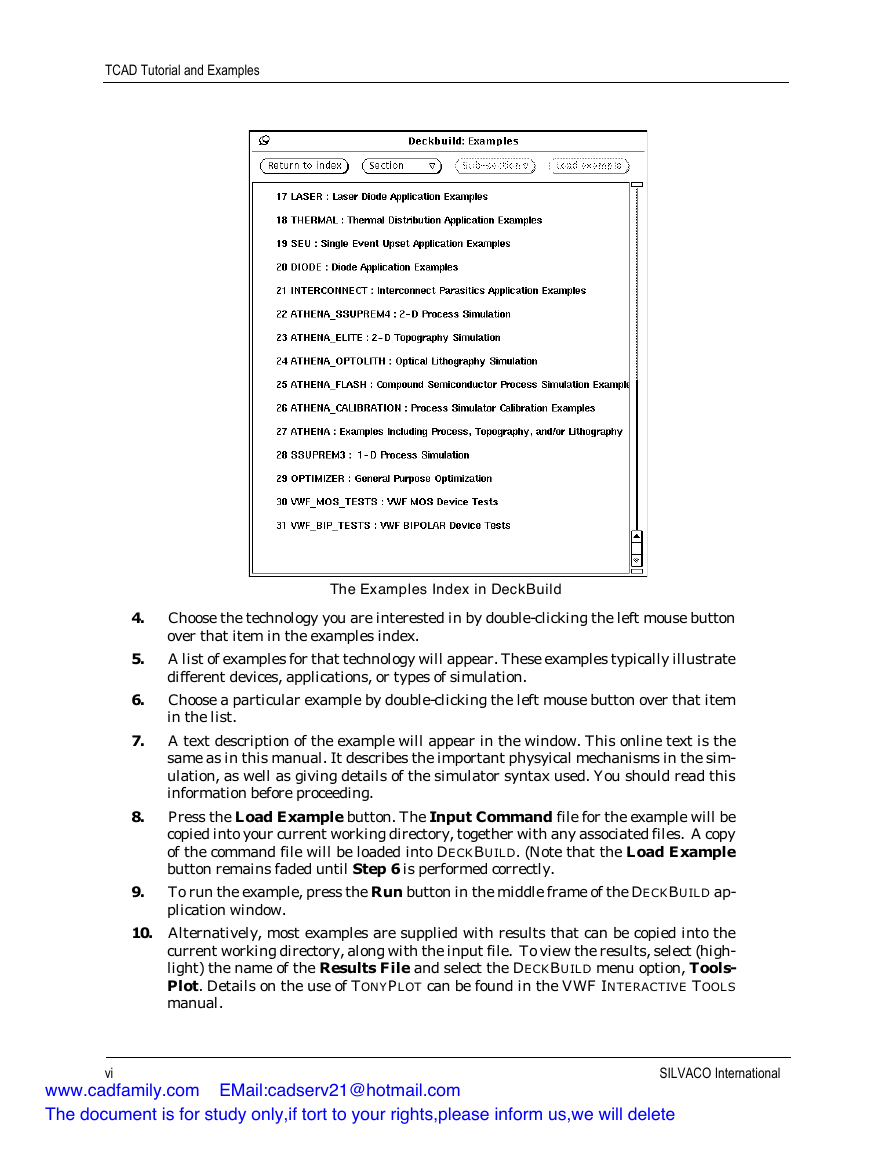

Chapter 1:

MOS1: MOS Application Examples

1.1. MOS1: MOS Application Examples

1.1.1. mos1ex01.in: NMOS: Id/Vgs and Threshold Voltage Extraction

1.1.2. mos1ex02.in: NMOS: Family of Id/Vds Curves

1.1.3. mos1ex03.in: NMOS: Sub-Threshold Slope Extraction

1.1.4. mos1ex04.in: NMOS: DIBL Extraction

1.1.5. mos1ex05.in: NMOS: Body Effect Extraction

1.1.6. mos1ex06.in: NMOS: Substrate and Gate Current Extraction

1.1.7. mos1ex07.in: NMOS: Breakdown Voltage Extraction

1.1.8. mos1ex08.in: PMOS: Id/Vgs and Threshold Voltage Extraction

1.1.9. mos1ex09.in: PMOS: Family of Id/Vds Curves

1.1.10. mos1ex10.in: PMOS: Sub-Threshold Slope Extraction

1.1.11. mos1ex11.in: PMOS: DIBL Extraction

1.1.12. mos1ex12.in: PMOS: Body Effect Extraction

1.1.13. mos1ex13.in: PMOS: Substrate and Gate Current Extraction

1.1.14. mos1ex14.in: PMOS: Breakdown Voltage Extraction

1.1.15. mos1ex15.in: NMOS: Gate Length Scaling

Chapter 2:

MOS2: Advanced MOS Applications Examples

2.1. MOS2: Advanced MOS Application Examples

2.1.1. mos2ex01.in: Circuit Analysis of NMOS Inverters

2.1.2. mos2ex02.in: Hot Electron Reliability

2.1.3. mos2ex03.in: Gate Turn-on Transient

2.1.4. mos2ex04.in: 3D Width Effect Simulation

2.1.5. mos2ex05.in: Comparison of Id/Vds using EB and NEB models

2.1.6. mos2ex06.in: BSIM3 SPICE Model Extraction (Salicide process)

2.1.7. mos2ex07.in: NMOS Snapback

2.1.8. mos2ex08.in: NMOS Second Breakdown Simulation

2.1.9. mos2ex09.in: Drain/Gate Overlap Capacitance

2.1.10. mos2ex10.in: 2D NMOS simulation from 1D SSUPREM3 Doping

2.1.11. mos2ex11.in: Breakdown Voltage using Ionization Integrals

2.1.12. mos2ex12.in: SiGe PMOS Process and Device Simulation

2.1.13. mos2ex13.in: SiGe PMOS Id/Vds with NEB Model

2.1.14. mos2ex14.in: Comparison of CVT, SHIRAHATA and WATT Mobility Models

2.1.15. mos2ex15.in : Effect of Poly Depletion on C-V curves

2.1.16. mos2ex16.in : Effect of Poly Doping on Threshold Voltage

Chapter 3:

BJT: Bipolar Application Examples

3.1. BJT: Bipolar Application Examples

3.1.1. bjtex01.in: NPN Gummel Plot and fT Extraction

3.1.2. bjtex02.in: 3D Bipolar Simulation

3.1.3. bjtex03.in: Analysis of NPN Device with 2 Base Contacts

3.1.4. bjtex04.in: NPN - Gummel Plot and Ic/Vce Characterization

3.1.5. bjtex05.in: NPN - BVCEO Breakdown Voltage

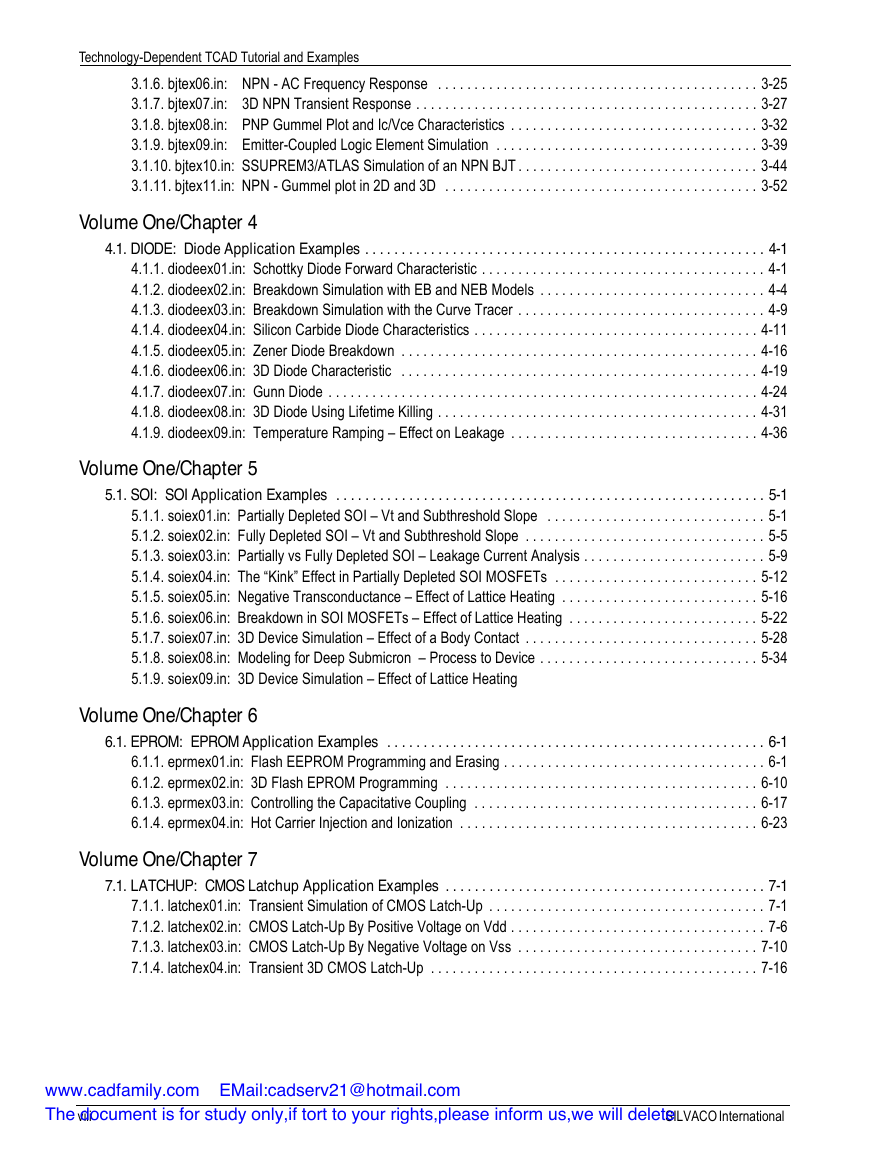

3.1.6. bjtex06.in: NPN - AC Frequency Response

3.1.7. bjtex07.in: 3D NPN Transient Response

3.1.8. bjtex08.in: PNP Gummel Plot and Ic/Vce Characteristic

3.1.9. bjtex09.in: Emitter-Coupled Logic Element Simulation

3.1.10. bjtex10.in: SSUPREM3/ATLAS Simulation of an NPN BJT

3.1.11. bjtex11.in: NPN - Gummel plot in 2D and 3D

Chapter 4:

DIODE: Diode Application Examples

4.1. DIODE: Diode Application Examples

4.1.1. diodeex01.in: Schottky Diode Forward Characteristic

4.1.2. diodeex02.in: Breakdown Simulation with EB and NEB Models

4.1.3. diodeex03.in: Breakdown Simulation with the Curve Tracer

4.1.4. diodeex04.in: Silicon Carbide Diode Characteristics

4.1.5. diodeex05.in: Zener Diode Breakdown

4.1.6. diodeex06.in: 3D Diode Characteristic

4.1.7. diodeex07.in: Gunn Diode

4.1.8. diodeex08.in : 3D Diode Using Lifetime Killing

4.1.9. diodeex09.in : Temperature Ramping – Effect on Leakage

Chapter 5:

SOI: SOI Application Examples

5.1. SOI: SOI Application Examples

5.1.1. soiex01.in: Partially Depleted SOI - Vt and Subthreshold Slope

5.1.2. soiex02.in: Fully Depleted SOI - Vt and Subthreshold Slope

5.1.3. soiex03.in: Partially vs Fully Depleted SOI - Leakage Current Analysis

5.1.4. soiex04.in: The “Kink” Effect in Partially Depleted SOI MOSFETs

5.1.5. soiex05.in: Negative Transconductance - Effect of Lattice Heating

5.1.6. soiex06.in: Breakdown in SOI MOSFETs - Effect of Lattice Heating

5.1.7. soiex07.in: 3D Device Simulation - Effect of a Body Contact

5.1.8. soiex08.in: Modeling for Deep Submicron - Process to Device

5.1.9. soiex09.in : 3D Device Simulation - Effect of Lattice Heating

Chapter 6:

EPROM: EPROM Application Examples

6.1. EPROM: Application Examples

6.1.1. eprmex01.in: Flash EEPROM Programming and Erasing

6.1.2. eprmex02.in: 3D Flash EPROM Programming

6.1.3. eprmex03.in: Controlling the Capacitative Coupling

6.1.4. eprmex04.in: Hot Carrier Injection and Ionization

Chapter 7:

LATCHUP: CMOS Latchup Application Examples

7.1. LATCHUP: CMOS Latchup Application Examples

7.1.1. latchex01.in: Transient Simulation of CMOS Latch-Up

7.1.2. latchex02.in: CMOS Latch-Up By Positive Voltage on Vdd

7.1.3. latchex03.in: CMOS Latch-Up By Negative Voltage on Vss

7.1.4. latchex04.in: Transient 3D CMOS Latch-Up

Chapter 8:

ESD: ESD Application Examples

8.1. ESD: ESD Application Examples

8.1.1. esdex01.in: Human Body Model in a Diode

8.1.2. esdex02.in: Charge Device Model in a Diode

8.1.3. esdex03.in: Human Body Model in a MOSFET

8.1.4. esdex04.in: HBM in a MOSFET with Energy Balance Models

8.1.5. esdex05.in: Second Breakdown of a MOSFET

Chapter 9:

POWER: Power Device Application Examples

9.1. POWER: Power Device Application Examples

9.1.1. powerex01.in: Reverse Recovery of a Power Diode

9.1.2. powerex02.in: Vertical DMOS Turn-on Characteristics

9.1.3. powerex03.in: IGBT Transient Latch-up with Lattice Heating

9.1.4. powerex04.in: IGBT Ic/Vce Characteristics

9.1.5. powerex05.in: Guard Ring Breakdown Analysis

9.1.6. powerex06.in: GTO Turn-off Transient

9.1.7. powerex07.in: LDMOS Breakdown

9.1.8. powerex08.in: LDMOS Breakdown using Ionization Integrals

9.1.9. powerex09.in : Anisotropic Mobility Characteristics of a SiC T-MOSFET

9.1.10. powerex10.in : Anisotropic Mobility Characteristics of a SiC DMOS Device

9.1.11. powerex11.in : Vertical DMOS Gate Charging Simulation

Chapter 10:

ISOLATION: ISO Application Examples

10.1. ISOLATION : ISOLATION Applications Examples

10.1.1 isolationex01.in : Local Oxidation Isolation Punchthrough

10.1.2 {subsection} isolationex02.in : Trench Isolation Punchthrough

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc