Cover

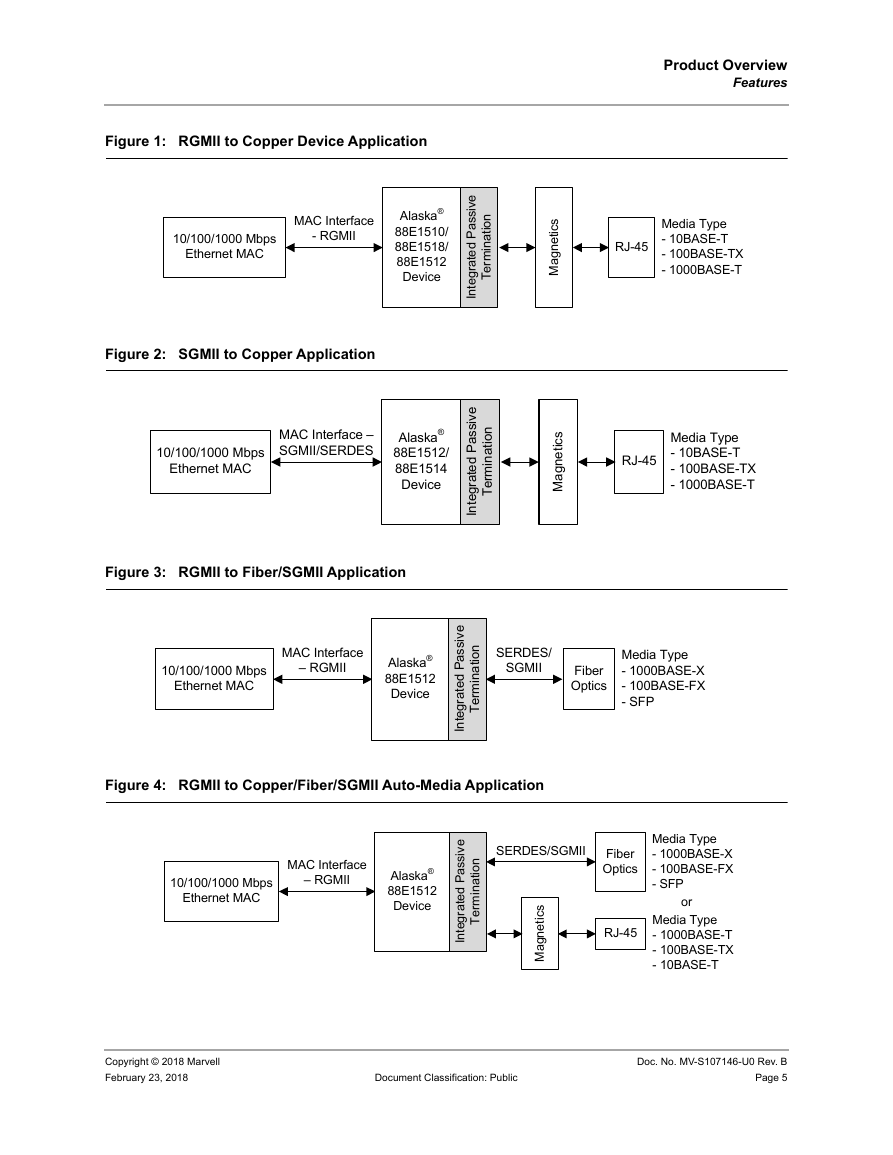

Product Overview

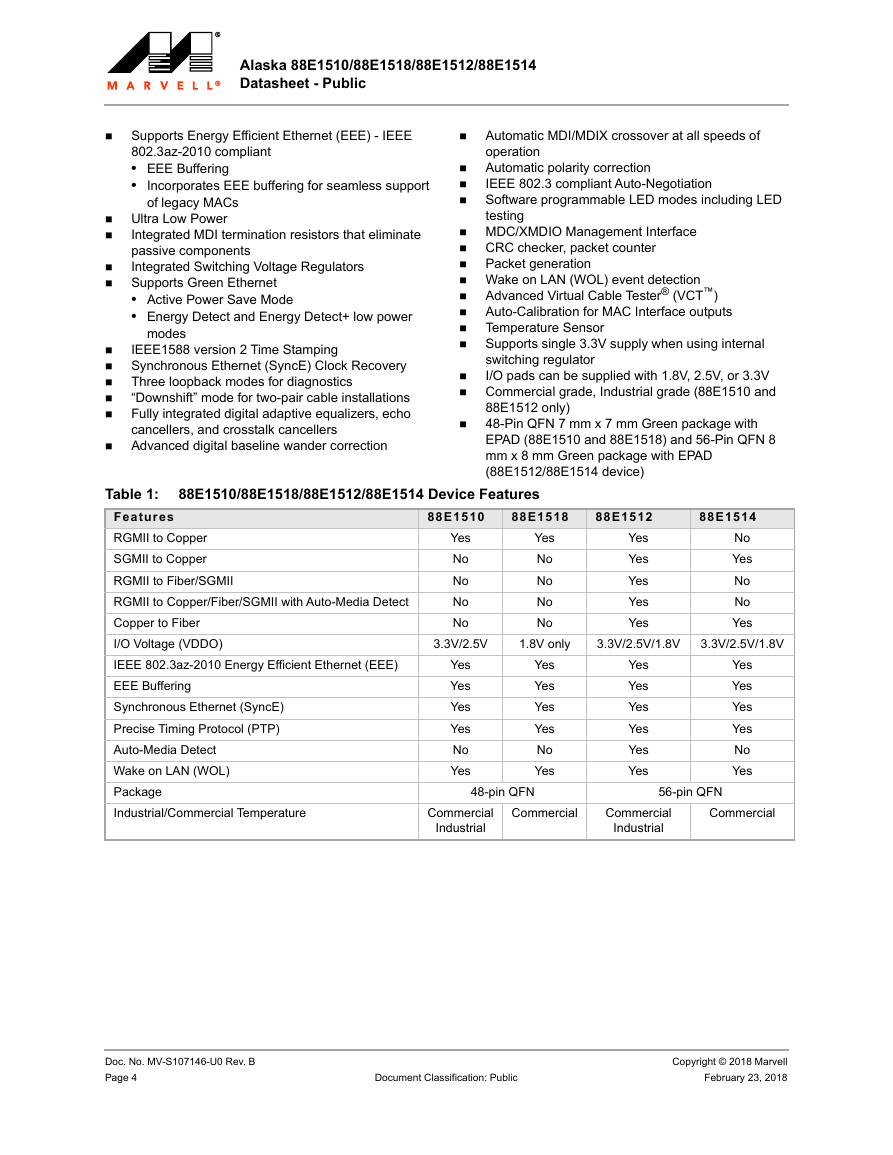

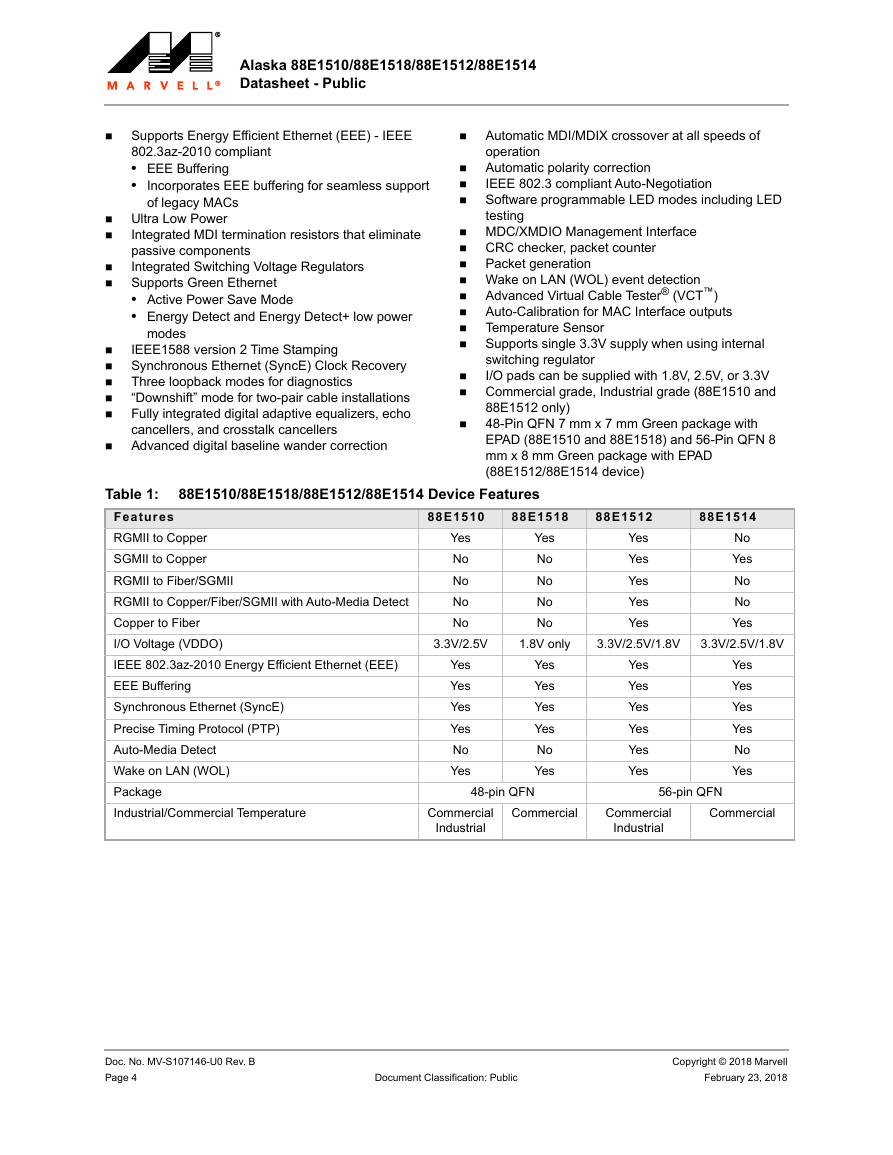

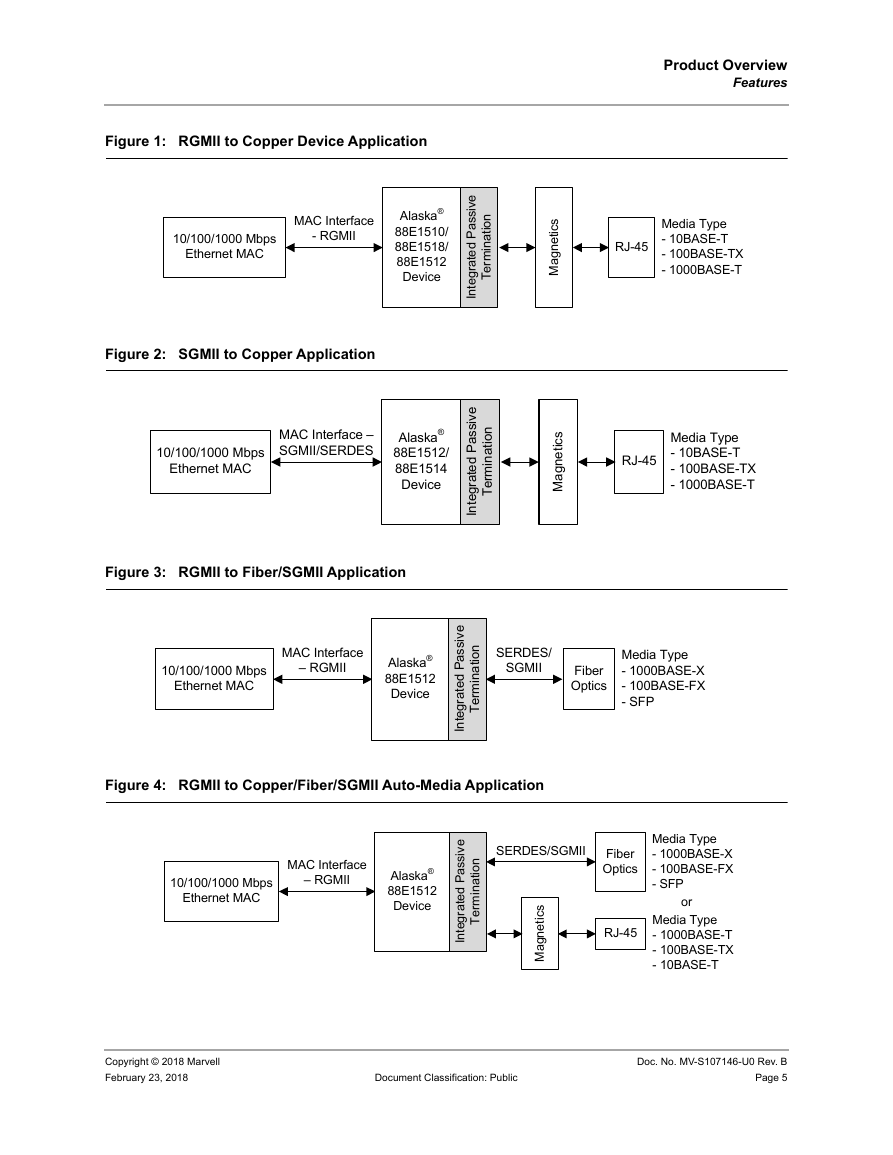

Features

Table of Contents

List of Tables

List of Figures

1 Signal Description

1.1 Pin Description

1.1.1 88E1510/88E1518 48-Pin QFN Package Pinout

1.1.2 88E1512 56-Pin QFN Package Pinout

1.1.3 88E1514 56-Pin QFN Package Pinout

1.2 Pin Assignment List

1.2.1 88E1510 48-Pin QFN Pin Assignment List - Alphabetical by Signal Name

1.2.2 88E1518 48-Pin QFN Pin Assignment List - Alphabetical by Signal Name

1.2.3 88E1512 56-Pin QFN Pin Assignment List - Alphabetical by Signal Name

1.2.4 88E1514 56-Pin QFN Pin Assignment List - Alphabetical by Signal Name

2 PHY Functional Specifications

2.1 Modes of Operation and Major Interfaces

2.2 Copper Media Interface

2.2.1 Transmit Side Network Interface

2.2.1.1 Multi-mode TX Digital to Analog Converter

2.2.1.2 Slew Rate Control and Waveshaping

2.2.2 Encoder

2.2.2.1 1000BASE-T

2.2.2.2 100BASE-TX

2.2.2.3 10BASE-T

2.2.3 Receive Side Network Interface

2.2.3.1 Analog to Digital Converter

2.2.3.2 Active Hybrid

2.2.3.3 Echo Canceller

2.2.3.4 NEXT Canceller

2.2.3.5 Baseline Wander Canceller

2.2.3.6 Digital Adaptive Equalizer

2.2.3.7 Digital Phase Lock Loop

2.2.3.8 Link Monitor

2.2.3.9 Signal Detection

2.2.4 Decoder

2.2.4.1 1000BASE-T

2.2.4.2 100BASE-TX

2.2.4.3 10BASE-T

2.3 1.25 GHz SERDES Interface

2.3.1 Electrical Interface

2.4 MAC Interfaces

2.4.1 SGMII

2.4.1.1 SGMII Speed and Link

2.4.1.2 SGMII TRR Blocking

2.4.1.3 False SERDES Link Up Prevention

2.4.2 RGMII

2.4.3 10/100 Mbps Functionality

2.4.4 TX_ER and RX_ER Coding

2.5 Loopback

2.5.1 System Interface Loopback

2.5.2 Line Loopback

2.5.3 External Loopback

2.6 Resets

2.7 Power Management

2.7.1 Low Power Modes

2.7.1.1 IEEE Power Down Mode

2.7.1.2 Copper Energy Detect Modes

2.7.2 RGMII/SGMII MAC Interface Power Down

2.8 Auto-Negotiation

2.8.1 10/100/1000BASE-T Auto-Negotiation

2.8.2 1000BASE-X Auto-Negotiation

2.8.3 SGMII Auto-Negotiation

2.8.3.1 Serial Interface Auto-Negotiation Bypass Mode

2.9 CRC Error Counter and Frame Counter

2.9.1 Enabling the CRC Error Counter and Packet Counter

2.10 Packet Generator

2.11 1.25G PRBS Generator and Checker

2.12 MDI/MDIX Crossover

2.13 Polarity Correction

2.14 FLP Exchange Complete with No Link

2.15 Duplex Mismatch Indicator

2.16 LED

2.16.1 LED Polarity

2.16.2 Pulse Stretching and Blinking

2.16.3 Bi-Color LED Mixing

2.16.4 Modes of Operation

2.16.4.1 Compound LED Modes

2.16.4.2 Speed Blink

2.16.4.3 Manual Override

2.16.4.4 MODE 1, MODE 2, MODE 3, MODE 4

2.17 Interrupt

2.18 Configuring the 88E1510/88E1518/88E1512/88E1514 Device

2.18.1 Hardware Configuration

2.18.2 Software Configuration - Management Interface

2.18.2.1 Preamble Suppression

2.19 Jumbo Packet Support

2.20 Temperature Sensor

2.21 Regulators and Power Supplies

2.21.1 AVDD18

2.21.2 AVDDC18

2.21.3 AVDD33

2.21.4 DVDD

2.21.5 REG_IN

2.21.6 AVDD18_OUT

2.21.7 DVDD_OUT

2.21.8 VDDO

2.21.9 Power Supply Sequencing

3 88E1510/88E1518/88E1512/88E1514 Register Description

3.1 PHY MDIO Register Description

4 Electrical Specifications

4.1 Absolute Maximum Ratings

4.2 Recommended Operating Conditions

4.3 Package Thermal Information

4.3.1 Thermal Conditions for 88E1510/88E1518 48-pin, QFN Package

4.3.2 Thermal Conditions for 88E1512/88E1514 56-pin, QFN Package

4.4 88E1510/88E1518 Current Consumption

4.4.1 Current Consumption when using External Regulators

4.4.2 Current Consumption when using Internal Regulators

4.5 88E1512 Current Consumption

4.5.1 Current Consumption when using External Regulators

4.5.2 Current Consumption when using Internal Regulators

4.6 88E1514 Current Consumption

4.6.1 Current Consumption when using External Regulators

4.6.2 Current Consumption when using Internal Regulators

4.7 DC Operating Conditions

4.7.1 Digital Pins

4.7.2 IEEE DC Transceiver Parameters

4.8 AC Electrical Specifications

4.8.1 Reset Timing

4.8.2 XTAL_IN/XTAL_OUT Timing

4.8.3 LED to CONFIG Timing

4.9 SGMII Timing

4.9.1 SGMII Output AC Characteristics

4.9.2 SGMII Input AC Characteristics

4.10 RGMII Timing

4.10.1 RGMII AC Characteristics

4.10.2 RGMII Delay Timing for Different RGMII Modes

4.10.2.1 PHY Input - TX_CLK Delay when Register 21_2.4 = 0

4.10.2.2 PHY Input - TX_CLK Delay when Register 21_2.4 = 1

4.10.2.3 PHY Output - RX_CLK Delay

4.10.2.4 PHY Output - RX_CLK Delay

4.11 MDC/MDIO Timing

4.12 IEEE AC Transceiver Parameters

4.13 Latency Timing

4.13.1 RGMII to 1000BASE-T Transmit Latency Timing

4.13.2 RGMII to 100BASE-TX Transmit Latency Timing

4.13.3 RGMII to 10BASE-T Transmit Latency Timing

4.13.4 1000BASE-T to RGMII Receive Latency Timing

4.13.5 100BASE-TX to RGMII Receive Latency Timing

4.13.6 10BASE-T to RGMII Receive Latency Timing

4.13.7 10/100/1000BASE-T to SGMII Latency Timing

4.13.8 SGMII to 10/100/1000BASE-T Latency Timing

5 Package Mechanical Dimensions

5.1 48-Pin QFN Package

5.2 56-Pin QFN Package

6 Part Order Numbering/Package Marking

6.1 Part Order Numbering

6.2 Package Marking

6.2.1 Commercial

6.2.2 Industrial

A Revision History

Contact Information

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc