TDA9885 也是一个免调整,多标准(PAL 制和 NTST 制)视频和伴音中频信号的锁相环

TDA9885是免调整多标准(PAL 制和 NTSC 制)的负极性调制的视频(VIF)和伴音中频

TDA9885

I 2 C 总线控制的单标准和多标准中频锁相环解调芯片

1 概述

(SIF)信号 锁相环(PLL)解调器。

(PLL)解调器,可适用于负极性调制两种方式和 FM 伴音信号处理。

2 功能

采用 5V 电源电压

增益可控宽带视频中频放大器(VIF)、AC 耦合

采用有源载波再生的多标准同步解调方法:良好的线性解调,互调图形好、谐波少,还

门控相位检波器,适用于 L 和 L 加强型标准。

全集成 VIF 压控振荡器(VCO),不需调整、频率可通过 I 2 C 总线对各种负极性和正极性

数字采集的 VIF 频率为 33.4,33.9,38.0,38.9,45.75 和 58.75 MHZ。

4 MHZ 基准频率输入:信号来自锁相环调谐系统(PLL)或晶体振荡器。

用于增益控制的 VIF 自动增益控制(AGC)检波器,对负极性调制信号作峰值同步检波;

有脉冲响应优良。

调制标准转接。

对正极性调制信号作峰值白电平检波。

经过引脚 OP1 作外部 AGC 调整。

精密全数字自动频率控制(AFC)检波器,具有 4 位(比特)是数摸转换器,通过 I 2 C

总线可读出 AFC 位。

控制。

经过 I 2 C 总线或用电位器可以调整 TOP(Take Over Point)

全集成伴音载波陷波器的陷波频率为 4.5,5.5,6.0 和 6.5 MHZ ,可由 FM 锁相环振荡器

适用于单基准准伴音载频分离方式的伴音中频(SIF)输入,可由 PLL 控制。

增益可控 SIF 放大器的 AGC 作用,使单基准 QSS(伴音准分离方式)混频器,通过 I 2 C

总线的转换,工作于高性能的单标准 QSS 方式和内载频方式。

AM 解调器 没有外部基准电路。

不需调整的具有选择性的 FM—PLL 解调器,具有高的线性度和低噪声特性

由 4 个 I 2 C 总线的地址可供选择

所有功能都用 I 2 C 总线控制

I 2 C 总线的收发信机带有可编程模块地址(MAD)的引脚

3 应用领域

可用于电视(TV),磁带录像机(VTR),机顶盒(STB)和 PC 机。

-1-

�

参 数

TDA9885

I 2 C 总线控制的单标准和多标准中频锁相环解调芯片

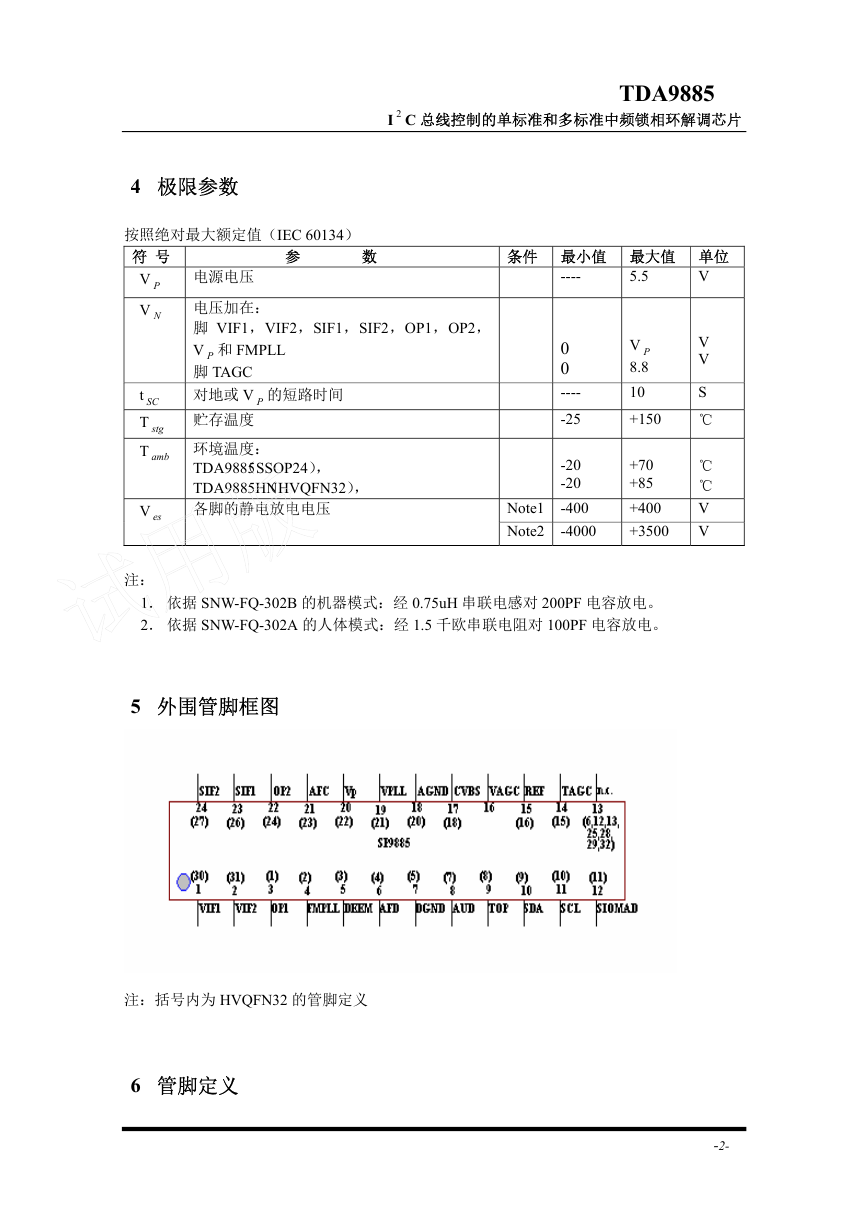

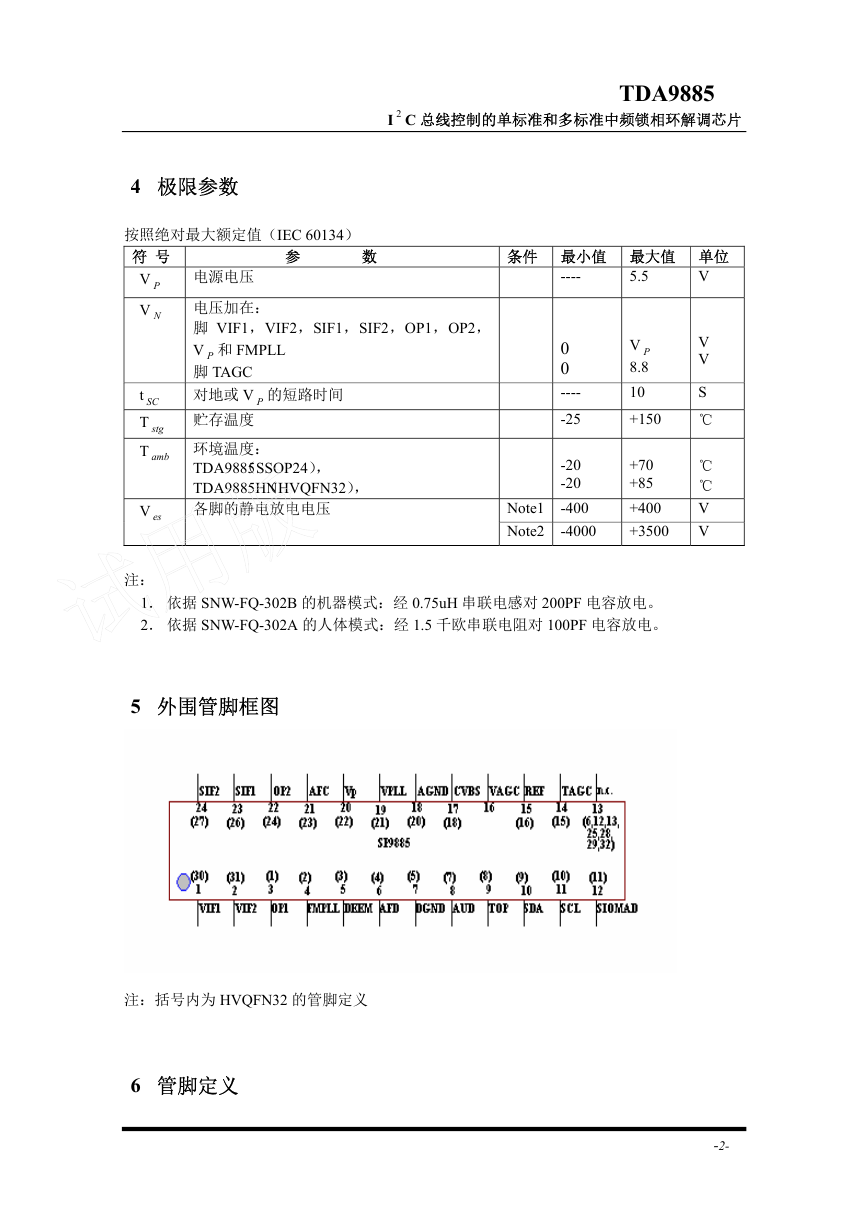

4 极限参数

按照绝对最大额定值(IEC 60134)

符 号

V P 电源电压

V N 电压加在:

脚 VIF1,VIF2,SIF1,SIF2,OP1,OP2,

V P 和 FMPLL

脚 TAGC

t SC 对地或 V P 的短路时间

T stg 贮存温度

T amb 环境温度:

TDA9885(SSOP24),

TDA9885HN(HVQFN32),

条件 最小值 最大值 单位

5.5

V

V P

8.8

10

+150

+70

+85

+400

+3500

V

V

S

℃

℃

℃

V

V

----

0

0

----

-25

-20

-20

-400

-4000

Note1

Note2

V es 各脚的静电放电电压

注:

1. 依据 SNW-FQ-302B 的机器模式:经 0.75uH 串联电感对 200PF 电容放电。

2. 依据 SNW-FQ-302A 的人体模式:经 1.5 千欧串联电阻对 100PF 电容放电。

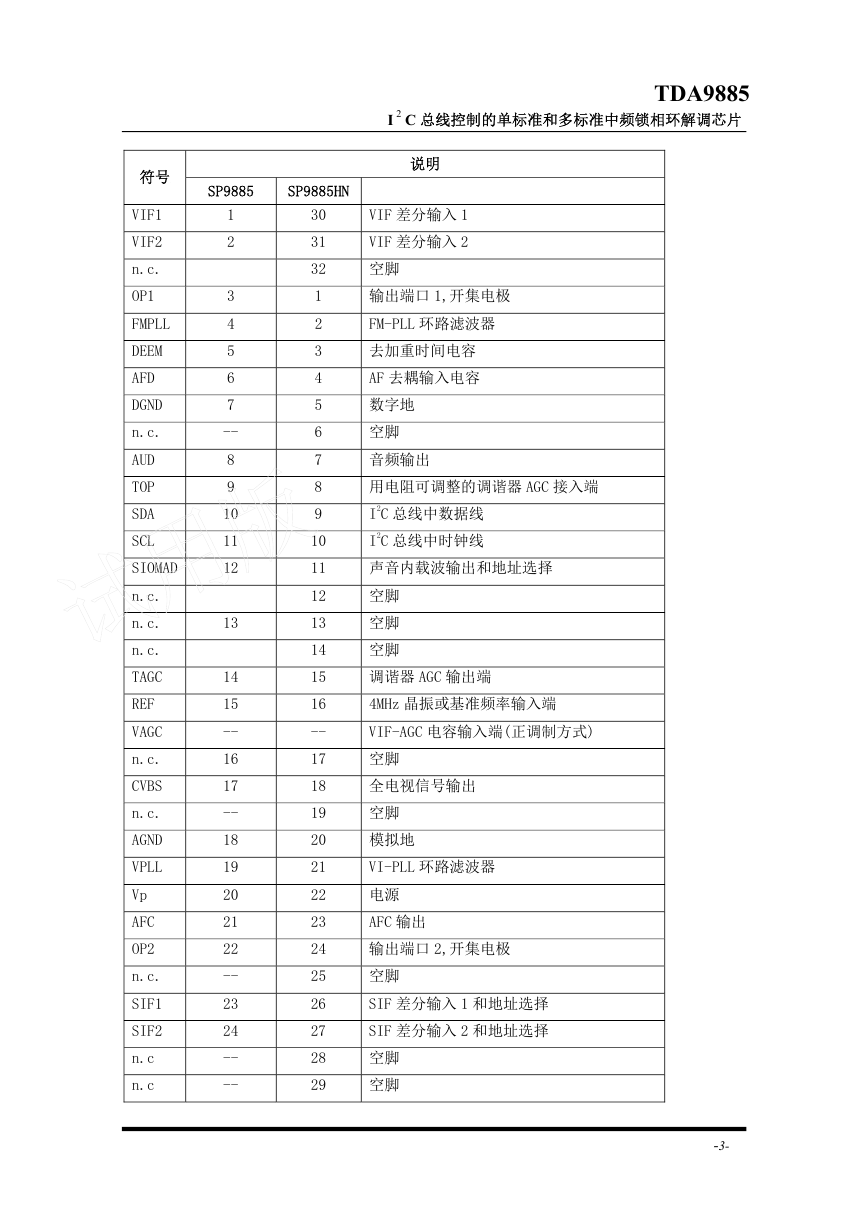

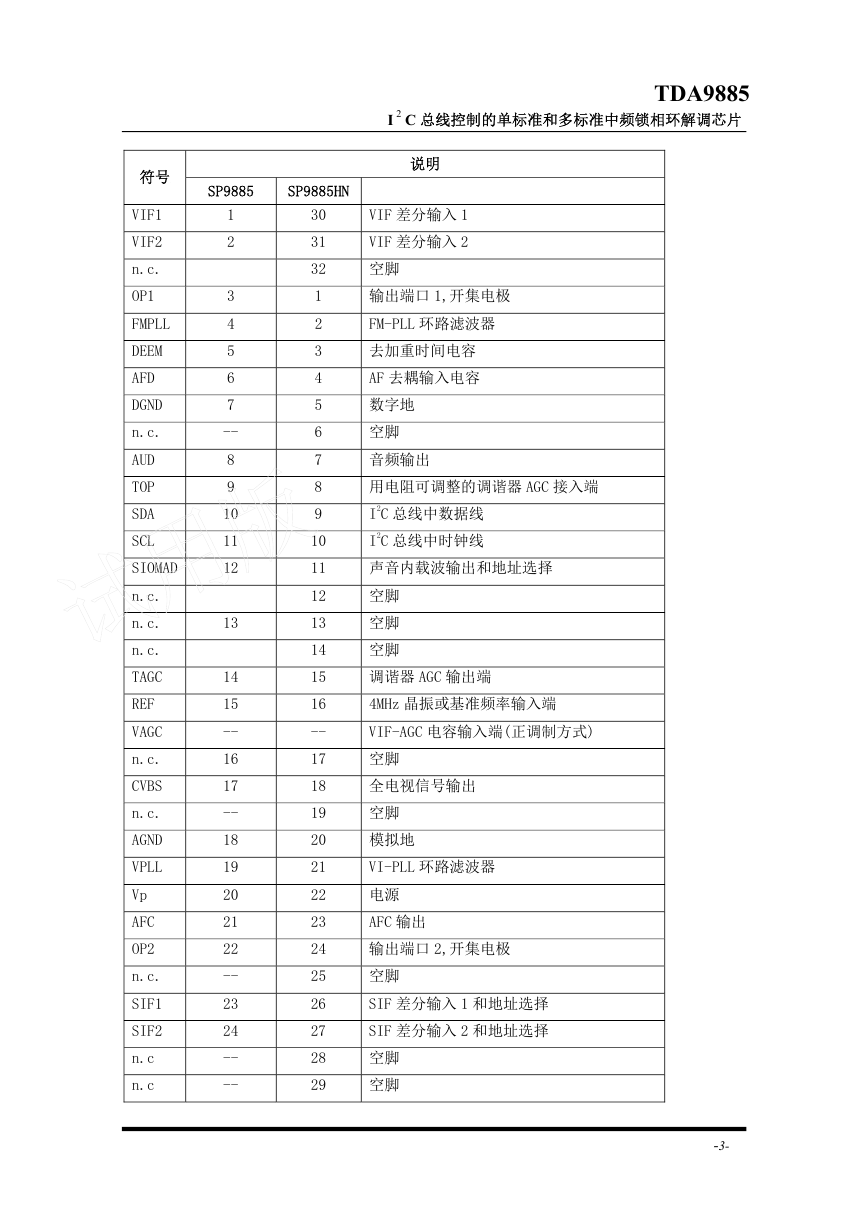

5 外围管脚框图

注:括号内为 HVQFN32 的管脚定义

6 管脚定义

-2-

�

符号

说明

空脚

30

31

32

SP9885

VIF 差分输入 2

VIF 差分输入 1

SP9885HN

TDA9885

I 2 C 总线控制的单标准和多标准中频锁相环解调芯片

VIF1

VIF2

n.c.

OP1

FMPLL

DEEM

AFD

DGND

n.c.

AUD

TOP

用电阻可调整的调谐器 AGC 接入端

输出端口 1,开集电极

FM-PLL 环路滤波器

AF 去耦输入电容

去加重时间电容

5

6

7

音频输出

3

4

5

6

7

8

数字地

1

2

8

9

1

2

3

4

--

空脚

10

11

12

13

14

15

--

16

17

--

18

19

20

21

22

--

23

24

--

--

SDA

SCL

SIOMAD

n.c.

n.c.

n.c.

TAGC

REF

VAGC

n.c.

CVBS

n.c.

AGND

VPLL

Vp

AFC

OP2

n.c.

SIF1

SIF2

n.c

n.c

9

10

11

12

13

14

15

16

--

17

18

19

20

21

22

23

24

25

26

27

28

29

I2C 总线中数据线

I2C 总线中时钟线

声音内载波输出和地址选择

空脚

空脚

空脚

调谐器 AGC 输出端

4MHz 晶振或基准频率输入端

VIF-AGC 电容输入端(正调制方式)

空脚

全电视信号输出

空脚

模拟地

VI-PLL 环路滤波器

电源

AFC 输出

输出端口 2,开集电极

空脚

SIF 差分输入 1 和地址选择

SIF 差分输入 2 和地址选择

空脚

空脚

-3-

�

TDA9885

I 2 C 总线控制的单标准和多标准中频锁相环解调芯片

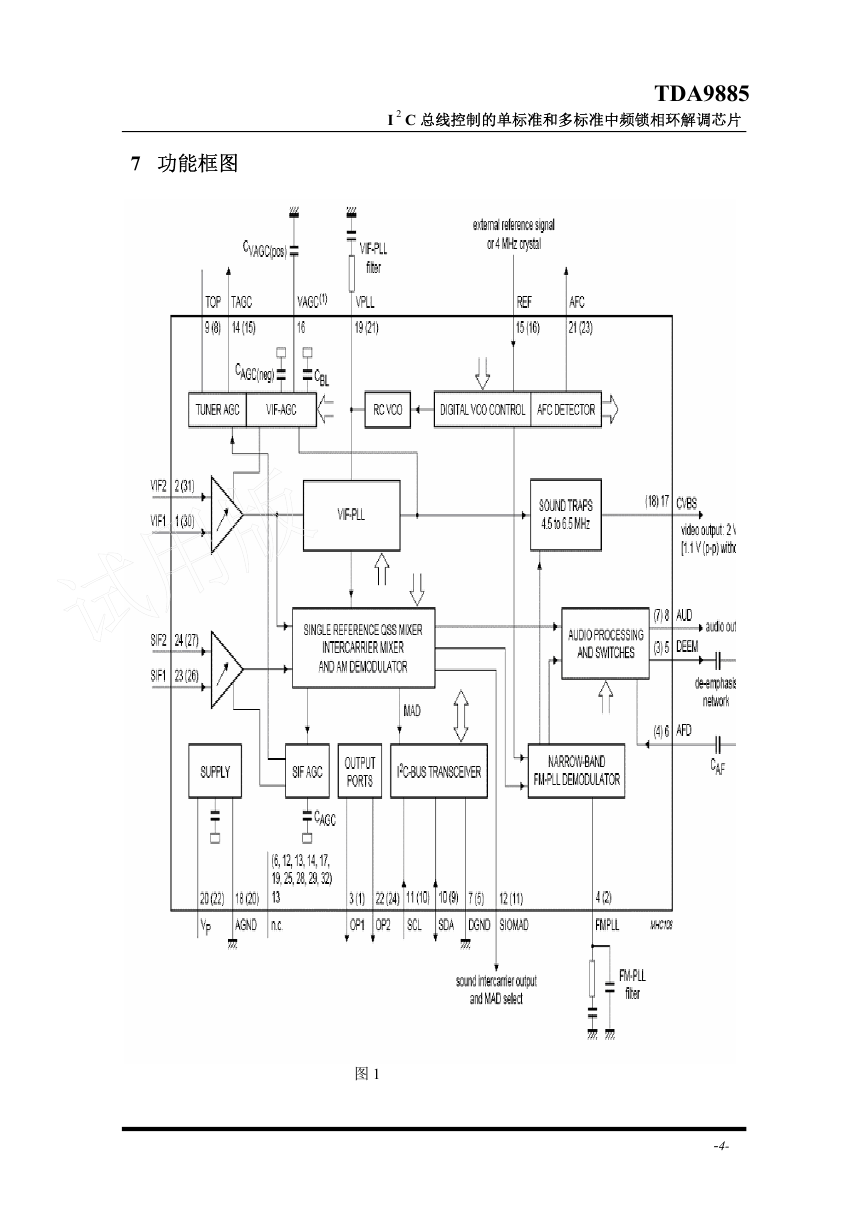

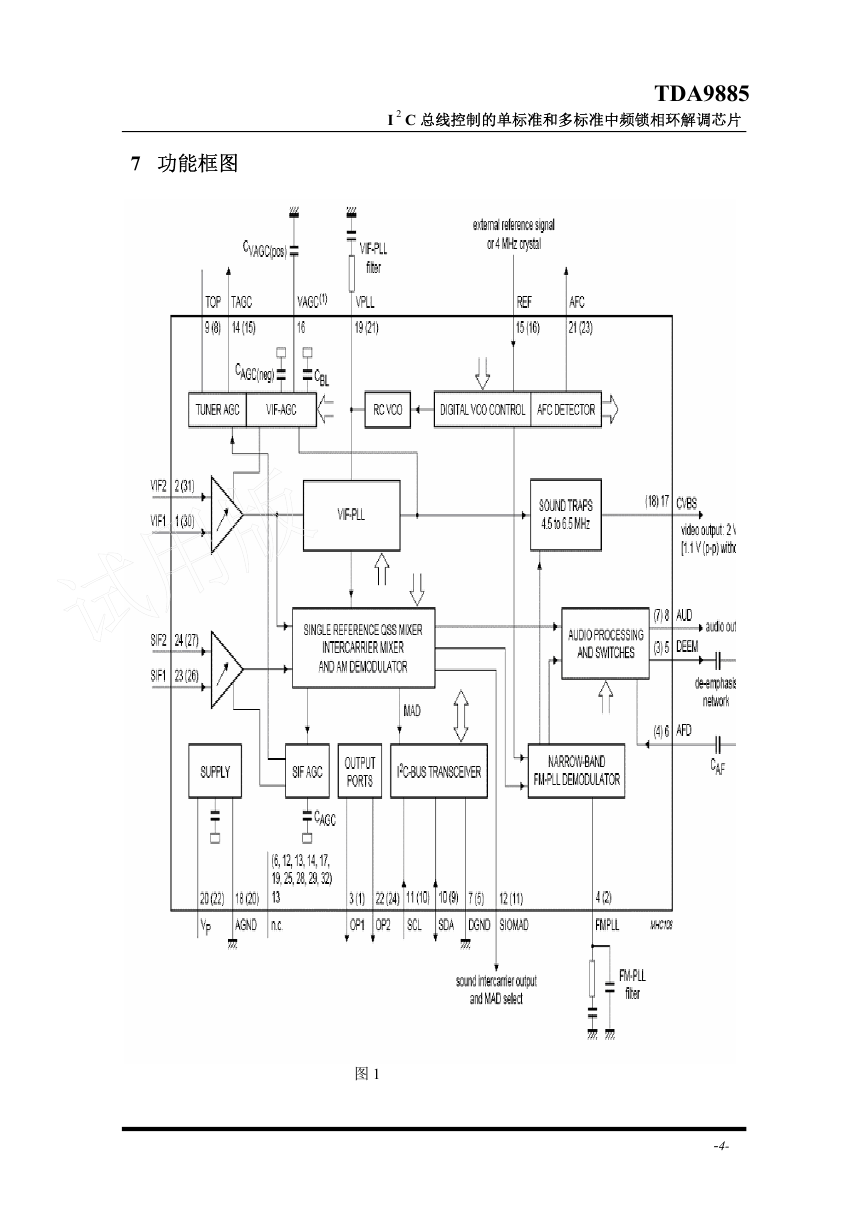

7 功能框图

图 1

-4-

�

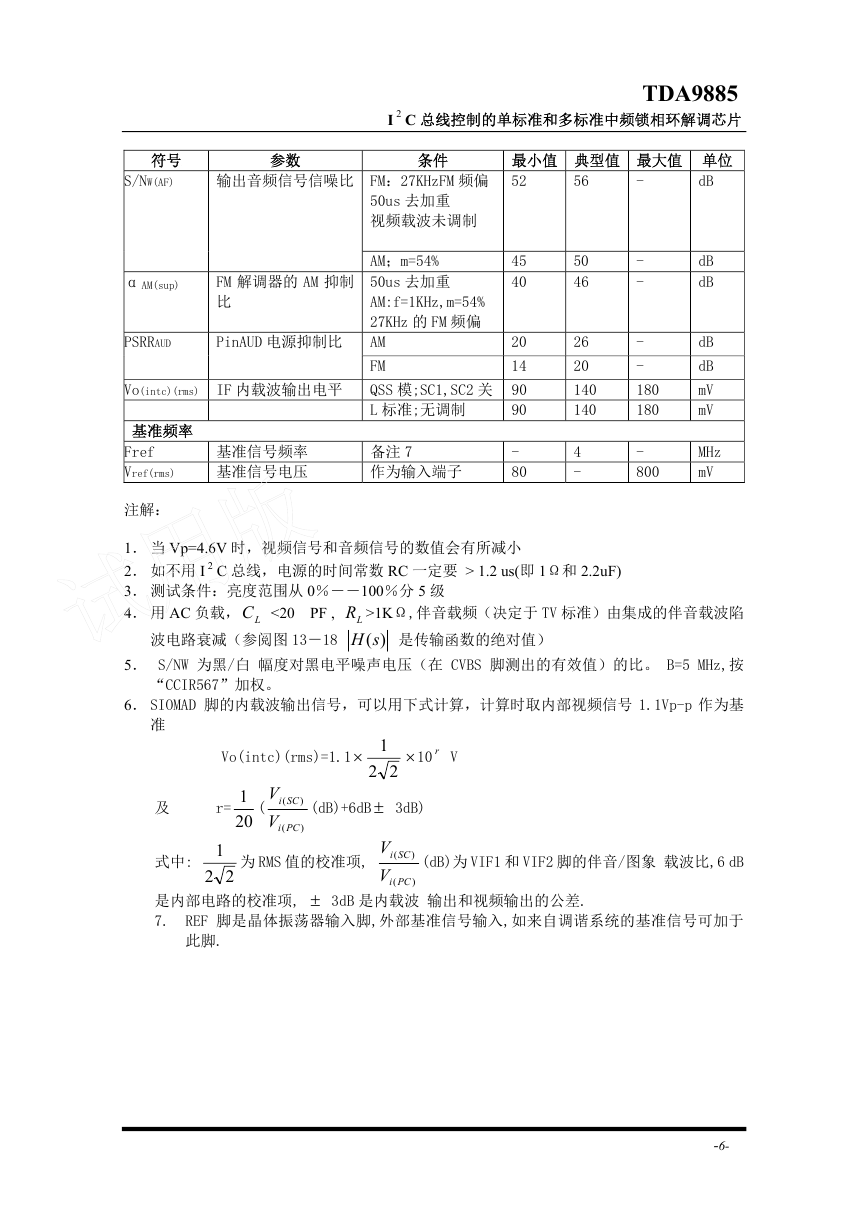

符号

参数

工作电压

工作电流

条件

备注 1 和 2

TDA9885

I 2 C 总线控制的单标准和多标准中频锁相环解调芯片

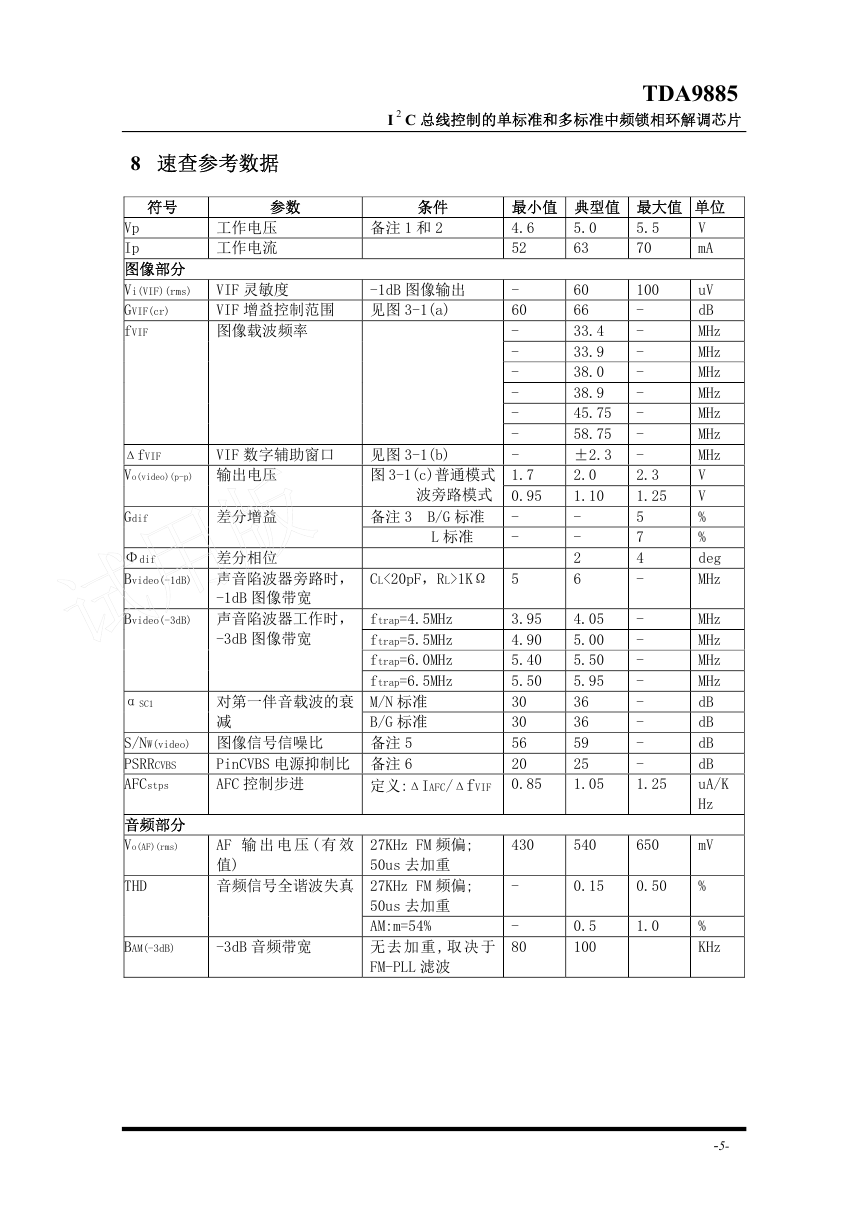

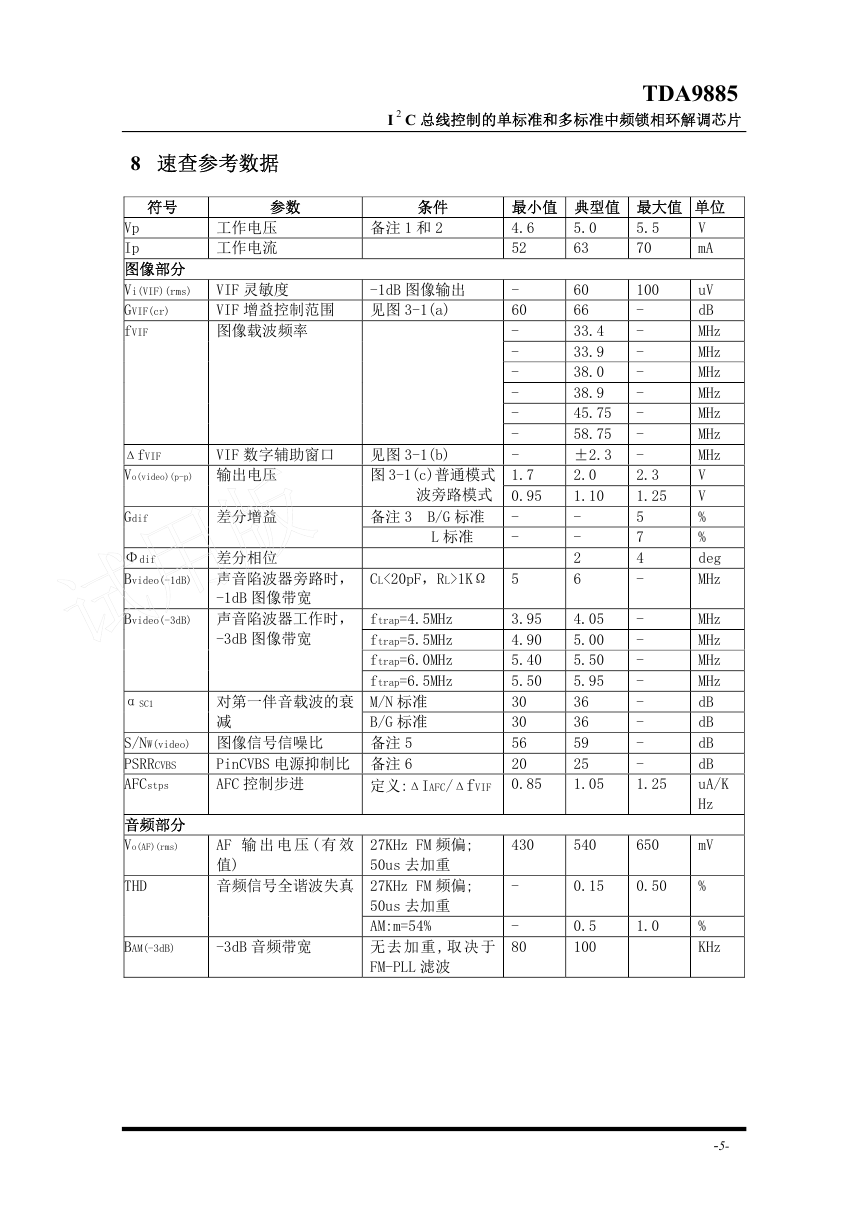

8 速查参考数据

Vp

Ip

图像部分

Vi(VIF)(rms)

GVIF(cr)

fVIF

ΔfVIF

Vo(video)(p-p) 输出电压

-

60

-

-

-

-

-

-

-

1.7

波旁路模式 0.95

VIF 灵敏度

VIF 增益控制范围 见图 3-1(a)

图像载波频率

最小值 典型值 最大值 单位

4.6

52

VIF 数字辅助窗口 见图 3-1(b)

5.0

63

5.5

70

V

mA

-1dB 图像输出

Gdif

差分增益

图 3-1(c)普通模式

备注 3 B/G 标准

L 标准

60

66

33.4

33.9

38.0

38.9

45.75

58.75

±2.3

2.0

1.10

-

-

2

6

100

-

-

-

-

-

-

-

-

2.3

1.25

5

7

4

-

uV

dB

MHz

MHz

MHz

MHz

MHz

MHz

MHz

V

V

%

%

deg

MHz

Φdif

Bvideo(-1dB) 声音陷波器旁路时,

差分相位

CL<20pF,RL>1KΩ

-1dB 图像带宽

Bvideo(-3dB) 声音陷波器工作时,

-3dB 图像带宽

ftrap=4.5MHz

ftrap=5.5MHz

ftrap=6.0MHz

ftrap=6.5MHz

M/N 标准

B/G 标准

备注 5

PinCVBS 电源抑制比 备注 6

AFC 控制步进

对第一伴音载波的衰

减

定义:ΔIAFC/ΔfVIF

S/NW(video) 图像信号信噪比

PSRRCVBS

AFCstps

αSC1

-

-

5

3.95

4.90

5.40

5.50

30

30

56

20

0.85

4.05

5.00

5.50

5.95

36

36

59

25

1.05

-

-

-

-

-

-

-

-

1.25

MHz

MHz

MHz

MHz

dB

dB

dB

dB

uA/K

Hz

音频部分

Vo(AF)(rms)

THD

AF 输 出 电 压 ( 有 效

值)

音频信号全谐波失真

BAM(-3dB)

-3dB 音频带宽

27KHz FM 频偏;

50us 去加重

27KHz FM 频偏;

50us 去加重

AM:m=54%

无 去 加重 , 取 决 于

FM-PLL 滤波

430

540

650

mV

-

-

80

0.15

0.50

%

0.5

100

1.0

%

KHz

-5-

�

50

46

dB

dB

参数

条件

56

-

dB

PinAUD 电源抑制比

输出音频信号信噪比

FM 解调器的 AM 抑制

比

最小值 典型值 最大值 单位

52

FM:27KHzFM 频偏

50us 去加重

视频载波未调制

AM;m=54%

50us 去加重

AM:f=1KHz,m=54%

27KHz 的 FM 频偏

AM

TDA9885

I 2 C 总线控制的单标准和多标准中频锁相环解调芯片

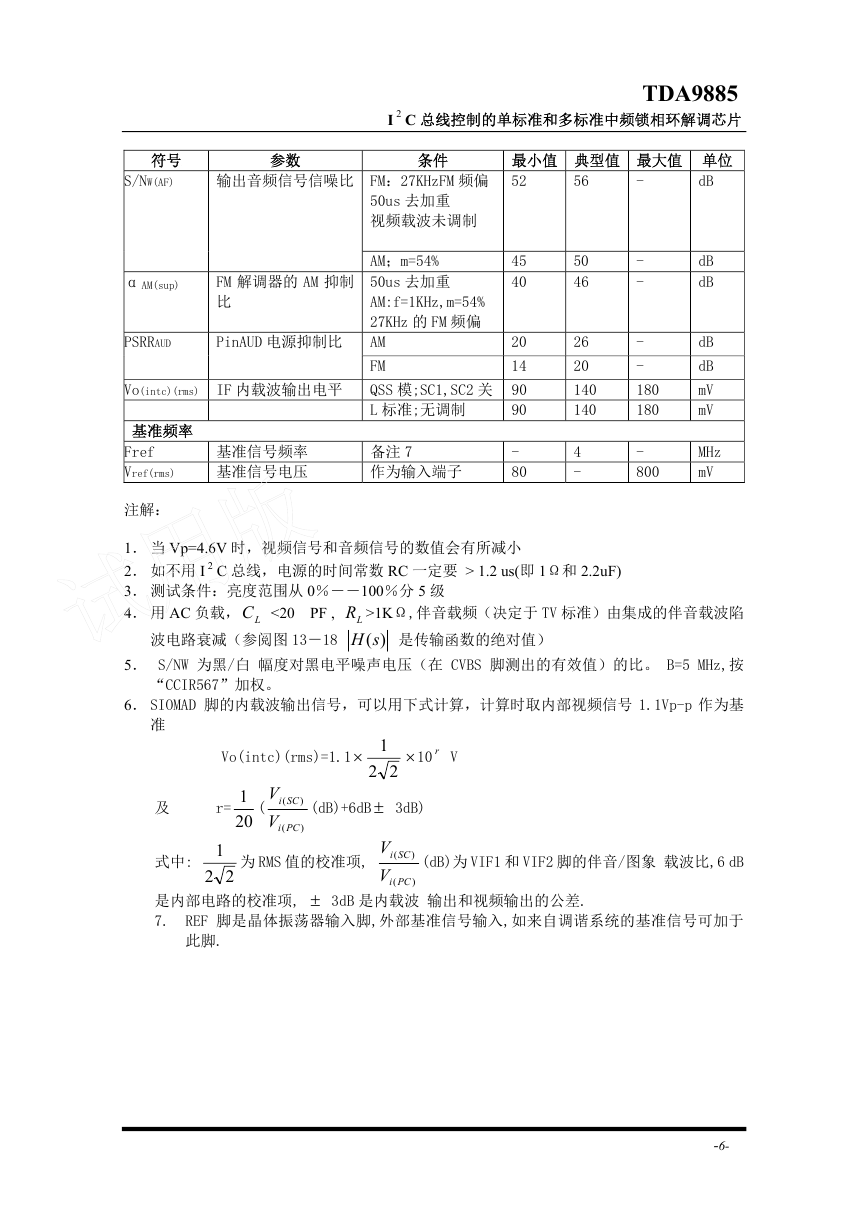

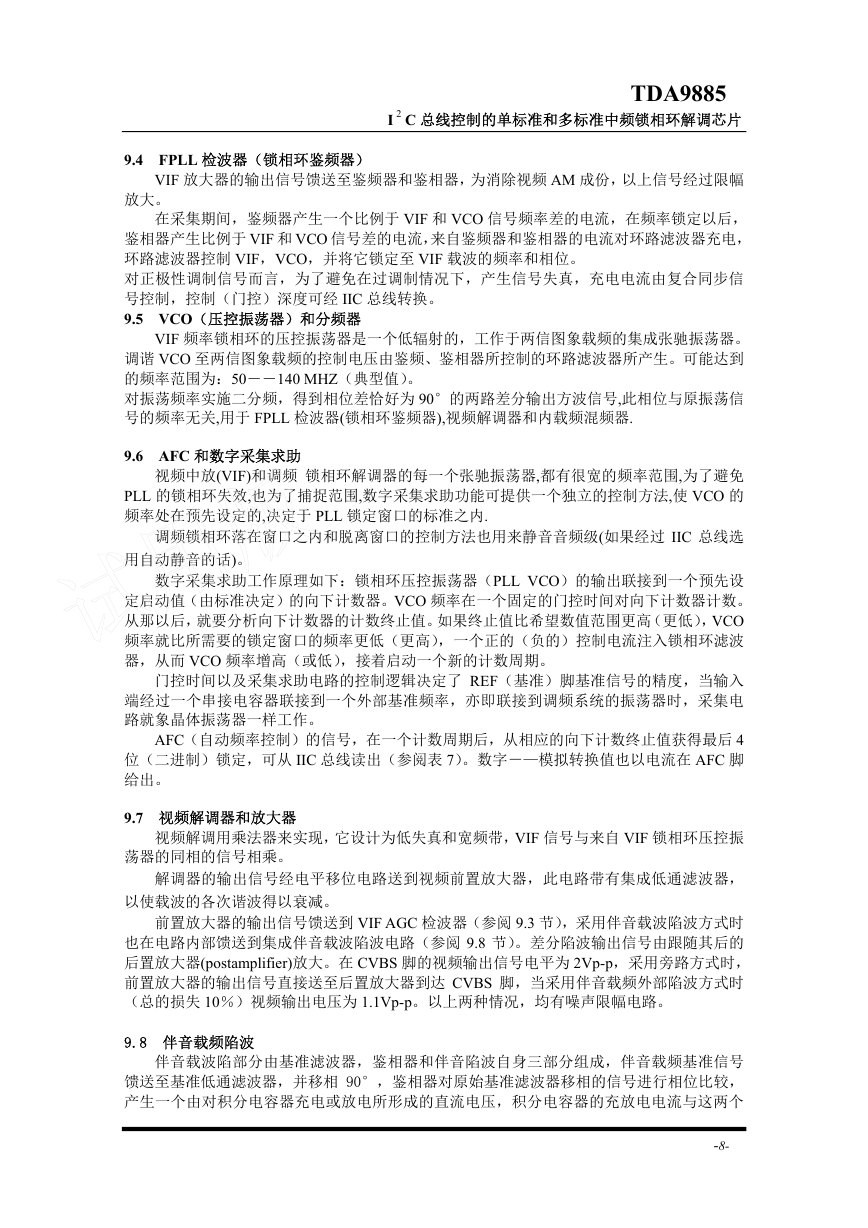

符号

S/NW(AF)

αAM(sup)

PSRRAUD

Vo(intc)(rms) IF 内载波输出电平

基准频率

Fref

Vref(rms)

注解:

1. 当 Vp=4.6V 时,视频信号和音频信号的数值会有所减小

2. 如不用 I 2 C 总线,电源的时间常数 RC 一定要 > 1.2 us(即 1Ω和 2.2uF)

3. 测试条件:亮度范围从 0%――100%分 5 级

4. 用 AC 负载, LC <20 PF ,

波电路衰减(参阅图 13-18

LR >1KΩ,伴音载频(决定于 TV 标准)由集成的伴音载波陷

)(sH

是传输函数的绝对值)

QSS 模;SC1,SC2 关 90

L 标准;无调制

90

基准信号频率

基准信号电压

备注 7

作为输入端子

26

20

140

140

dB

dB

mV

mV

180

180

-

800

45

40

20

14

-

80

4

-

-

-

-

-

MHz

mV

FM

5. S/NW 为黑/白 幅度对黑电平噪声电压(在 CVBS 脚测出的有效值)的比。 B=5 MHz,按

6. SIOMAD 脚的内载波输出信号,可以用下式计算,计算时取内部视频信号 1.1Vp-p 作为基

“CCIR567”加权。

准

Vo(intc)(rms)=1.1×

1

及 r= 20

(

V

SCi

(

V

PCi

(

)

)

(dB)+6dB ± 3dB)

1

22

× 10 r V

式中:

1

22

为 RMS 值的校准项,

V

SCi

(

V

PCi

(

)

)

(dB)为 VIF1 和 VIF2 脚的伴音/图象 载波比,6 dB

是内部电路的校准项, ± 3dB 是内载波 输出和视频输出的公差.

7. REF 脚是晶体振荡器输入脚,外部基准信号输入,如来自调谐系统的基准信号可加于

此脚.

-6-

�

TDA9885

I 2 C 总线控制的单标准和多标准中频锁相环解调芯片

9 基本说明

图 1 表示器件的简单方框图,它由以下基本功能块组成:

视频中频放大器(VIF 放大器)

调皮器 AGC 和 VIF-AGC

VIF-AGC 检波器

频率锁相环(FPLL)检波器(锁相环鉴频器)

VCO(压控振荡器)和分频器

AFC 和数字采集求助

视频解调器和放大器

伴音载波陷波

SIF(伴音中频)放大器

SIF-AGC 检波器

单基准 QSS(准伴音中频分离)混频器

AM 解调器

调频解调器和采集求助

音频放大器和静音时间常数

内置稳压管

I 2 C 总线收发信器和 MAD(模块地址)

9.1 视频中频(VIF)放大器

视频中频(VIF)放大器由 3 级交流耦合差分放大器组成,增益控制由发射极电路完成。总的

增益控制范围的典型值为 66dB,差分电路的输入阻抗,典型值为 2KΩ电阻与 3pF 电容相并联。

9.2 谐器 AGC 和 VIF-AGC

这个功能块使 VIF-AGC 和 SIF-AGC 检波器产生的电压,在内部对 VIF 和 SIF 放大器能进行

处理,并产生调谐器 AGC 所需要的控制电流,调谐器 AGC 控制电流的产生可以经过 IIC 总线(见

表 13)或通过 TOP 脚的电位器(在这种情况下, IIC 总线的信息不能贮存,与设计有关)来实施,电

位器的状态可以自动检测, IIC 总线不能调整。

而且,可以通过一个比较器,根据从 AGC 检波器获得的电压,测定 VIF 输入端的输入电压是

否已高于 200uV,这个信息可通过 IIC 总线(位 VIFLEV=1)读出。

9.3 VIF-AGC 检波器

增益控制由同步头电平检波(负极性调制)或峰值白电平检波(正极性调制)完成。负

极性调制时,同步头电平电压通过快速峰值检波器储存在一个积分电容器上,这个电压同一

个基准电压(标称同步头电平)在比较器中相比较,从而使比较器对 AGC 电容器放电或充电,

以获得所需要的 VIF 增益,总的 AGC 反应时间很快,以至于能承受飞机的震颤声而不出现过

载现象。

当信号为正极性调制时,峰值白电平电压同基准电压(标称白电平)在比较器中相比较,

从而使比较器对外部的 AGC 电容器充电(快速)或放电(慢速)以获得所需要的 VIF 增益。

VIF 增益增加,需要很长的时间常数,这是因为峰值白电平在一场时间里仅出现一次。为了减

小这个时间常数,设置一个附加的电平检波器用来增加 AGC 电容器的放电电流(快速方式),

此时 VIF 幅度的步进式减小由实际检出的黑电平电压所控制。快速方式 AGC 阈值电平为视频

幅度的-6dB(典型值),快速方式状态也可用来提高 SIF-AGC 检波器的速度,在缺少峰值

白电平脉冲的情况下,VIF 增益的增加以+3dB 为限(典型值),这是通过将检出的实际黑电

平电压与相应的基准电压相应的基准电压相比较而得到的。

-7-

�

VIF 放大器的输出信号馈送至鉴频器和鉴相器,为消除视频 AM 成份,以上信号经过限幅

TDA9885

I 2 C 总线控制的单标准和多标准中频锁相环解调芯片

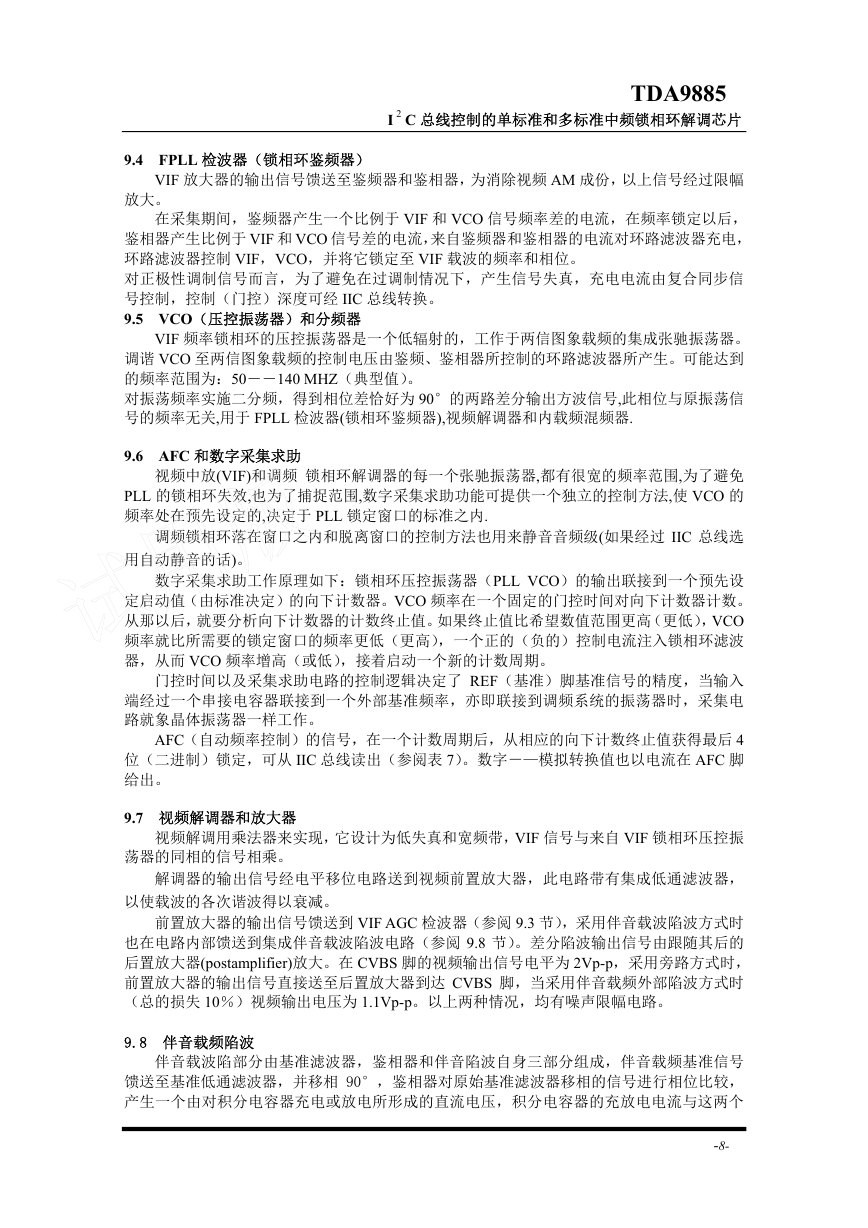

9.4 FPLL 检波器(锁相环鉴频器)

放大。

在采集期间,鉴频器产生一个比例于 VIF 和 VCO 信号频率差的电流,在频率锁定以后,

鉴相器产生比例于 VIF 和 VCO 信号差的电流,来自鉴频器和鉴相器的电流对环路滤波器充电,

环路滤波器控制 VIF,VCO,并将它锁定至 VIF 载波的频率和相位。

对正极性调制信号而言,为了避免在过调制情况下,产生信号失真,充电电流由复合同步信

号控制,控制(门控)深度可经 IIC 总线转换。

9.5 VCO(压控振荡器)和分频器

VIF 频率锁相环的压控振荡器是一个低辐射的,工作于两信图象载频的集成张驰振荡器。

调谐 VCO 至两信图象载频的控制电压由鉴频、鉴相器所控制的环路滤波器所产生。可能达到

的频率范围为:50――140 MHZ(典型值)。

对振荡频率实施二分频,得到相位差恰好为 90°的两路差分输出方波信号,此相位与原振荡信

号的频率无关,用于 FPLL 检波器(锁相环鉴频器),视频解调器和内载频混频器.

9.6 AFC 和数字采集求助

视频中放(VIF)和调频 锁相环解调器的每一个张驰振荡器,都有很宽的频率范围,为了避免

PLL 的锁相环失效,也为了捕捉范围,数字采集求助功能可提供一个独立的控制方法,使 VCO 的

频率处在预先设定的,决定于 PLL 锁定窗口的标准之内.

调频锁相环落在窗口之内和脱离窗口的控制方法也用来静音音频级(如果经过 IIC 总线选

用自动静音的话)。

数字采集求助工作原理如下:锁相环压控振荡器(PLL VCO)的输出联接到一个预先设

定启动值(由标准决定)的向下计数器。VCO 频率在一个固定的门控时间对向下计数器计数。

从那以后,就要分析向下计数器的计数终止值。如果终止值比希望数值范围更高(更低),VCO

频率就比所需要的锁定窗口的频率更低(更高),一个正的(负的)控制电流注入锁相环滤波

器,从而 VCO 频率增高(或低),接着启动一个新的计数周期。

门控时间以及采集求助电路的控制逻辑决定了 REF(基准)脚基准信号的精度,当输入

端经过一个串接电容器联接到一个外部基准频率,亦即联接到调频系统的振荡器时,采集电

路就象晶体振荡器一样工作。

AFC(自动频率控制)的信号,在一个计数周期后,从相应的向下计数终止值获得最后 4

位(二进制)锁定,可从 IIC 总线读出(参阅表 7)。数字-—模拟转换值也以电流在 AFC 脚

给出。

9.7 视频解调器和放大器

荡器的同相的信号相乘。

视频解调用乘法器来实现,它设计为低失真和宽频带,VIF 信号与来自 VIF 锁相环压控振

解调器的输出信号经电平移位电路送到视频前置放大器,此电路带有集成低通滤波器,

以使载波的各次谐波得以衰减。

前置放大器的输出信号馈送到 VIF AGC 检波器(参阅 9.3 节),采用伴音载波陷波方式时

也在电路内部馈送到集成伴音载波陷波电路(参阅 9.8 节)。差分陷波输出信号由跟随其后的

后置放大器(postamplifier)放大。在 CVBS 脚的视频输出信号电平为 2Vp-p,采用旁路方式时,

前置放大器的输出信号直接送至后置放大器到达 CVBS 脚,当采用伴音载频外部陷波方式时

(总的损失 10%)视频输出电压为 1.1Vp-p。以上两种情况,均有噪声限幅电路。

9.8 伴音载频陷波

伴音载波陷部分由基准滤波器,鉴相器和伴音陷波自身三部分组成,伴音载频基准信号

馈送至基准低通滤波器,并移相 90°,鉴相器对原始基准滤波器移相的信号进行相位比较,

产生一个由对积分电容器充电或放电所形成的直流电压,积分电容器的充放电电流与这两个

-8-

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc