计算机组成原理课程设计报告

班级:07 计算机 06 班

姓名: 杨佳学

学号: 20073069

完成时间:

2009 年 12 月 25 日

一、课程设计目的

1.在实验机上设计实现机器指令及对应的微指令(微程序)并验证,从而进一步掌握微程

序设计控制器的基本方法并了解指令系统与硬件结构的对应关系;

2.通过控制器的微程序设计,综合理解计算机组成原理课程的核心知识并进一步建立整机

系统的概念;

3.培养综合实践及独立分析、解决问题的能力。

二、课程设计的任务

针对 COP2000 实验仪,从详细了解该模型机的指令/微指令系统入手,以实现乘法和除

法运算功能为应用目标,在 COP2000 的集成开发环境下,设计全新的指令系统并编写对应

的微程序;之后编写实现乘法和除法的程序进行设计的验证。

三、 课程设计使用的设备(环境)

1.硬件

COP2000 实验仪

PC 机

2.软件

COP2000 仿真软件

四、课程设计的具体内容(步骤)

1.详细了解并掌握 COP 2000 模型机的微程序控制器原理,通过综合实验来实现

(1)该模型机指令系统的特点:

① 总体概述

COP2000 模型机包括了一个标准 CPU 所具备所有部件,这些部件包括:运算器 ALU、累

加器 A、工作寄存器 W、左移门 L、直通门 D、右移门 R、寄存器组 R0-R3、程序计数器 PC、

地址寄存器 MAR、堆栈寄存器 ST、中断向量寄存器 IA、输入端口 IN、输出端口寄存器 OUT、

程序存储器 EM、指令寄存器 IR、微程序计数器 uPC、微程序存储器 uM,以及中断控制电路、

跳转控制电路。其中运算器和中断控制电路以及跳转控制电路用 CPLD 来实现,其它电路都

是用离散的数字电路组成。微程序控制部分也可以用组合逻辑控制来代替。

模型机为 8 位机,数据总线、地址总线都为 8 位,但其工作原理与 16 位机相同。相比

而言 8 位机实验减少了烦琐的连线,但其原理却更容易被学生理解、吸收。

�

模型机的指令码为 8 位,根据指令类型的不同,可以有 0 到 2 个操作数。指令码的最

低两位用来选择 R0-R3 寄存器,在微程序控制方式中,用指令码做为微地址来寻址微程序

存储器,找到执行该指令的微程序。而在组合逻辑控制方式中,按时序用指令码产生相应

的控制位。在本模型机中,一条指令最多分四个状态周期,一个状态周期为一个时钟脉冲,

每个状态周期产生不同的控制逻辑,实现模型机的各种功能。模型机有 24 位控制位以控制

寄存器的输入、输出,选择运算器的运算功能,存储器的读写。

模型机的缺省的指令集分几大类: 算术运算指令、逻辑运算指令、移位指令、数据传

输指令、跳转指令、中断返回指令、输入/输出指令。

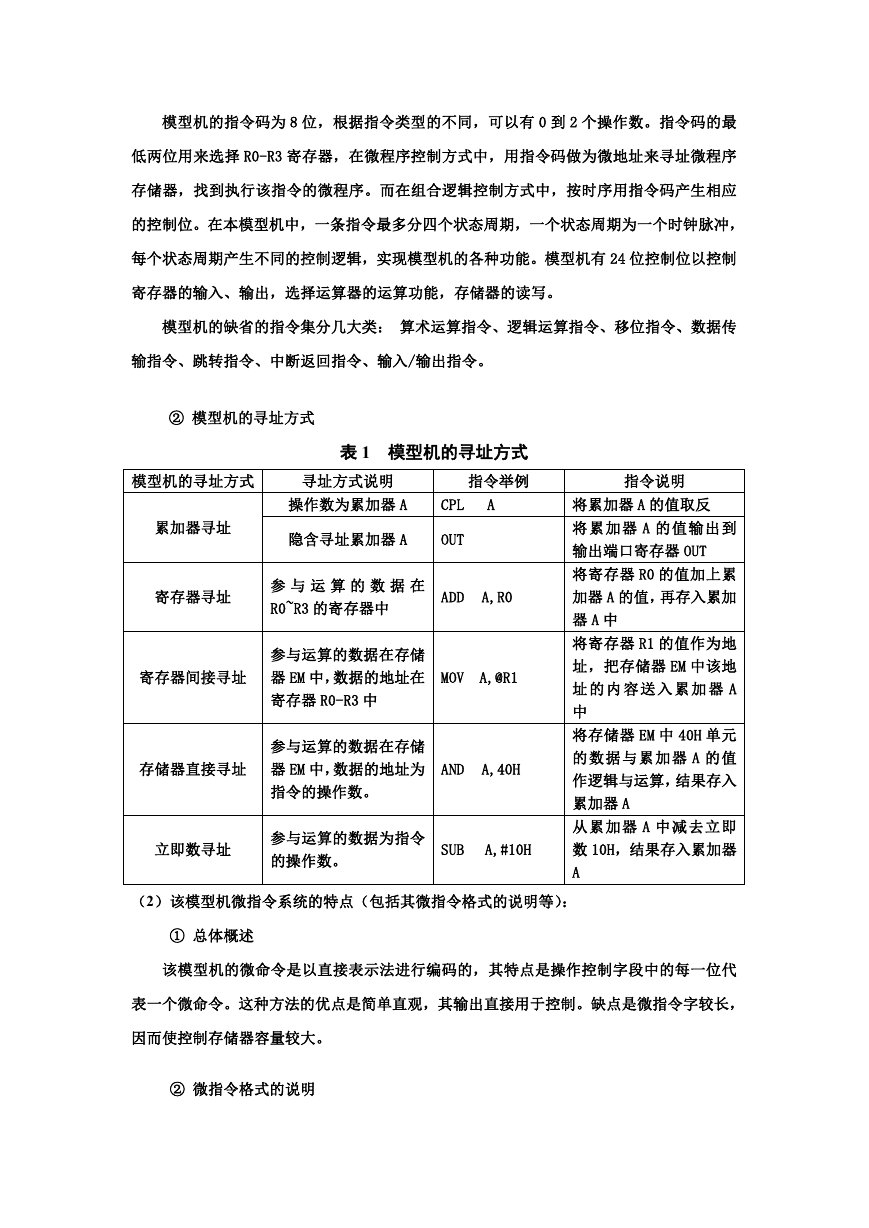

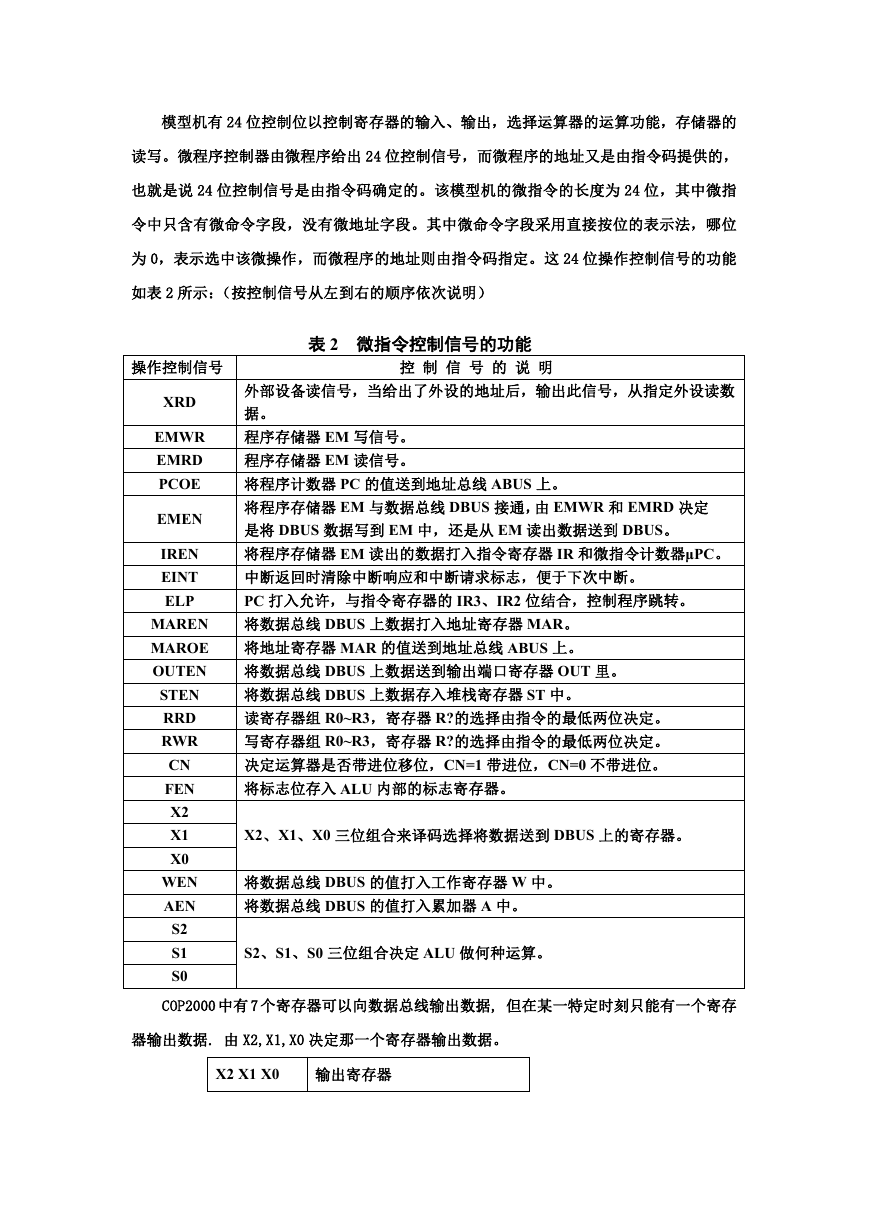

② 模型机的寻址方式

模型机的寻址方式

表 1 模型机的寻址方式

指令举例

寻址方式说明

指令说明

操作数为累加器 A

CPL

A

将累加器 A 的值取反

累加器寻址

隐含寻址累加器 A

OUT

寄存器寻址

参 与 运 算 的 数 据 在

R0~R3 的寄存器中

ADD

A,R0

寄存器间接寻址

参与运算的数据在存储

器 EM 中,数据的地址在

寄存器 R0-R3 中

MOV

A,@R1

存储器直接寻址

参与运算的数据在存储

器 EM 中,数据的地址为

指令的操作数。

AND

A,40H

立即数寻址

参与运算的数据为指令

的操作数。

SUB

A,#10H

将累加器 A 的值输出到

输出端口寄存器 OUT

将寄存器 R0 的值加上累

加器 A 的值,再存入累加

器 A 中

将寄存器 R1 的值作为地

址,把存储器 EM 中该地

址 的 内 容 送 入 累 加 器 A

中

将存储器 EM 中 40H 单元

的数据与累加器 A 的值

作逻辑与运算,结果存入

累加器 A

从累加器 A 中减去立即

数 10H,结果存入累加器

A

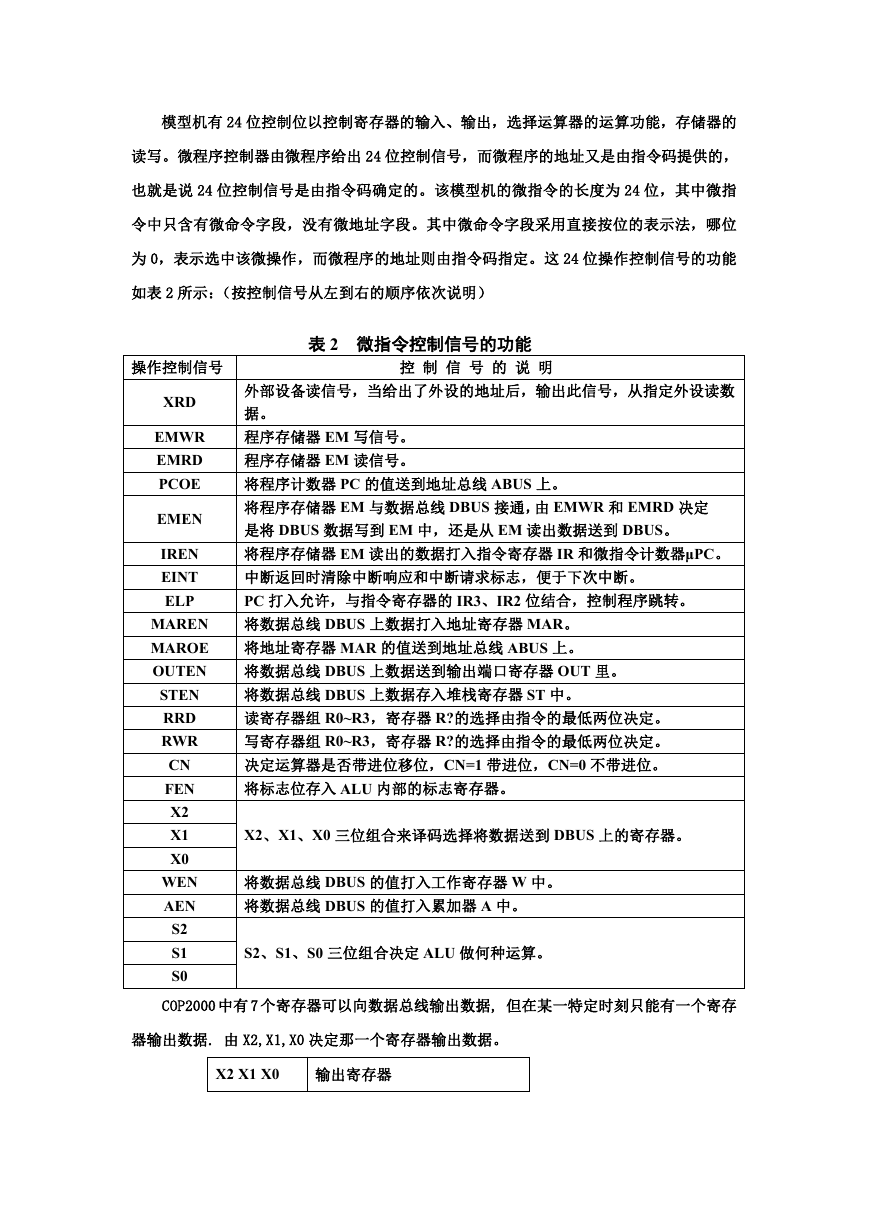

(2)该模型机微指令系统的特点(包括其微指令格式的说明等):

① 总体概述

该模型机的微命令是以直接表示法进行编码的,其特点是操作控制字段中的每一位代

表一个微命令。这种方法的优点是简单直观,其输出直接用于控制。缺点是微指令字较长,

因而使控制存储器容量较大。

② 微指令格式的说明

�

模型机有 24 位控制位以控制寄存器的输入、输出,选择运算器的运算功能,存储器的

读写。微程序控制器由微程序给出 24 位控制信号,而微程序的地址又是由指令码提供的,

也就是说 24 位控制信号是由指令码确定的。该模型机的微指令的长度为 24 位,其中微指

令中只含有微命令字段,没有微地址字段。其中微命令字段采用直接按位的表示法,哪位

为 0,表示选中该微操作,而微程序的地址则由指令码指定。这 24 位操作控制信号的功能

如表 2 所示:(按控制信号从左到右的顺序依次说明)

操作控制信号

控 制 信 号 的 说 明

表 2 微指令控制信号的功能

外部设备读信号,当给出了外设的地址后,输出此信号,从指定外设读数

据。

程序存储器 EM 写信号。

程序存储器 EM 读信号。

将程序计数器 PC 的值送到地址总线 ABUS 上。

将程序存储器 EM 与数据总线 DBUS 接通,由 EMWR 和 EMRD 决定

是将 DBUS 数据写到 EM 中,还是从 EM 读出数据送到 DBUS。

将程序存储器 EM 读出的数据打入指令寄存器 IR 和微指令计数器μPC。

中断返回时清除中断响应和中断请求标志,便于下次中断。

PC 打入允许,与指令寄存器的 IR3、IR2 位结合,控制程序跳转。

将数据总线 DBUS 上数据打入地址寄存器 MAR。

将地址寄存器 MAR 的值送到地址总线 ABUS 上。

将数据总线 DBUS 上数据送到输出端口寄存器 OUT 里。

将数据总线 DBUS 上数据存入堆栈寄存器 ST 中。

读寄存器组 R0~R3,寄存器 R?的选择由指令的最低两位决定。

写寄存器组 R0~R3,寄存器 R?的选择由指令的最低两位决定。

决定运算器是否带进位移位,CN=1 带进位,CN=0 不带进位。

将标志位存入 ALU 内部的标志寄存器。

X2、X1、X0 三位组合来译码选择将数据送到 DBUS 上的寄存器。

将数据总线 DBUS 的值打入工作寄存器 W 中。

将数据总线 DBUS 的值打入累加器 A 中。

S2、S1、S0 三位组合决定 ALU 做何种运算。

XRD

EMWR

EMRD

PCOE

EMEN

IREN

EINT

ELP

MAREN

MAROE

OUTEN

STEN

RRD

RWR

CN

FEN

X2

X1

X0

WEN

AEN

S2

S1

S0

COP2000 中有 7 个寄存器可以向数据总线输出数据, 但在某一特定时刻只能有一个寄存

器输出数据. 由 X2,X1,X0 决定那一个寄存器输出数据。

X2 X1 X0

输出寄存器

�

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

外部输入门

中断向量

堆栈寄存器

PC 寄存器

直通门

右移门

左移门

IN_OE

IA_OE

ST_OE

PC_OE

D_OE

R_OE

L_OE

没有输出

COP2000 中的运算器由一片 EPLD 实现. 有 8 种运算, 通过 S2,S1,S0 来选择。运算数据

由寄存器 A 及寄存器 W 给出, 运算结果输出到直通门 D。

S2 S1 S0

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

功能

A+W

A-W

A|W

A&W

加

减

或

与

A+W+C 带进位加

A-W-C

带进位减

~A

A

A 取反

输出 A

2。计算机中实现乘法和除法的原理

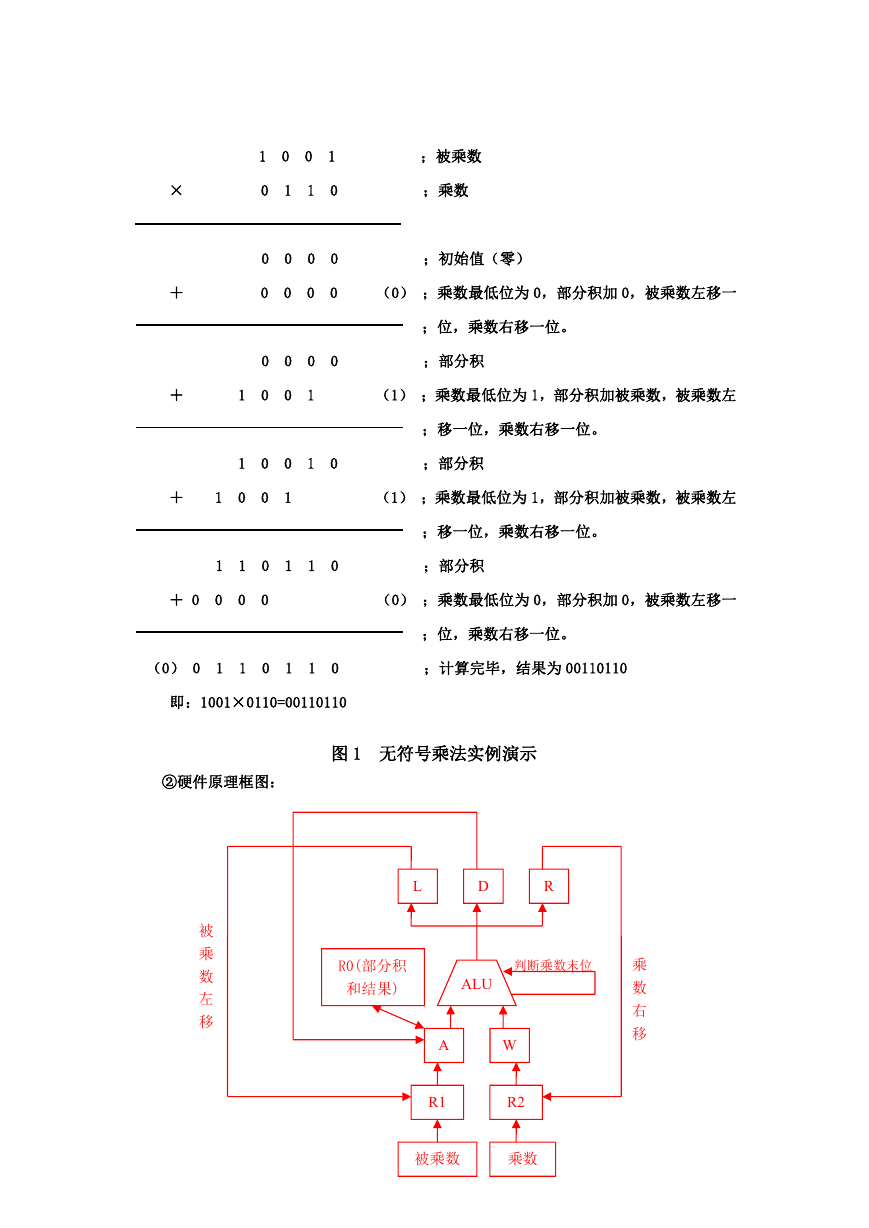

(1)无符号乘法

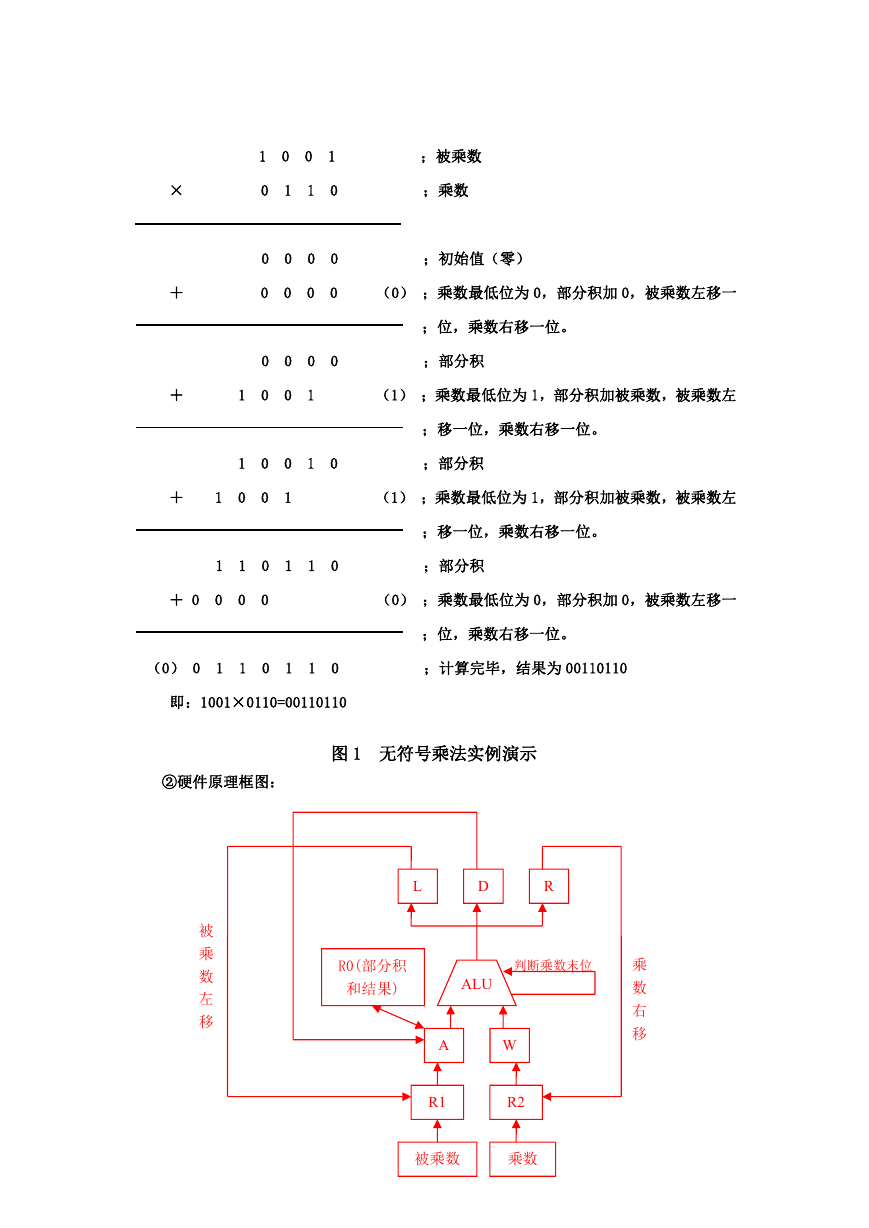

①实例演示(即,列 4 位乘法具体例子演算的算式):

被乘数为 1001(二进制),即为十进制的 9;乘数为 0110(二进制),即为十进制的 6。

那么,可以通过笔算得到:

即十进制运算结果为:

1001×0110=00110110

9×6=54

无符号乘法的实例演示如图 1 所示:

�

1

0

0

1

;被乘数

×

0

1

1

0

;乘数

0

0

0

0

0

0

0

0

+

+

+

+ 0

1

1

0

1

0

1

1

0

0

0

0

0

0

1

0

0

0

0

0

0

1

;初始值(零)

(0) ;乘数最低位为 0,部分积加 0,被乘数左移一

;位,乘数右移一位。

;部分积

(1) ;乘数最低位为 1,部分积加被乘数,被乘数左

;移一位,乘数右移一位。

1

0

;部分积

(1) ;乘数最低位为 1,部分积加被乘数,被乘数左

;移一位,乘数右移一位。

1

1

0

;部分积

(0) ;乘数最低位为 0,部分积加 0,被乘数左移一

;位,乘数右移一位。

(0) 0

1

1

0

1

1

0

;计算完毕,结果为 00110110

即:1001×0110=00110110

图 1 无符号乘法实例演示

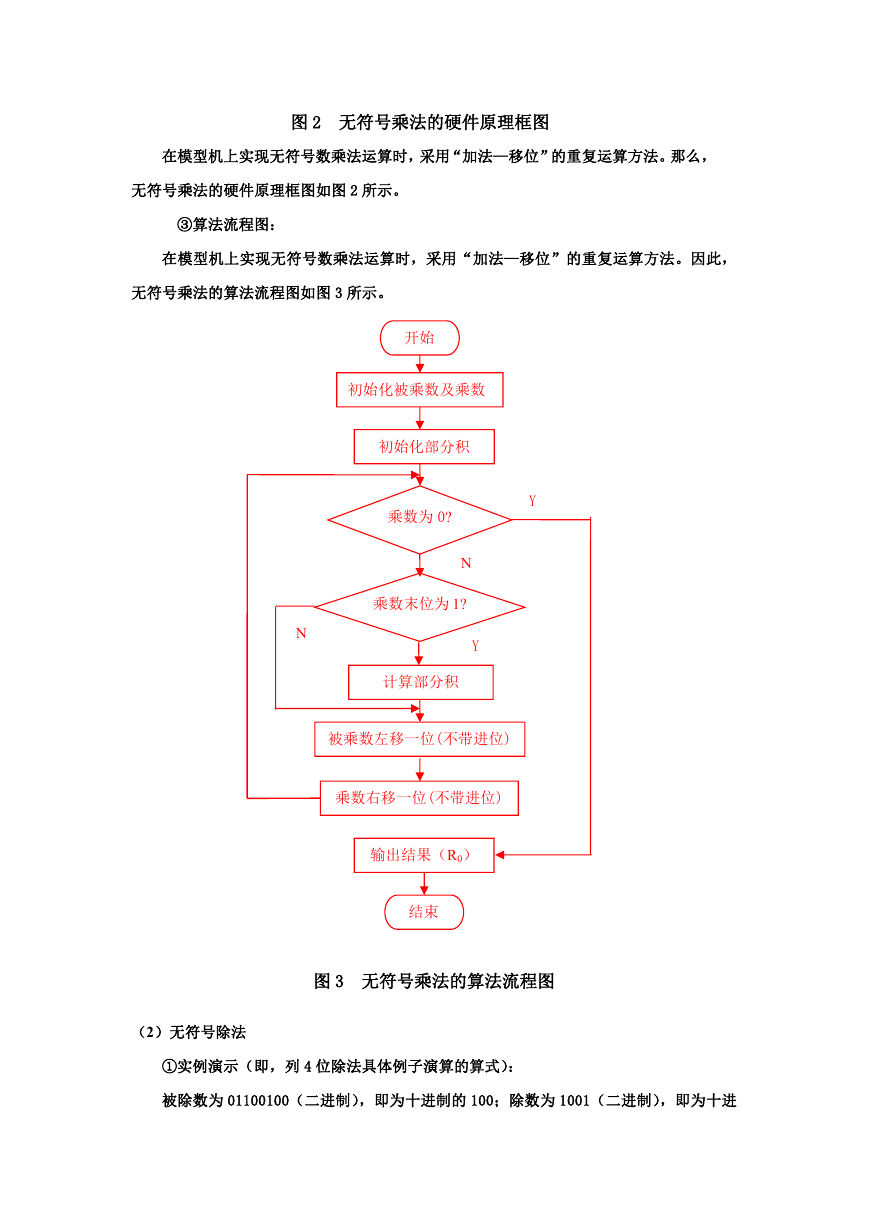

②硬件原理框图:

被

乘

数

左

移

L

D

R

R0(部分积

和结果)

ALU

判断乘数末位

A

R1

W

R2

被乘数

乘数

乘

数

右

移

�

图 2 无符号乘法的硬件原理框图

在模型机上实现无符号数乘法运算时,采用“加法—移位”的重复运算方法。那么,

无符号乘法的硬件原理框图如图 2 所示。

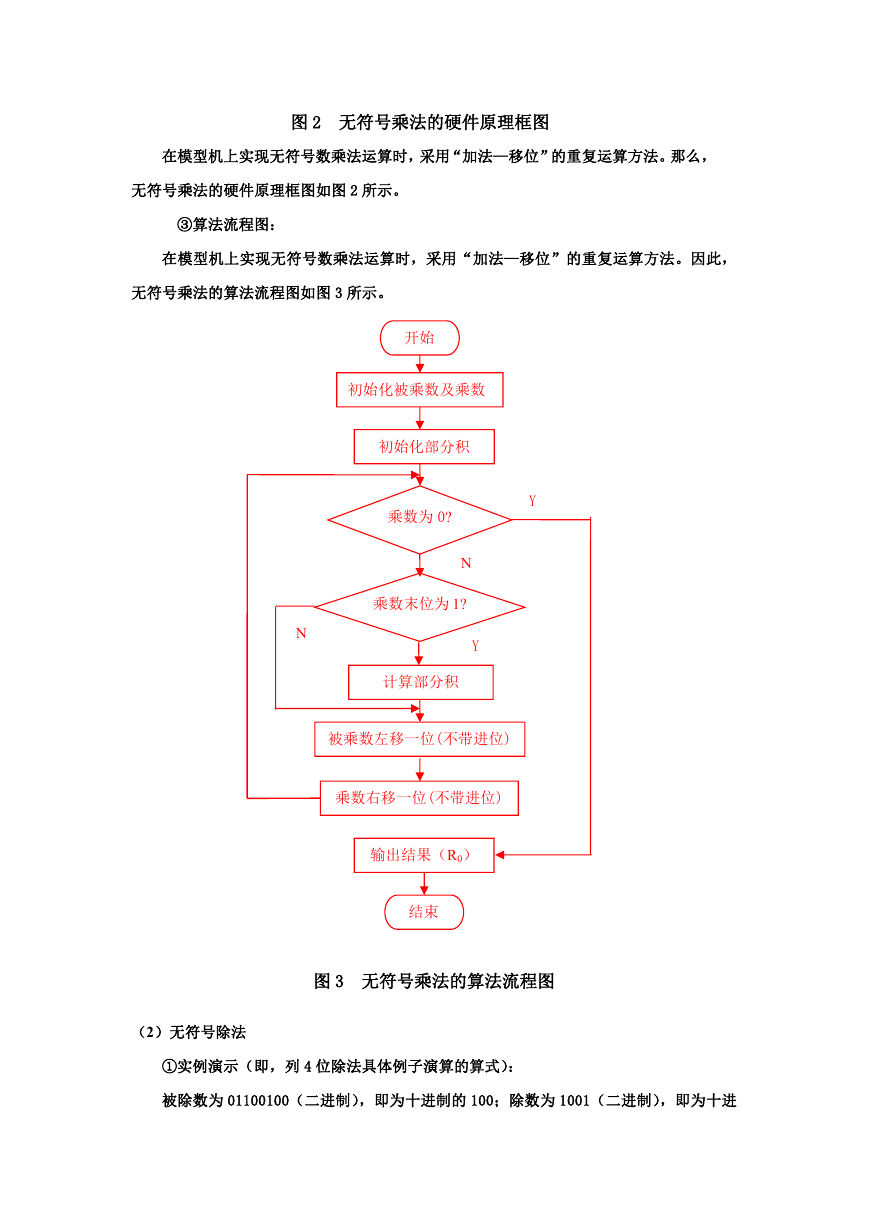

③算法流程图:

在模型机上实现无符号数乘法运算时,采用“加法—移位”的重复运算方法。因此,

无符号乘法的算法流程图如图 3 所示。

开始

初始化被乘数及乘数

初始化部分积

乘数为 0?

Y

N

N

乘数末位为 1?

Y

计算部分积

被乘数左移一位(不带进位)

乘数右移一位(不带进位)

输出结果(R0)

结束

图 3 无符号乘法的算法流程图

(2)无符号除法

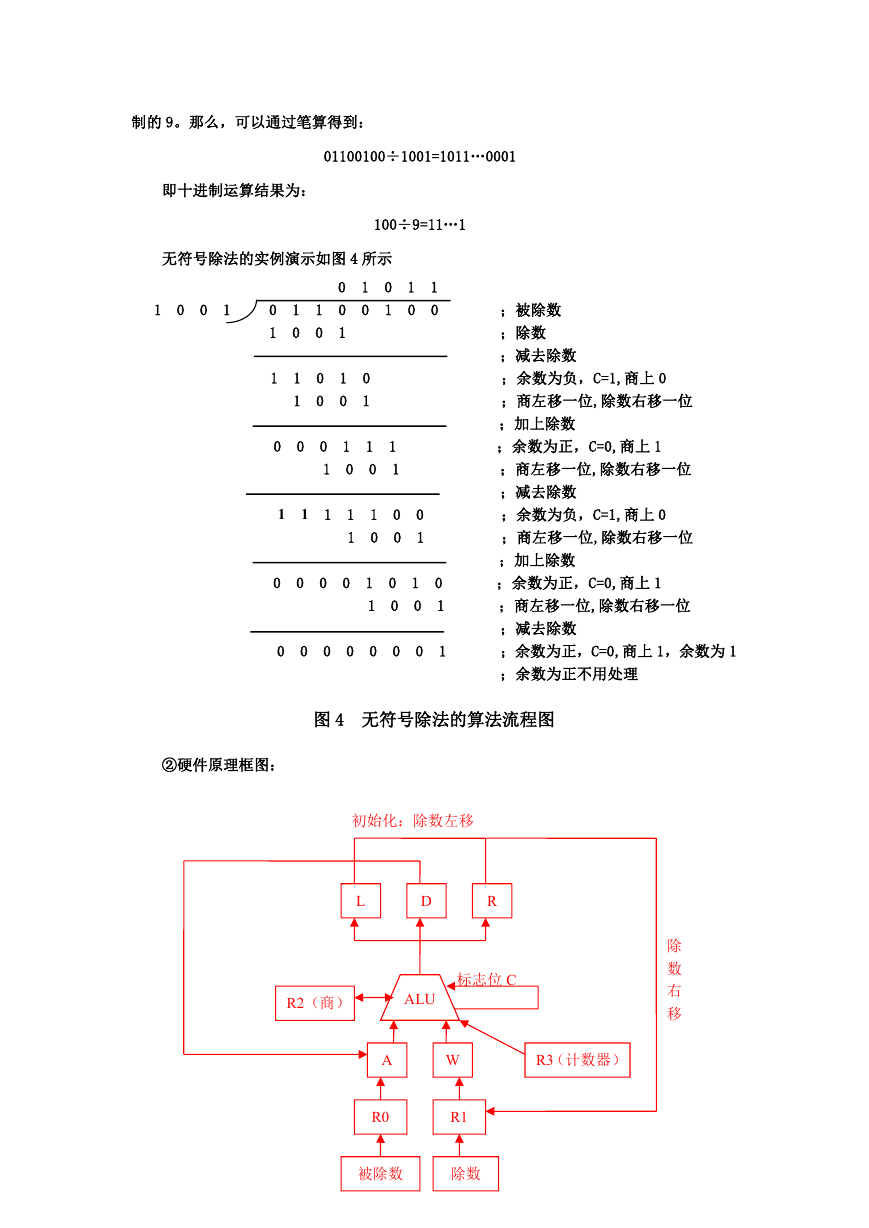

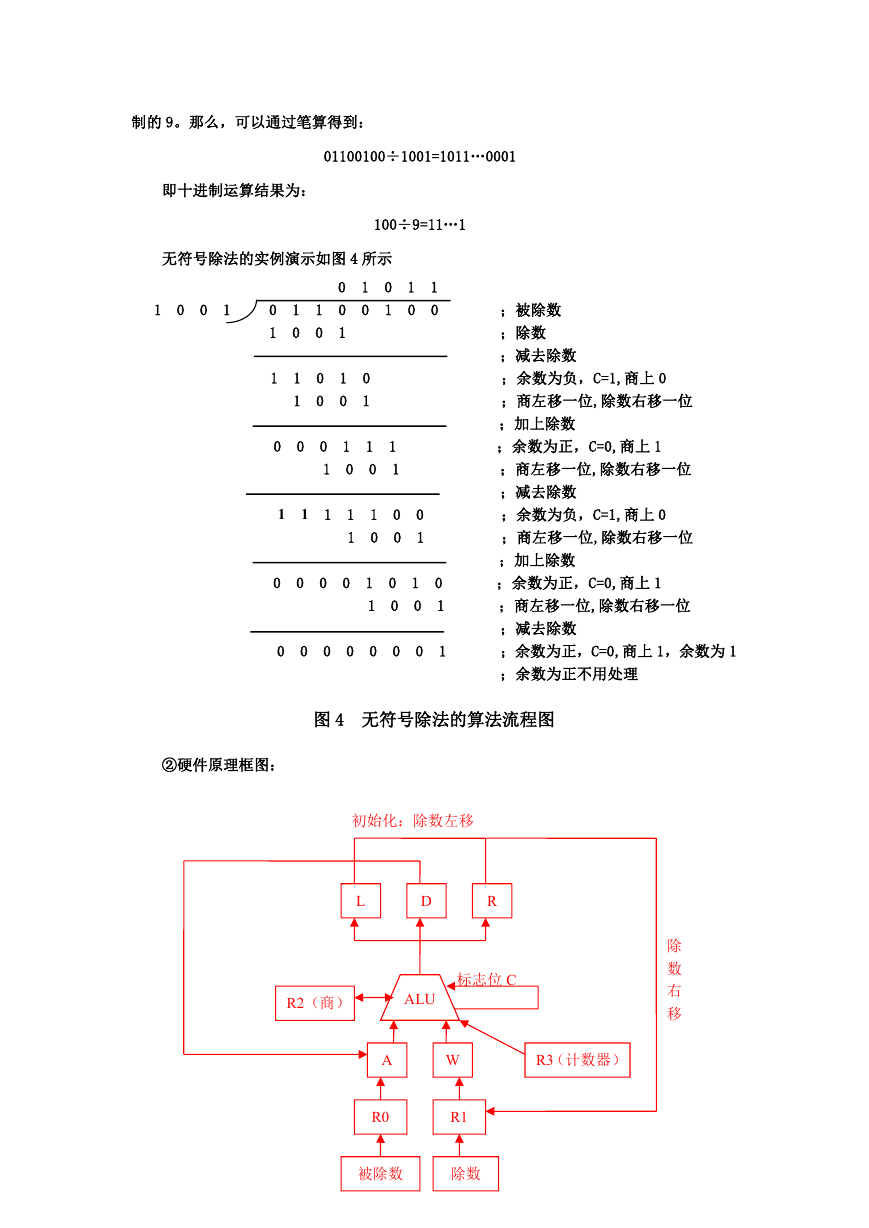

①实例演示(即,列 4 位除法具体例子演算的算式):

被除数为 01100100(二进制),即为十进制的 100;除数为 1001(二进制),即为十进

�

制的 9。那么,可以通过笔算得到:

01100100÷1001=1011…0001

即十进制运算结果为:

无符号除法的实例演示如图 4 所示

100÷9=11…1

1

0

0

1

0

1

1

0

1

0

0

1

1

1

0

1

1

1

0

0

0

0

0

1

1

0

1

0

0

1

0

0

0

1

1

0

1

0

1

1

1

1

1

1

1

1

0

0

0

0

1

0

0

0

0

1

1

0

0

1

0

0

1

0

0

0

0

0

0

0

1

;被除数

;除数

;减去除数

;余数为负,C=1,商上 0

;商左移一位,除数右移一位

;加上除数

;余数为正,C=0,商上 1

;商左移一位,除数右移一位

;减去除数

;余数为负,C=1,商上 0

;商左移一位,除数右移一位

;加上除数

;余数为正,C=0,商上 1

;商左移一位,除数右移一位

;减去除数

;余数为正,C=0,商上 1,余数为 1

;余数为正不用处理

图 4 无符号除法的算法流程图

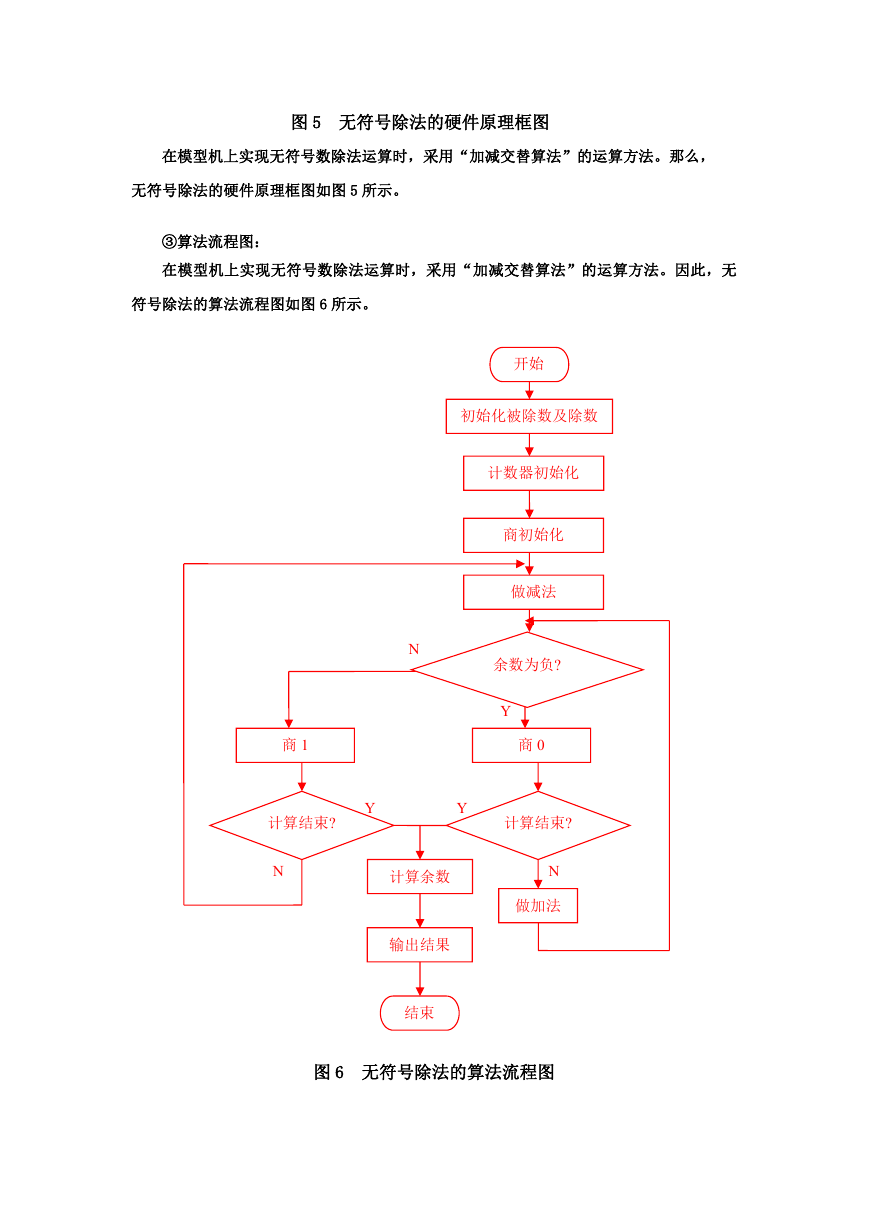

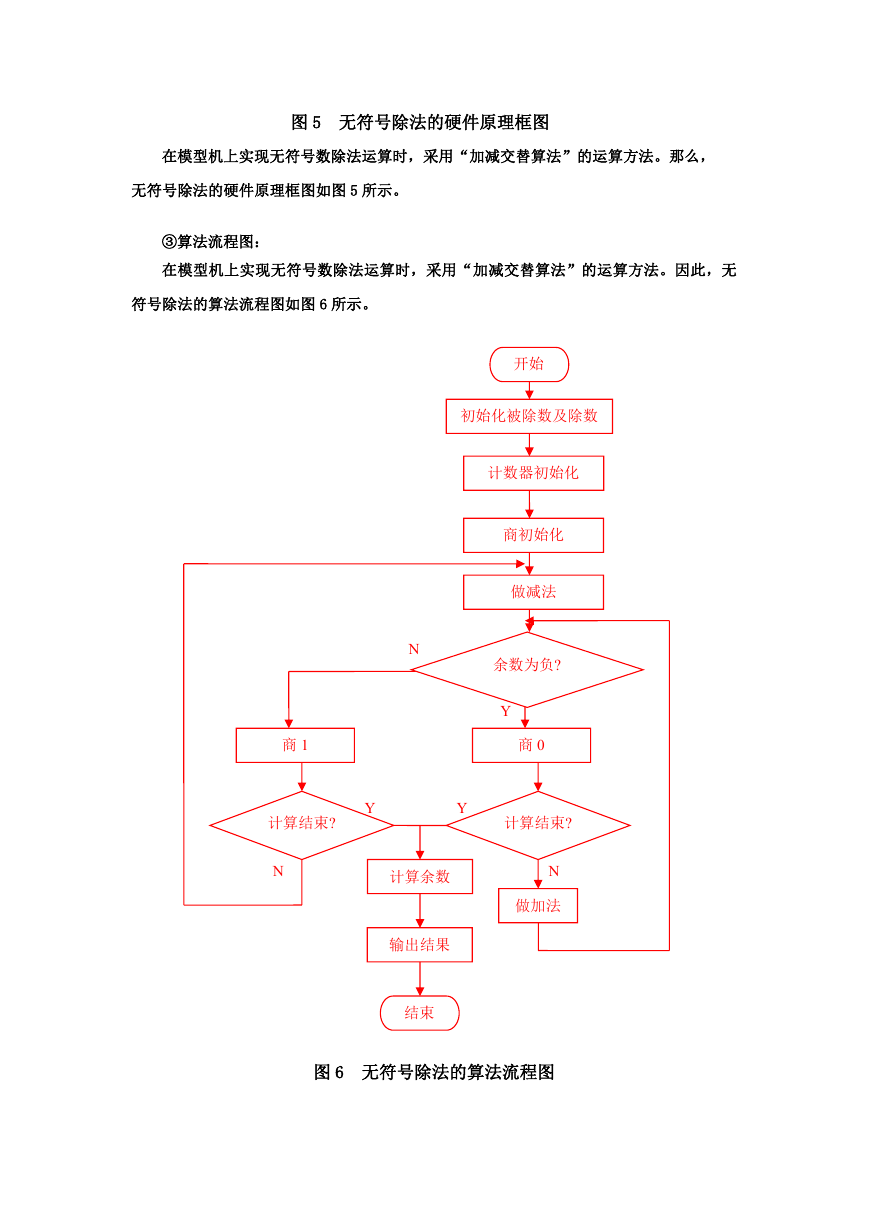

②硬件原理框图:

初始化:除数左移

L

D

R

R2(商)

ALU

标志位 C

A

R0

W

R1

被除数

除数

除

数

右

移

R3(计数器)

�

图 5 无符号除法的硬件原理框图

在模型机上实现无符号数除法运算时,采用“加减交替算法”的运算方法。那么,

无符号除法的硬件原理框图如图 5 所示。

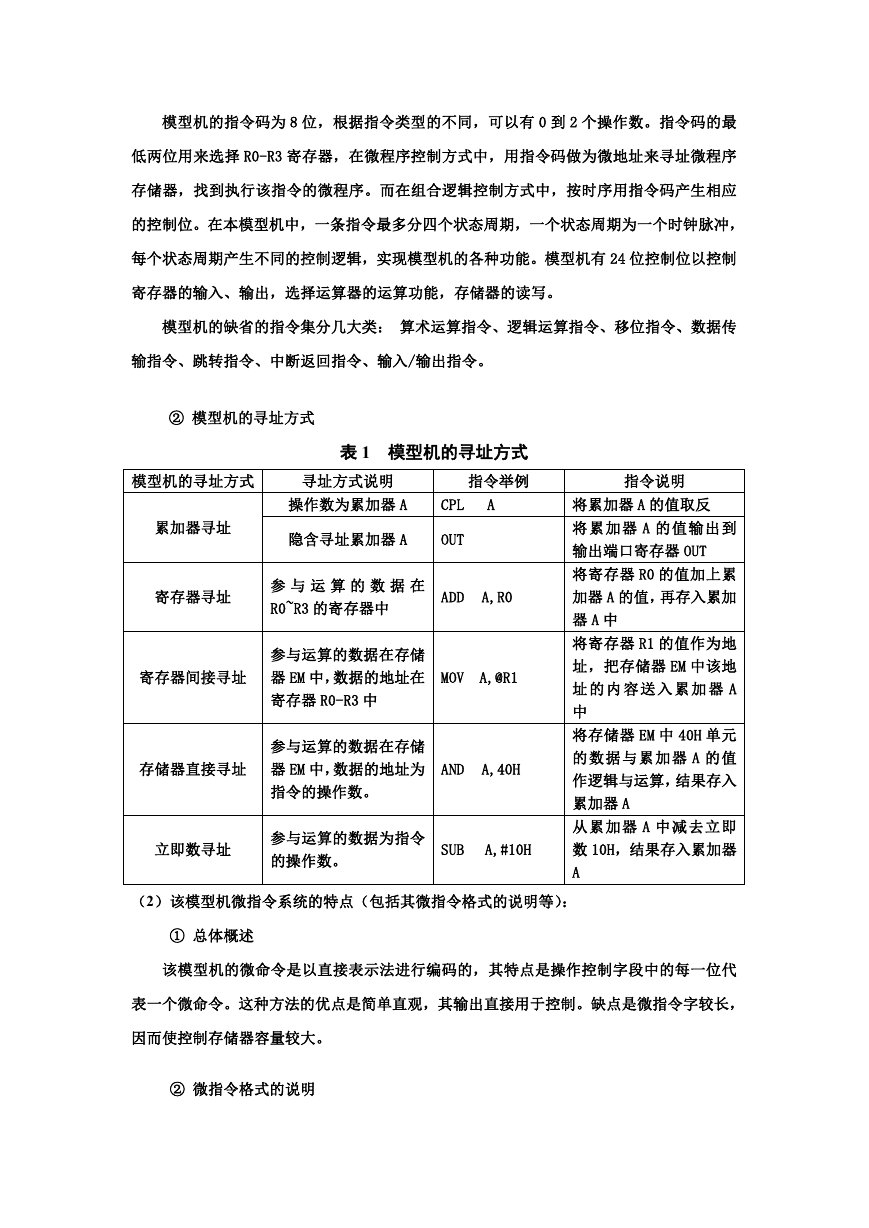

③算法流程图:

在模型机上实现无符号数除法运算时,采用“加减交替算法”的运算方法。因此,无

符号除法的算法流程图如图 6 所示。

开始

初始化被除数及除数

计数器初始化

商初始化

做减法

余数为负?

Y

商 0

计算结束?

N

做加法

N

商 1

计算结束?

Y

Y

N

计算余数

输出结果

结束

图 6 无符号除法的算法流程图

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc