PCIe 规范详细解析

一:从 PCIE 速度说起

2016 年 8 月 29 日 Martrixer Leave a comment

从今天开始,老男孩要开始讲 PCIe 了。对我来说,这是个很大的挑战:首先,

我自己本身,对 PCIe 并没有做到胸有成竹,我的 PCIe 知识也只是停留在理论

阶段,我并没有实际做过任何有关 PCIe 的东西;其次,我要把 PCIe 讲得深入

浅出,让读者轻易接受,我觉得很难,根本原因就是我还没有做到胸有 PCIe;

最后,我的文章都会通过 ssdfans 公众号推出(还没有关注的同学,赶快关

注),很多读者都是 PCIe 高手,班门弄斧,我深感压力。但尽管如此,我还是

决定出发,我自己努力学习,尽我最大能力把我学到的东西分享给大家,也希

望各位 PCIe 大拿们,帮忙斧正文章的错误,我希望不是我一个人,而是和各位

大拿们一起,带领大家攀上 PCIe 的高峰。

我是从事 SSD 工作的,为什么要讲 PCIe,原因很简单,现在很多 SSD 都开始

使用 PCIe 接口。那为什么 SSD 要用 PCIe 接口?因为它快,比 SATA 快。它究

竟有多快?我们今天首先从 PCIe 接口的速度开始我们的 PCIe 之旅。

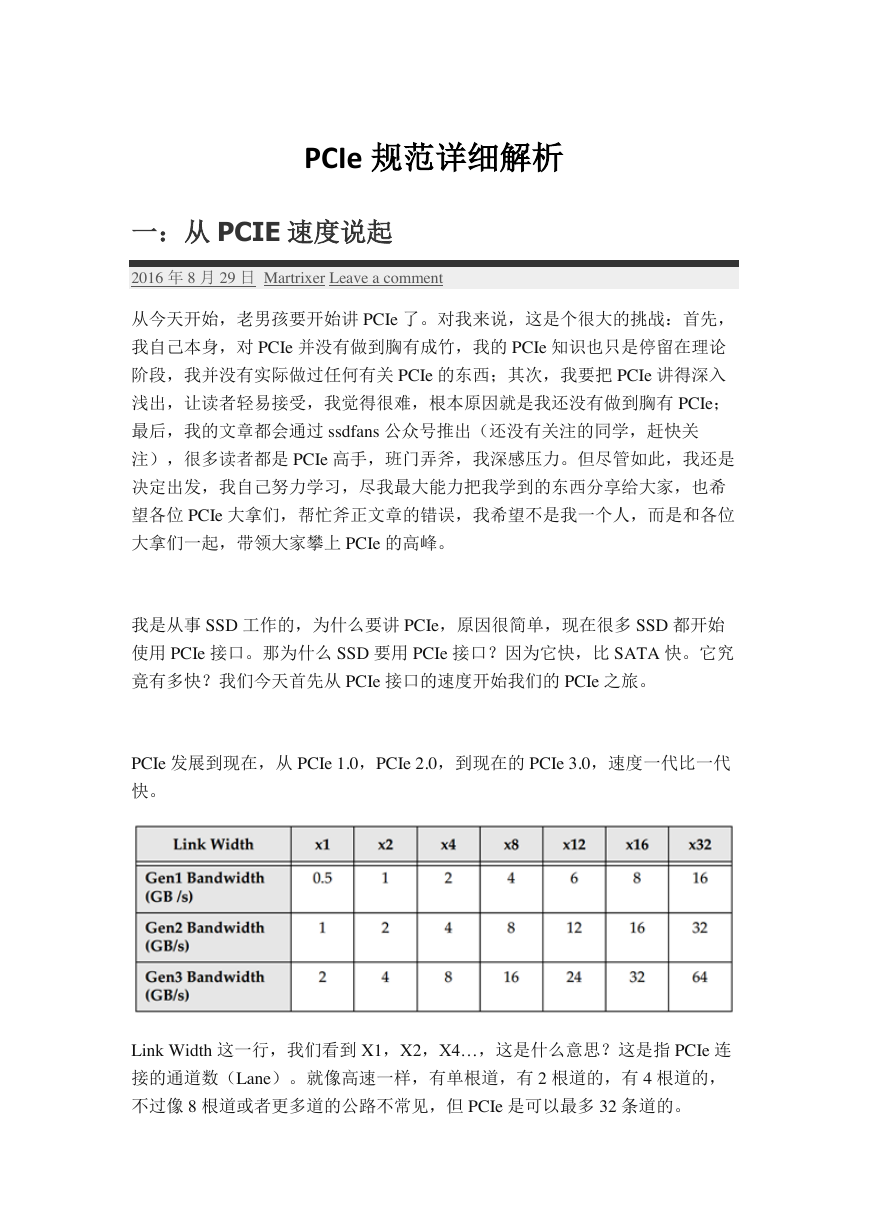

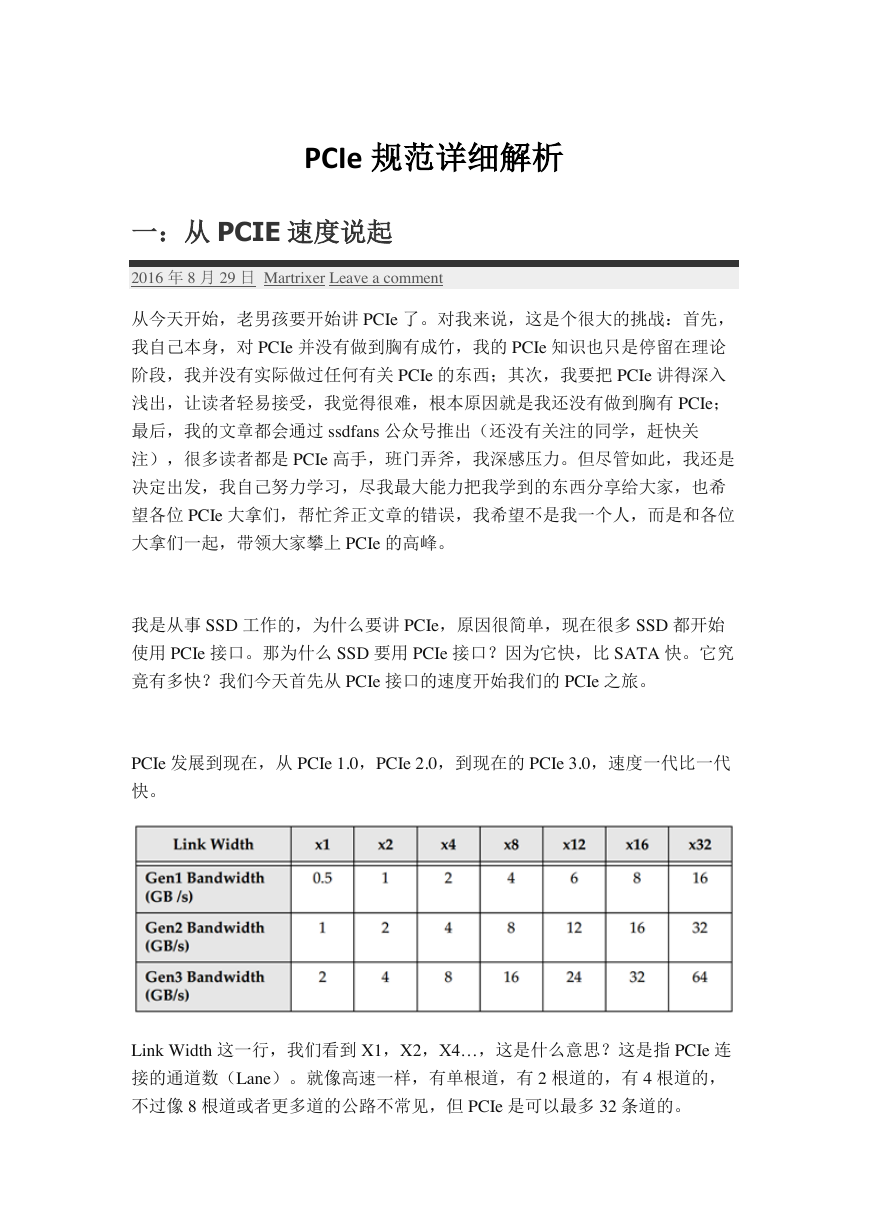

PCIe 发展到现在,从 PCIe 1.0,PCIe 2.0,到现在的 PCIe 3.0,速度一代比一代

快。

Link Width 这一行,我们看到 X1,X2,X4…,这是什么意思?这是指 PCIe 连

接的通道数(Lane)。就像高速一样,有单根道,有 2 根道的,有 4 根道的,

不过像 8 根道或者更多道的公路不常见,但 PCIe 是可以最多 32 条道的。

�

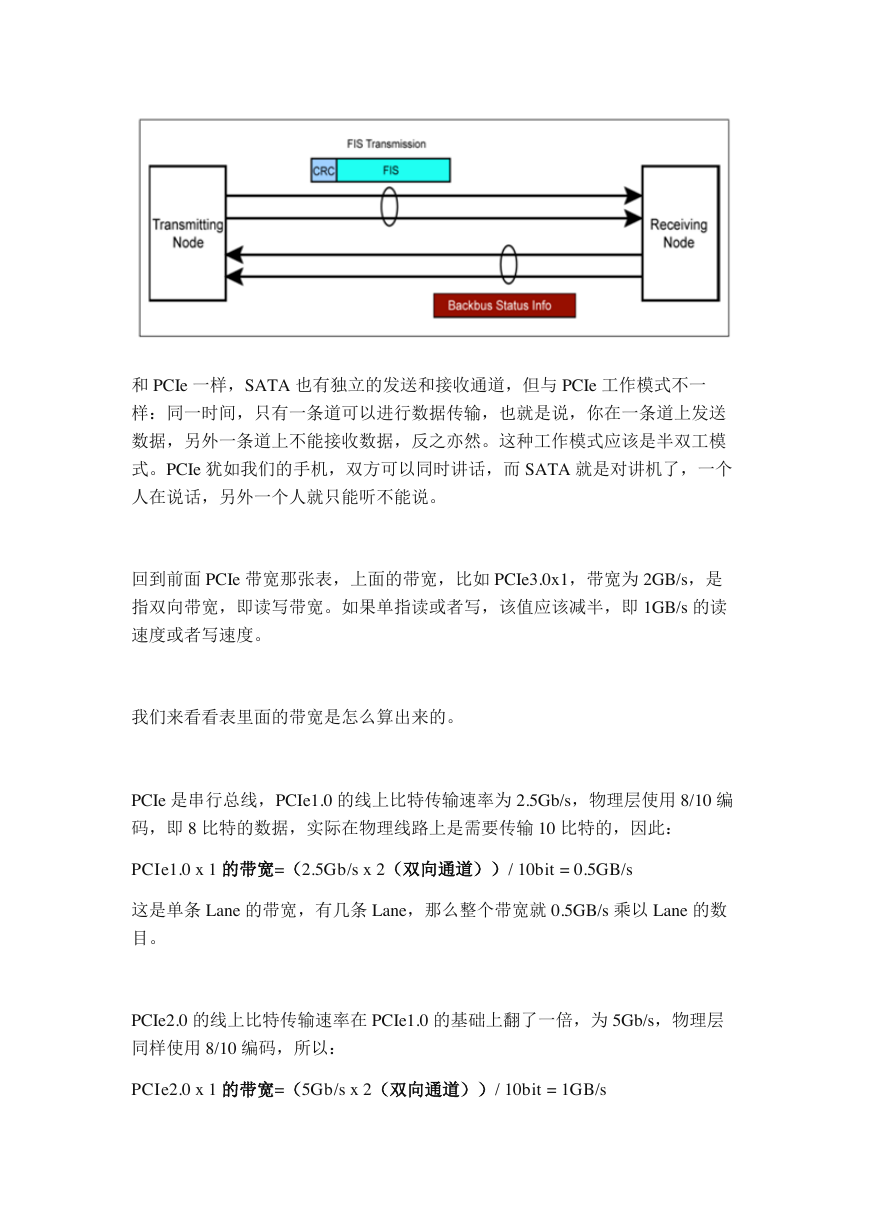

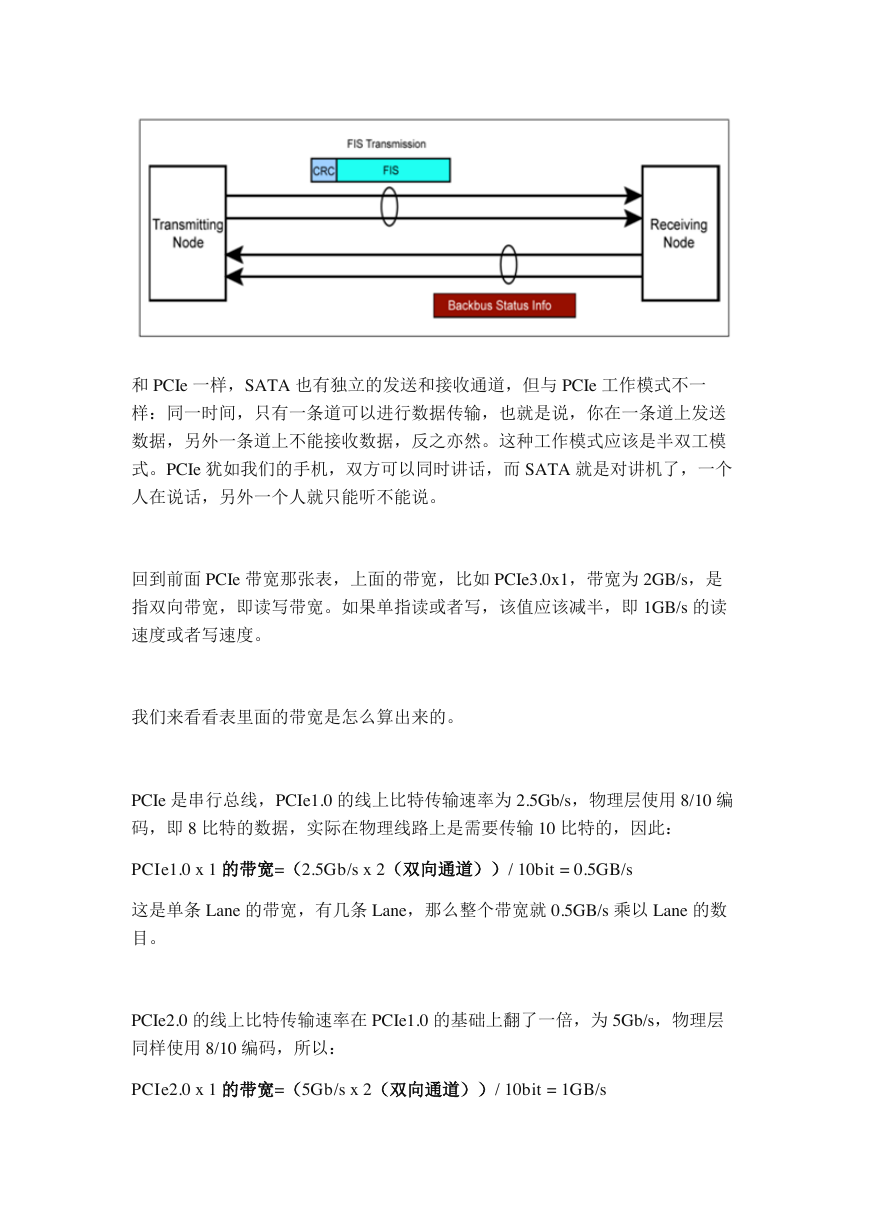

两个设备之间的 PCIe 连接,叫做一个 Link,如下图所示:

从 A 到 B,之间是个双向连接,车可以从 A 驶向 B,同时,车也可以从 B 驶向

A,各行其道。两个 PCIe 设备之间,有专门的发送和接收通道,数据可以同时

往两个方向传输,PCIe spec 称这种工作模式为双单工模式(dual-simplex),可

以理解为全双工模式。

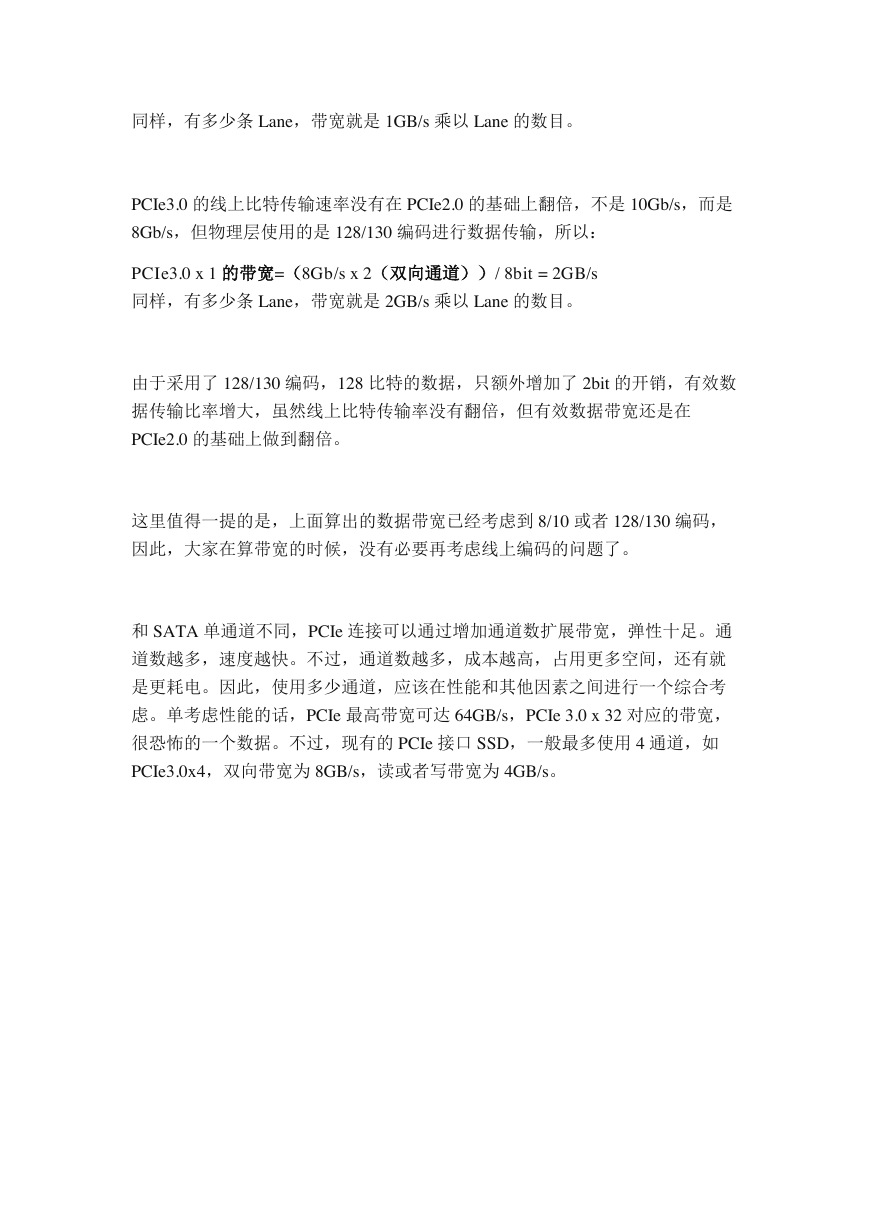

SATA 是什么工作模式呢?

�

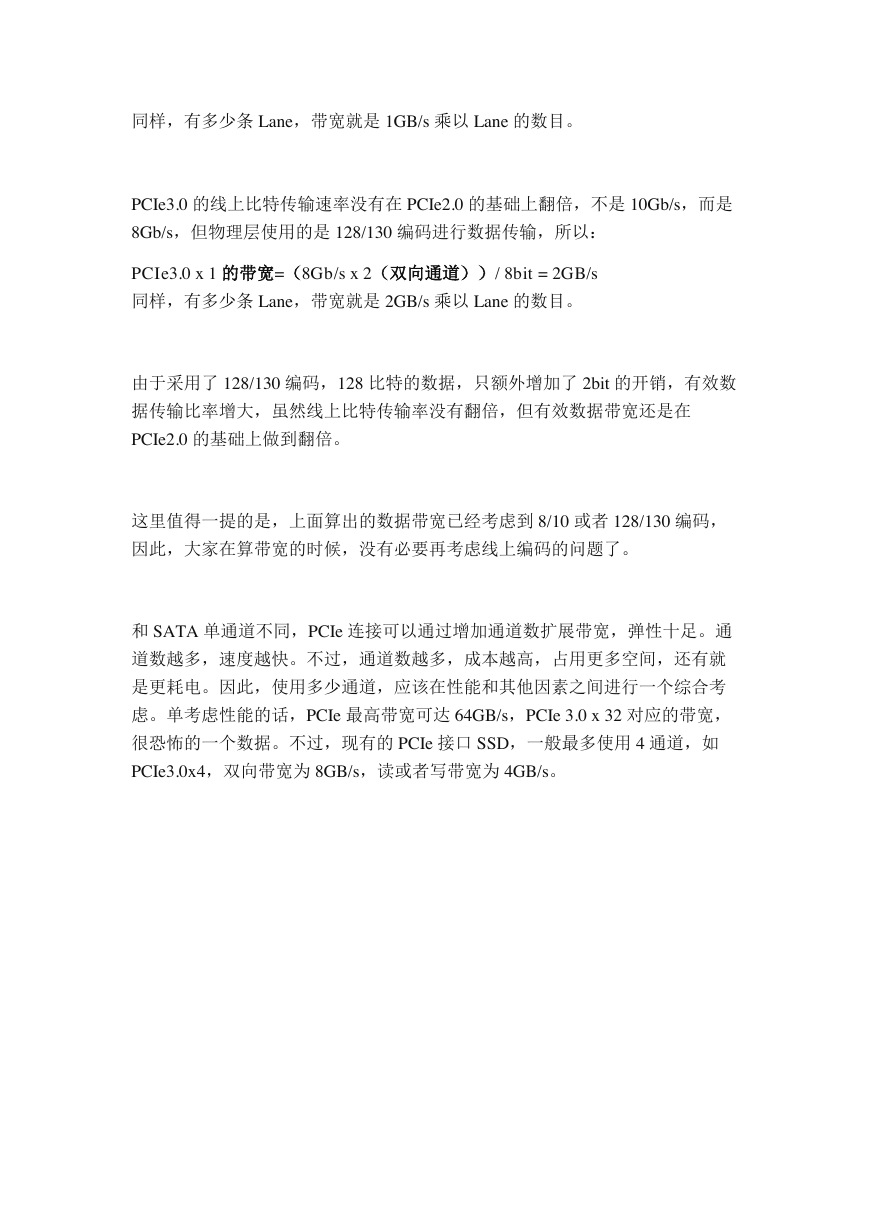

和 PCIe 一样,SATA 也有独立的发送和接收通道,但与 PCIe 工作模式不一

样:同一时间,只有一条道可以进行数据传输,也就是说,你在一条道上发送

数据,另外一条道上不能接收数据,反之亦然。这种工作模式应该是半双工模

式。PCIe 犹如我们的手机,双方可以同时讲话,而 SATA 就是对讲机了,一个

人在说话,另外一个人就只能听不能说。

回到前面 PCIe 带宽那张表,上面的带宽,比如 PCIe3.0x1,带宽为 2GB/s,是

指双向带宽,即读写带宽。如果单指读或者写,该值应该减半,即 1GB/s 的读

速度或者写速度。

我们来看看表里面的带宽是怎么算出来的。

PCIe 是串行总线,PCIe1.0 的线上比特传输速率为 2.5Gb/s,物理层使用 8/10 编

码,即 8 比特的数据,实际在物理线路上是需要传输 10 比特的,因此:

PCIe1.0 x 1 的带宽=(2.5Gb/s x 2(双向通道))/ 10bit = 0.5GB/s

这是单条 Lane 的带宽,有几条 Lane,那么整个带宽就 0.5GB/s 乘以 Lane 的数

目。

PCIe2.0 的线上比特传输速率在 PCIe1.0 的基础上翻了一倍,为 5Gb/s,物理层

同样使用 8/10 编码,所以:

PCIe2.0 x 1 的带宽=(5Gb/s x 2(双向通道))/ 10bit = 1GB/s

�

同样,有多少条 Lane,带宽就是 1GB/s 乘以 Lane 的数目。

PCIe3.0 的线上比特传输速率没有在 PCIe2.0 的基础上翻倍,不是 10Gb/s,而是

8Gb/s,但物理层使用的是 128/130 编码进行数据传输,所以:

PCIe3.0 x 1 的带宽=(8Gb/s x 2(双向通道))/ 8bit = 2GB/s

同样,有多少条 Lane,带宽就是 2GB/s 乘以 Lane 的数目。

由于采用了 128/130 编码,128 比特的数据,只额外增加了 2bit 的开销,有效数

据传输比率增大,虽然线上比特传输率没有翻倍,但有效数据带宽还是在

PCIe2.0 的基础上做到翻倍。

这里值得一提的是,上面算出的数据带宽已经考虑到 8/10 或者 128/130 编码,

因此,大家在算带宽的时候,没有必要再考虑线上编码的问题了。

和 SATA 单通道不同,PCIe 连接可以通过增加通道数扩展带宽,弹性十足。通

道数越多,速度越快。不过,通道数越多,成本越高,占用更多空间,还有就

是更耗电。因此,使用多少通道,应该在性能和其他因素之间进行一个综合考

虑。单考虑性能的话,PCIe 最高带宽可达 64GB/s,PCIe 3.0 x 32 对应的带宽,

很恐怖的一个数据。不过,现有的 PCIe 接口 SSD,一般最多使用 4 通道,如

PCIe3.0x4,双向带宽为 8GB/s,读或者写带宽为 4GB/s。

�

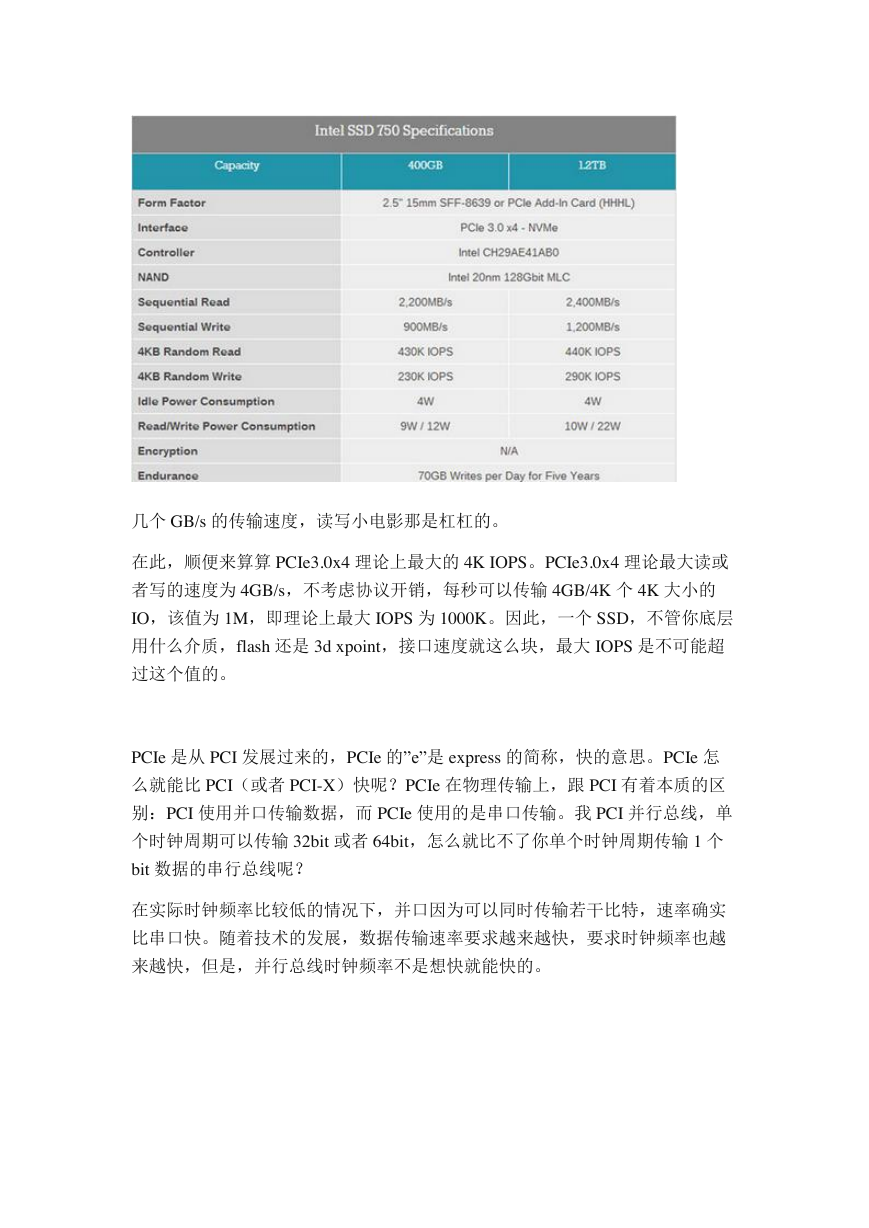

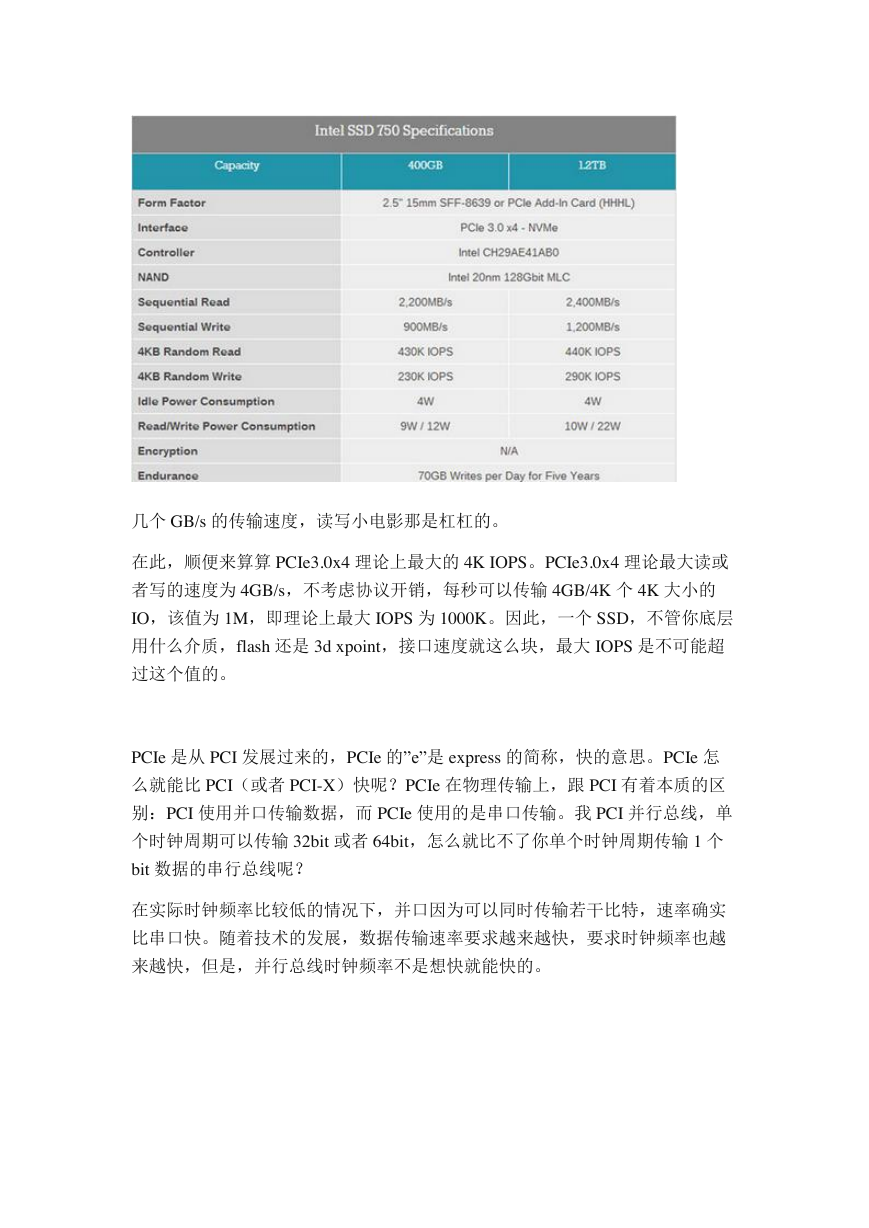

几个 GB/s 的传输速度,读写小电影那是杠杠的。

在此,顺便来算算 PCIe3.0x4 理论上最大的 4K IOPS。PCIe3.0x4 理论最大读或

者写的速度为 4GB/s,不考虑协议开销,每秒可以传输 4GB/4K 个 4K 大小的

IO,该值为 1M,即理论上最大 IOPS 为 1000K。因此,一个 SSD,不管你底层

用什么介质,flash 还是 3d xpoint,接口速度就这么块,最大 IOPS 是不可能超

过这个值的。

PCIe 是从 PCI 发展过来的,PCIe 的”e”是 express 的简称,快的意思。PCIe 怎

么就能比 PCI(或者 PCI-X)快呢?PCIe 在物理传输上,跟 PCI 有着本质的区

别:PCI 使用并口传输数据,而 PCIe 使用的是串口传输。我 PCI 并行总线,单

个时钟周期可以传输 32bit 或者 64bit,怎么就比不了你单个时钟周期传输 1 个

bit 数据的串行总线呢?

在实际时钟频率比较低的情况下,并口因为可以同时传输若干比特,速率确实

比串口快。随着技术的发展,数据传输速率要求越来越快,要求时钟频率也越

来越快,但是,并行总线时钟频率不是想快就能快的。

�

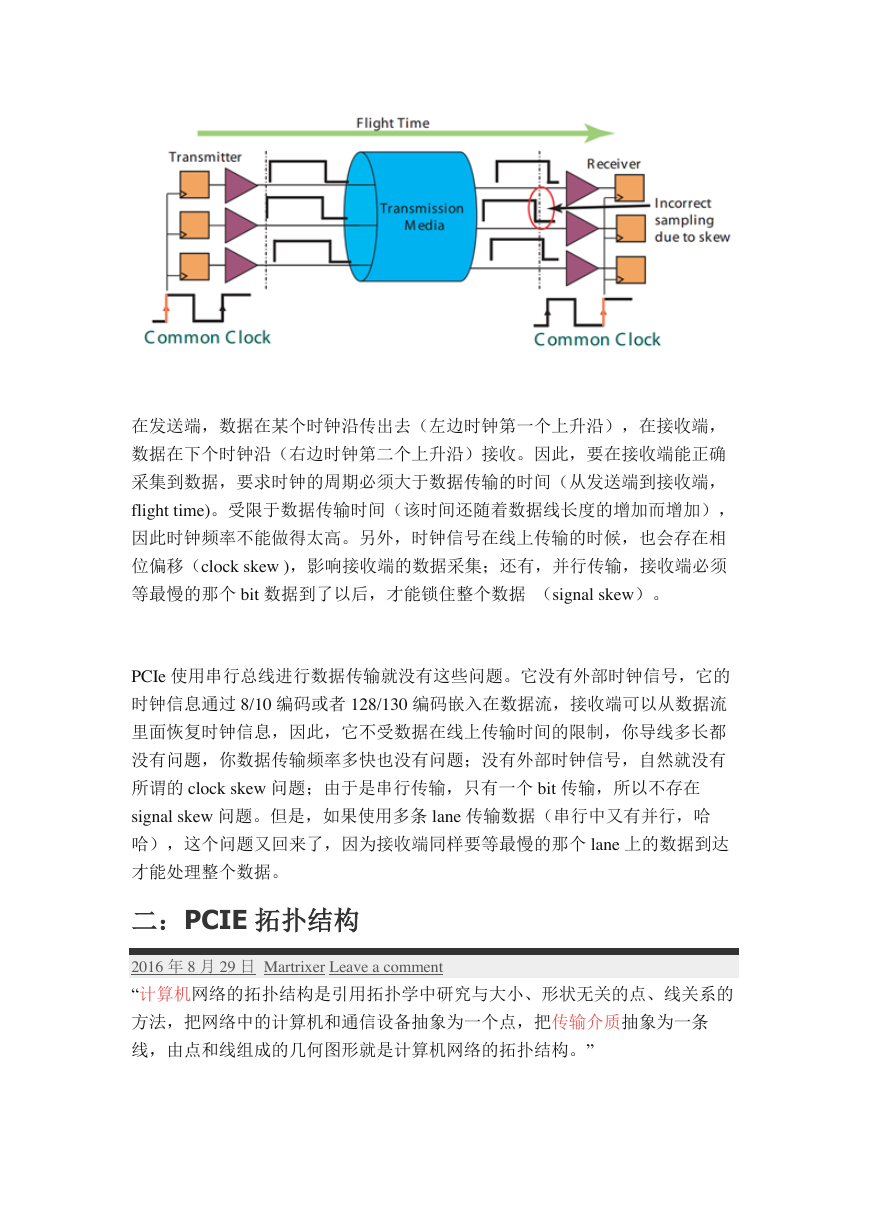

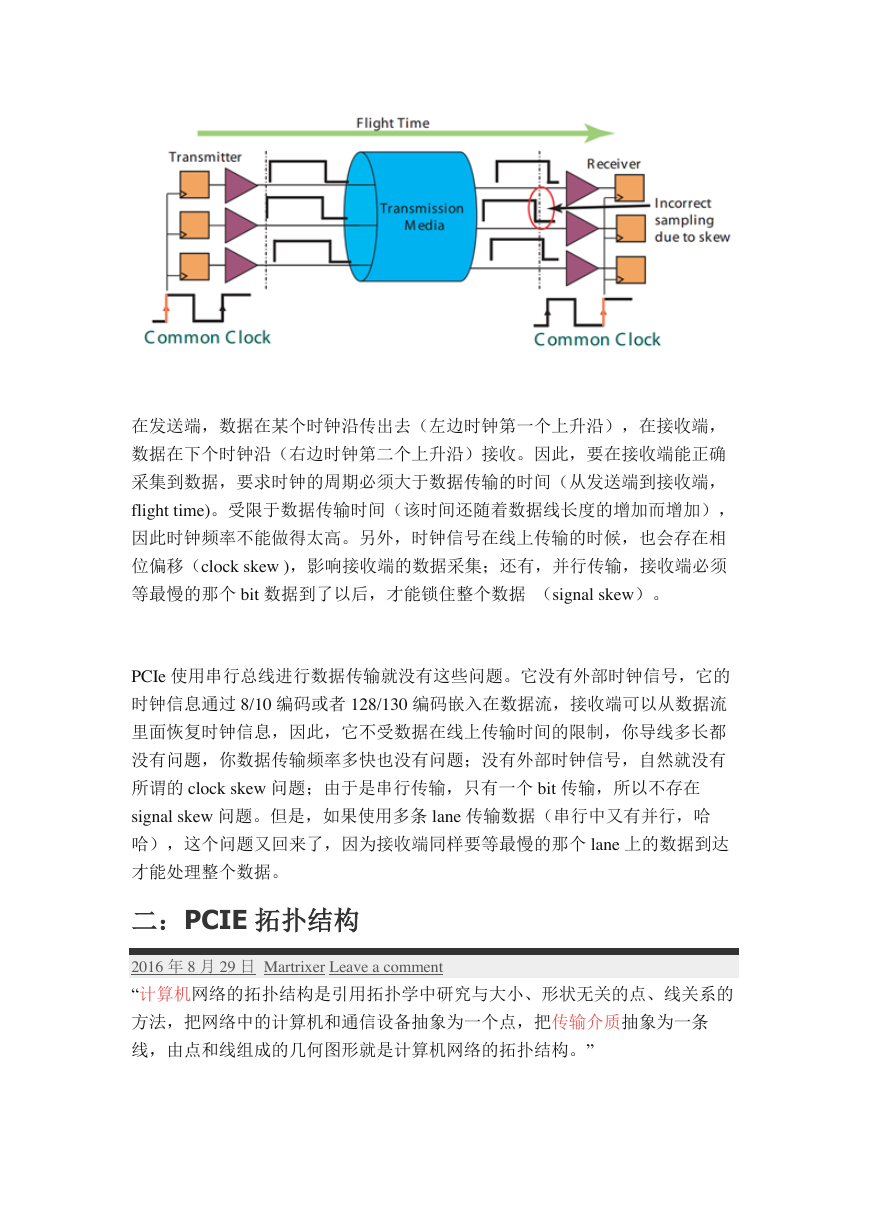

在发送端,数据在某个时钟沿传出去(左边时钟第一个上升沿),在接收端,

数据在下个时钟沿(右边时钟第二个上升沿)接收。因此,要在接收端能正确

采集到数据,要求时钟的周期必须大于数据传输的时间(从发送端到接收端,

flight time)。受限于数据传输时间(该时间还随着数据线长度的增加而增加),

因此时钟频率不能做得太高。另外,时钟信号在线上传输的时候,也会存在相

位偏移(clock skew ),影响接收端的数据采集;还有,并行传输,接收端必须

等最慢的那个 bit 数据到了以后,才能锁住整个数据 (signal skew)。

PCIe 使用串行总线进行数据传输就没有这些问题。它没有外部时钟信号,它的

时钟信息通过 8/10 编码或者 128/130 编码嵌入在数据流,接收端可以从数据流

里面恢复时钟信息,因此,它不受数据在线上传输时间的限制,你导线多长都

没有问题,你数据传输频率多快也没有问题;没有外部时钟信号,自然就没有

所谓的 clock skew 问题;由于是串行传输,只有一个 bit 传输,所以不存在

signal skew 问题。但是,如果使用多条 lane 传输数据(串行中又有并行,哈

哈),这个问题又回来了,因为接收端同样要等最慢的那个 lane 上的数据到达

才能处理整个数据。

二:PCIE 拓扑结构

2016 年 8 月 29 日 Martrixer Leave a comment

“计算机网络的拓扑结构是引用拓扑学中研究与大小、形状无关的点、线关系的

方法,把网络中的计算机和通信设备抽象为一个点,把传输介质抽象为一条

线,由点和线组成的几何图形就是计算机网络的拓扑结构。”

�

计算机网络的最主要的拓扑结构有总线型拓扑、环形拓扑、树形拓扑、星形拓

扑、混合型拓扑以及网状拓扑。

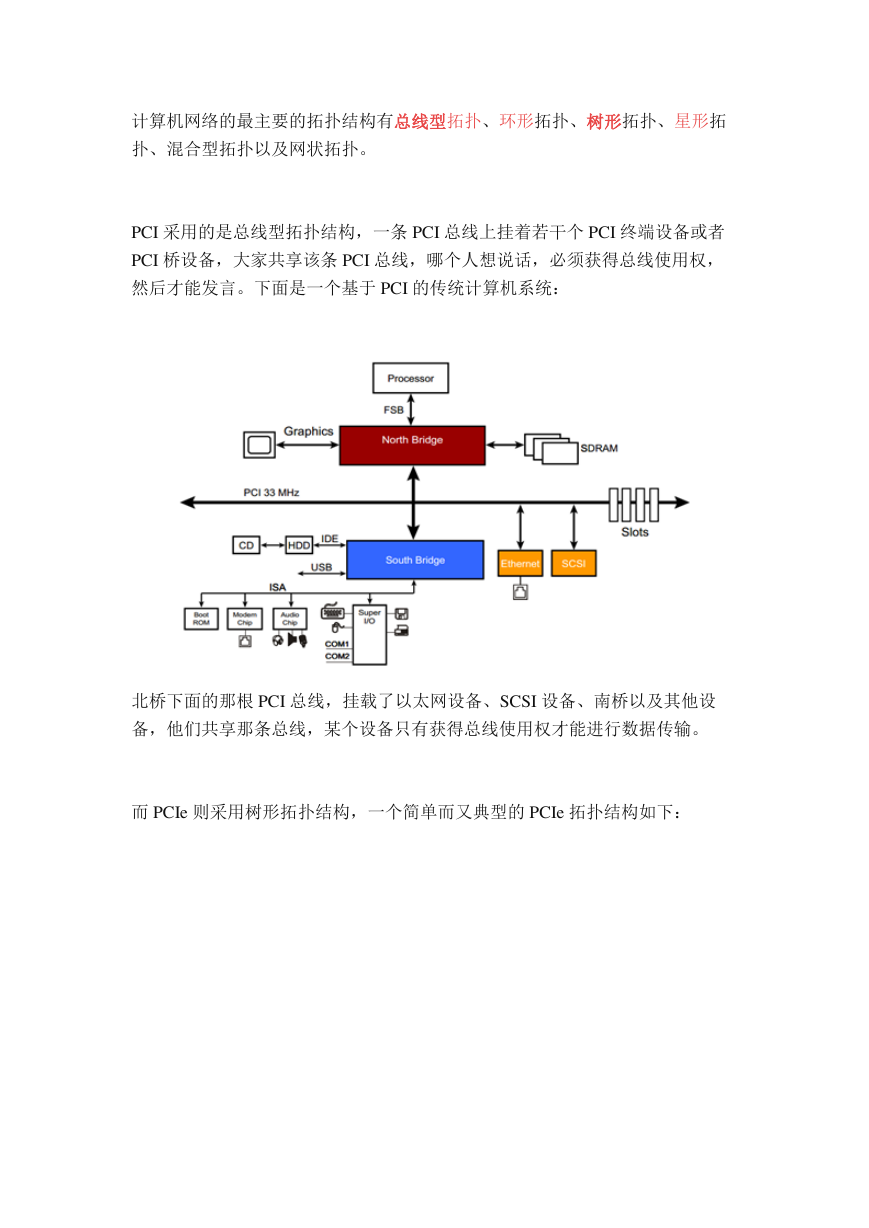

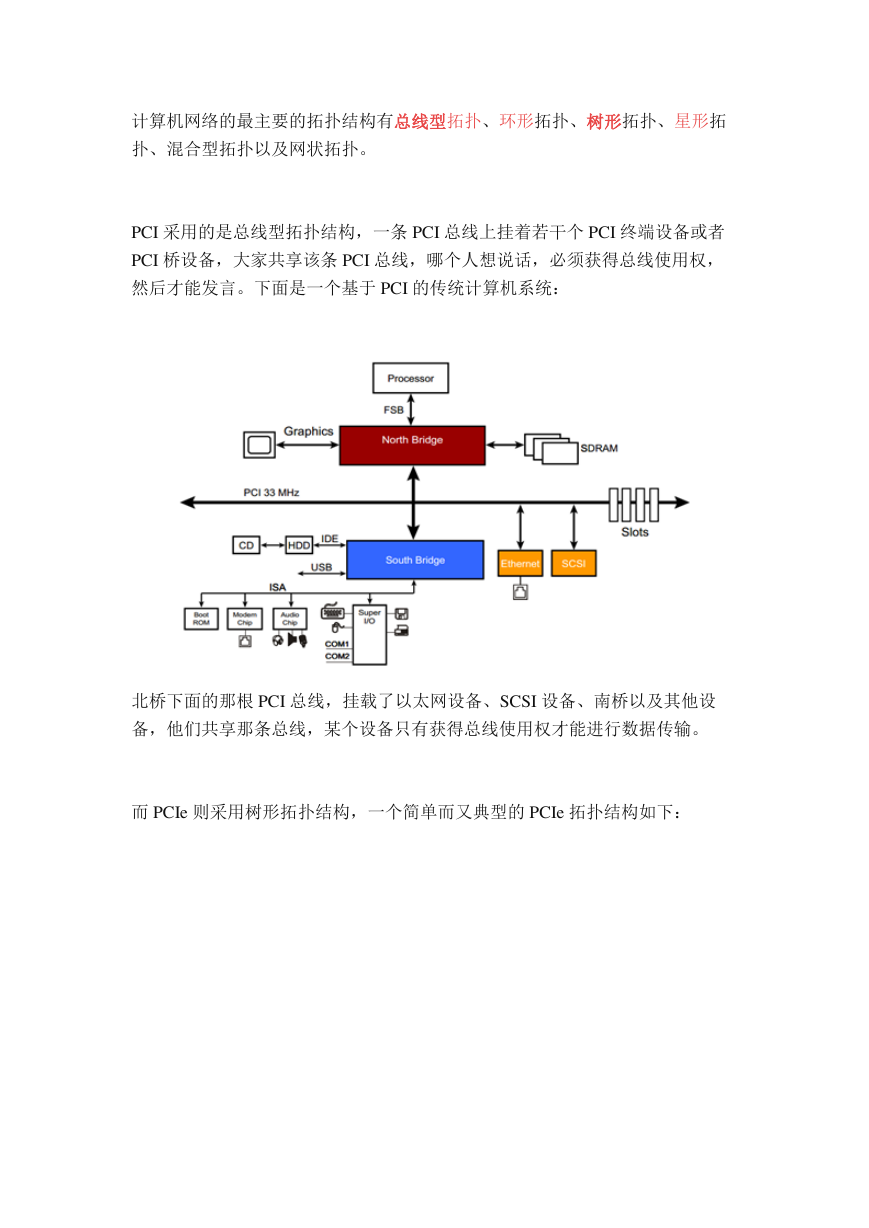

PCI 采用的是总线型拓扑结构,一条 PCI 总线上挂着若干个 PCI 终端设备或者

PCI 桥设备,大家共享该条 PCI 总线,哪个人想说话,必须获得总线使用权,

然后才能发言。下面是一个基于 PCI 的传统计算机系统:

北桥下面的那根 PCI 总线,挂载了以太网设备、SCSI 设备、南桥以及其他设

备,他们共享那条总线,某个设备只有获得总线使用权才能进行数据传输。

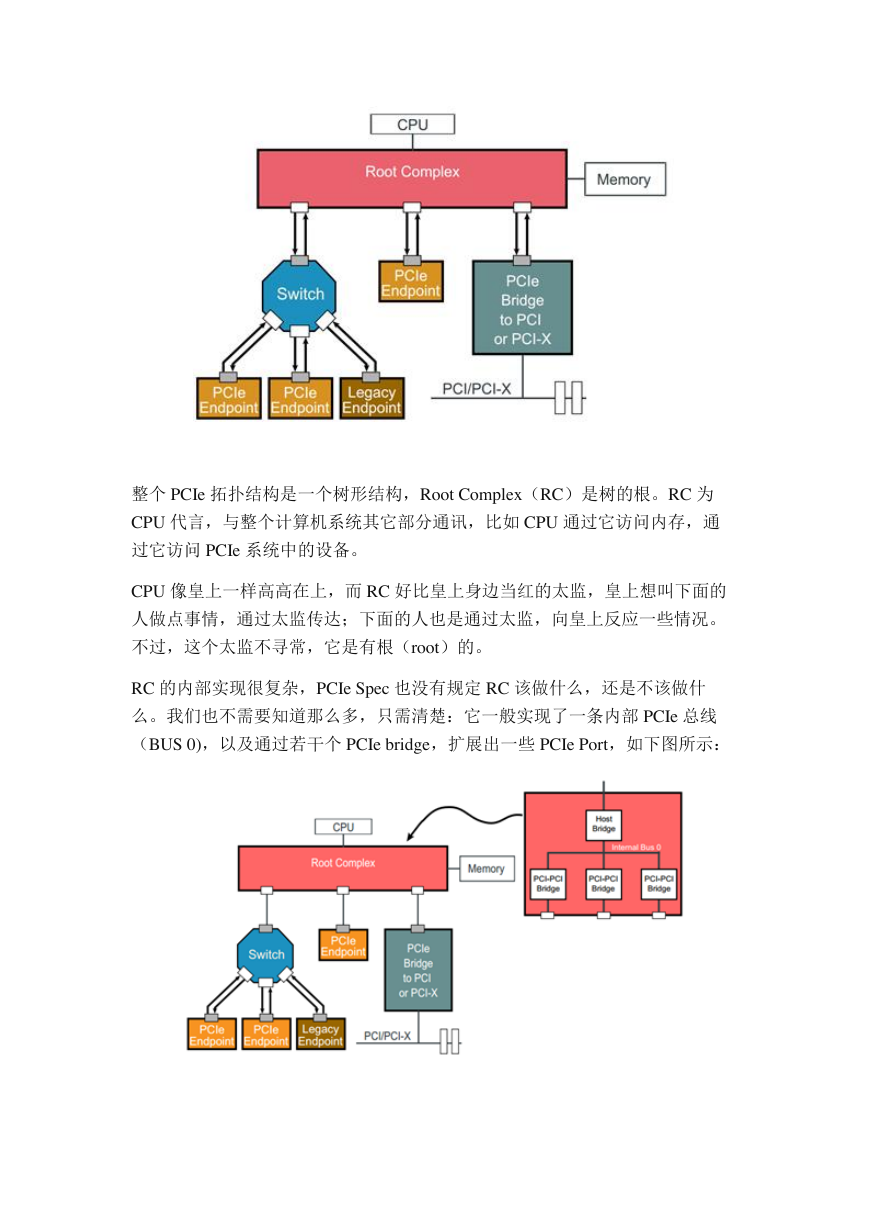

而 PCIe 则采用树形拓扑结构,一个简单而又典型的 PCIe 拓扑结构如下:

�

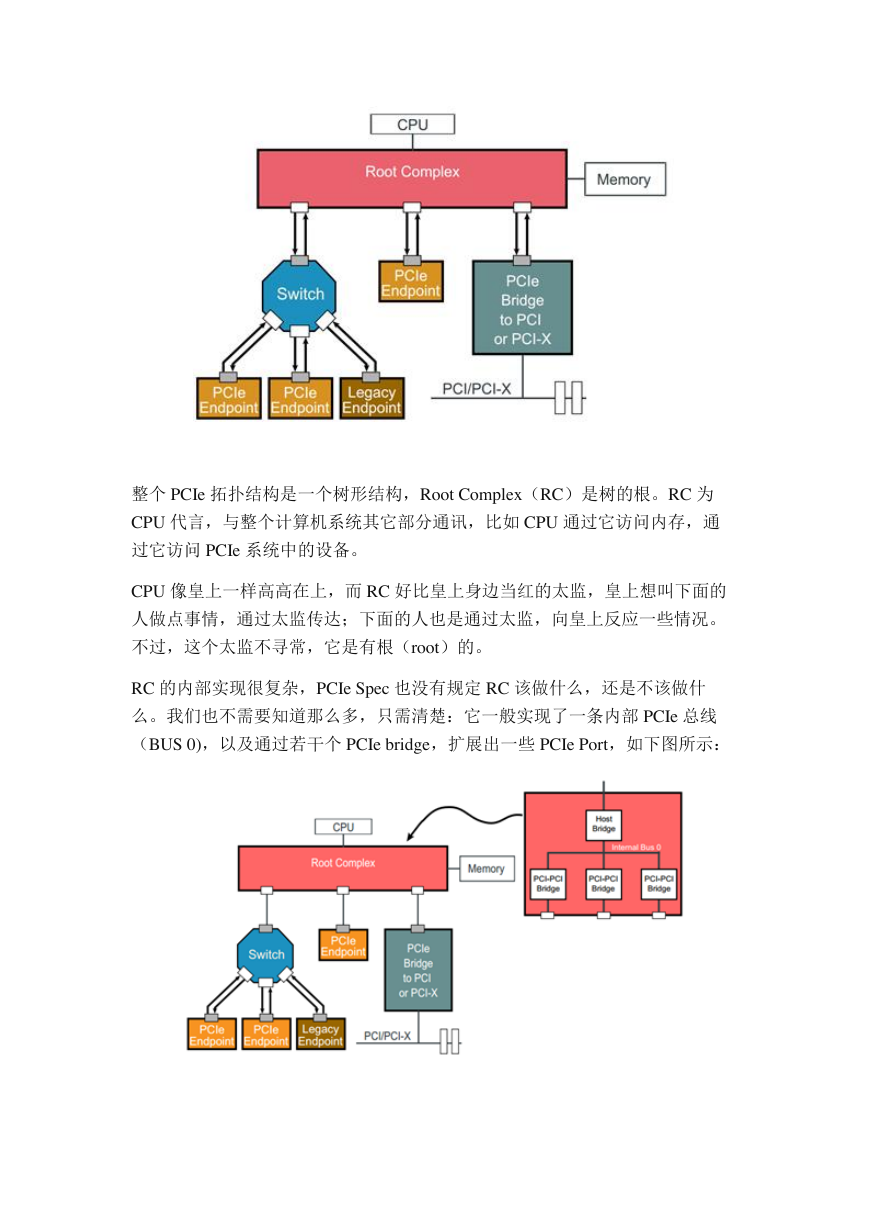

整个 PCIe 拓扑结构是一个树形结构,Root Complex(RC)是树的根。RC 为

CPU 代言,与整个计算机系统其它部分通讯,比如 CPU 通过它访问内存,通

过它访问 PCIe 系统中的设备。

CPU 像皇上一样高高在上,而 RC 好比皇上身边当红的太监,皇上想叫下面的

人做点事情,通过太监传达;下面的人也是通过太监,向皇上反应一些情况。

不过,这个太监不寻常,它是有根(root)的。

RC 的内部实现很复杂,PCIe Spec 也没有规定 RC 该做什么,还是不该做什

么。我们也不需要知道那么多,只需清楚:它一般实现了一条内部 PCIe 总线

(BUS 0),以及通过若干个 PCIe bridge,扩展出一些 PCIe Port,如下图所示:

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc