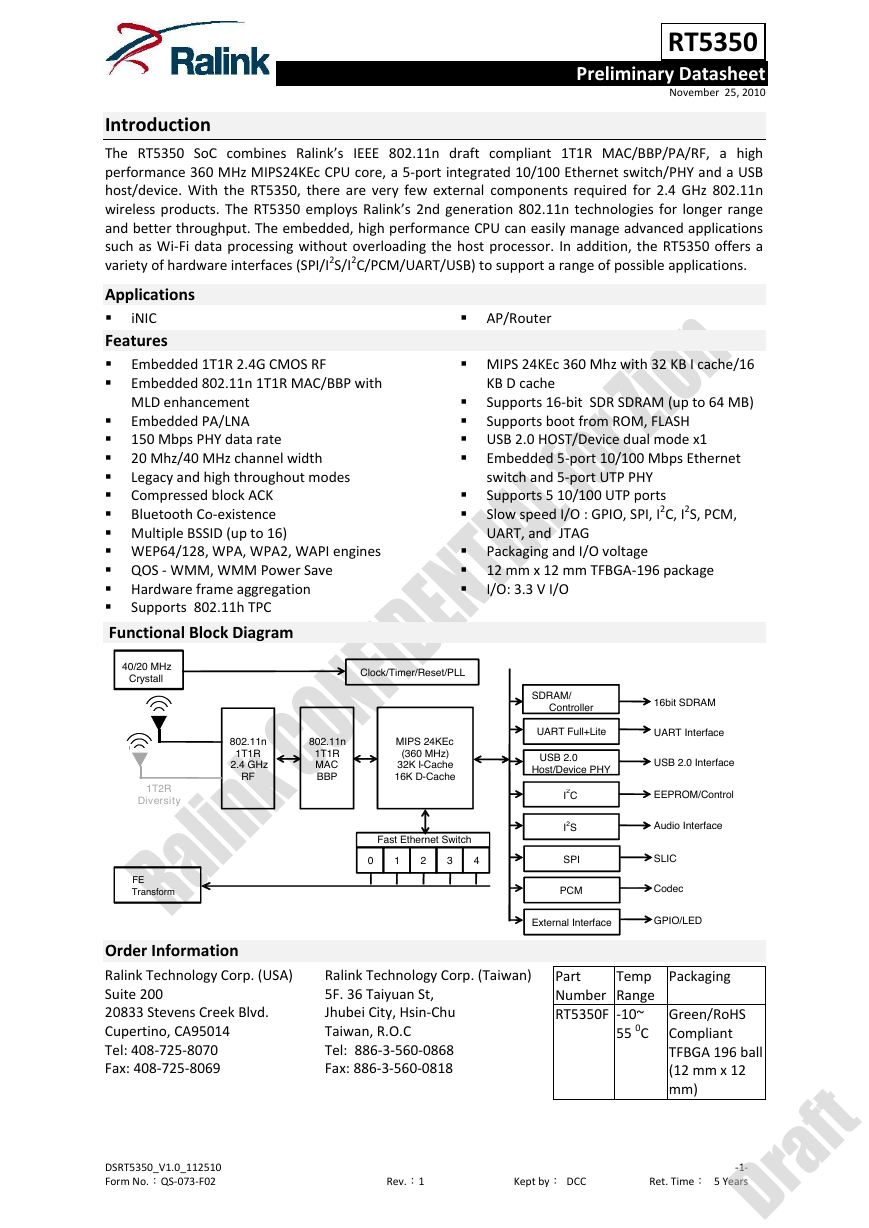

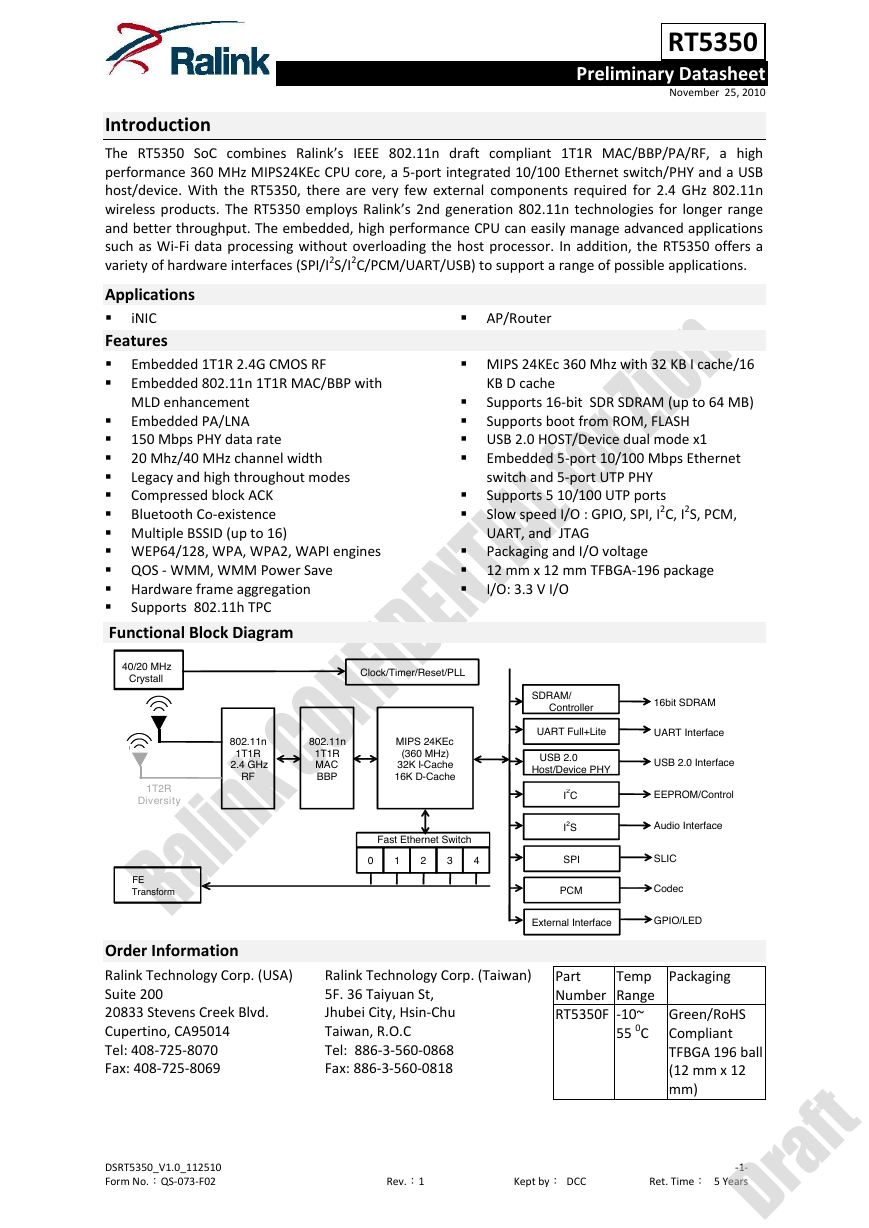

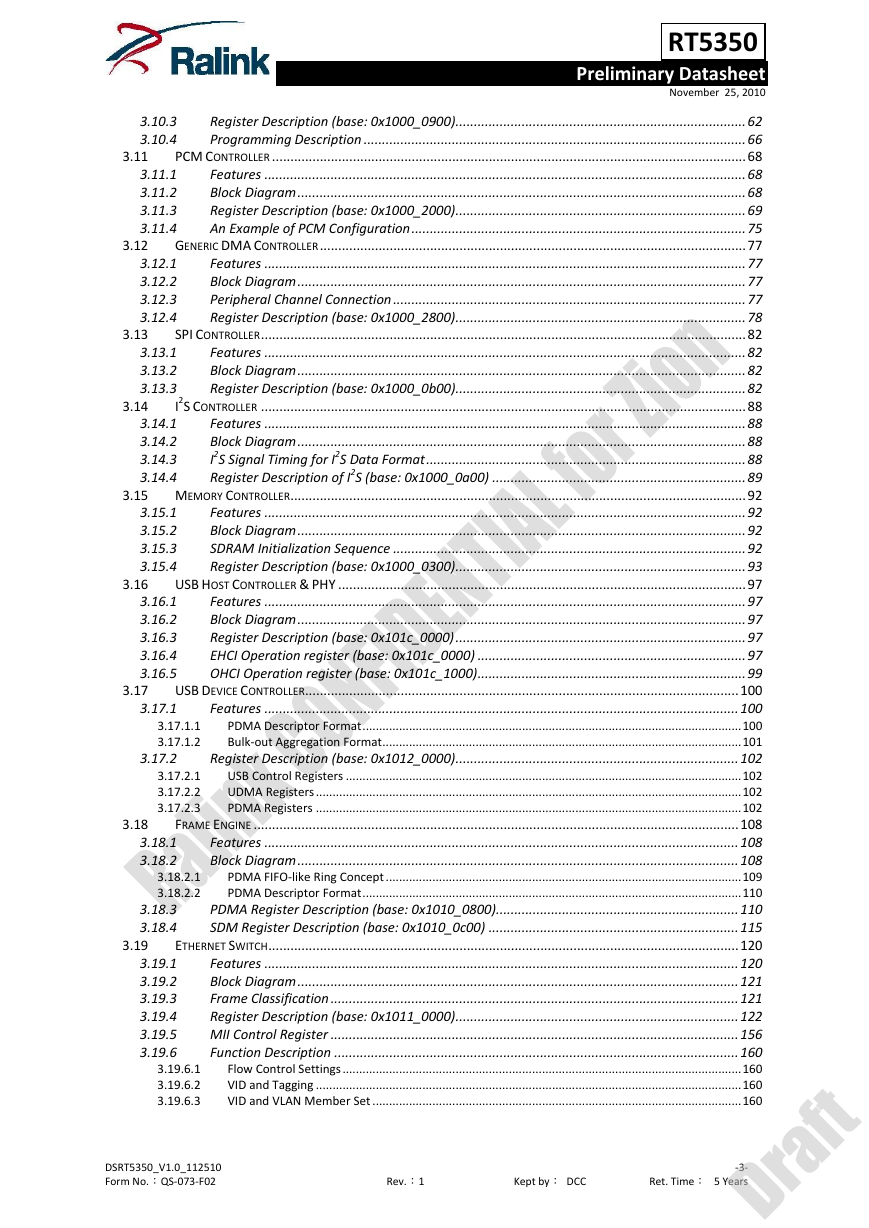

Introduction

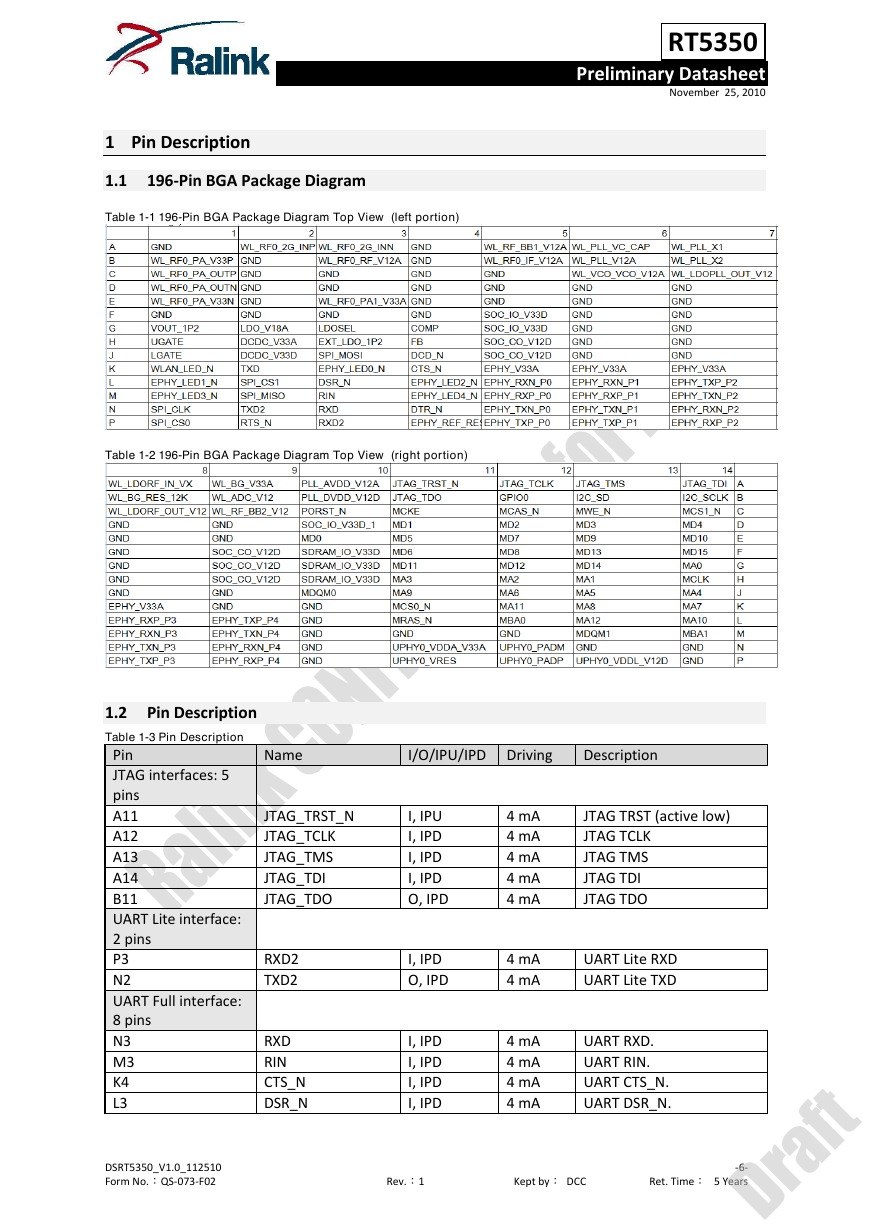

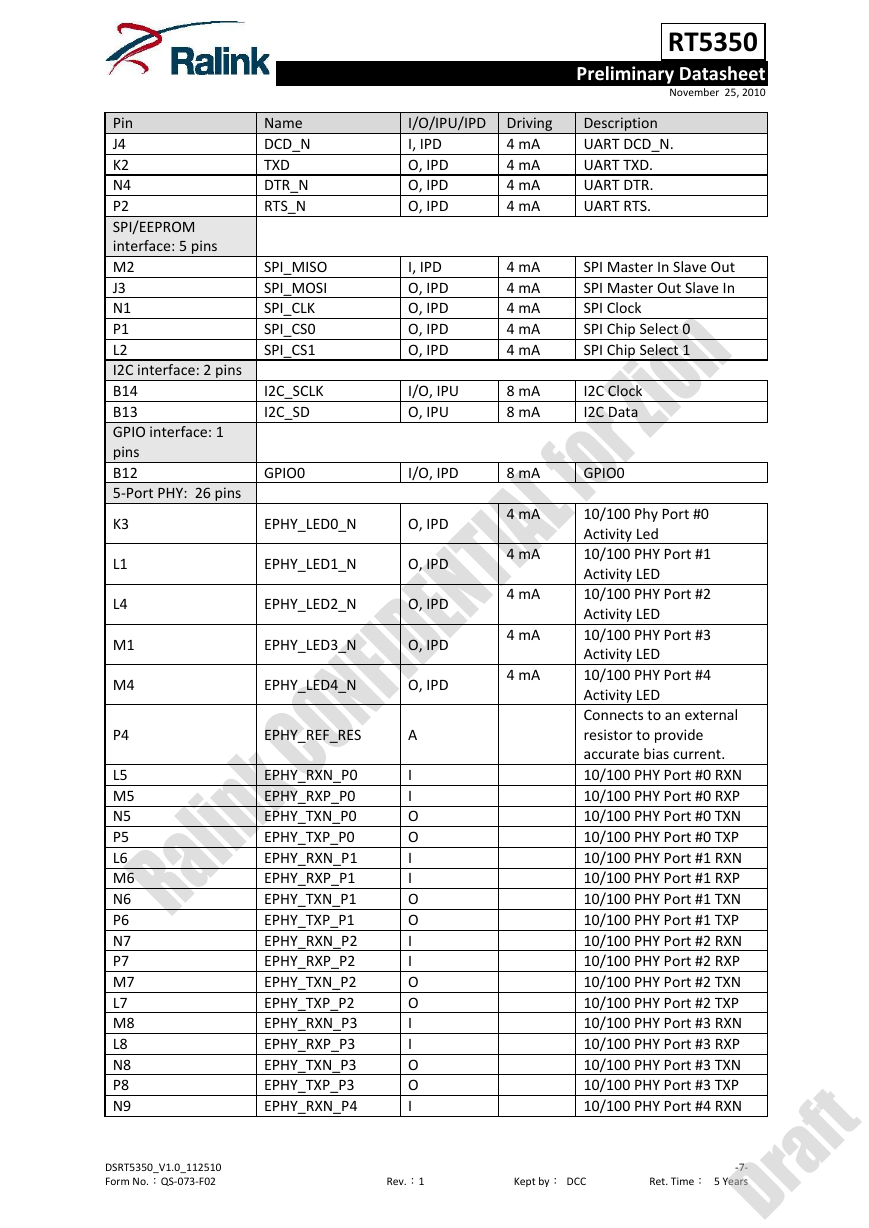

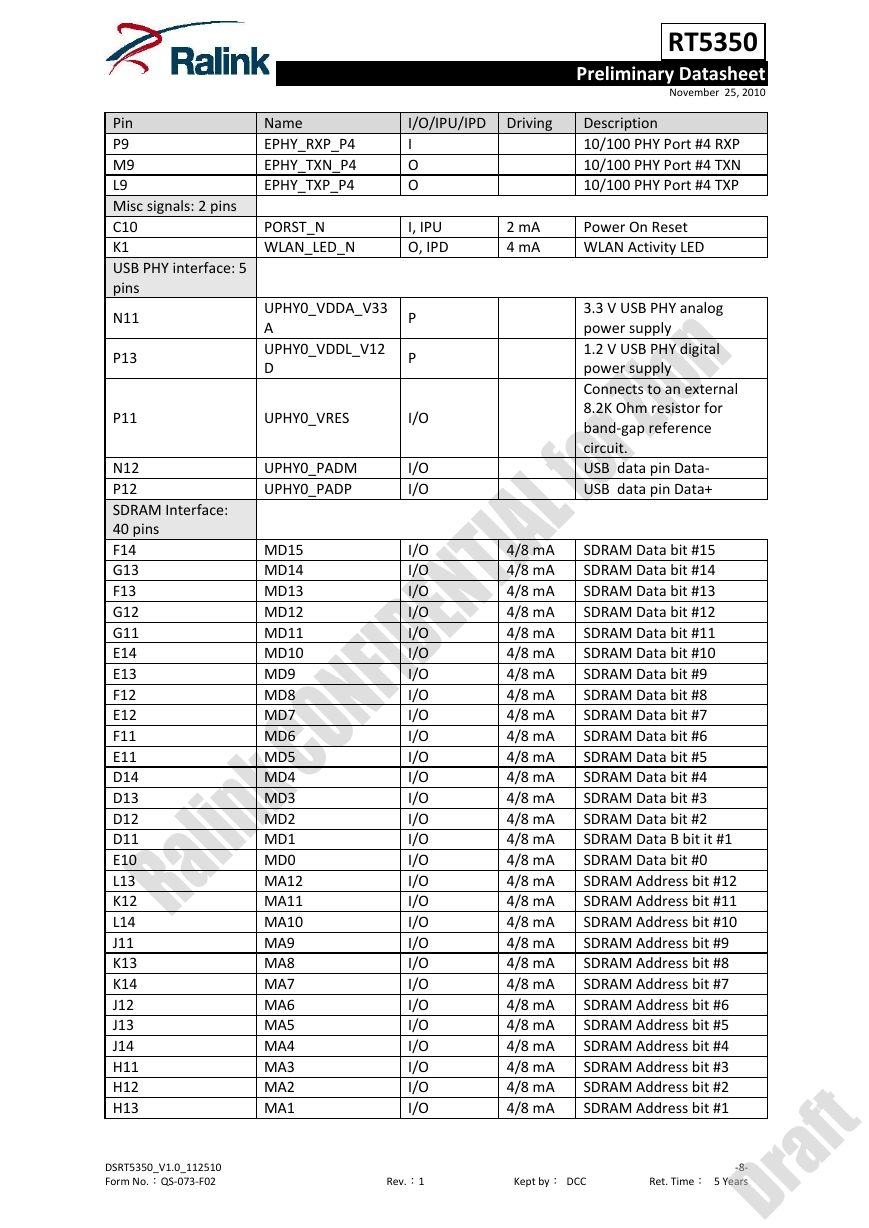

1 Pin Description

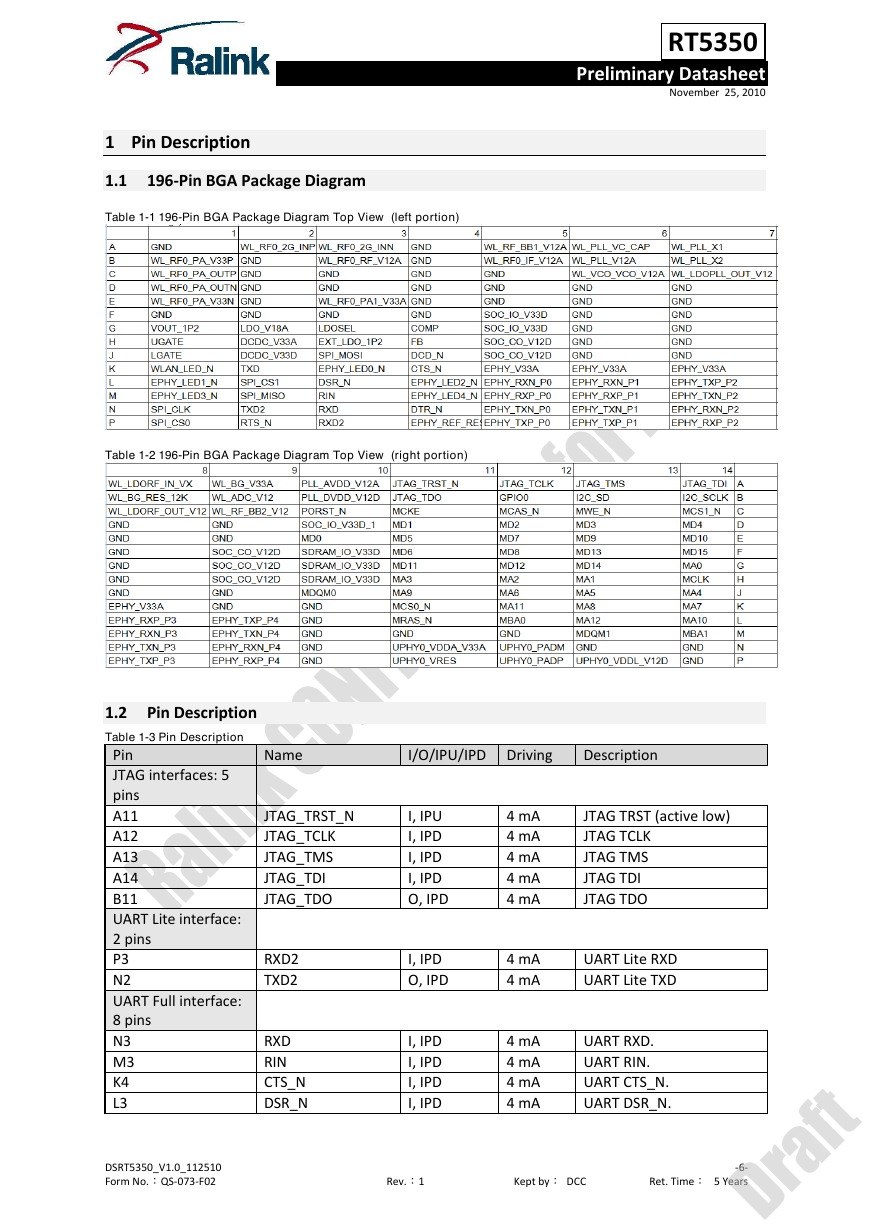

1.1 196-Pin BGA Package Diagram

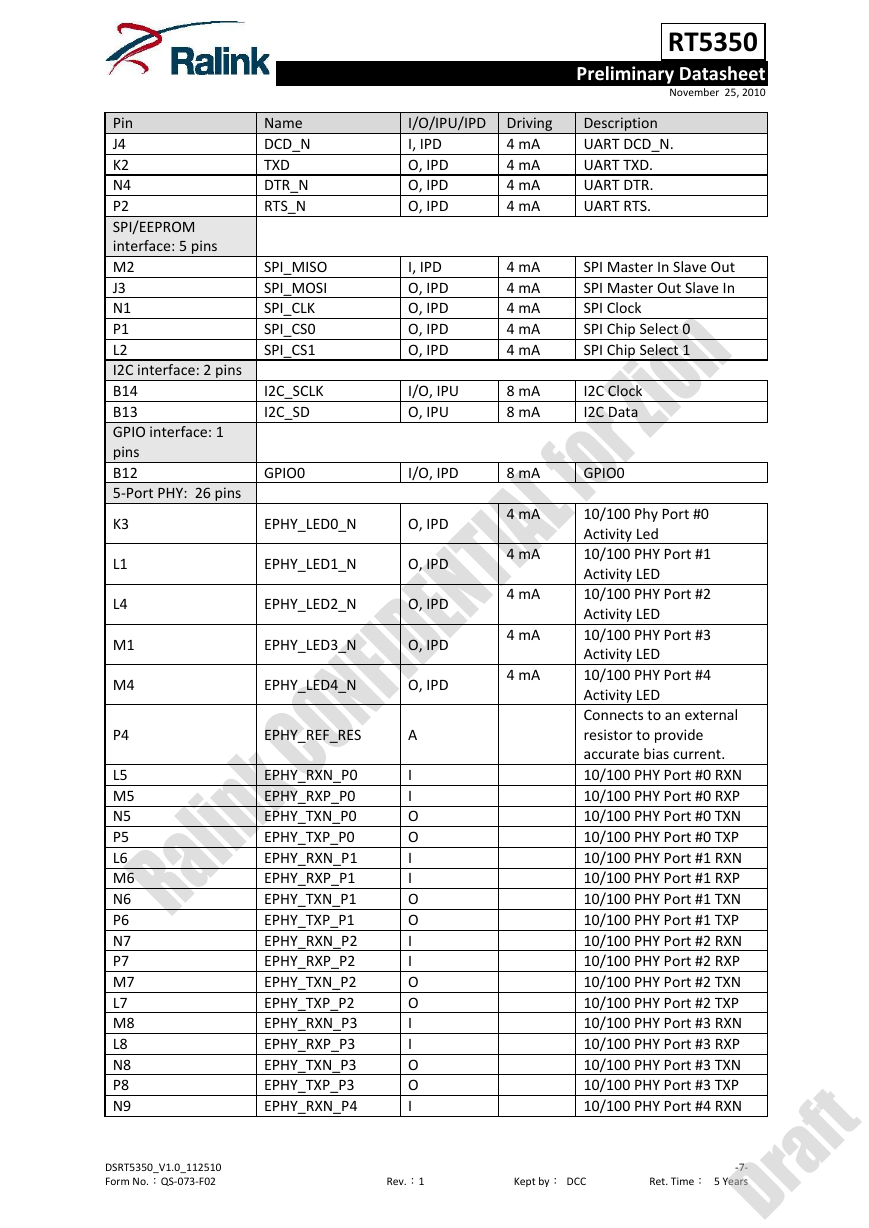

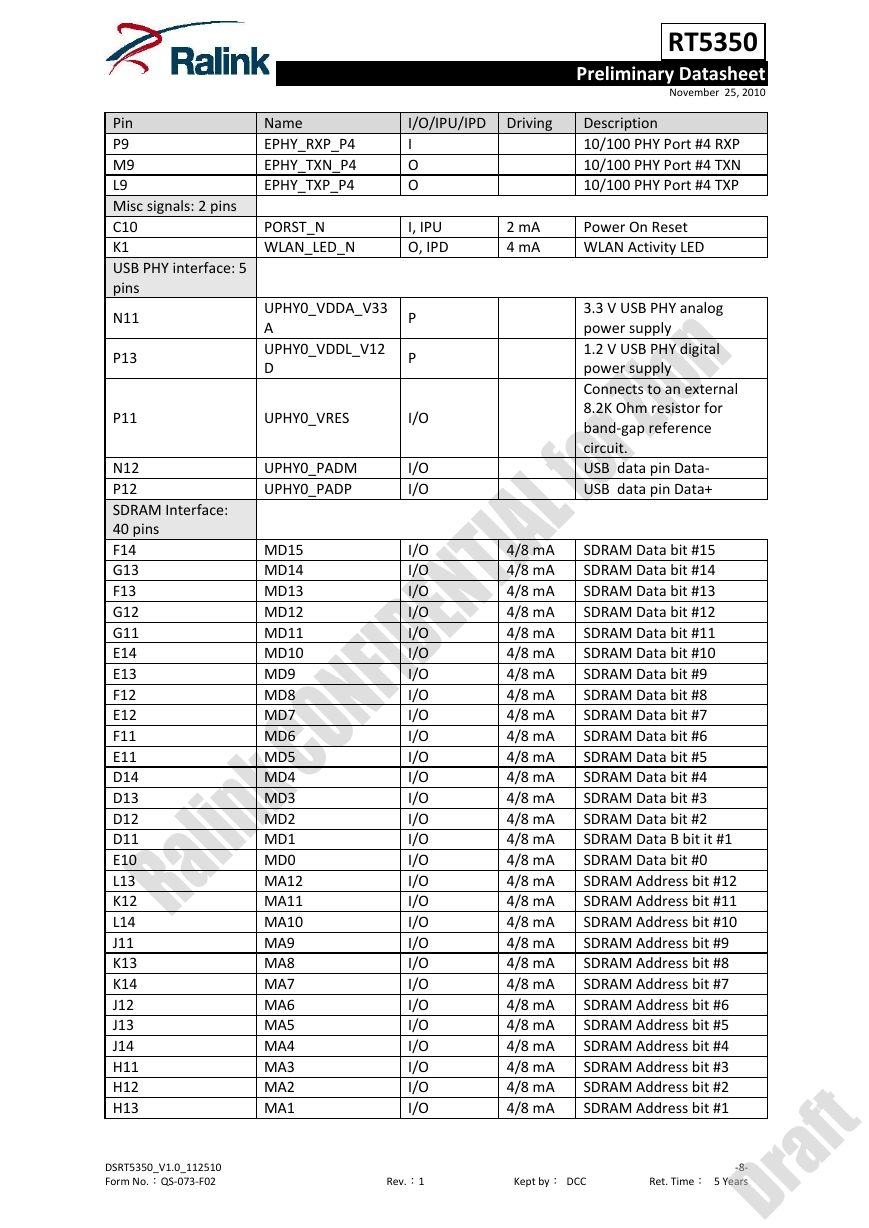

1.2 Pin Description

1.3 Pin Sharing Scheme

1.4 Boot strapping description

2 Maximum Ratings and Operating Conditions (TBD)

2.1 Absolute Maximum Ratings

2.2 Thermal Information

2.3 Operating Conditions

2.4 Storage Condition

2.5 External Xtal Specfications

2.6 DC Electrical Characteristics

2.7 AC Electrical Characteristics

2.7.1 SDRAM Interface

2.7.2 Power On Sequence

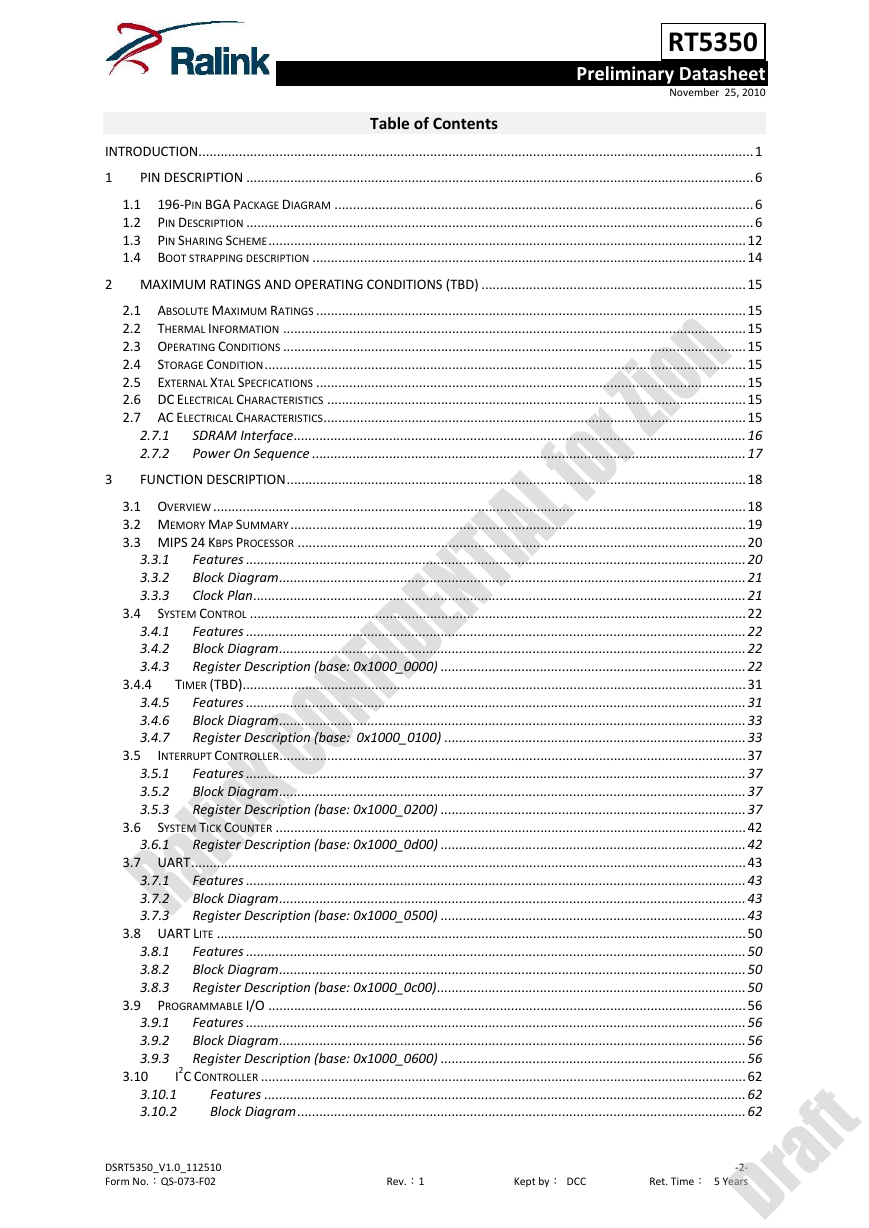

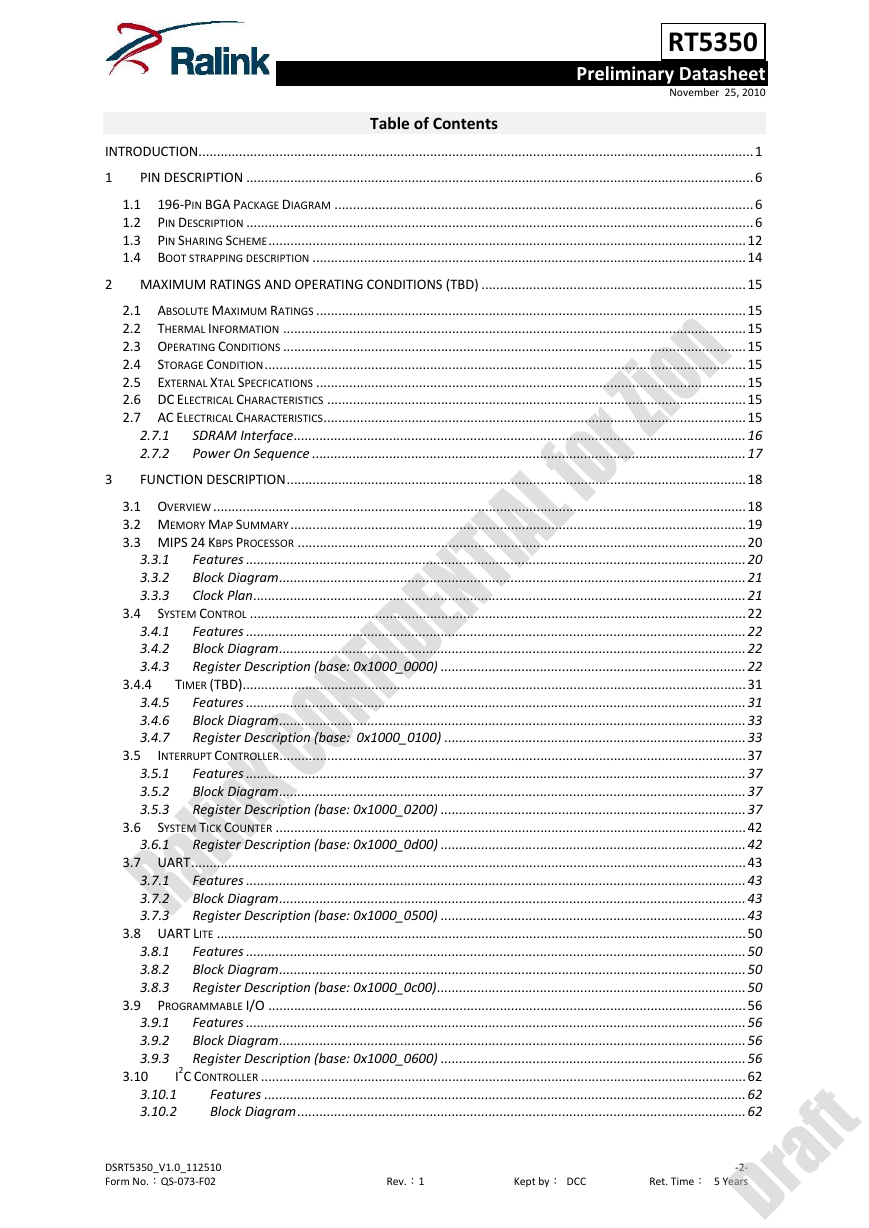

3 Function Description

3.1 Overview

3.2 Memory Map Summary

3.3 MIPS 24 Kbps Processor

3.3.1 Features

3.3.2 Block Diagram

3.3.3 Clock Plan

3.4 System Control

3.4.1 Features

3.4.2 Block Diagram

3.4.3 Register Description (base: 0x1000_0000)

3.4.4 Timer (TBD)

3.4.5 Features

3.4.6 Block Diagram

3.4.7 Register Description (base: 0x1000_0100)

3.5 Interrupt Controller

3.5.1 Features

3.5.2 Block Diagram

3.5.3 Register Description (base: 0x1000_0200)

3.6 System Tick Counter

3.6.1 Register Description (base: 0x1000_0d00)

3.7 UART

3.7.1 Features

3.7.2 Block Diagram

3.7.3 Register Description (base: 0x1000_0500)

3.8 UART Lite

3.8.1 Features

3.8.2 Block Diagram

3.8.3 Register Description (base: 0x1000_0c00)

3.9 Programmable I/O

3.9.1 Features

3.9.2 Block Diagram

3.9.3 Register Description (base: 0x1000_0600)

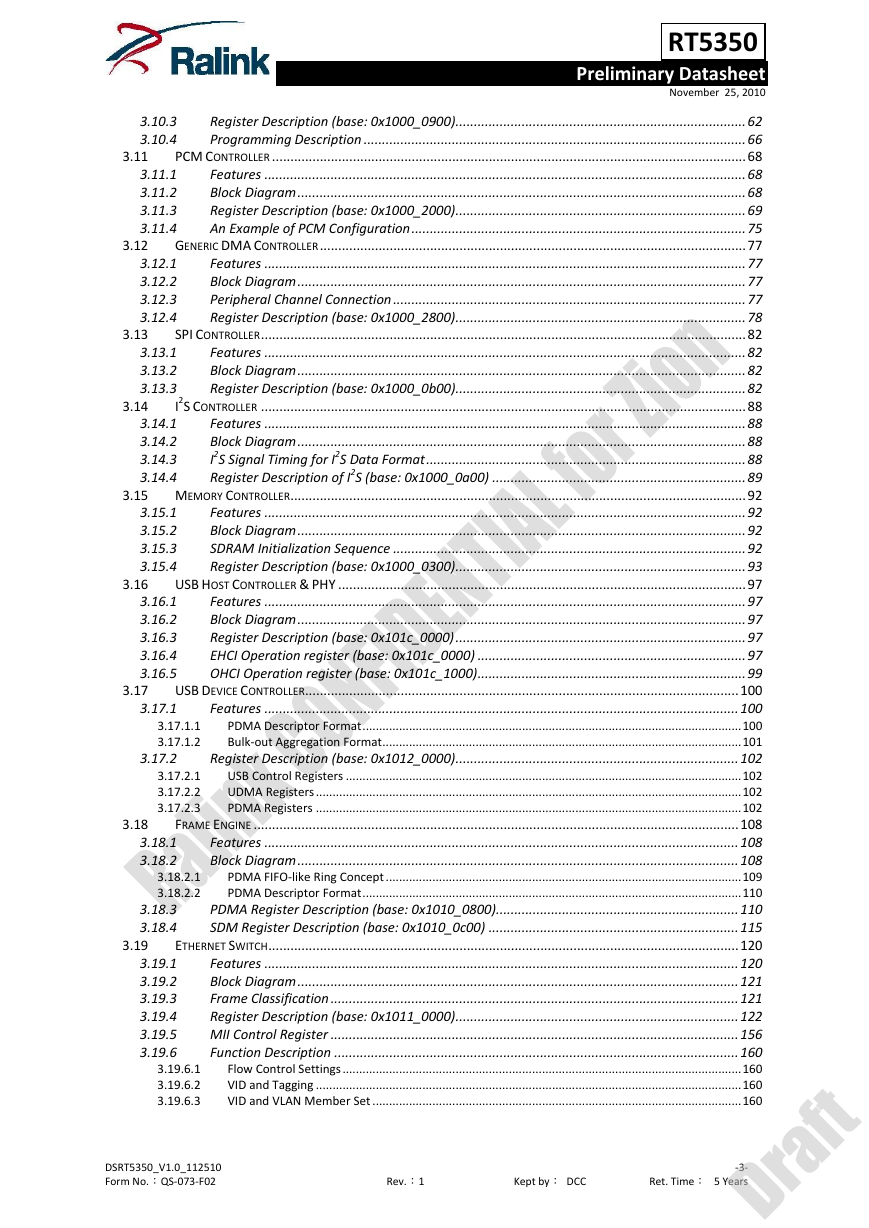

3.10 I2C Controller

3.10.1 Features

3.10.2 Block Diagram

3.10.3 Register Description (base: 0x1000_0900)

3.10.4 Programming Description

3.11 PCM Controller

3.11.1 Features

3.11.2 Block Diagram

3.11.3 Register Description (base: 0x1000_2000)

3.11.4 An Example of PCM Configuration

3.12 Generic DMA Controller

3.12.1 Features

3.12.2 Block Diagram

3.12.3 Peripheral Channel Connection

3.12.4 Register Description (base: 0x1000_2800)

3.13 SPI Controller

3.13.1 Features

3.13.2 Block Diagram

3.13.3 Register Description (base: 0x1000_0b00)

3.14 I2S Controller

3.14.1 Features

3.14.2 Block Diagram

3.14.3 I2S Signal Timing for I2S Data Format

3.14.4 Register Description of I2S (base: 0x1000_0a00)

3.15 Memory Controller

3.15.1 Features

3.15.2 Block Diagram

3.15.3 SDRAM Initialization Sequence

3.15.4 Register Description (base: 0x1000_0300)

3.16 USB Host Controller & PHY

3.16.1 Features

3.16.2 Block Diagram

3.16.3 Register Description (base: 0x101c_0000)

3.16.4 EHCI Operation register (base: 0x101c_0000)

3.16.5 OHCI Operation register (base: 0x101c_1000)

3.17 USB Device Controller

3.17.1 Features

3.17.1.1 PDMA Descriptor Format

3.17.1.2 Bulk-out Aggregation Format

3.17.2 Register Description (base: 0x1012_0000)

3.17.2.1 USB Control Registers

3.17.2.2 UDMA Registers

3.17.2.3 PDMA Registers

3.18 Frame Engine

3.18.1 Features

3.18.2 Block Diagram

3.18.2.1 PDMA FIFO-like Ring Concept

3.18.2.2 PDMA Descriptor Format

3.18.3 PDMA Register Description (base: 0x1010_0800)

3.18.4 SDM Register Description (base: 0x1010_0c00)

3.19 Ethernet Switch

3.19.1 Features

3.19.2 Block Diagram

3.19.3 Frame Classification

3.19.4 Register Description (base: 0x1011_0000)

3.19.5 MII Control Register

3.19.6 Function Description

3.19.6.1 Flow Control Settings

3.19.6.2 VID and Tagging

3.19.6.3 VID and VLAN Member Set

3.19.6.3.1 Tag and Untag

3.19.6.3.2 Port VID

3.19.6.3.3 Double Tag

3.19.6.3.4 Special Tag

3.19.6.4 Packet Classification, QoS, Scheduling and Buffer Control

3.19.6.5 Spanning Tree Protocol

3.20 802.11n 1T1R MAC/BBP

3.20.1 Features

3.20.2 Block Diagram

3.20.3 Register Description - SCH/WPDMA (base: 0x1018_0000)

3.20.3.1 Register Description - PBF (base: 0x1018_0000)

3.20.3.2 Register Description – RF TEST (base: 0x1018_0000)

3.20.3.3 Register Description - MAC (base: 0x1018_0000)

3.20.3.4 MAC Tx Configuration Registers (offset: 0x1300)

3.20.3.5 MAC Rx Configuration Registers

3.20.3.6 MAC Security Configuration Registers

3.20.3.7 MAC HCCA/PSMP CSR

3.20.3.8 MAC Statistics Counters

3.20.3.9 MAC Search Table (base: 0x1018_0000, offset: 0x1800)

3.20.3.10 Security table/CIS/Beacon/NULL frame (base : 1018_0000, offset: 0x4000)

3.20.4 Security Key Format (8DW)

3.20.5 IV/EIV Format (2 DW)

3.20.6 WCID Attribute Entry Format (1DW)

3.20.7 Shared Key Mode Entry Format (1DW)

3.20.7.1 Security Tables

3.20.8 Descriptor and Wireless information

3.20.8.1 Tx Frame Information

3.20.8.2 Tx Descriptor Format

3.20.8.3 TXWI Format

3.20.8.4 Rx Descriptor Ring

3.20.8.5 RX Descriptor Format

3.20.8.6 RXWI Format

3.20.8.7 Brief PHY Rate Format and Definition

3.20.9 Driver Implementation Note

3.20.9.1 Instructions for Downloading 8051 Firmware

3.20.9.2 Instructions for Initializing DMA

3.20.9.3 Instructions for Clock Control

3.20.9.3.1 Clock Turn-off Sequence

3.20.9.3.2 Clock Turn-on Sequence

3.20.9.4 Instructions for Tx/Rx Control

3.20.9.4.1 Freeze Tx and Rx Sequence

3.20.9.4.2 Recover Tx and Rx Sequence

3.20.9.5 Instructions for RF Power on/off Sequence

3.20.9.5.1 Power down RF components sequence:

3.20.9.5.2 Enable RF components sequence:

3.20.9.6 Power Saving Procedure

3.20.9.7 Power Recovery Procedure

3.20.9.8 Parameters

4 Packaging Physical Dimensions

3

4.1 TFBGA 196B(12×12×0.94 mm)

5 Revision History

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc