本科毕业设计论文

目 录

第一章 绪论................................................................................................................1

1.1 图像采集系统的应用......................................................................................... 1

1.2 国内外研究现状................................................................................................. 2

1.3 图像处理的实时化和高速化............................................................................. 3

1.4 本论文的主要工作............................................................................................. 5

第二章 系统设计方案..................................................................................................6

2.1 可编程逻辑器件概述......................................................................................... 6

2.2 现有视频图像处理系统方案分析比较............................................................. 7

2.2.1 方案一:CPLD/FPGA+USB/PCI/ISA+PC..................................................... 7

2.2.2 方案二:CPLD/FPGA+DSP+USB/PCI/ISA..................................................... 8

2.3 本文采用的系统设计方案............................................................................... 10

2.3.1 系统整体结构........................................................................................... 10

2.3.2 系统工作原理........................................................................................... 11

2.3.3 系统主要器件选型................................................................................... 12

2.3.4 系统难点分析........................................................................................... 12

第三章 FPGA 视频信号采集.......................................................................................13

3.1 视频信号采集流程........................................................................................... 13

SAA7113 寄存器配置..................................................................................... 13

3.2

3.2.1 SAA7113 简介............................................................................................ 14

2I C协议简介............................................................................................15

3.2.2

3.2.3 SAA7113 初始化配置................................................................................ 17

3.2.4 FPGA 配置实现.......................................................................................... 18

3.3 SAA7113 仿真模型设计................................................................................... 20

3.3.1 YUV 视频流协议分析................................................................................ 20

3.3.2 模块设计.................................................................................................... 22

3.4 SAA7113 同步信号生成模块设计................................................................... 22

3.5 采集控制模块设计........................................................................................... 23

3.5.1 模块实现.................................................................................................... 23

3.5.2 跨时钟域处理............................................................................................ 24

SDRAM 整页突发读写控制器设计................................................................. 25

SDRAM 结构及工作原理.......................................................................... 25

3.6.1

3.6.2 设计实现................................................................................................... 27

SDR_SDRAM 控制器 IP 核介绍....................................................................... 29

第四章 USB2.0 视频图像传输....................................................................................34

4.1 FPGA SLAVE FIFO 控制器设计......................................................................... 34

3.6

3.7

i

�

本科毕业设计论文

4.1.1 模块结构.................................................................................................... 36

FIFO 写控制器状态机............................................................................ 37

4.1.2

FX2 固件程序设计......................................................................................... 37

4.2

4.3 驱动程序设计.................................................................................................. 39

4.4 PC 机应用程序设计......................................................................................... 40

参考文献......................................................................................................................43

致谢.............................................................................................................................. 45

毕业设计小结..............................................................................................................46

ii

�

本科毕业设计论文

第一章 绪论

1.1 图像采集系统的应用

随着计算机技术的发展,电子产品不断地更新换代,高速、高效、高可靠性

的产品成为研究必然。在视频图像处理技术领域,传统的脱机图像处理系统己经

满足不了市场的需求,在这种趋势下,大规模集成电路或专用芯片处理系统发展

壮大。目前市场上,DSP 芯片不论集成度还是运算速度都有了大幅度提升,市场

价格也大幅降低,种种因素使得 DSP 芯片成为图像处理系统的主流趋势,而图

像采集处理系统也在这种情况下飞速发展。

实现图像处理技术的应用是多方面的,可以说,凡是在图像处理技术应用的

地方都可以应用实时图像处理技术,原因在于实时图像处理技术可以提高图像处

理的速度。但是,这要付出一定的代价,这种代价包括设备上和开发上的代价。

在可用、不可用的地方,代价问题会成为考虑的重点,而在必须应用的地方,考

虑的重点则是实时图像处理系统的性能及可行性。从应用图像处理技术的紧迫性

来看,其应用领域主要集中在消费类产品、军事、工业自动化以及公安的形式侦

察上,在这些领域强有力的推动下,实时图像处理技术得到了迅速的发展。对图

像处理系统和并行图像处理技术最前沿技术得跟踪和掌握,及针对图像处理系统

的走势,无疑高速率、高质量的实时图像显示画面将代表着未来十几年,甚至几

十年的图像处理系统的发展方向 。[1]

图像并行处理技术是图像处理中的一个重要方面,是提高图像处理速度的最

有效技术,其发展水平一直受到图像界的关注,原因在于:一方面,图像并行处

理技术的发展难度很大,这种难度不仅在于图像并行处理系统的硬件及系统结构

本身,以及它对计算机技术和集成电路等技术的依赖关系,而且在于实际应用的

复杂性和应用部门对系统价格的承受能力;另一方面,图像并行处理技术的发展

所产生的效益也是十分显著的,它在处理速度上所获得的加速比是令人振奋的,

其实际应用系统也将产生很大的经济效益和社会效益。

数字计算机对于图像处理技术有着划时代的意义,在数字化信息时代,传统

的模拟存储处理方式正在被数字化方式取代。图像采集以及处理技术也逐渐向数

字化方向转变。随着微电子技术的发展,超大规模集成电路被运用于电子设计的

各个领域,数字图像处理技术也有了突破性的进步。在现代多媒体技术中,实时

图像采集占有极其重要的地位。如今,图像采集系统大多采用实时图像采集技术。

1

�

本科毕业设计论文

实时图像采集系统己经被广泛的应用于手机、PDA、可视电话、工业控制、机器

视觉、实时监控等领域。近十年来,现场可编程门阵列 FPGA(Field Programmable

Gate Array)的飞速发展为实时图像采集设计提供了新的方向与思路。[2]

1.2 国内外研究现状

视频图像经过数字化后其数据量相当的庞大,传统的图像采集处理系统已经

不能满足如此高速数据的处理要求。目前,嵌入式系统已经成为实时图像采集系

统的热门话题。嵌入式系统功能与可靠性强、软硬件结合、体积小、功耗小、成

本低,为图像采集系统的发展提供了一种新的解决方案。特别是以 DSP、FPGA

为核心处理器的图像采集研究方法,已经成为实时图像采集领域的趋势。相比较

国内,发达国家在图像采集处理系统研究领域发展较快,其产品性能好、耐用、

可靠性强、使用范围广,但价格比较昂贵。国内产品价格较低、但不论在可靠性、

制造工艺及精度上都有所欠缺。因此,如何改进现有图像采集处理技术具有相当

的积极意义。[3]

在九十年代前,主要是以模拟设备为主的图像信息处理系统,称为第一代模

拟图像处理系统。但由于工业应用中视频监控等系统中信息流的形式以模拟视频

信号为主,其系统的网络结构主要是一种单功能、单向、集总方式的信息采集网

络,介质专用的特点,因此系统尽管己经发展到很高的水平,却无多少潜力可挖,

其固有局限性存在,难以满足更高的要求,数字化是必由之路[5]。九十年代中

期,计算机技术和视频技术飞速发展,人们利用计算的的高速数据处理能力进行

视频的采集和处理,利用显示器的高分辨率实现图像的多画面显示,大大提高了

图像质量,这种基于 PC 机的多媒体主控台系统称为数字化视频图像处理系统。

基于 PC 的视频图像处理系统的组成结构为:兼容+工控 PC 机+视频采集卡十普通

胶可靠的操作平台+应用软件。这种系统处理方式对视频图像进行了数字化,充

分利用计算机的快速处理能力,对视频图像进行压缩、分析、存储和显示。

九十年代末,随着网络带宽、计算机处理能力和储存容量的进一步提高,以

及各种视频图像处理技术的出现,图像采集处理进入全数字化时代。大规模集成

电路或专用芯片取代计算机的脱机图像处理系统。随着 DSP 芯片集成度和运算

速度的大幅提高及价格的大幅降低,DSP 芯片成为脱机图像采集系统的主流处理

器。美国 TI 公司的 DSP 及其图像处理平台在世界市场上处于主导和领先地位。

国内的 DSP 技术起步较晚,但发展较快,90 年代末就有比较成熟的产品出现。

典型产品有 WT62OIp/RA、WT670lP/PA 图像处理系统和 WT32EA 通用图像处理

系统。在专用图像处理系统方面,西南物理研究所开发的机遇 DSP 的视频跟踪

警戒装置和中科院沈阳自动化研究所开发的基于 DSP 的视频跟踪装置,都取得

了很好的效果。台湾凌阳公司的图像识别芯片 SPCA563,用于智能交互式玩具

中,能识别颜色、形状和障碍物。[4]

2

�

本科毕业设计论文

现代大容量高速度的 FPGA 以及相应可编程片上系统 SOPC 技术的出现,为

图像采集和处理系统提供了一种新的解决方案。目前,在图像方面已经有很多成

熟的 IP Core,如 2D 滤波器、2D 快速傅里叶变换、颜色空间转换、JPEG 图像编

码器等。利用 FPGA 来实现“DSP’’系统己经十分普遍,应用在诸如实时图像处理、

联合战术无线通信等。

使用 Altera 公司 FPGA 内嵌 SOPC 构架完成图像的采集、处理及显示功能,

目前在国内还处于初级阶段,这种系统 SOPC 软核构架具有一定的风险性。但

Altera 的技术支持可以使用 FPGA 内部的硬件资源和内部正进行外部设备的驱动

开发等,这样大大减少硬件设计的复杂性。而且,FPGA 实现数字信号处理最显

著的特点就是高速性能好,以软件方式控制操作和运算的系统速度显然无法与纯

硬件系统相比,因为软件是通过顺序执行的方式来完成控制和运算步骤的,而

HDL 语言描述的系统是以并行方式工作的。目前,国内外对基于 FPGA 这种“虚

拟 SOC,的需求呈上升趋势。

在 FPGA 中,一般内嵌可配置的 RAM、LVDS、PLL 及硬件乘法累加器等

模块。用 FPGA 来处理数字信号可以很好的解决数据量大、处理速度不匹配、可

靠性低及精度小等问题,并能很好协调并行性与顺序性的矛盾。因 FPGA 灵活的

可配置特性,使其构成的 DSP 系统易于测试与修改。如今,利用 FPGA 来实现

DSP 系统己经发展普遍,以 FPGA 为代表的数字系统处理技术也有了新的发展,

主要有:

�高效性:各大现场可编程逻辑器件厂商在不断地补充其知识产权 (IP)核心

库。设计人员可以直接利用这些经过测试和优化、可保证正确性的现成的资源来

完成复杂的片上系统设计,提高设计的准确性及高效性。

�密度及功耗小:便携式产品的发展,使得产品对现场可编程器件的高密度、

低功耗要求逐步提升。芯片正朝着高密度、低功耗方向发展。

�实现片上系统:深亚微米技术的发展使得片上系统 SOPC 的实现成为可

能。[5]

1.3 图像处理的实时化和高速化

图像处理是计算机应用领域中一个极为活跃的领域,它的发展己有 40 余年

的历史,在此期间,随着计算机、集成电路等技术的飞速发展,图像处理无论在

算法上、系统结构上,还是在应用上以及普及的程度上都取得了长足的进展。但

是图像处理依然面临着许多挑战性的问题,其中最主要的问题就是如何提高解决

实际复杂问题的综合能力,就当前的技术水平来说,这种综合能力包括图像处理

的网络化、复杂问题的求解与图像处理速度的实时化和高速化。

图像处理的速度问题主要由图像数据的特点、图像处理算法的复杂性以及处

理系统硬件结构和速度引起。为提高图像处理系统速度,一方面可以改变图像数

3

�

本科毕业设计论文

据特点,但这种方法通常是不可取的,因为处理系统往往需要充分利用图像数据

中的信息;其次是选用高速处理器件,并尽量减化图像处理算法;再者可以采用

并行处理技术,这种技术选用多个高速处理器件来完成同一任务,使得处理速度

得到成倍提高。图像并行处理技术是图像处理中的一个重要方面,是提高图像处

理速度的最有效技术,其发展水平一直受到图像界的关注。原因在于:一方面,

图像并行处理技术的发展难度很大,这种难度不仅在于图像处理系统的硬件及系

统结构本身,以及它对计算机技术和集成电路等技术的依赖关系,而且在于实际

应用的复杂性和应用部门对系统价格的承受能力;另一方面,图像并行处理技术

的发展所产生的效益也是十分显著的,它在处理速度上所获得的加速比是令人振

奋的,其实际应用系统也将产生很大的经济效益和社会效益。

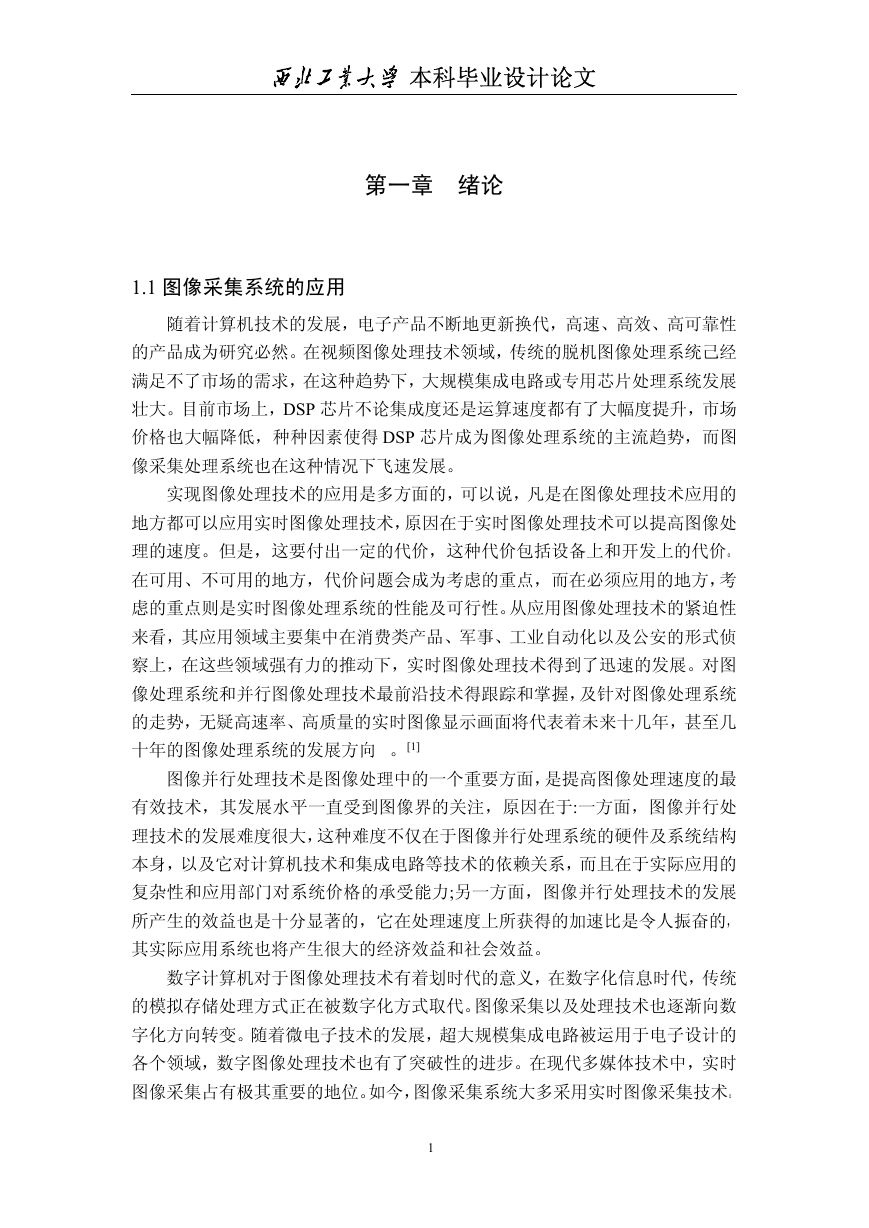

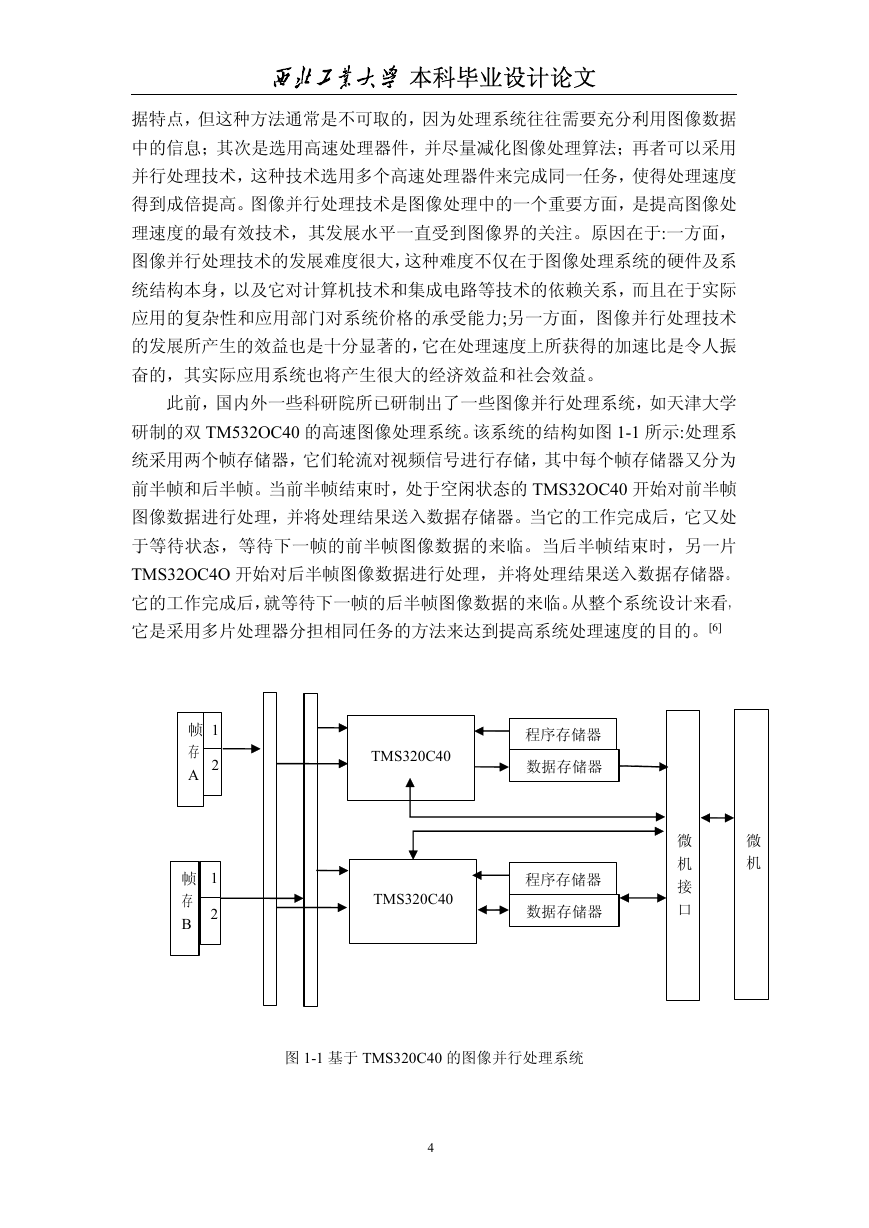

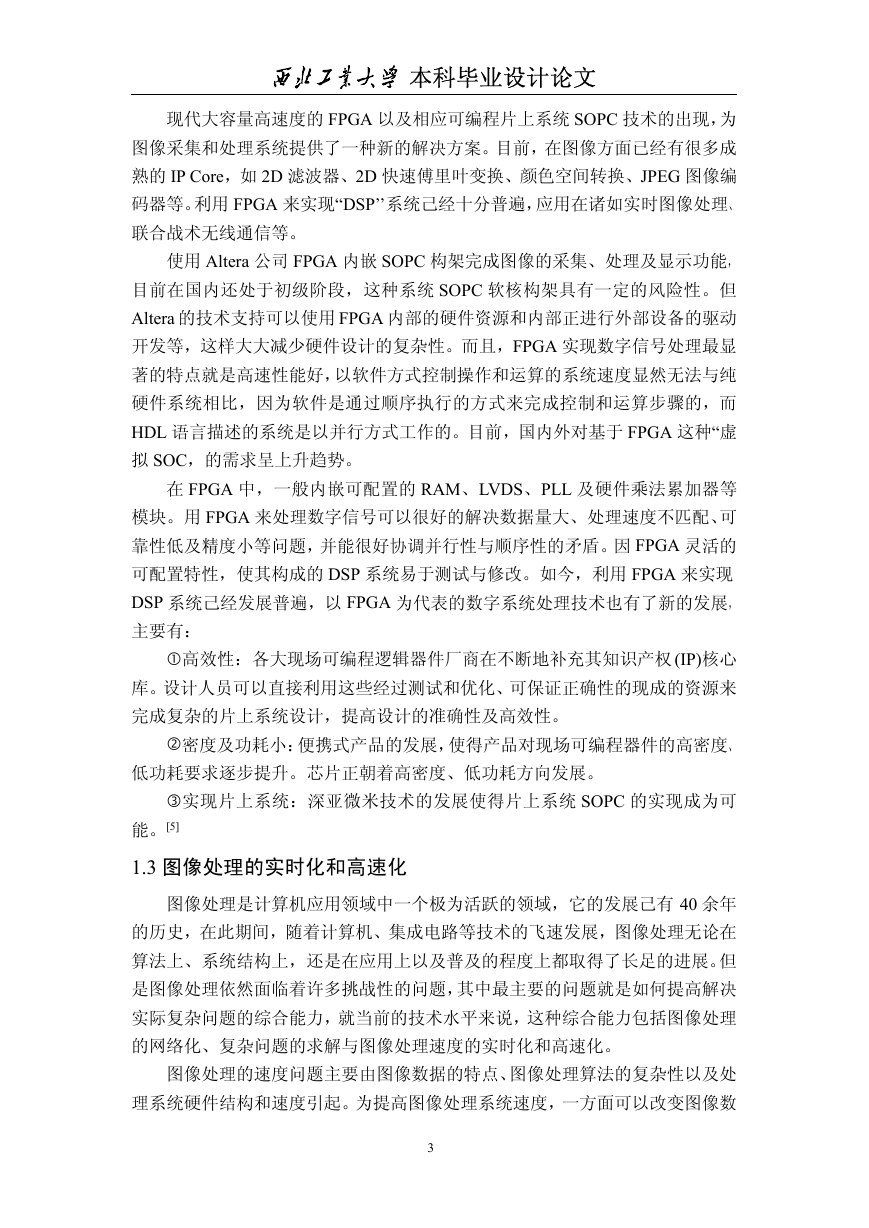

此前,国内外一些科研院所已研制出了一些图像并行处理系统,如天津大学

研制的双 TM532OC40 的高速图像处理系统。该系统的结构如图 1-1 所示:处理系

统采用两个帧存储器,它们轮流对视频信号进行存储,其中每个帧存储器又分为

前半帧和后半帧。当前半帧结束时,处于空闲状态的 TMS32OC40 开始对前半帧

图像数据进行处理,并将处理结果送入数据存储器。当它的工作完成后,它又处

于等待状态,等待下一帧的前半帧图像数据的来临。当后半帧结束时,另一片

TMS32OC4O 开始对后半帧图像数据进行处理,并将处理结果送入数据存储器。

它的工作完成后,就等待下一帧的后半帧图像数据的来临。从整个系统设计来看,

它是采用多片处理器分担相同任务的方法来达到提高系统处理速度的目的。[6]

1

2

帧

存

A

1

2

帧

存

B

TMS320C40

程序存储器

数据存储器

TMS320C40

程序存储器

数据存储器

微

机

微

机

接

口

图 1-1 基于 TMS320C40 的图像并行处理系统

4

�

本科毕业设计论文

1.4 本论文的主要工作

本论文主要目的在于设计一种基于 FPGA 和 USB2.0 的视频图像采集及处理

平台,在此平台上可以验证各种图像处理或视频压缩算法,并通过 USB2.0 实现

视频图像的 PC 机采集及处理后数据传输。另外,整个平台还需兼顾处理的实时

化和高速化,以满足不同领域视频图像预处理要求。整个系统可分为四个部

分:FPGA 视频信号采集、视频图像处理算法 FPGA 实现、USB2.0 视频信号传输

和视频图像显示部分。其中视频图像处理算法 FPGA 实现部分可由用户根据自己

的具体需求来实现,本论文的设计重心在于提供一个基于 FPGA 的视频图像处理

算法验证平台,不涉及具体算法的实现过程。

5

�

本科毕业设计论文

第二章 系统设计方案

2.1 可编程逻辑器件概述

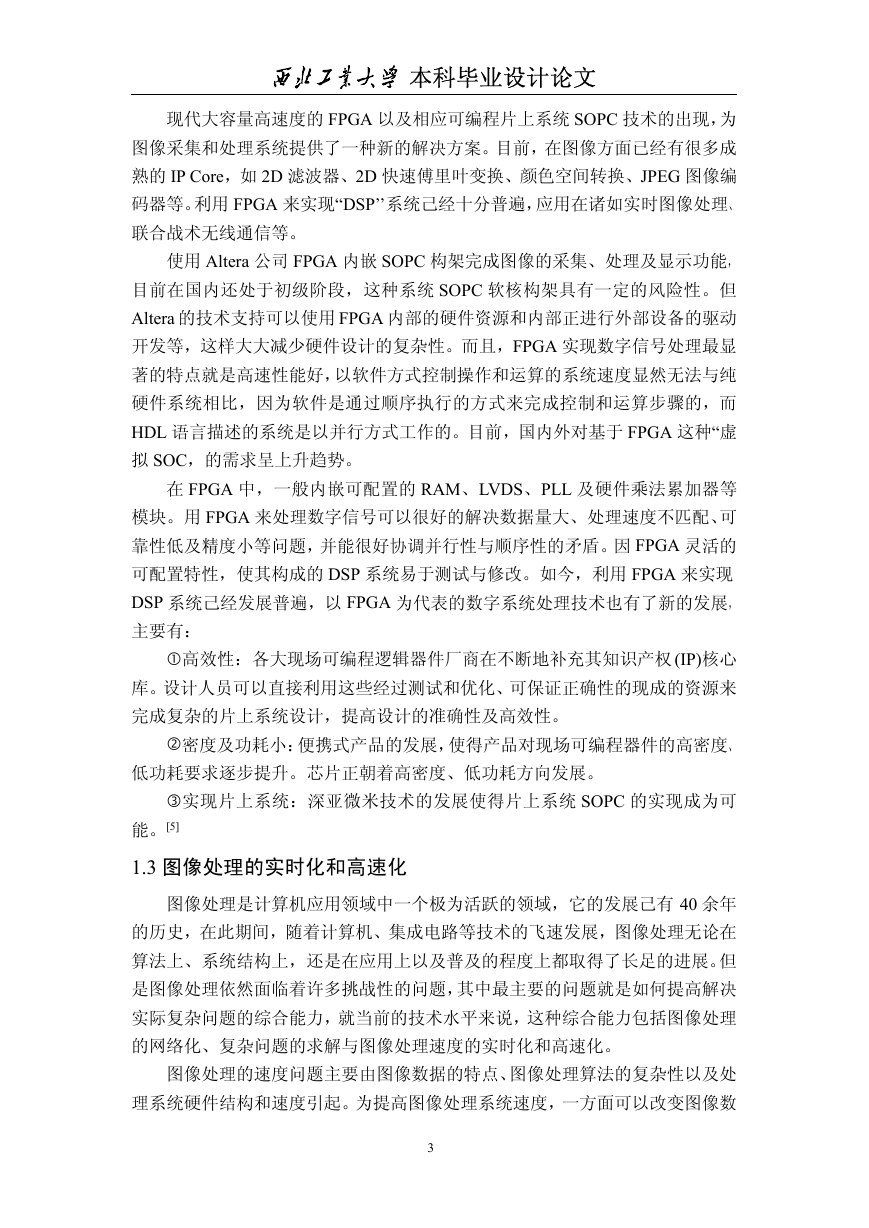

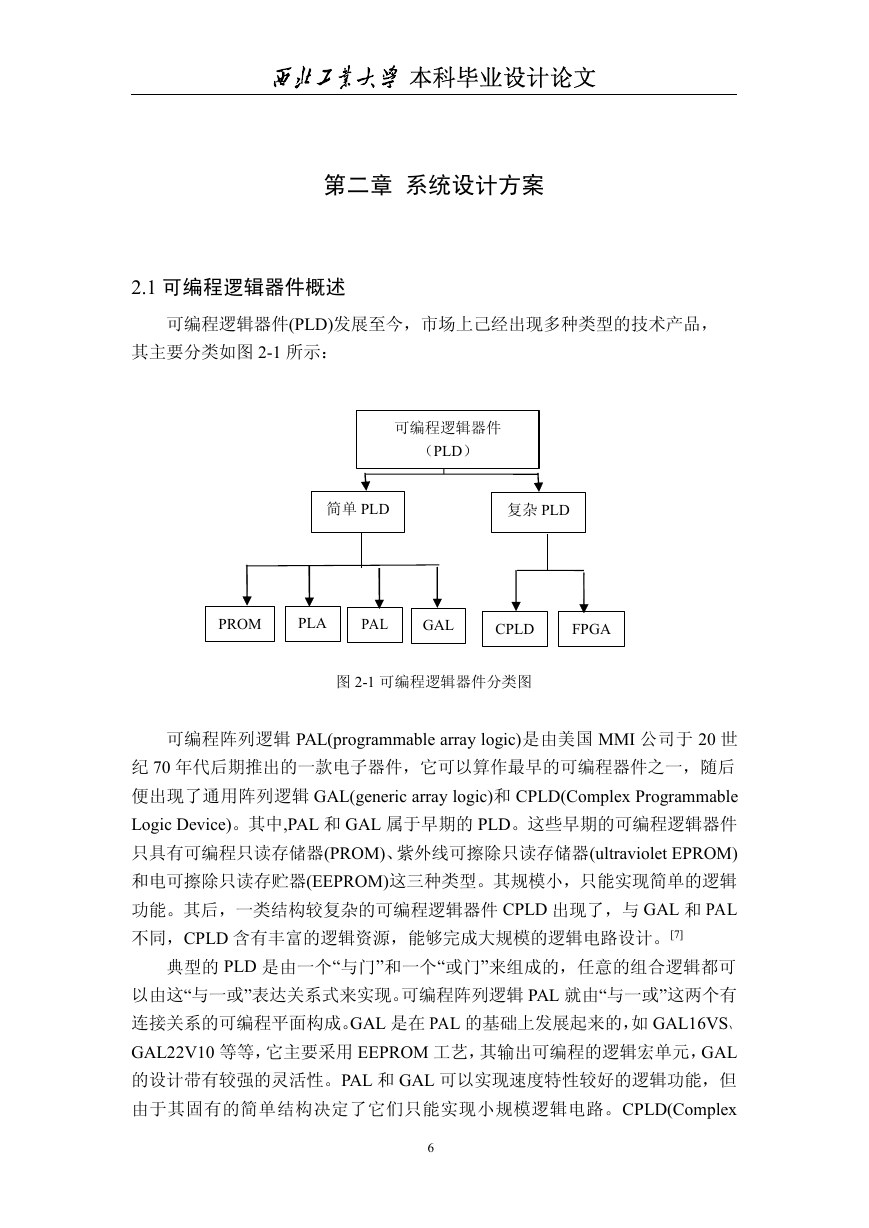

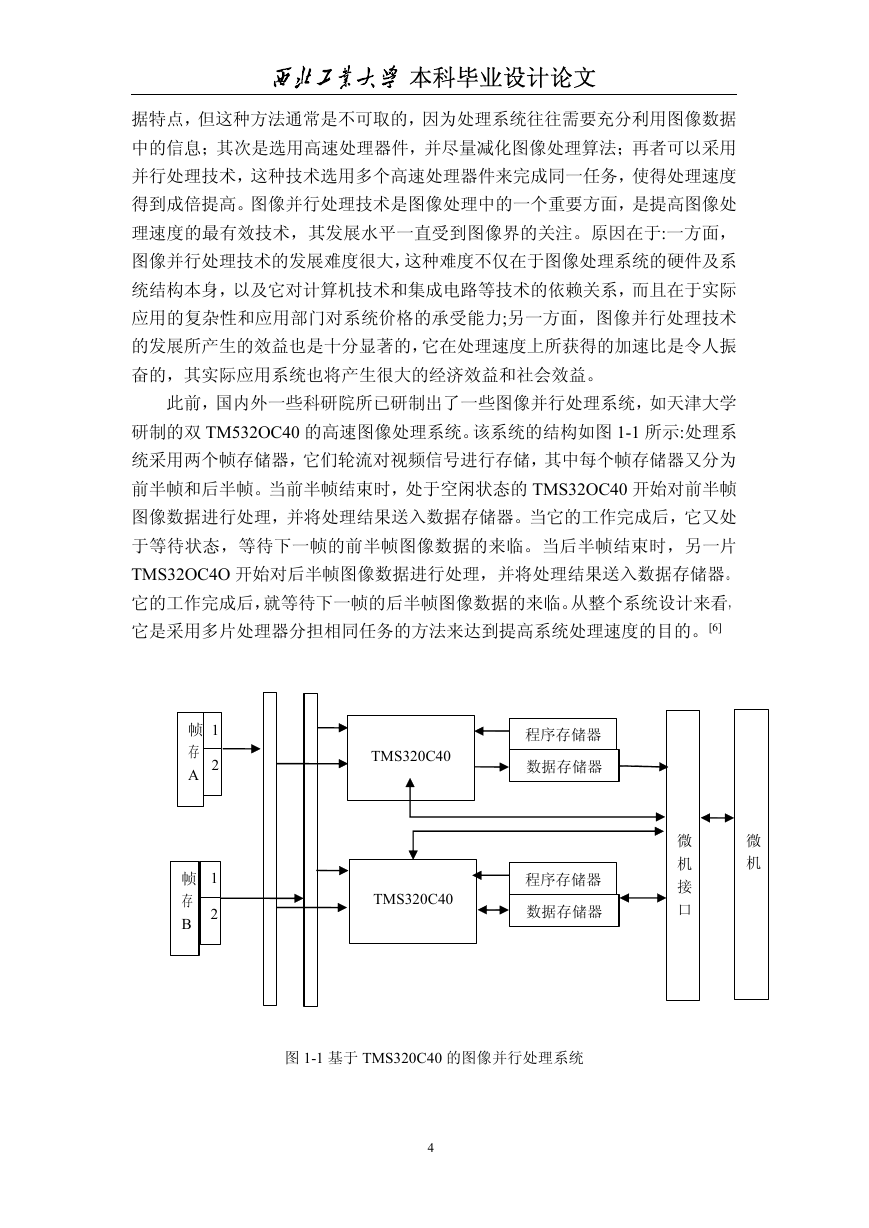

可编程逻辑器件(PLD)发展至今,市场上己经出现多种类型的技术产品,

其主要分类如图 2-1 所示:

可编程逻辑器件

(PLD)

简单 PLD

复杂 PLD

PROM

PLA

PAL

GAL

CPLD

FPGA

图 2-1 可编程逻辑器件分类图

可编程阵列逻辑 PAL(programmable array logic)是由美国 MMI 公司于 20 世

纪 70 年代后期推出的一款电子器件,它可以算作最早的可编程器件之一,随后

便出现了通用阵列逻辑 GAL(generic array logic)和 CPLD(Complex Programmable

Logic Device)。其中,PAL 和 GAL 属于早期的 PLD。这些早期的可编程逻辑器件

只具有可编程只读存储器(PROM)、紫外线可擦除只读存储器(ultraviolet EPROM)

和电可擦除只读存贮器(EEPROM)这三种类型。其规模小,只能实现简单的逻辑

功能。其后,一类结构较复杂的可编程逻辑器件 CPLD 出现了,与 GAL 和 PAL

不同,CPLD 含有丰富的逻辑资源,能够完成大规模的逻辑电路设计。[7]

典型的 PLD 是由一个“与门”和一个“或门”来组成的,任意的组合逻辑都可

以由这“与一或”表达关系式来实现。可编程阵列逻辑 PAL 就由“与一或”这两个有

连接关系的可编程平面构成。GAL 是在 PAL 的基础上发展起来的,如 GAL16VS、

GAL22V10 等等,它主要采用 EEPROM 工艺,其输出可编程的逻辑宏单元,GAL

的设计带有较强的灵活性。PAL 和 GAL 可以实现速度特性较好的逻辑功能,但

由于其固有的简单结构决定了它们只能实现小规模逻辑电路。CPLD(Complex

6

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc