异步设计与同步设计的时序分析

�

学习指南

【知识目标】

(1) 理解亚稳态产生的物理意义

(2) 理解触发器本身的建立时间和保持时间以及异步复位恢复的概念

(3) 理解亚稳态恢复和同步寄存器的概念

(4) 理解组合逻辑的延迟产生的原理,掌握系统时钟频率的计算

(5) 理解并掌握时钟偏斜和抖动及其对时钟频率的影响

(6) 理解提高系统时钟频率的两种方法

(7) 了解False Path和多时钟周期的概念,知道使用False Path和多时钟周期进行时序约束。

(8) 理解并掌握芯片之间的时序接口设计

(9) 理解并掌握异步电路的设计方法

【技能目标】

(1) 学会基本的静态时序分析(建立时间、保持时间等)与设计约束

(2) 学会时钟频率计算及其提高系统时钟频率的集中方法

(3) 学会设计异步电路的设计方法

(4) 学会对芯片之间的接口时序进行约束

(5) 能够设计稳定的异步电路

�

学习指南

【重点难点】

(1) 建立时间和保持时间对系统时钟周期

的影响

(2) 给定约束条件下的静态时序分析

(3) 异步设计方法

�

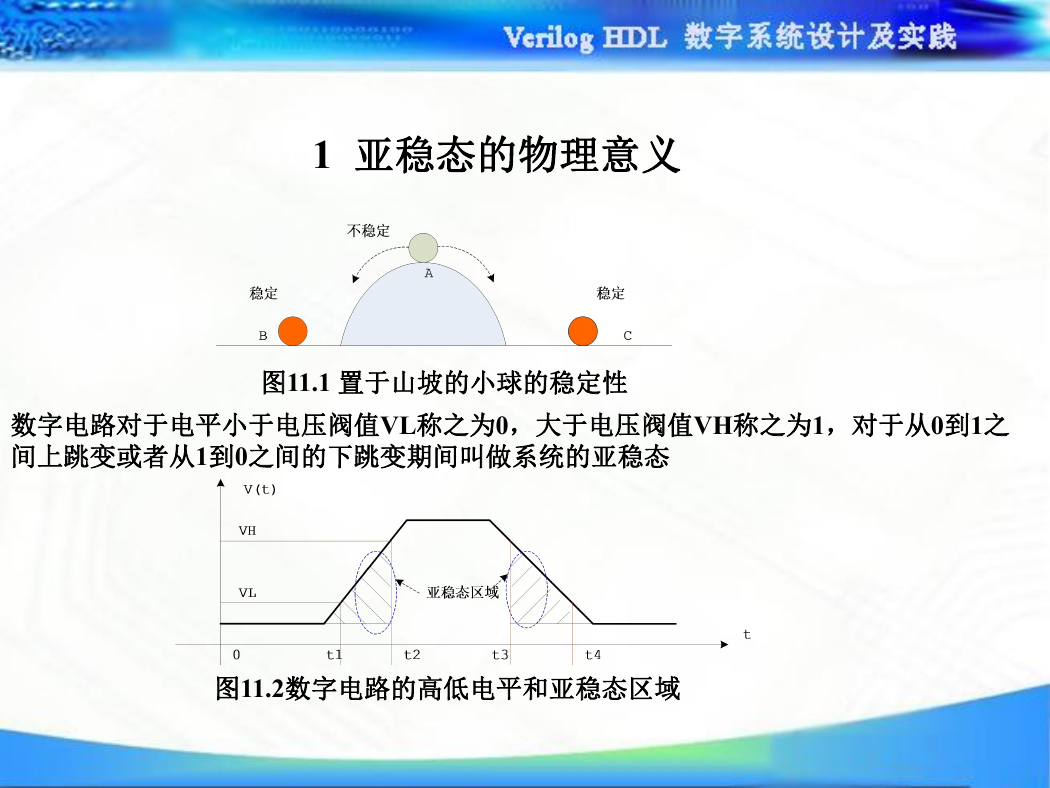

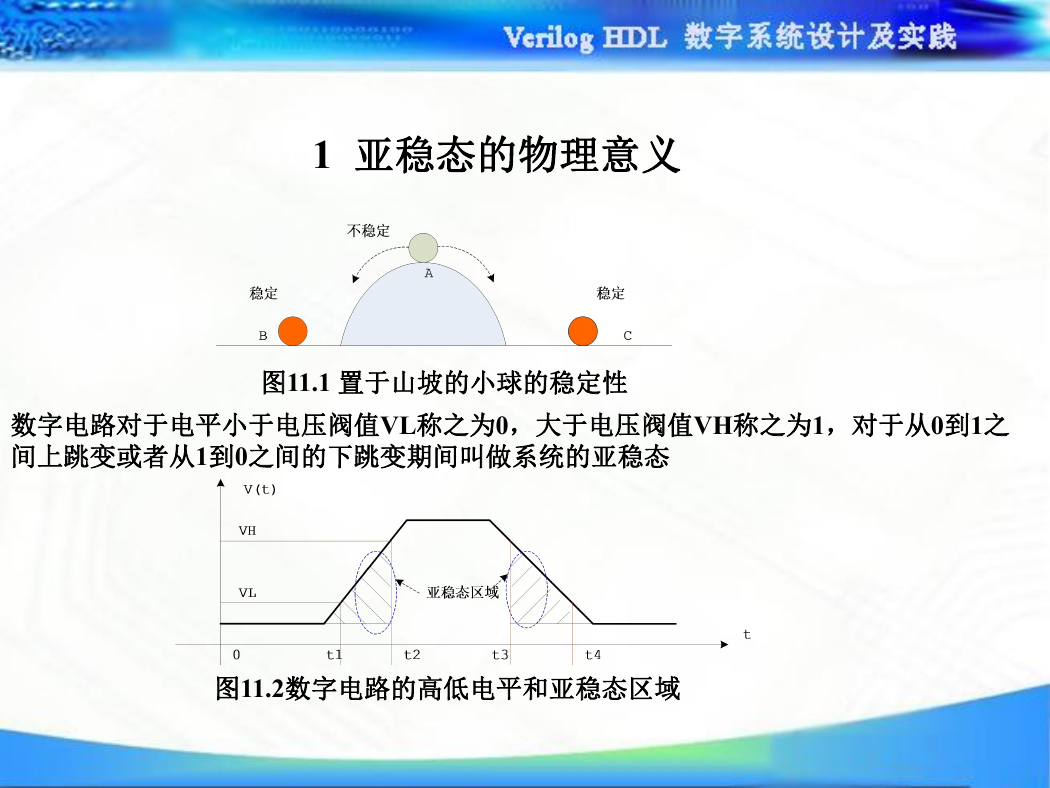

1 亚稳态的物理意义

图11.1 置于山坡的小球的稳定性

数字电路对于电平小于电压阀值VL称之为0,大于电压阀值VH称之为1,对于从0到1之

间上跳变或者从1到0之间的下跳变期间叫做系统的亚稳态

图11.2数字电路的高低电平和亚稳态区域

�

2 亚稳态与建立时间、保持时间、异步复位恢复时间

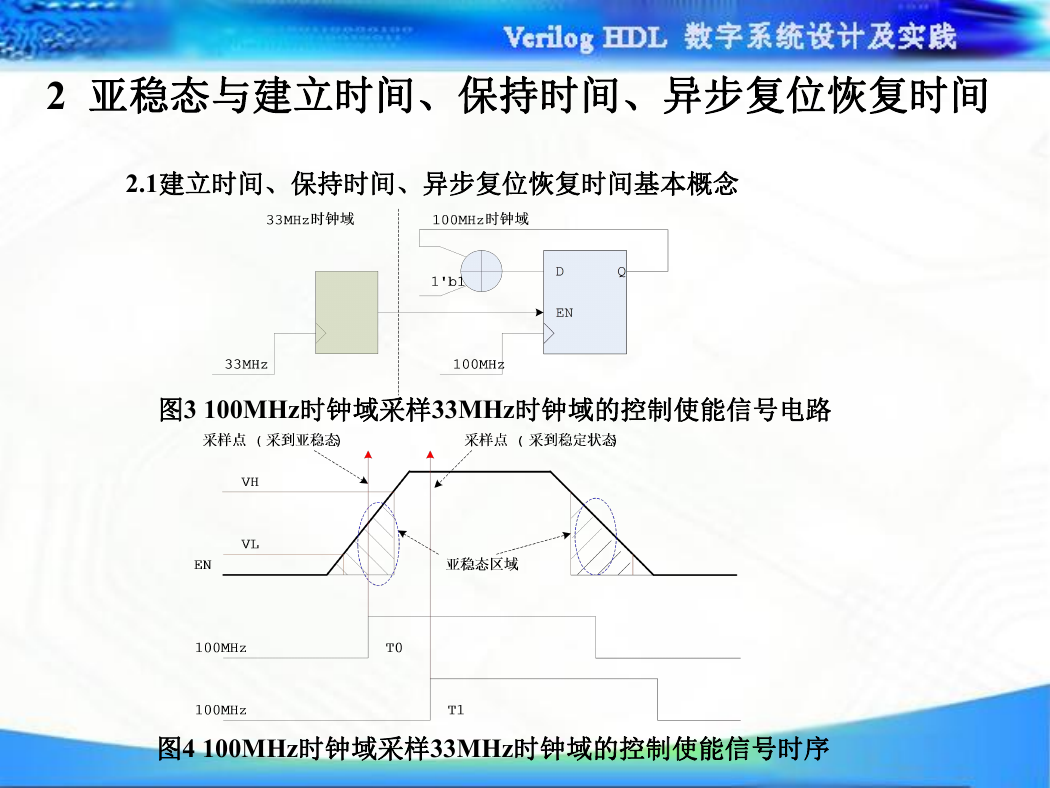

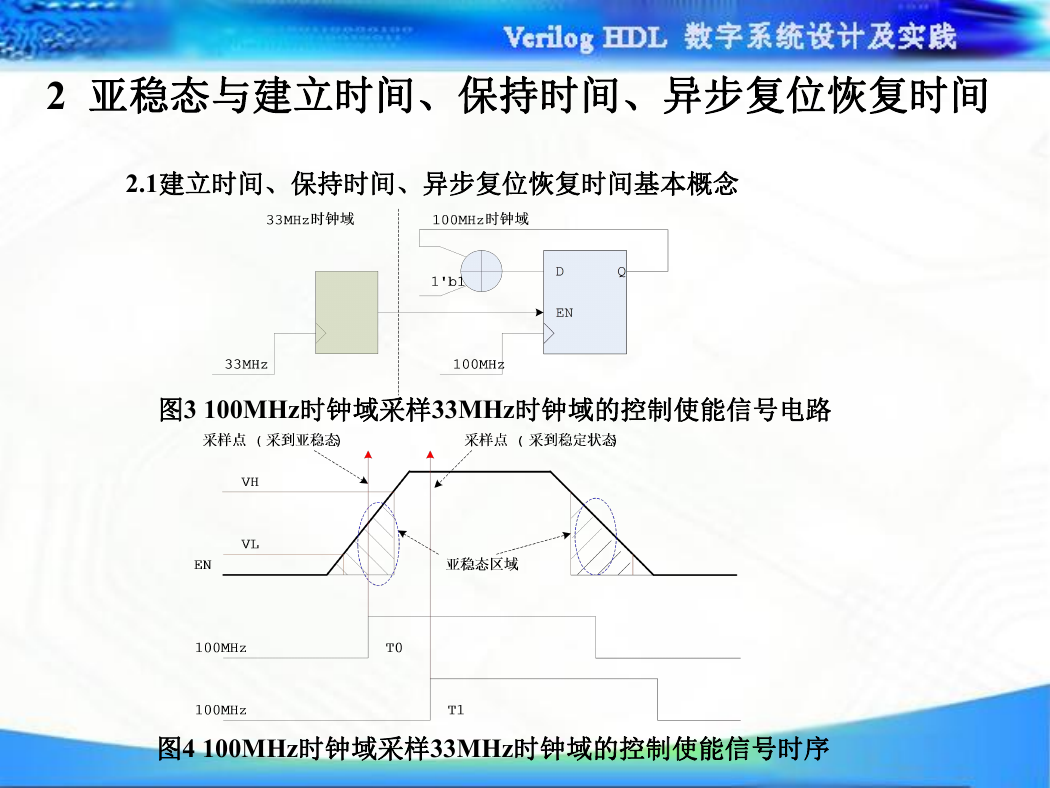

2.1建立时间、保持时间、异步复位恢复时间基本概念

图3 100MHz时钟域采样33MHz时钟域的控制使能信号电路

图4 100MHz时钟域采样33MHz时钟域的控制使能信号时序

�

2 亚稳态与建立时间、保持时间、异步复位恢复时间

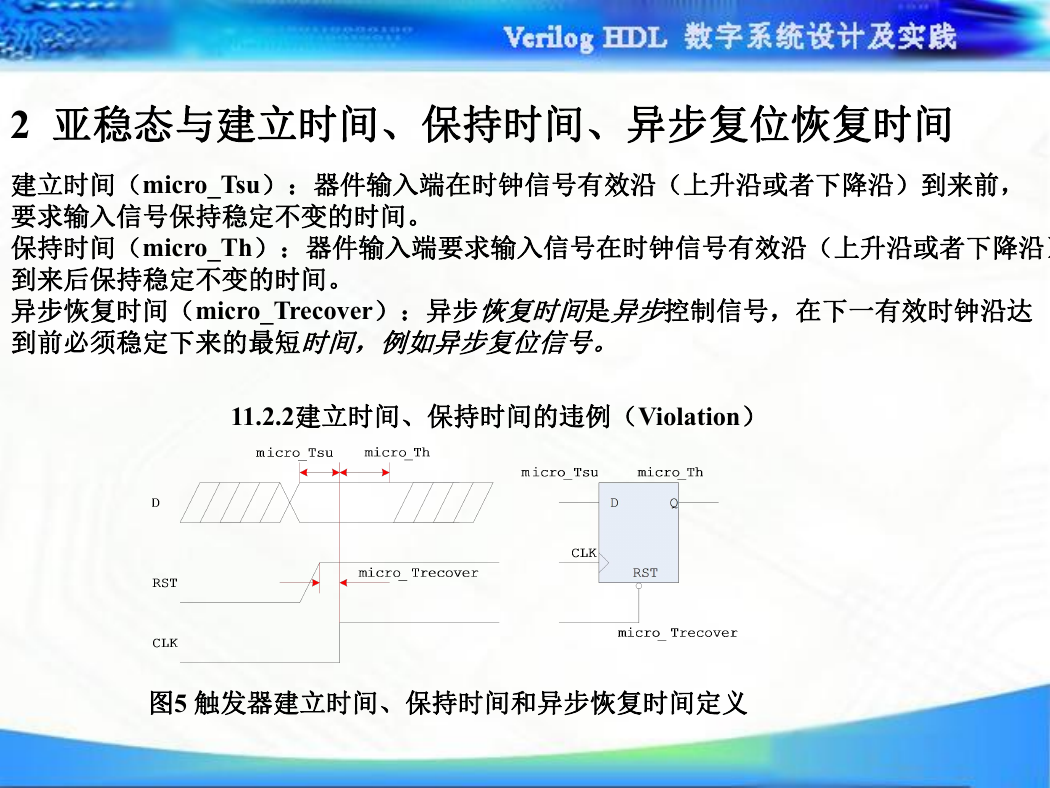

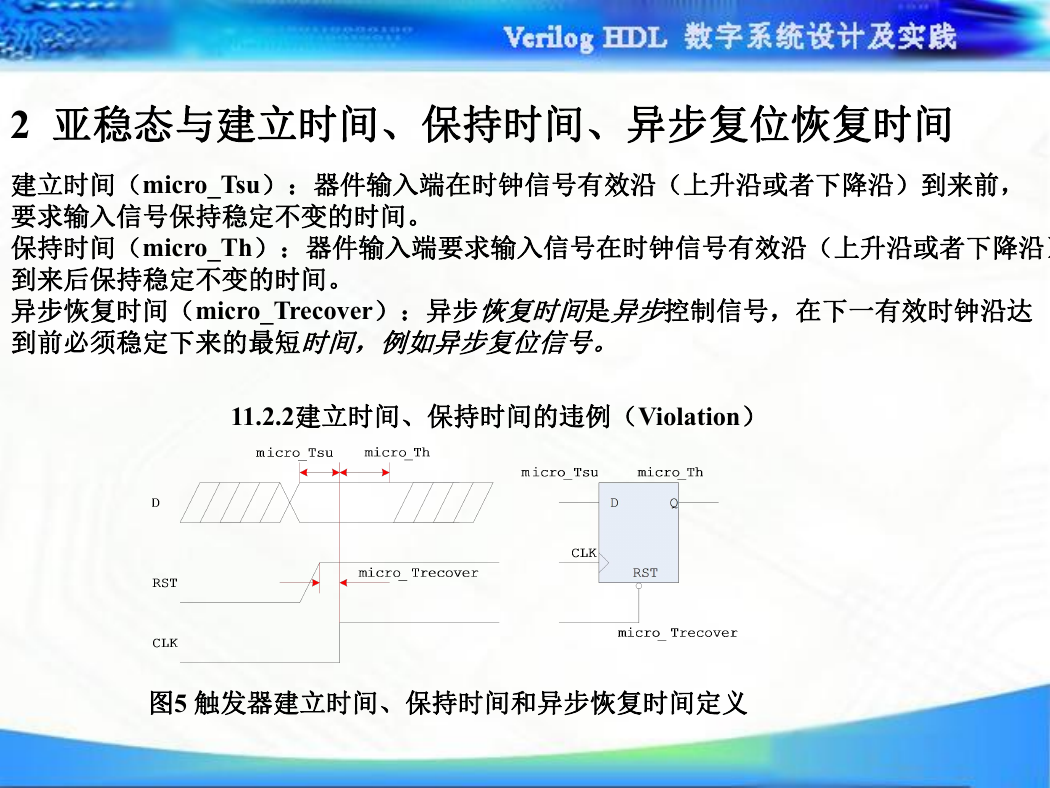

建立时间(micro_Tsu):器件输入端在时钟信号有效沿(上升沿或者下降沿)到来前,

要求输入信号保持稳定不变的时间。

保持时间(micro_Th):器件输入端要求输入信号在时钟信号有效沿(上升沿或者下降沿)

到来后保持稳定不变的时间。

异步恢复时间(micro_Trecover):异步恢复时间是异步控制信号,在下一有效时钟沿达

到前必须稳定下来的最短时间,例如异步复位信号。

11.2.2建立时间、保持时间的违例(Violation)

图5 触发器建立时间、保持时间和异步恢复时间定义

�

2 亚稳态与建立时间、保持时间、异步复位恢复时间

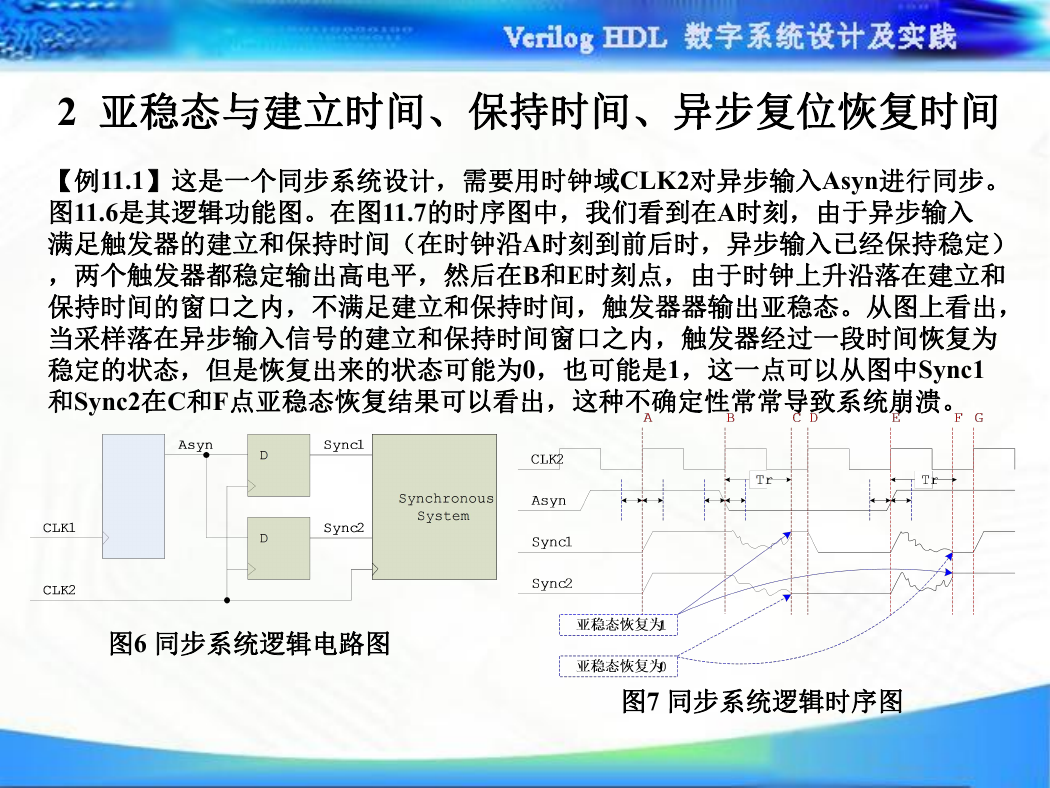

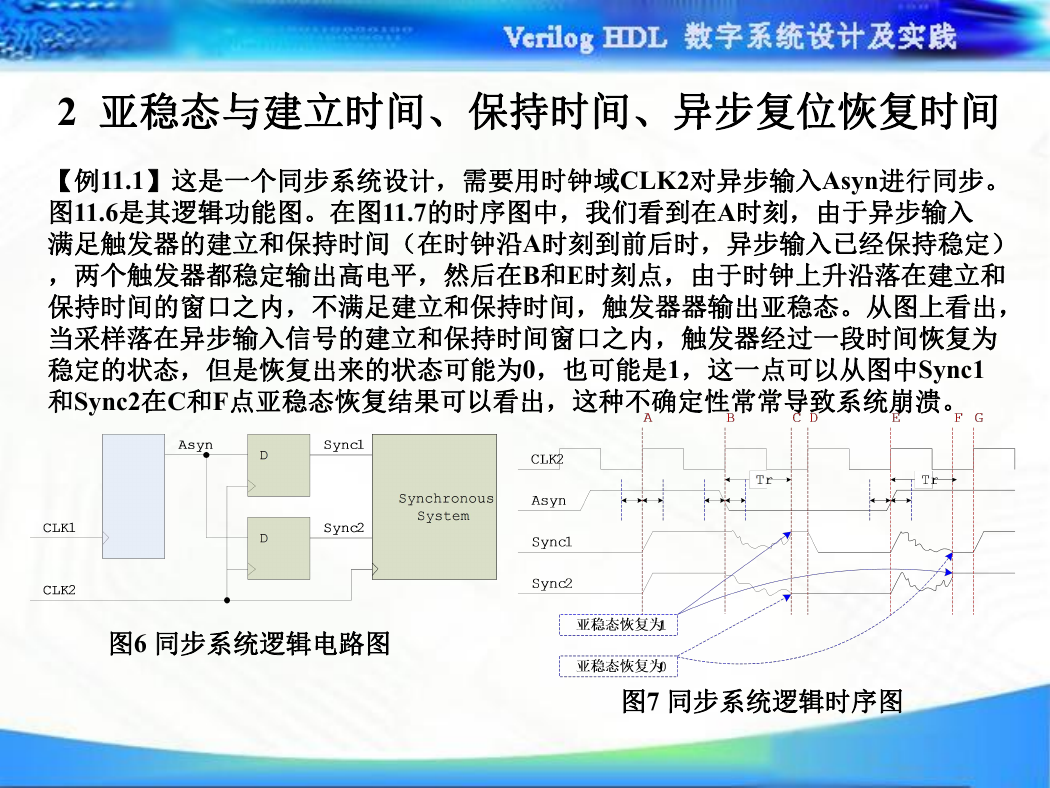

【例11.1】这是一个同步系统设计,需要用时钟域CLK2对异步输入Asyn进行同步。

图11.6是其逻辑功能图。在图11.7的时序图中,我们看到在A时刻,由于异步输入

满足触发器的建立和保持时间(在时钟沿A时刻到前后时,异步输入已经保持稳定)

,两个触发器都稳定输出高电平,然后在B和E时刻点,由于时钟上升沿落在建立和

保持时间的窗口之内,不满足建立和保持时间,触发器器输出亚稳态。从图上看出,

当采样落在异步输入信号的建立和保持时间窗口之内,触发器经过一段时间恢复为

稳定的状态,但是恢复出来的状态可能为0,也可能是1,这一点可以从图中Sync1

和Sync2在C和F点亚稳态恢复结果可以看出,这种不确定性常常导致系统崩溃。

图6 同步系统逻辑电路图

图7 同步系统逻辑时序图

�

3 亚稳态的恢复时间Tr与同步寄存器的MTBF

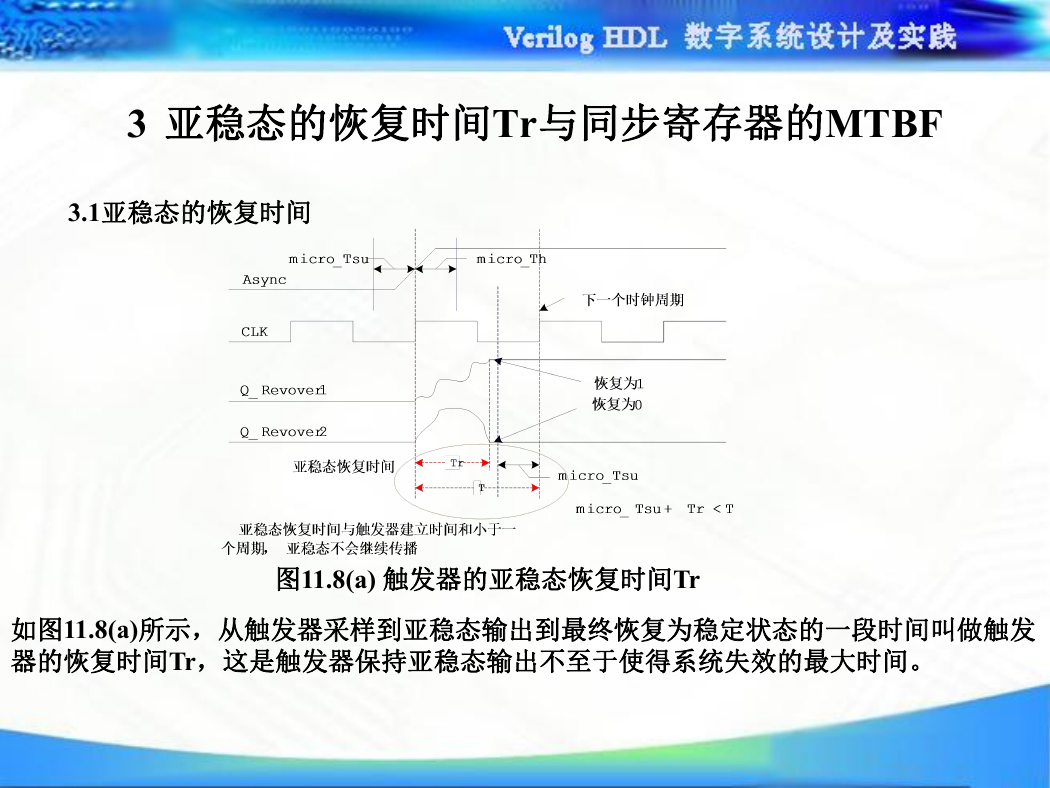

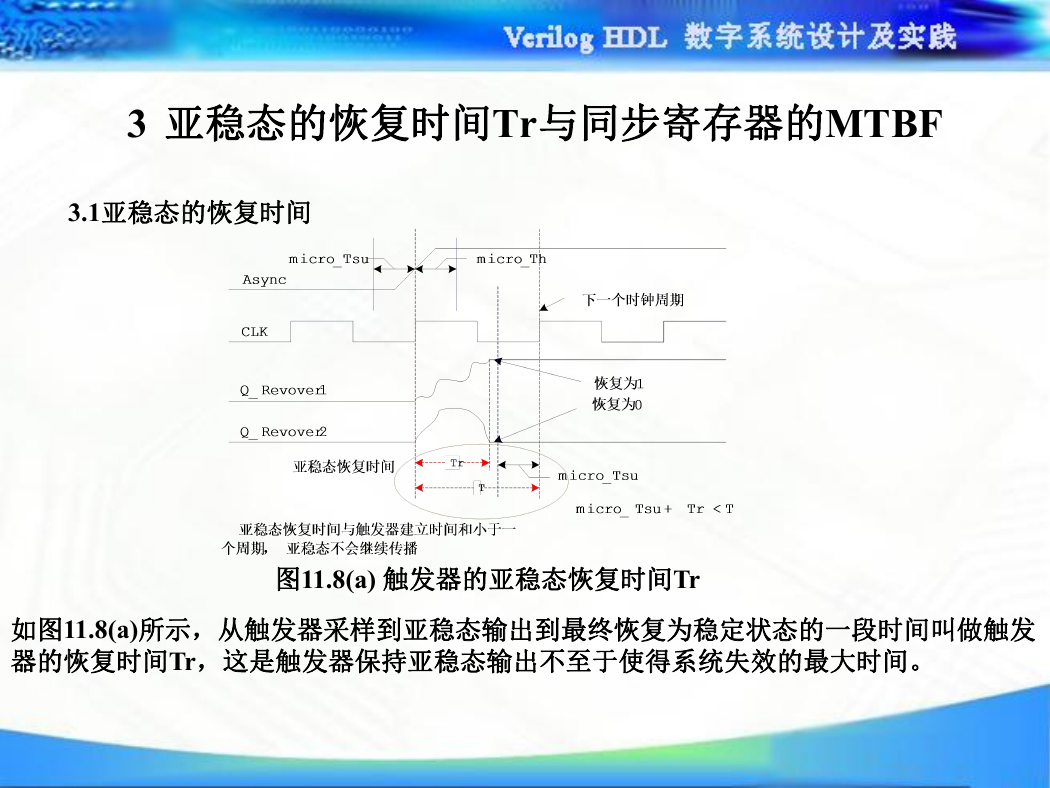

3.1亚稳态的恢复时间

图11.8(a) 触发器的亚稳态恢复时间Tr

如图11.8(a)所示,从触发器采样到亚稳态输出到最终恢复为稳定状态的一段时间叫做触发

器的恢复时间Tr,这是触发器保持亚稳态输出不至于使得系统失效的最大时间。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc