Sony Corporation

SLVS-EC Specification

SLVS-EC

Specification

Version 1.2

xx July 2013

1/74

Sony Confidential

�

Sony Corporation

SLVS-EC Specification

USE RESTRICTION NOTICE

This USE RESTRICTION NOTICE (“Notice”) is for customers who are considering or currently

using the CMOS image sensor products or the DSP products (“Products”) integrated with SLVS-EC

interface set forth in this specification. Sony Corporation (“Sony”) may, at any time, modify this

Notice which will be available to you in the latest specification for SLVS-EC. You should abide by

the latest version of this Notice. If a Sony subsidiary or distributor has its own use restriction notice

on the Products, such a use restriction notice will additionally apply between you and the subsidiary

or distributor. You should consult a sales representative of the subsidiary or distributor of Sony

(“Sales Representative”) on such a use restriction notice when you consider using the Products with

SLVS-EC interface.

All materials contained herein are protected by copyright laws, and may not be reproduced,

republished, distributed, transmitted, displayed, broadcast or otherwise exploited in any manner

without the permission of Sony.

Disclaimer

Sony will not assume responsibility for any problems in connection with your use of the technical

information shown in this specification or for any infringement of third-party rights due to the same.

It is therefore your sole legal and financial responsibility to resolve any such problems and

infringement. THIS SPECIFICATION DOCUMENT IS PROVIDED "AS IS" AND WITHOUT

WARRANTY OF ANY KIND, AND SONY EXPRESSLY DISCLAIMS ALL WARRANTIES,

EXPRESS OR IMPLIED, STATUTORY OR OTHERWISE, INCLUDING, BUT NOT LIMITED

TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A

PARTICULAR USE OR PURPOSE, AND THE WARRANTY OF NON-INFRINGEMENT OF

ANY THIRD PARTY INTELLECTUAL PROPERTY. SONY DOES NOT WARRANT THAT THE

TECHNICAL INFORMATION SHOWN IN THIS SPECIFICATION WILL MEET YOUR

REQUIREMENTS. FURTHERMORE, SONY DOES NOT WARRANT OR MAKE ANY

REPRESENTATIONS REGARDING THE USE OR THE RESULTS OF THE USE OF THE

TECHNICAL INFORMATION SHOWN IN THIS SPECIFICATION IN TERMS OF ITS

CORRECTNESS, ACCURACY, RELIABILITY, CONNECTIVITY OR OTHERWISE. NO ORAL

OR WRITTEN INFORMATION OR ADVICE GIVEN BY SONY OR A SONY AUTHORIZED

REPRESENTATIVE OR SALES REPRESENTATIVE SHALL CREATE A WARRANTY OR IN

ANY WAY INCREASE THE SCOPE OF THIS WARRANTY.

No License Implied

The technical information shown in this specification is for your reference purposes only. The

availability of this specification shall not be construed as giving any indication that Sony and its

licensors will license any intellectual property rights in such information by any implication or

otherwise.

Governing Law

This Notice shall be governed by and construed in accordance with the laws of Japan, without

reference to principles of conflict of laws or choice of laws. All controversies and disputes arising

out of or relating to this Notice shall be submitted to the exclusive jurisdiction of the Tokyo District

Court in Japan as the court of first instance.

Other Applicable Terms and Conditions

The terms and conditions set forth in the Sony specifications, which will be made available to you

when you order the Products, shall apply to your use of the Products instead of this specification.

You should review those terms and conditions when you consider purchasing and/or using the

Products.

2/74

Sony Confidential

�

Sony Corporation

Copyrights

The entire contents of this document are copyrighted by Sony.

SLVS-EC Specification

3/74

Sony Confidential

�

Sony Corporation

CONTENTS

SLVS-EC Specification

1. Overview ...................................................................................................................................... 8

1.1.

1.2.

Scope ..................................................................................................................................... 8

Purpose .................................................................................................................................. 8

2. Reference Documents ................................................................................................................. 9

3. Definitions, acronyms, and abbreviations ................................................................................. 9

3.1. Definitions ............................................................................................................................ 9

3.2. Acronyms and abbreviations ................................................................................................. 9

4. Architecture ............................................................................................................................... 10

4.2.

4.1.

System Topology ................................................................................................................. 10

4.1.1.

Basic Topology ........................................................................................................... 10

4.1.2. Multiple I/F Topology ................................................................................................. 11

4.1.3. Multiple CIS Topology ............................................................................................... 12

Frame Synchronization Scheme .......................................................................................... 13

DSP Master with shared clock .................................................................................... 13

DSP Master without shared clock ............................................................................... 13

CIS Master with shared clock ..................................................................................... 14

CIS Master without shared clock ................................................................................ 15

4.3. Hierarchical Structure ......................................................................................................... 16

Application Layer ....................................................................................................... 17

LINK Layer ................................................................................................................. 17

PHY Layer .................................................................................................................. 17

4.2.1.

4.2.2.

4.2.3.

4.2.4.

4.3.1.

4.3.2.

4.3.3.

5. Application Layer Protocol Interface ...................................................................................... 18

5.1. RAW Pixel Data Format ..................................................................................................... 18

5.2. Embedded Data Transfer ..................................................................................................... 18

Frame Format ...................................................................................................................... 19

5.3.

Single Stream Frame Format ...................................................................................... 19

5.3.1.

Initialization ................................................................................................................ 20

5.3.2.

5.3.3.

Standby ....................................................................................................................... 21

5.3.4. Mode Change .............................................................................................................. 22

5.3.5. Mode Change with Standby ........................................................................................ 25

Interrupt....................................................................................................................... 26

5.3.6.

5.4. Attribute and Configuration Register .................................................................................. 27

5.5. Multiple Stream Transfer .................................................................................................... 28

Frame Format of Multiple Stream Transfer ................................................................ 29

5.5.1.

6. LINK Layer Specification ........................................................................................................ 30

6.1.

6.2.

6.3.

6.2.1.

6.1.1.

Pixel to Byte Format Converter .......................................................................................... 30

Payload Data Format ................................................................................................... 34

Payload Data Error Correction ............................................................................................ 36

Payload Data Format with ECC .................................................................................. 37

Packetize ............................................................................................................................. 38

Packet Format ............................................................................................................. 38

Format and Protocol Error Handling ........................................................................... 40

6.4. Lane Management ............................................................................................................... 41

Lane Distribution ........................................................................................................ 42

Lane Distribution with Payload ECC .......................................................................... 43

6.5. LINK Protocol Management ............................................................................................... 44

6.4.1.

6.4.2.

6.3.1.

6.3.2.

4/74

Sony Confidential

�

Sony Corporation

SLVS-EC Specification

6.5.1.

6.5.2.

6.5.3.

Packet Header Generation ........................................................................................... 44

Packet Footer Generation ............................................................................................ 46

Protocol Management FSM ........................................................................................ 48

7. PHY Layer Specification .......................................................................................................... 51

7.1.

7.1.1.

7.1.2.

7.1.3.

7.1.4.

7.1.5.

PHY Protocol Management ................................................................................................ 51

Protocol Management FSM ........................................................................................ 51

Training Sequence ....................................................................................................... 52

Packet Data Transfer Sequence ................................................................................... 53

Standby Sequence ....................................................................................................... 53

PHY Control Code ...................................................................................................... 54

7.2. Bandwidth Control .............................................................................................................. 54

7.3. Lane Skew Control ............................................................................................................. 56

7.4.

Symbol Encoding ................................................................................................................ 57

7.5. Bit Ordering in Symbol Data .............................................................................................. 59

7.6.

Symbol Alignment .............................................................................................................. 60

7.7. Baud Rate Scheme .............................................................................................................. 60

8. Electrical Characteristics ......................................................................................................... 61

8.1. TX Characteristics .............................................................................................................. 61

8.2. RX Characteristics .............................................................................................................. 62

8.3. Common Characteristics ..................................................................................................... 63

8.4.

Interconnect Characteristics ................................................................................................ 64

Annex A. RX Analog Functional Specification ............................................................................... 65

Annex B. Implementation of Multiple Stream Transfer (Informative) ........................................ 70

Annex C. Frame format depending on CIS implementation ........................................................ 72

Annex D. RX Protocol Management FSM (Informative) .............................................................. 73

FIGURES

Figure 1 Basic Topology .................................................................................................................. 10

Figure 2 Multiple I/F Topology ....................................................................................................... 11

Figure 3 Multiple CIS Topology ...................................................................................................... 12

Figure 4 DSP Master with shared clock ........................................................................................... 13

Figure 5 DSP Master without shared clock ...................................................................................... 14

Figure 6 CIS Master with shared clock ............................................................................................ 15

Figure 7 CIS Master without shared clock ....................................................................................... 15

Figure 8 SLVS-EC Hierarchical Structure ....................................................................................... 16

Figure 9 Example of Single Stream Frame Format.......................................................................... 19

Figure 10 Example Frame Format and Control Sequence for Initialization .................................... 20

Figure 11 Example Frame Format and Control Sequence for Standby ............................................ 21

Figure 12 Example Frame Format and Control Sequence for Mode Change .................................. 22

Figure 13 Example Sequence of Lane Num Change (1 to 4)........................................................... 23

5/74

Sony Confidential

�

Sony Corporation

SLVS-EC Specification

Figure 14 Example Sequence of Lane Num Change (4 to 2)........................................................... 24

Figure 15 Example Sequence of Mode Change with Standby ......................................................... 25

Figure 16 Example Frame Format and Control Sequence for Interrupt .......................................... 26

Figure 17 Example of Multiple Stream Transfer by Multiple I/F .................................................... 28

Figure 18 Example Frame Format of Multiple Stream Transfer ...................................................... 29

Figure 19 Payload data format (left: RAW10, right: RAW12) ........................................................ 35

Figure 20 Payload Data Format with ECC Option = 1 .................................................................... 37

Figure 21 Packet Format (left: CRC Option=OFF, right: CRC Option=ON) .................................. 38

Figure 22 Packet Format with Payload Data ECC ........................................................................... 39

Figure 23 Lane-Distributed Packet Data Format ............................................................................. 42

Figure 24 Lane-Distributed Packet Data Format with Payload ECC ............................................... 43

Figure 25 Data Structure of Packet Header ...................................................................................... 44

Figure 26 Example Implementation of CRC16 (Informative) ......................................................... 45

Figure 27 CRC32 Calculation and Insertion .................................................................................... 46

Figure 28 TX Protocol Management Signaling Interface ................................................................ 48

Figure 29 FSM for TX LINK Layer Protocol .................................................................................. 49

Figure 30 FSM for TX PHY Layer Protocol .................................................................................... 51

Figure 31 Detailed Definition of Training Sequence ....................................................................... 53

Figure 32 Detailed Definition of Packet Data Transfer Sequence ................................................... 53

Figure 33 Detailed Definition of Standby Sequence ........................................................................ 53

Figure 34 CIS and PHY Bandwidth Definition (Informative) ......................................................... 55

Figure 35 Pad Code Insertion for Bandwidth Adjustment ............................................................... 55

Figure 36 Lane Skew Control by Deskew Code .............................................................................. 56

Figure 37 Bit Ordering in Symbol Data ........................................................................................... 59

Figure 38 Definition of TX characteristics ...................................................................................... 61

Figure 39 Definitions of TX DC parameters .................................................................................... 61

Figure 40 Definitions of TX AC parameters .................................................................................... 61

Figure 41 Definition of RX characteristics ...................................................................................... 62

Figure 42 Definitions of RX AC parameters ................................................................................... 62

Figure 43 A template of a differential insertion loss ........................................................................ 64

Figure 44 Example of SLVS-EC RX block diagram ....................................................................... 65

Figure 45 Standard functional block diagram of RX Analog ........................................................... 66

Figure 46 Bit ordering in RX Analog............................................................................................... 68

Figure 47 Example of RX Analog timing diagram .......................................................................... 69

Figure 48 Definition of Lane Skew in RX Analog .......................................................................... 69

Figure 49 Example of Customized Block Diagram of Multiple I/F Topology ................................ 70

Figure 50 Example of Frame Format (Frame Start=1 @ Line Number=3) ..................................... 72

Figure 51 Example of Frame Format (Frame Start=1 @ EBD line) ................................................ 72

Figure 52 RX Protocol Management Signaling Interface ................................................................ 73

Figure 53 FSM for RX LINK Layer Protocol .................................................................................. 73

Figure 54 FSM for RX PHY Layer Protocol ................................................................................... 74

6/74

Sony Confidential

�

Sony Corporation

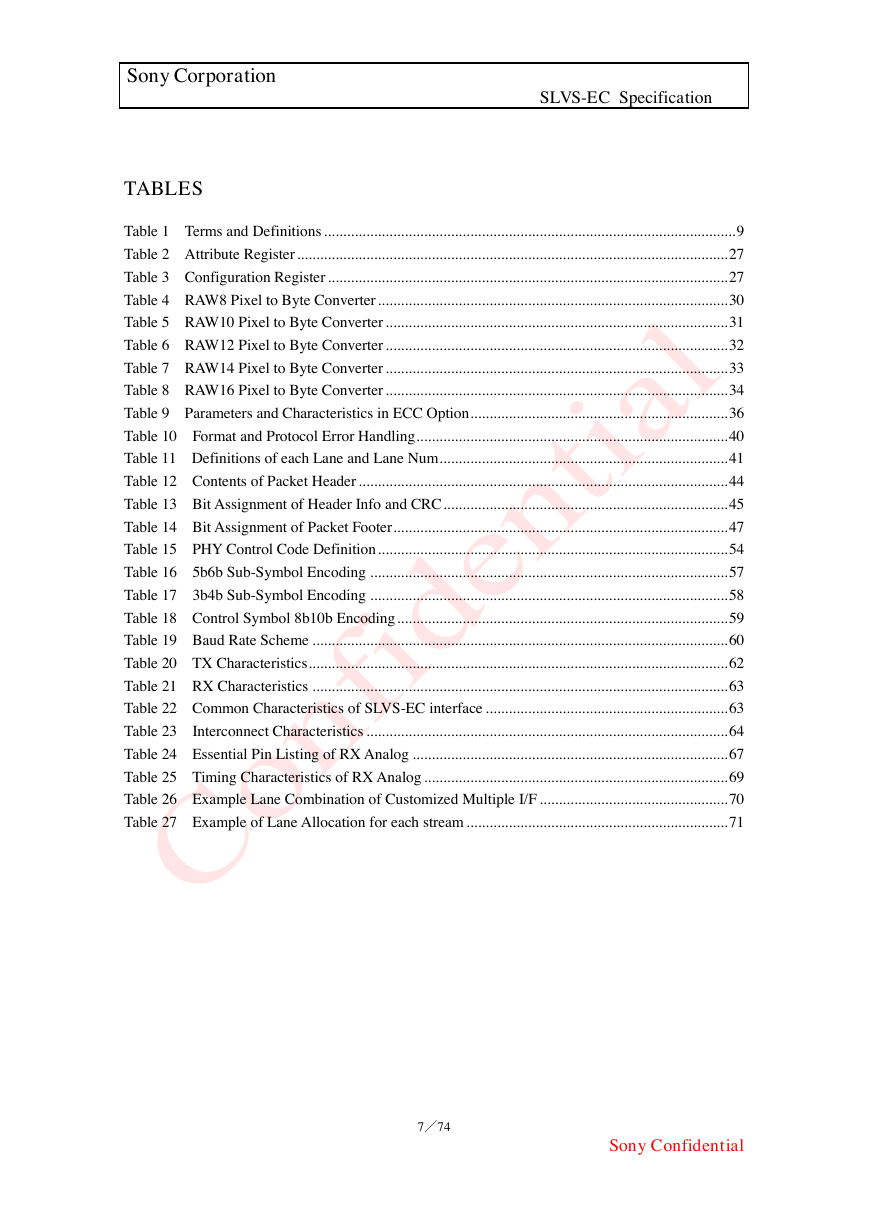

TABLES

SLVS-EC Specification

Table 1 Terms and Definitions ........................................................................................................... 9

Table 2 Attribute Register ................................................................................................................ 27

Table 3 Configuration Register ........................................................................................................ 27

Table 4 RAW8 Pixel to Byte Converter ........................................................................................... 30

Table 5 RAW10 Pixel to Byte Converter ......................................................................................... 31

Table 6 RAW12 Pixel to Byte Converter ......................................................................................... 32

Table 7 RAW14 Pixel to Byte Converter ......................................................................................... 33

Table 8 RAW16 Pixel to Byte Converter ......................................................................................... 34

Table 9 Parameters and Characteristics in ECC Option ................................................................... 36

Table 10 Format and Protocol Error Handling ................................................................................. 40

Table 11 Definitions of each Lane and Lane Num ........................................................................... 41

Table 12 Contents of Packet Header ................................................................................................ 44

Table 13 Bit Assignment of Header Info and CRC .......................................................................... 45

Table 14 Bit Assignment of Packet Footer ....................................................................................... 47

Table 15 PHY Control Code Definition ........................................................................................... 54

Table 16 5b6b Sub-Symbol Encoding ............................................................................................. 57

Table 17 3b4b Sub-Symbol Encoding ............................................................................................. 58

Table 18 Control Symbol 8b10b Encoding ...................................................................................... 59

Table 19 Baud Rate Scheme ............................................................................................................ 60

Table 20 TX Characteristics ............................................................................................................. 62

Table 21 RX Characteristics ............................................................................................................ 63

Table 22 Common Characteristics of SLVS-EC interface ............................................................... 63

Table 23 Interconnect Characteristics .............................................................................................. 64

Table 24 Essential Pin Listing of RX Analog .................................................................................. 67

Table 25 Timing Characteristics of RX Analog ............................................................................... 69

Table 26 Example Lane Combination of Customized Multiple I/F ................................................. 70

Table 27 Example of Lane Allocation for each stream .................................................................... 71

7/74

Sony Confidential

�

Sony Corporation

1. Overview

SLVS-EC Specification

This specification describes the high-speed serial interface technology in order to configure a camera

system using a high-speed and a high-definition Sony CMOS Image Sensor (CIS).

This interface realizes wideband pixel data transfer at a high frame rate between a CIS and a DSP

(digital signal processor). As such, it introduces an optimized packet data format and control

protocol with little redundancy, and a simple architecture consisting of just two layers: a LINK Layer

that enables format processing of wideband data using parallel architecture, and a PHY Layer that

can provide high-speed data transfer with low power consumption.

A Scalable FEC (Forward Error Correction) function is also introduced as the control protocol for

data transfer errors that are a major overhead factor in high-speed serial interfaces. This realizes

highly reliable data transfer with minimized redundancy and low latency according to the

application.

In addition, the optimally budgeted electrical characteristics of a transmitter and receiver are

specified as an interface between a CIS that utilizes semiconductor devices focused on an

enhancement of imaging characteristics and a DSP manufactured using the latest semiconductor

process technology with high-frequency characteristics. This enables to achieve high performance

with a high-speed, low power, small area PHY circuit.

1.1. Scope

This specification prescribes the data transfer interface specifications between a CIS and DSP.

In this specification, the necessary items to secure connectivity between the transmission and

reception sides are specified. These items mainly include the formats of the transferred packets and

data, the protocols and sequences used to control each function, and the definitions, restrictions and

other conditions needed to describe these items.

In addition, the electrical characteristics of the transmitter and receiver, characteristics of

recommended interconnect and external components are also specified for the PHY Layer.

Furthermore, the required definitions, restrictions and other conditions are specified for the interface

with the Application Layer, and system configurations integrated with this high-speed interface and

other information are also noted as reference information.

However, the specifications within the Application Layer, the transmission and reception circuit

implementations, and the specifications for interfaces other than between the CIS and DSP are not

included within the scope of this specification.

1.2. Purpose

The specification prescribed by this document can be used to develop wider band interfaces with

higher power efficiency to meet demands for even higher numbers of pixels and faster imaging

characteristics in the camera market, for applications such as color video cameras, digital still

cameras, and single lens reflex cameras.

The interface that conforms to this specification can be used to develop DSP that secure connectivity

with Sony’s high-speed, high definition CIS, and also to develop CIS that can be connected with

these DSP.

8/74

Sony Confidential

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc