V3V3V3V3硬件设计指南

硬件设计指南

硬件设计指南

硬件设计指南

Copyright

Allwinner Technology, All rights reserved

Copyright

Allwinner Technology, All rights reserved

Copyright ©©©© Allwinner Technology, All rights reserved

Copyright

Allwinner Technology, All rights reserved

1

�

目录

PART 1: Schematic Design guide

PART 2: PCB Layout guide

Copyright

Allwinner Technology, All rights reserved

Copyright

Allwinner Technology, All rights reserved

Copyright ©©©© Allwinner Technology, All rights reserved

Copyright

Allwinner Technology, All rights reserved

2

�

目录

PART 1: Schematic Design guide

PART 2: PCB Layout guide

Copyright

Allwinner Technology, All rights reserved

Copyright

Allwinner Technology, All rights reserved

Copyright ©©©© Allwinner Technology, All rights reserved

Copyright

Allwinner Technology, All rights reserved

3

�

PART 1: Schematic Design guide

� 1. CPU

� 2. POWER

� 3. DRAM

� 4. SPI NAND/NOR

� 5. KEY

� 6. CAMERA

� 7. AUDIO

� 8. USB

� 9. CARD

� 10. WIFI

� 11. ESD

Copyright

Allwinner Technology, All rights reserved

Copyright

Allwinner Technology, All rights reserved

Copyright ©©©© Allwinner Technology, All rights reserved

Copyright

Allwinner Technology, All rights reserved

4

�

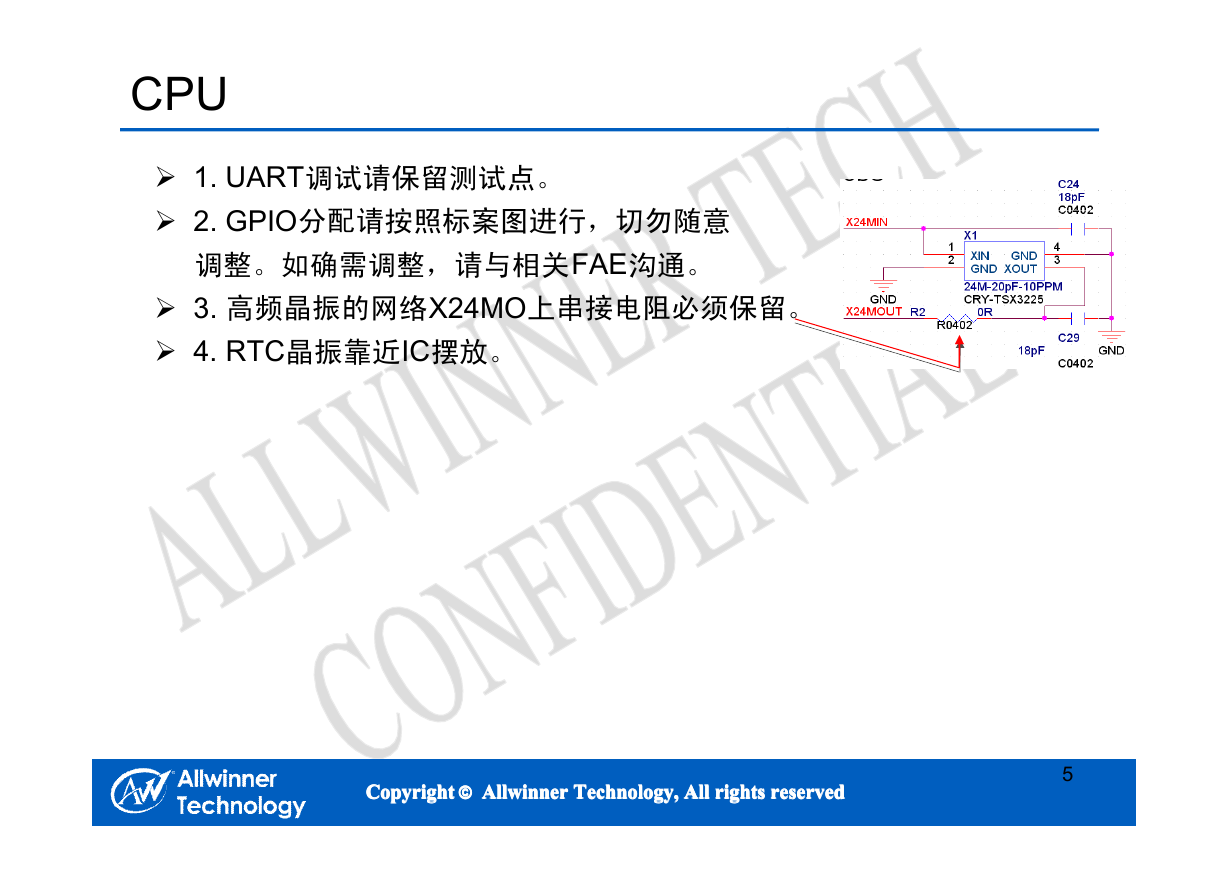

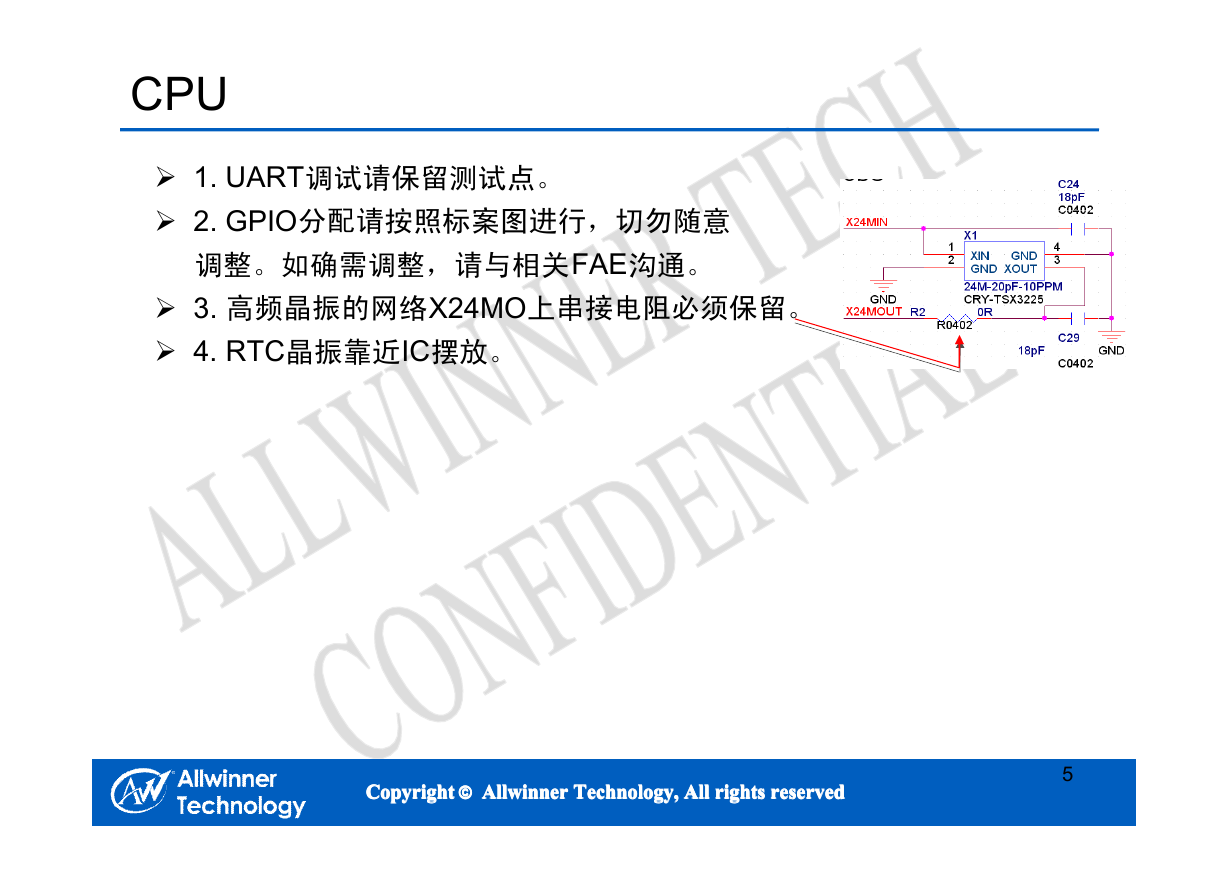

CPU

� 1. UART调试请保留测试点。

� 2. GPIO分配请按照标案图进行,切勿随意

调整。如确需调整,请与相关FAE沟通。

� 3. 高频晶振的网络X24MO上串接电阻必须保留。

� 4. RTC晶振靠近IC摆放。

Copyright

Allwinner Technology, All rights reserved

Copyright

Allwinner Technology, All rights reserved

Copyright ©©©© Allwinner Technology, All rights reserved

Copyright

Allwinner Technology, All rights reserved

5

�

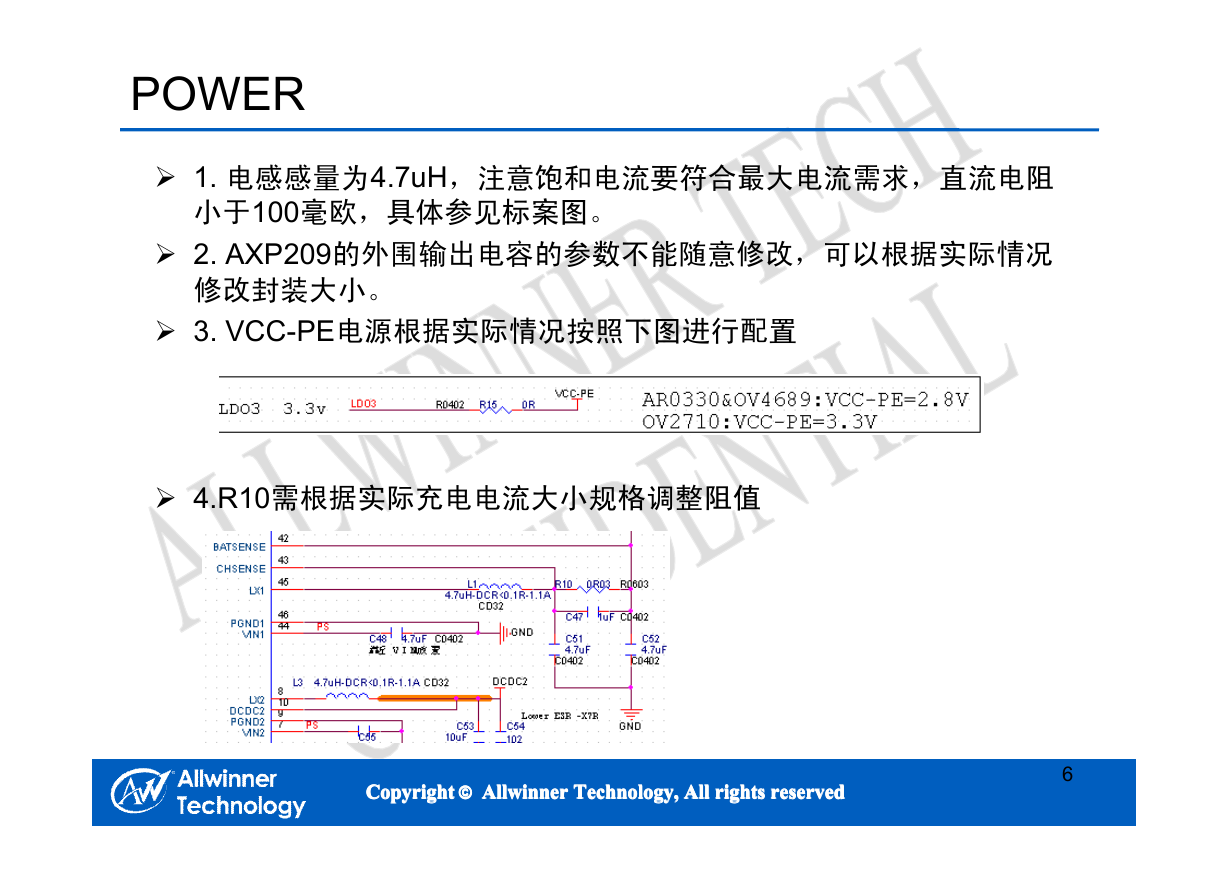

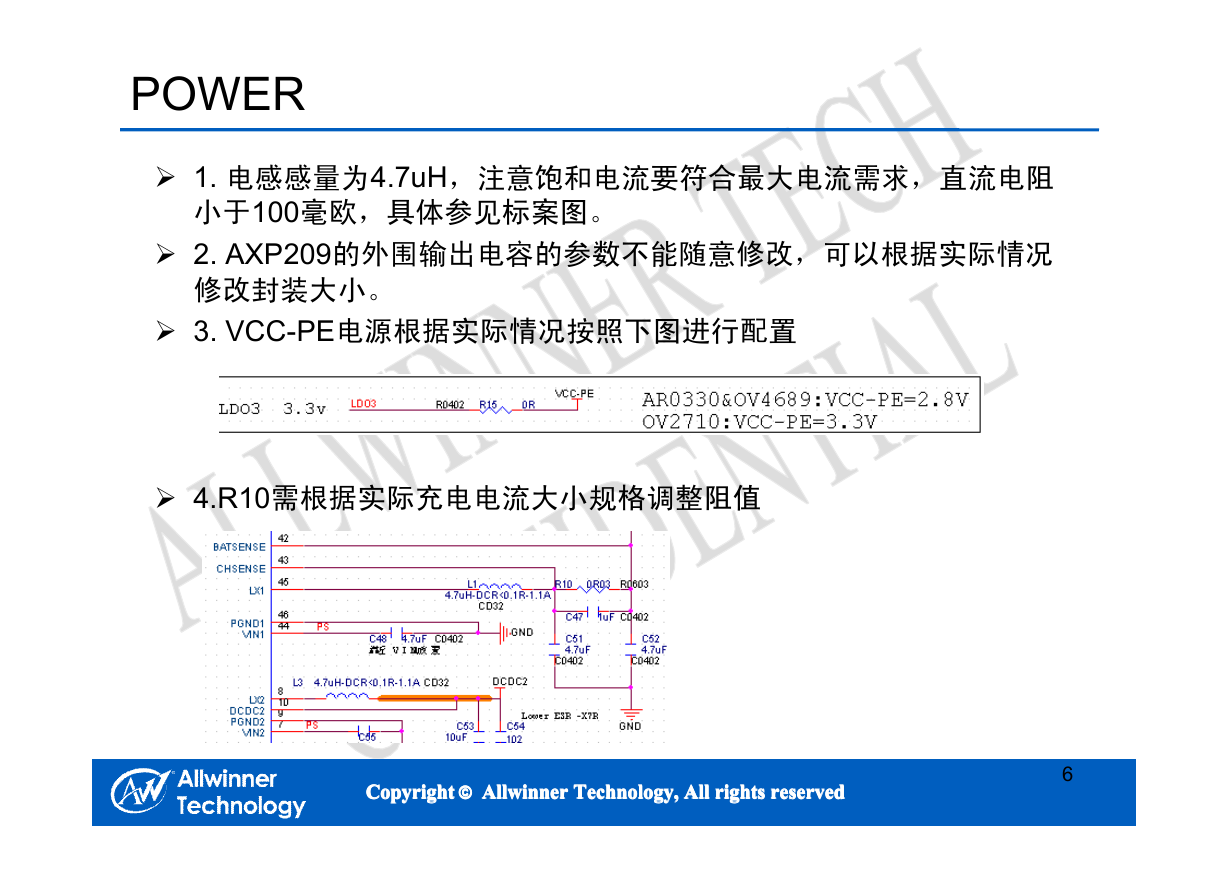

POWER

� 1. 电感感量为4.7uH,注意饱和电流要符合最大电流需求,直流电阻

小于100毫欧,具体参见标案图。

� 2. AXP209的外围输出电容的参数不能随意修改,可以根据实际情况

修改封装大小。

� 3. VCC-PE电源根据实际情况按照下图进行配置

� 4.R10需根据实际充电电流大小规格调整阻值

Copyright

Allwinner Technology, All rights reserved

Copyright

Allwinner Technology, All rights reserved

Copyright ©©©© Allwinner Technology, All rights reserved

Copyright

Allwinner Technology, All rights reserved

6

�

DRAM

� 1. V3支持DDR3/3L,使用时需先确定DRAM的类型,以及单片的位

宽,参考标案原理图连接

� 2. 主控和DRAM端每一个ZQ PIN都必须接240R-1%精度的下拉到地

电阻.

� 3. SDQ0-SDQ7,SDQ8-SDQ15,分别为2组数据线,若用

DDR3/3L,则可以进行组内或者组间交换,若进行组间交换,则相应

的SDQM和SDQS差分对也必须对应交换.

Copyright

Allwinner Technology, All rights reserved

Copyright

Allwinner Technology, All rights reserved

Copyright ©©©© Allwinner Technology, All rights reserved

Copyright

Allwinner Technology, All rights reserved

7

�

SPI NAND/NOR

� V3支持SPI NAND/NOR FLASH

Copyright

Allwinner Technology, All rights reserved

Copyright

Allwinner Technology, All rights reserved

Copyright ©©©© Allwinner Technology, All rights reserved

Copyright

Allwinner Technology, All rights reserved

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc