Candence

NC-Verilog

simulator tutorial

第一章 介绍

这个手册将向你介绍使用 NC-Verilog simulator 和 SimVision。

本文使用的是一个用 Veilog 硬件编程语言编写的一个饮料分配机,通过这个例

子你将学会:

·编译 Verilog 源文件,描述设计,在 NC-Launch(用于管理你的大型设计

的图形交互接口)上进行设计的仿真。NCLaunch 帮助你配置和启动编译器,描

述器和仿真器。当然你还可以在 NCLaunch 上运行像 SDF compiler,HDL Analysis

and Lint, Code Coverage Analyzer, NCBrowse, and Comparescan.之类的工具。

·在 SimVision 分析环境下进行对设计中的问题的调试。

SimVision 是一个 candence 仿真器统一的图形化的调试环境。

SimVision 可以用于调试用 verilog,vhdl,SystemC 或者它们混合写成的

数字,仿真,或数模混合电路的设计。

你可以在以下几种模式运行 SimVision:

·Simulate 模式

在 Simulate 模式下你可以实时的看到仿真的数据。也就是说,你可以

在仿真仿真的过程中就进行数据的分析。你可以通过对设计设置断点和分

步来达到控制仿真的。

为了帮助你追踪整个仿真过程,SimVision 提供了几个工具:

·控制台窗口 Console Window

·源浏览器

Source Browser

·设计浏览器 Design Browser

·循环阅读器 Cycle Viewer

·原理图追踪

·信号流浏览器 Signal Flow Browser

Waveform Window

·波形窗口

·寄存器窗口 Register Window

Schematic Tracer

这些窗口之间是连接了的,所以如果你在一个窗口中选中了一个对象,

那么在其它窗口中也会被选中。

·Post-processing environment (PPE)模式

在 PPE 模式下,对仿真结果数据的分析是在仿真过程结束了后进行的。

除了仿真器之外,你能访问所有的 SimVision 的工具。就像 Simulator 模

式中一样,这里所有的窗口也是连接了的,你在一个窗口中选择了的目标

也会在其它窗口中选中。要在 PPE 模式下运行,你必须先对设计进行仿真,

然后把仿真的资料存到一个文件中,你可以随时从 simulation 模式切换到

PPE 模式,但是不能在 PPE 模式切换到 simulation 模式中去。

本指南将向你介绍 SimVision 的主要几个工具:

控制台 Console window:

Console window 允许你输入 tcl 仿真的命令和 SimVision

的命令。

Design Browser:

Design Browser 让你进入设计的各层,以及信号和变

量的数据库。

�

Register window:

Register window 让你可以使用一个开放式的图形编辑

器来定义一些记录簿,每个都包含了一个自定义的仿真数据

的观点。

Signal Flow Browser:

Signal Flow Browser 让你追踪信号的变化。

Source Browser:

Source Browser 让你可以看到设计的源代码。

Waveform window:

Waveform window 把仿真的资料在 X-Y 坐标系里面描绘

出来。数据通常被显示为值和时间的关系,但是它也可以是

已经记录下了的数据。

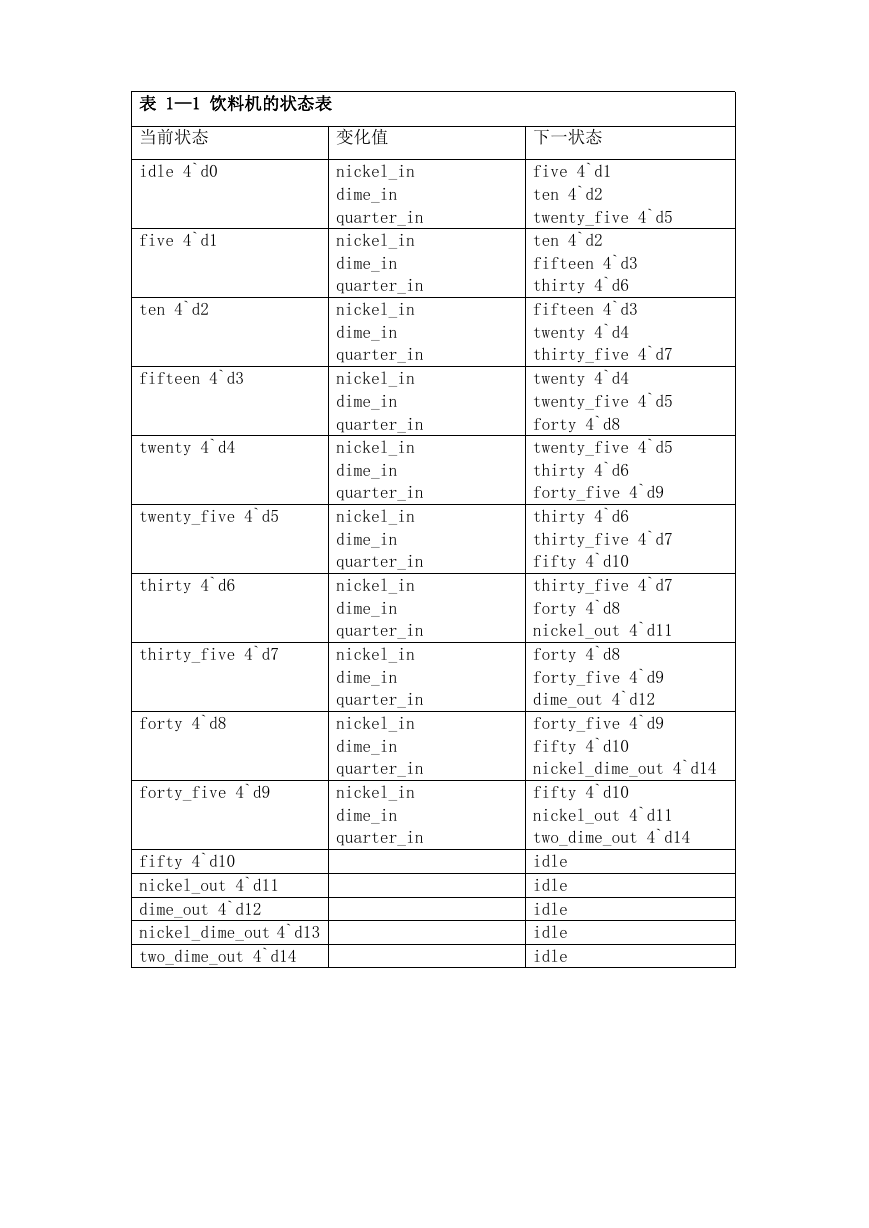

饮料机的例子

饮料机由以下几个模块组成:

Drink-machine:用于计算用户给了的钱,对饮料进行分发,并且给用户找

钱。

Coin-counter:用硬币和机器相连,并且确定机器什么时候没有找头了。

Can-counter:用饮料和机器相连,并且确定机器什么时候没有饮料了。

这个例子同样有一个测试模块,它用于初始化饮料机并且用 nickel(五美

分),dime(十美分),quarter(二十五美分)的不同组合对机器进行投币来买

饮料。对于接受硬币和分发饮料的行为被建模成一个状态机。用户已经投入的硬

币总量决定了当前的状态。接下来用户投入的硬币的类型决定了下一个状态。举

例来说,当没有钱投入的时候,机器处于空闲状态。当用户投入一个 nickel 的

时候,机器进入下一个状态——five。当当前状态是 five 的时候用户又投入了

一个 quarter,机器就进入了下一个状态——thirty。当用户投入的钱到了五十

美分的时候,机器就分发一罐饮料,同时进入空闲状态。 当用户投入的钱超过

了五十美分的时候,机器分发一罐饮料,找回零钱,然后进入空闲状态。

�

变化值

nickel_in

dime_in

quarter_in

nickel_in

dime_in

quarter_in

nickel_in

dime_in

quarter_in

nickel_in

dime_in

quarter_in

nickel_in

dime_in

quarter_in

nickel_in

dime_in

quarter_in

nickel_in

dime_in

quarter_in

nickel_in

dime_in

quarter_in

nickel_in

dime_in

quarter_in

nickel_in

dime_in

quarter_in

表 1—1 饮料机的状态表

当前状态

idle 4`d0

five 4`d1

ten 4`d2

fifteen 4`d3

twenty 4`d4

twenty_five 4`d5

thirty 4`d6

thirty_five 4`d7

forty 4`d8

forty_five 4`d9

fifty 4`d10

nickel_out 4`d11

dime_out 4`d12

nickel_dime_out 4`d13

two_dime_out 4`d14

下一状态

five 4`d1

ten 4`d2

twenty_five 4`d5

ten 4`d2

fifteen 4`d3

thirty 4`d6

fifteen 4`d3

twenty 4`d4

thirty_five 4`d7

twenty 4`d4

twenty_five 4`d5

forty 4`d8

twenty_five 4`d5

thirty 4`d6

forty_five 4`d9

thirty 4`d6

thirty_five 4`d7

fifty 4`d10

thirty_five 4`d7

forty 4`d8

nickel_out 4`d11

forty 4`d8

forty_five 4`d9

dime_out 4`d12

forty_five 4`d9

fifty 4`d10

nickel_dime_out 4`d14

fifty 4`d10

nickel_out 4`d11

two_dime_out 4`d14

idle

idle

idle

idle

idle

�

更多的信息

SimVision 还提供了其它的没有在这个指南里面用到的工具。

工具/Feature

介绍

Simulation Cycle Debugger

原理描述器显示了用 Verilog 或者 Vhdl 编写的设

计的原理图,可以让你描述在设计中的信号。

在 SimVision 的用户指南里面看 12 章,看一个设

计的示意图。

Simulation Cycle Debugger 让你在一个仿真过程

中,在各个时间点,Delta Cycle,仿真阶段,或者是

时间进行过程中停止。它对于 Verilog-XL 或者 AMS 是

不可用的

看 SimVision 用户指南的 11 章:在 Delta Cycle

层面上进行调试

�

第二章 开始

在你仿真你的设计以前,你必须编译和描述它。编译过程将把源文件中的用

HDL 编写的单元编译成内在的描述。描述设计将在设计的实例化,结构化信息的

基础上建立设计的层次结构,建立信号的连接,计算所有对象的初始值。你编译,

描述和仿真你的设计要用到以下的工具:

描述设计并且生成仿真的 snapshot。

对 snapshot 进行仿真仿真。

Ncvlog: 编译 Verilog 源文件。

ncelab

ncsim

当然你也可以利用 ncverilog 的命令以一步实现(single-step)的模式来

运行 NC-Verilog。你也可以使用单一的工具,NCLaunch——一个可以帮助你建

立大型的设计工程的用户图形接口平台。NCLaunch 帮助你配置和启动仿真的工

具。 你可以在多步实现(multi-step)或者单步实现(single-step)的模式下

运行这些工具。它也可以让你打开 Comparescan, SDF Compiler, HDL Analysis

和 Lint, Code Coverage Analyzer, NCBrowse, 以及其它仿真仿真的工具。这

个指南将向你展示怎么在多步实现(multi-step)的模式下使用 NCLaunch。

拷贝指南的数据

本例的所有源文件包含在 Candence 的安装包中。源文件在下面的这个地址:

install_dir/doc/ncvlogtut/examples

建立一个新的檔夹(比图说:tutorial), 然后拷贝指南的文件到这个檔夹。

例:

mkdir tutorial

cd tutorial

cp install_dir/doc/ncvlogtut/examples/* .

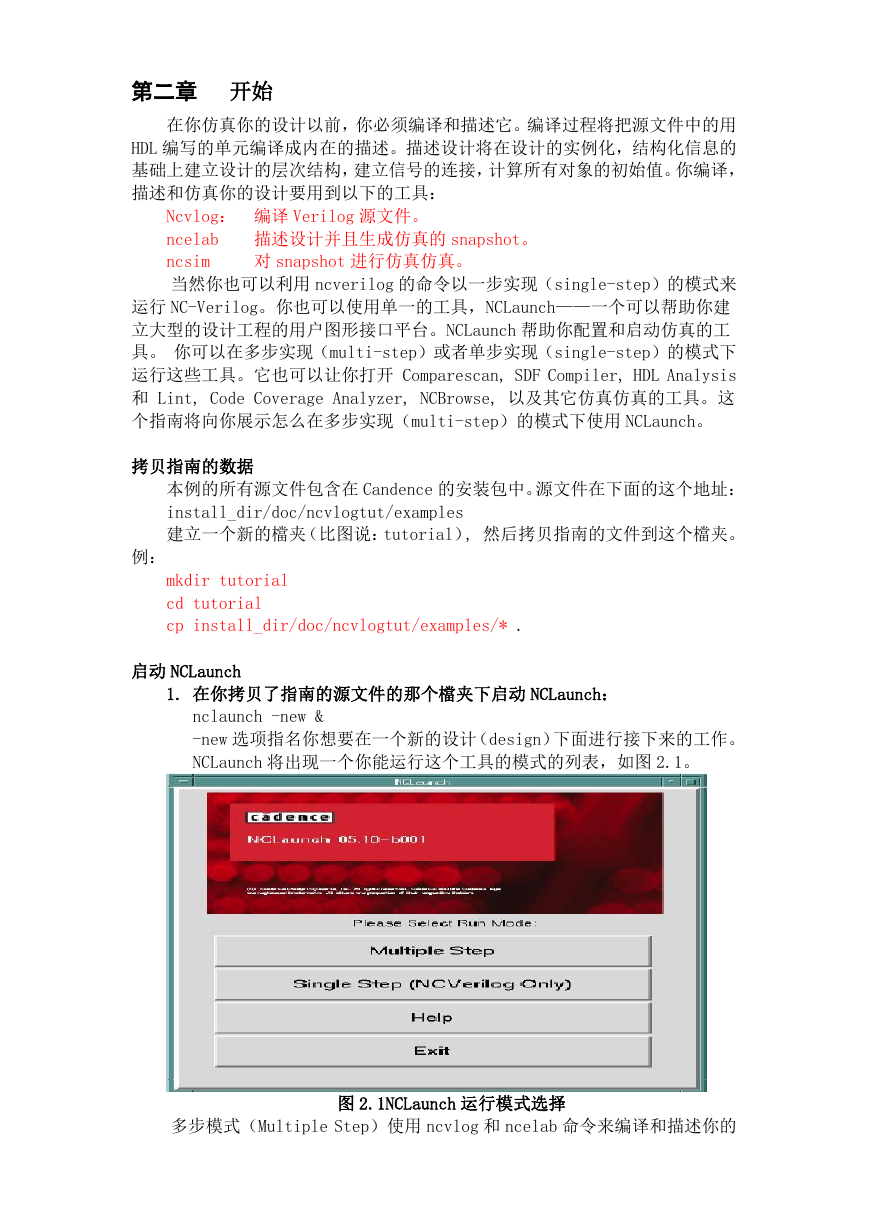

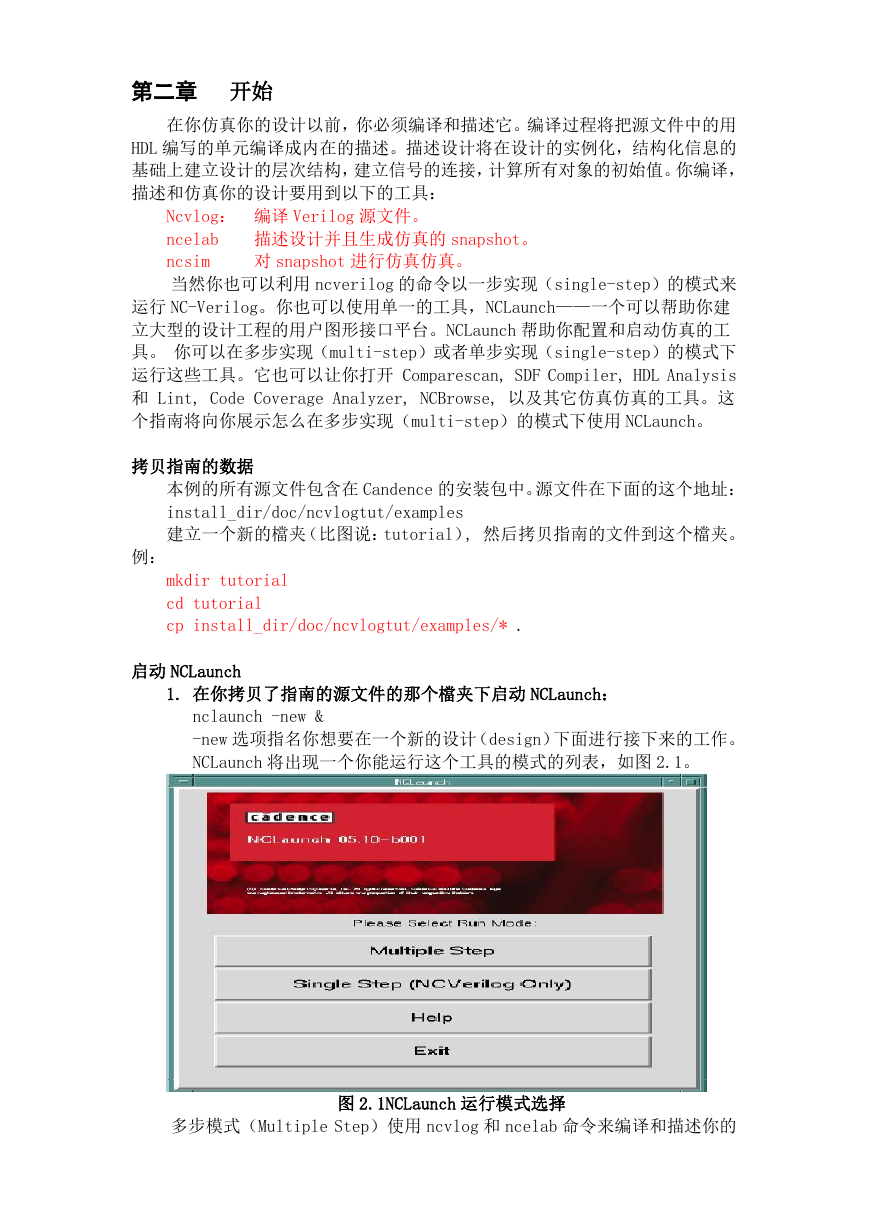

启动 NCLaunch

1. 在你拷贝了指南的源文件的那个檔夹下启动 NCLaunch:

nclaunch -new &

-new 选项指名你想要在一个新的设计(design)下面进行接下来的工作。

NCLaunch 将出现一个你能运行这个工具的模式的列表,如图 2.1。

多步模式(Multiple Step)使用 ncvlog 和 ncelab 命令来编译和描述你的

图 2.1NCLaunch 运行模式选择

�

设计;单步模式(Single Step)使用 ncverilog 命令。

2. 选择 Multiple Step.

NCLaunch 显示的主窗口如图 2.2 :

图 2.2 NCLaunch 主窗口

左边的窗口显示了当前目录下的所有的文件,在你编译和描述了设计以后,

右边窗口就会显示设计的库。上面是菜单和一些用于启动工具的按键。

编译(compiling)源文件

在你仿真仿真你的设计以前,你必须用编译器编译源文件,并且用描述器

(elaborator)把设计描述成 snapshot 的形式。Snapshot 是仿真器将调用的你

的设计的表述,它和其它由 compiler 和 elaborator 产生的中间目标一起保存在

库中。

NCLaunch 的主窗口让你可以连接你编译和描述设计所需要的工具,当然还

有其它的程序。你利用 Tools 和 Utilities 菜单,或者你也可以利用工具栏里面

的工具按钮,你可以打开工具和其它程序。不是所有的工具和程序都放在工具栏

里面,但是你可以通过自己定义工具栏来确定把自己喜欢的工具和程序放在工具

栏里面。

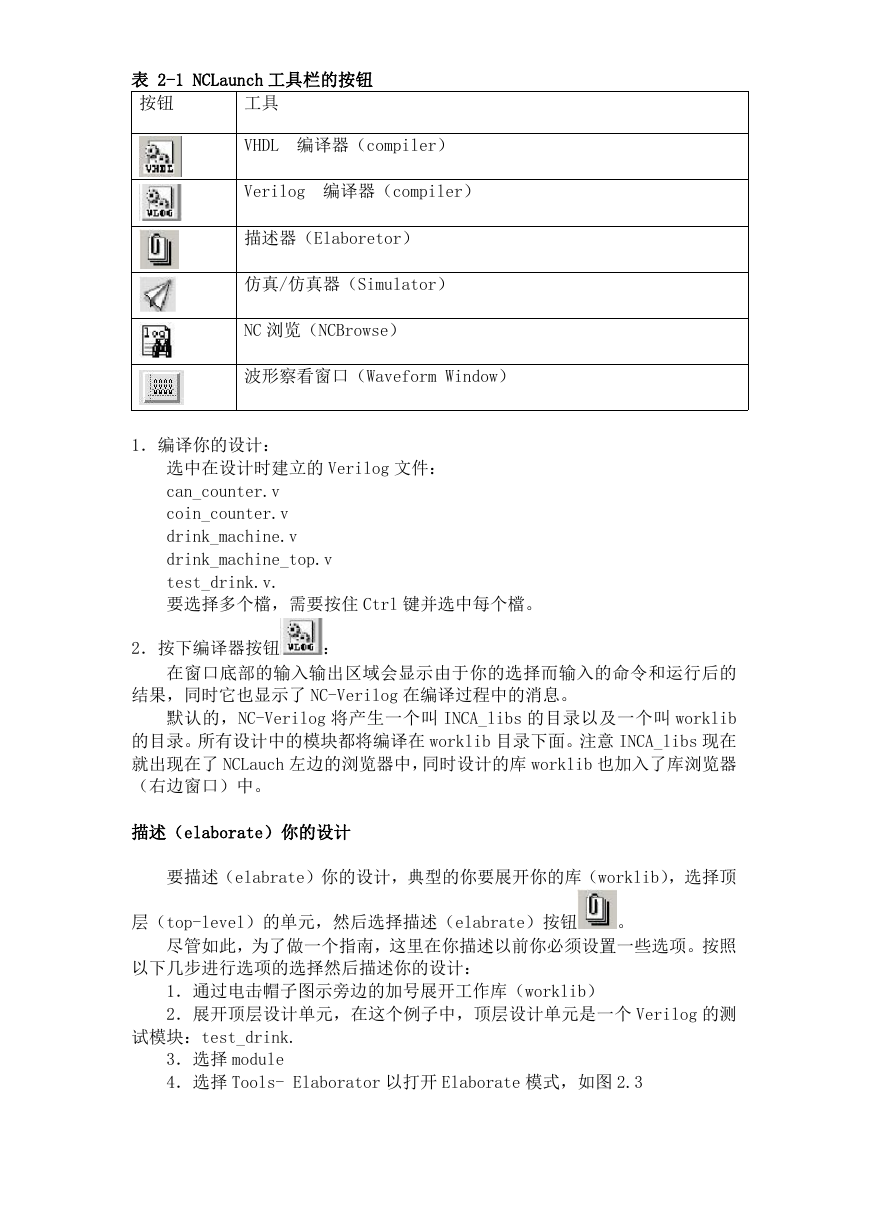

表 2-1 例出了在工具栏里面的工具。

�

表 2-1 NCLaunch 工具栏的按钮

按钮

工具

VHDL 编译器(compiler)

Verilog 编译器(compiler)

描述器(Elaboretor)

仿真/仿真器(Simulator)

NC 浏览(NCBrowse)

波形察看窗口(Waveform Window)

1.编译你的设计:

选中在设计时建立的 Verilog 文件:

can_counter.v

coin_counter.v

drink_machine.v

drink_machine_top.v

test_drink.v.

要选择多个檔,需要按住 Ctrl 键并选中每个檔。

2.按下编译器按钮

:

在窗口底部的输入输出区域会显示由于你的选择而输入的命令和运行后的

结果,同时它也显示了 NC-Verilog 在编译过程中的消息。

默认的,NC-Verilog 将产生一个叫 INCA_libs 的目录以及一个叫 worklib

的目录。所有设计中的模块都将编译在 worklib 目录下面。注意 INCA_libs 现在

就出现在了 NCLauch 左边的浏览器中,同时设计的库 worklib 也加入了库浏览器

(右边窗口)中。

描述(elaborate)你的设计

要描述(elabrate)你的设计,典型的你要展开你的库(worklib),选择顶

层(top-level)的单元,然后选择描述(elabrate)按钮

。

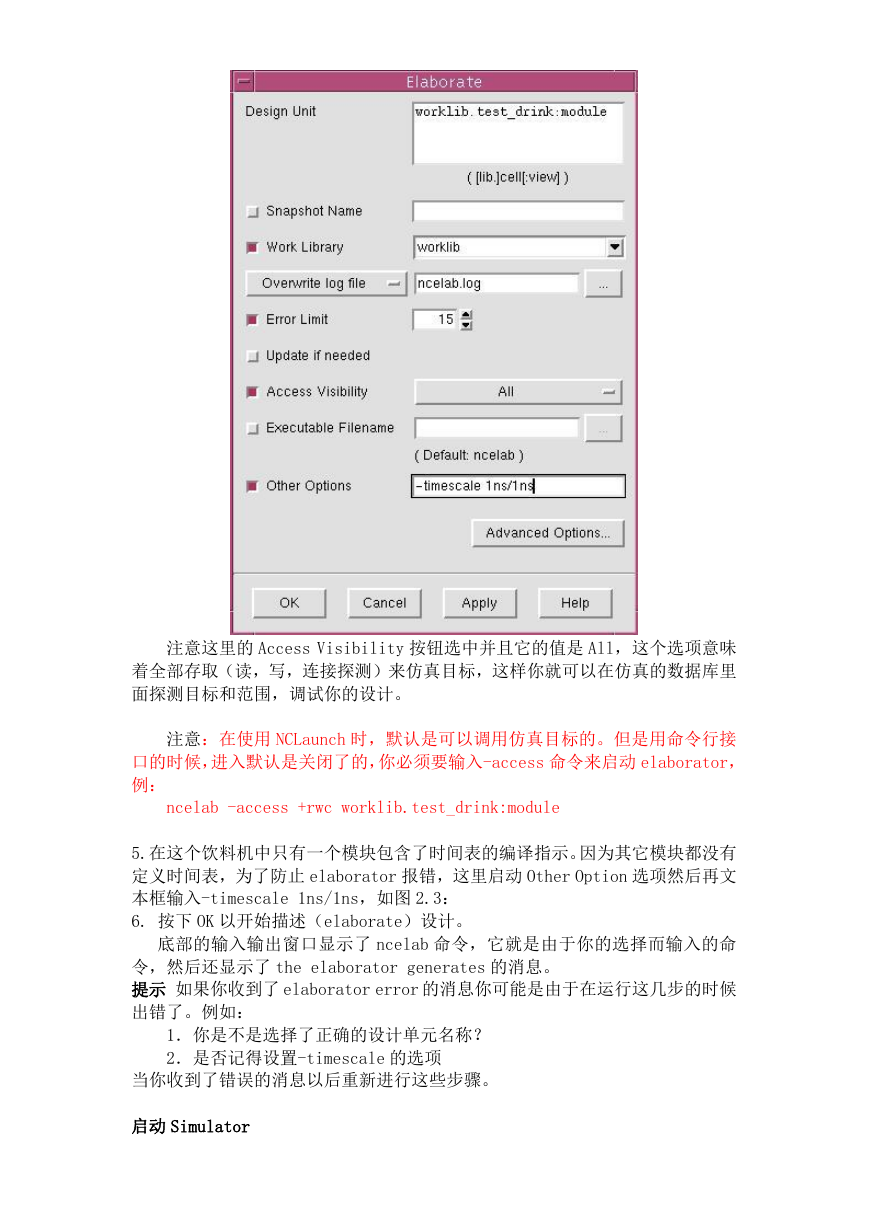

尽管如此,为了做一个指南,这里在你描述以前你必须设置一些选项。按照

以下几步进行选项的选择然后描述你的设计:

1.通过电击帽子图示旁边的加号展开工作库(worklib)

2.展开顶层设计单元,在这个例子中,顶层设计单元是一个 Verilog 的测

试模块:test_drink.

3.选择 module

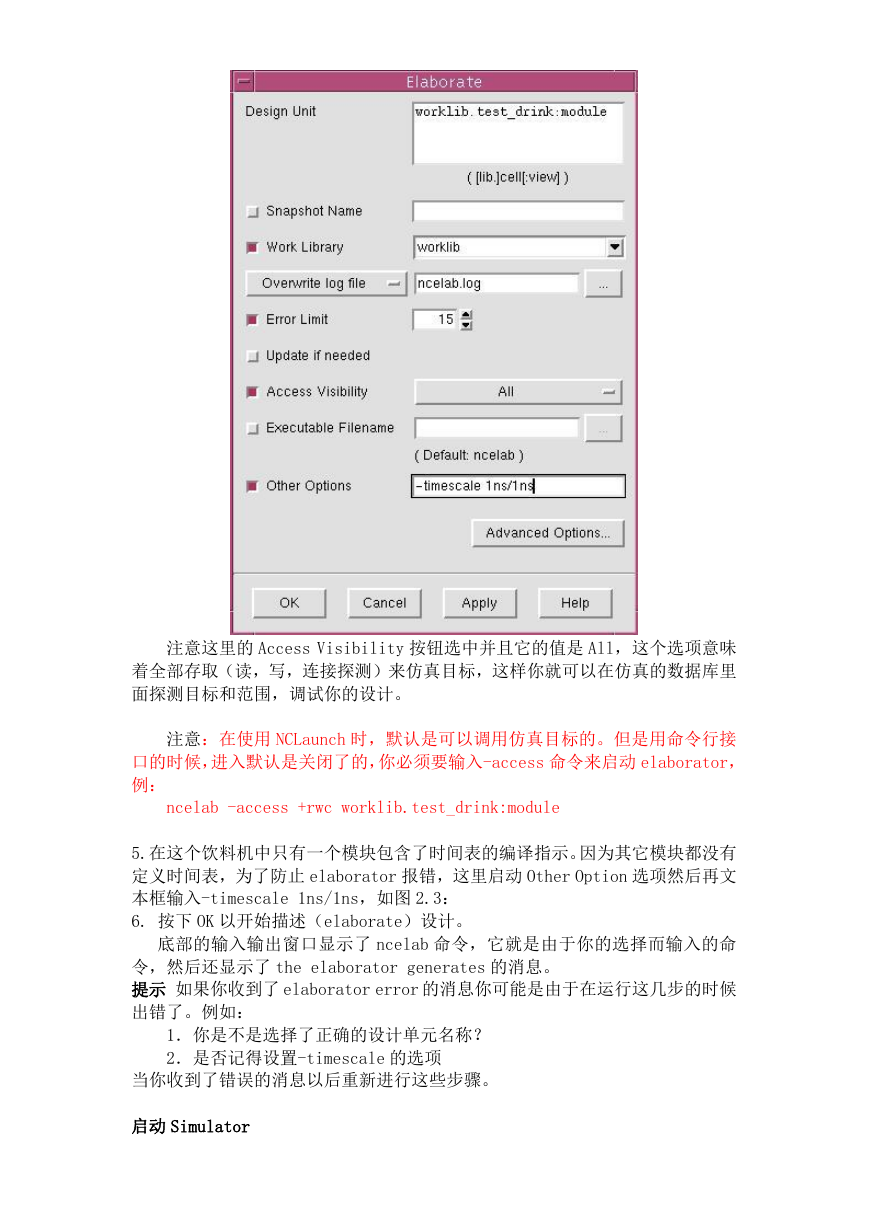

4.选择 Tools- Elaborator 以打开 Elaborate 模式,如图 2.3

�

注意这里的 Access Visibility 按钮选中并且它的值是 All,这个选项意味

着全部存取(读,写,连接探测)来仿真目标,这样你就可以在仿真的数据库里

面探测目标和范围,调试你的设计。

注意:在使用 NCLaunch 时,默认是可以调用仿真目标的。但是用命令行接

口的时候,进入默认是关闭了的,你必须要输入-access 命令来启动 elaborator,

例:

ncelab -access +rwc worklib.test_drink:module

5.在这个饮料机中只有一个模块包含了时间表的编译指示。因为其它模块都没有

定义时间表,为了防止 elaborator 报错,这里启动 Other Option 选项然后再文

本框输入-timescale 1ns/1ns,如图 2.3:

6. 按下 OK 以开始描述(elaborate)设计。

底部的输入输出窗口显示了 ncelab 命令,它就是由于你的选择而输入的命

令,然后还显示了 the elaborator generates 的消息。

提示 如果你收到了 elaborator error 的消息你可能是由于在运行这几步的时候

出错了。例如:

1.你是不是选择了正确的设计单元名称?

2.是否记得设置-timescale 的选项

当你收到了错误的消息以后重新进行这些步骤。

启动 Simulator

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc