内置晶振、I IC 串行接口的高精度实时时钟 IC- SD2403AP Ver1.3

I IC 串行接口的实时时钟 IC V1.3

SD2403AP

1. 概述概述概述概述

SD2403AP 是一种内置晶振、具有标准 IIC 接口的实时时钟芯片,CPU 可使用该接口通过 5 位地址寻址来读

写片内 32 字节寄存器的数据(包括时间寄存器、报警寄存器、控制寄存器、通用 SRAM 寄存器)。

SD2403AP 内置晶振, 该芯片可保证时钟精度为±5ppm(在 25℃±1℃下),即年误差小于 2.5 分钟。

SD2403AP 内置单路定时/报警中断输出,报警中断时间最长可设至 100 年。

SD2403AP 内置时钟精度数字调整功能,可以在很宽的范围内校正时钟的偏差(-189ppm~+189ppm,分辨力为

3.05ppm),并通过外置的温度传感器可设定适应温度变化的调整值,实现在宽温范围内高精度的计时功能。

SD2403AP 具有一个后备电池输入脚 VBAT,当芯片检测到主电源 VDD 掉到后备电池电压以下,芯片会自动转为由

接在 VBAT 的后备电池供电。

2.2.2.2. 特性特性特性特性

� 低功耗: 1.1μA 典型值(VBAT =3.0V,Ta=25℃)。

� 工作电压:1.8~5.5V,工作温度:-40℃~+85℃。

� 标准 IIC 总线接口方式,最高速度 400KHZ(4.5V~5.5V)。

� 年、月、日、星期、时、分、秒的 BCD 码输入/输出,并可通过独立的地址访问各时间寄存器。

� 闰年自动调整功能(从 2000 年~2099 年)。

� 可选择 12/24 小时制式.

� 内置年、月、日、星期、时、分、秒共 7 字节的报警数据寄存器及 1 字节的报警允许寄存器。

� 内置 12 字节通用 SRAM 寄存器可用于存储用户的一般数据。

� 三种中断均可选择从 INT 脚输出,并具有两个中断标志位.

� 可设定并自动重置的单路报警中断功能(时间范围最长设至 100 年),年、月、日、星期、时、分、秒报警

共有 96 种组合方式,并有单事件报警和周期性报警两种中断输出模式.

� 周期性频率中断输出:从 32768Hz~1/16Hz……1 秒共十五种方波脉冲.

� 自动重置的 8 位倒计时定时器,可选的 4 种时钟源(4096HZ、64HZ、1HZ、1/60HZ).

� 内置时钟精度数字调整功能,可通过程序来调整走时的快慢。用户采用外置的温度传感器,设定适应温度

变化的调整值,可实现在宽温范围内高精度的计时功能。

� 具有一个后备电池输入脚 VBAT ,芯片依据不同的电压自动从 VDD 切换到 VBAT 或从 VBAT 切换到 VDD。

� 在 VBAT 模式下,芯片具有中断输出允许或禁止的功能,可满足在备用电池供电时输出中断的需要。

� 内置 IIC 总线 0.5 秒自动复位功能(从 Start 命令开始计时),保证时钟数据的有效性及可靠性,避免 IIC 总

线挂死问题。

� 内置三个时钟数据写保护位, 避免对数据的误写操作,可更好地保护时钟数据。

� 内置 VBAT 模式 IIC 总线通信禁止功能,从而避免在电池供电时 CPU 对时钟操作所消耗的电池电量,也可避

免在主电源上、下电的过程中因 CPU 的 I/O 端口所输出的不受控的杂波信号对时钟芯片的误写操作,进一

步提高时钟芯片的可靠性。

� 内置上电复位电路及指示位。

� 内置电源稳压,内部计时电压可低至 1.5V。

� 芯片管脚抗静电(ESD)>4KV。

� 芯片在兴威帆的评估板上可通过 4KV 的群脉冲(EFT)干扰。

� 内置晶振,出厂前已对时钟进行校准,时钟精度为±5ppm(在 25℃±1℃下),即年误差小于 2.5 分钟。

� 封装形式:8 脚的 DIP 封装, SD2403API 为工业级型号。

1

�

I IC 串行接口的实时时钟 IC V1.3

SD2403AP

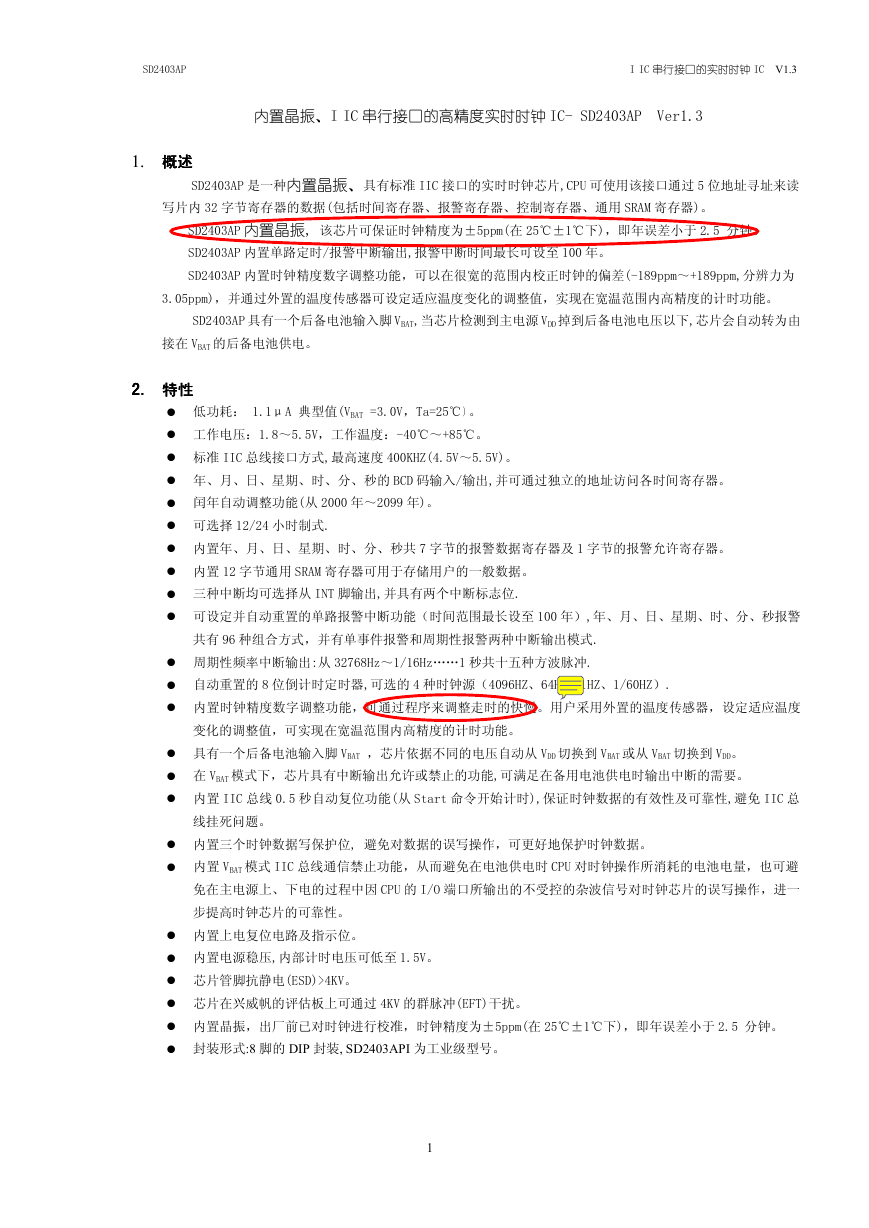

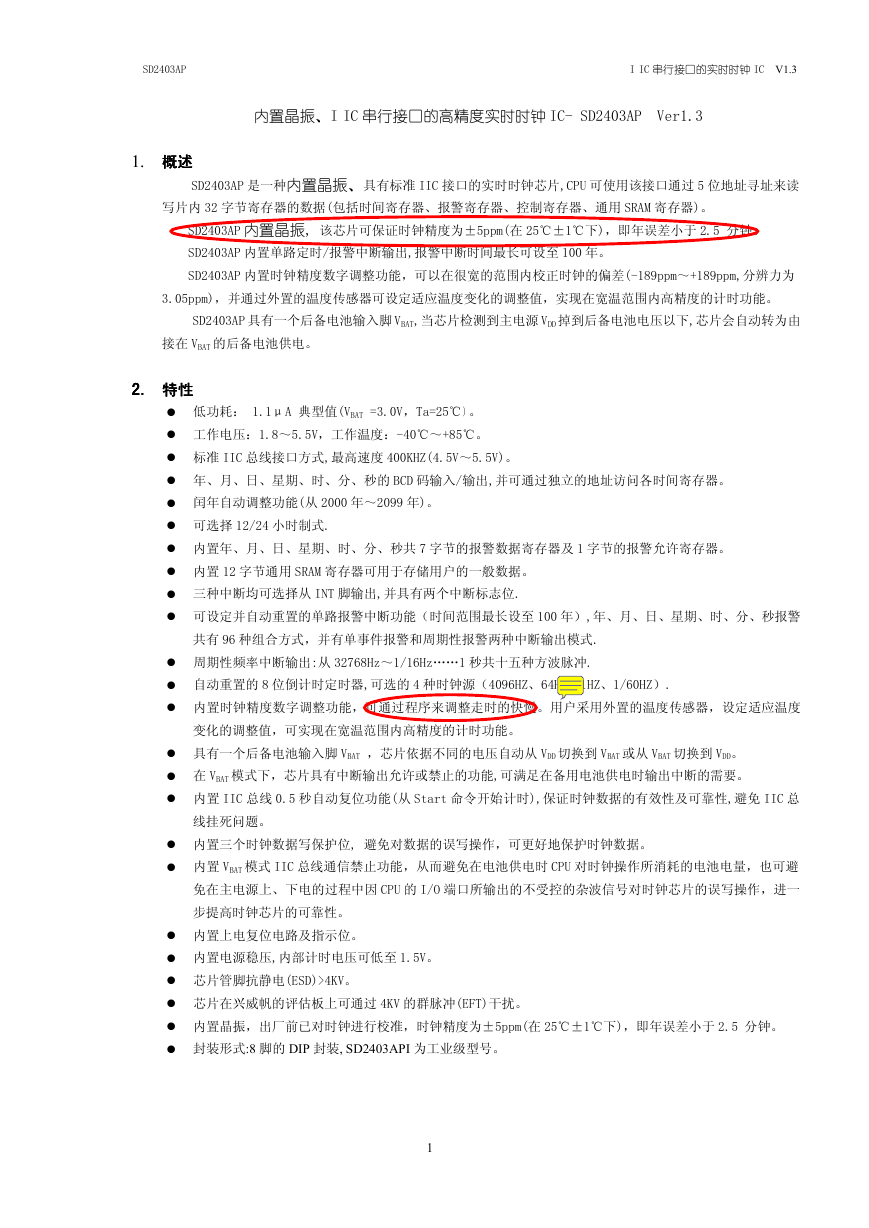

3.3.3.3. 原理框图

原理框图原理框图

原理框图

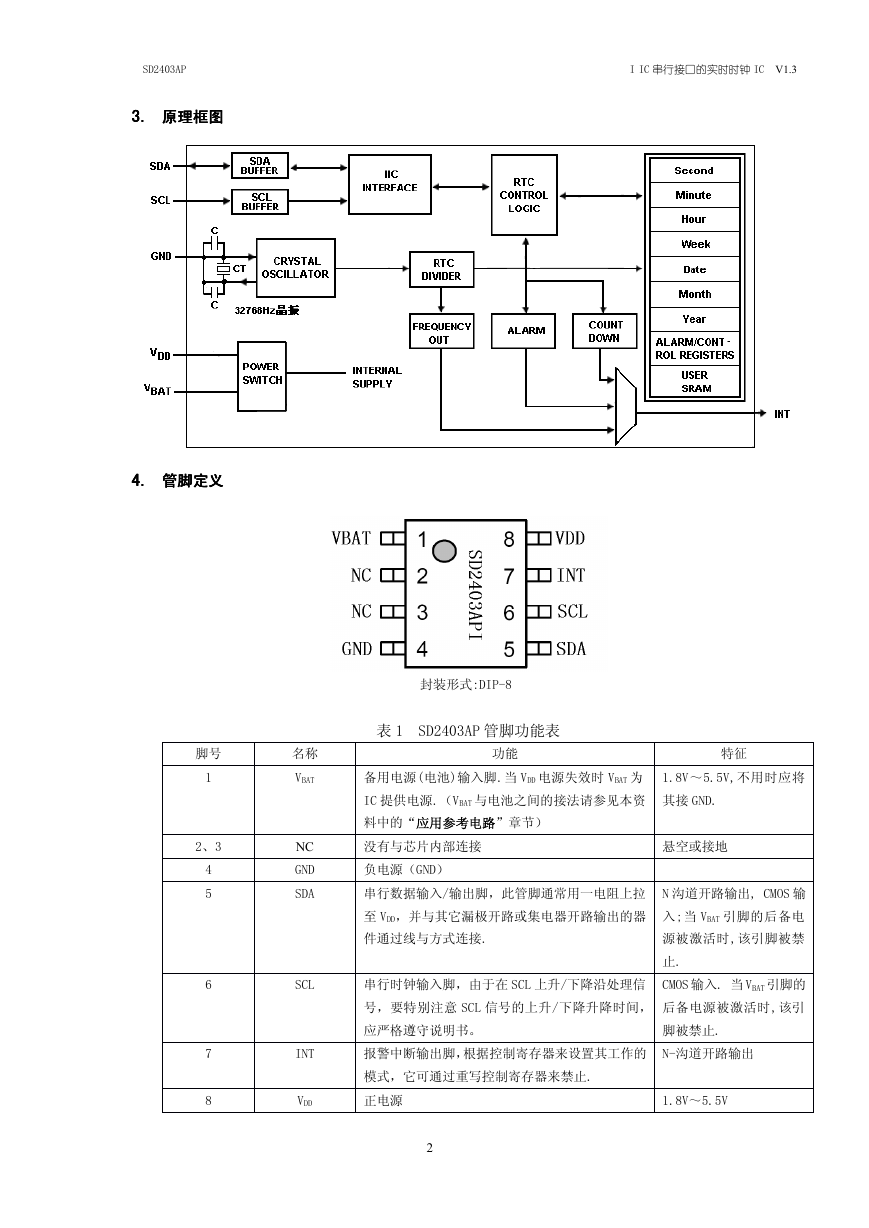

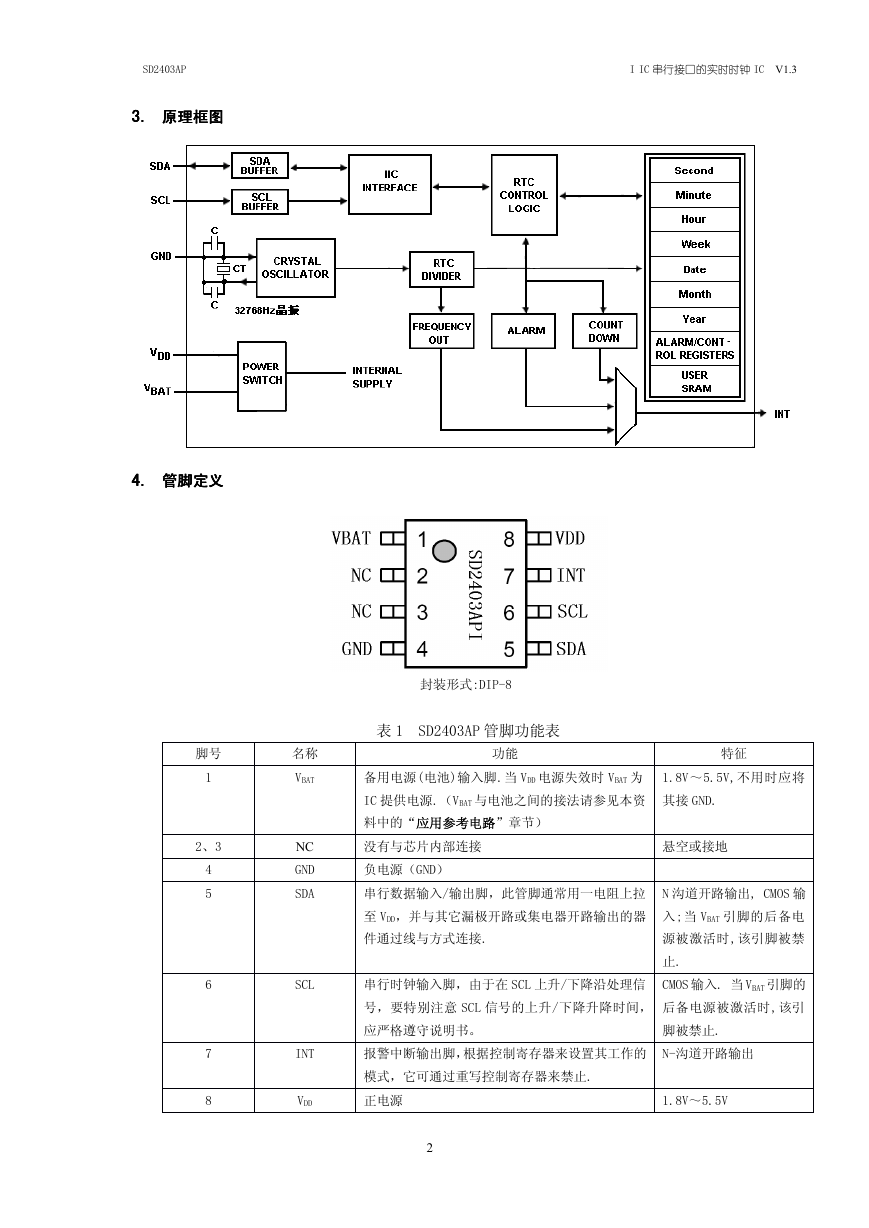

4.4.4.4. 管脚定义

管脚定义管脚定义

管脚定义

脚号

1

2、3

4

5

6

7

8

封装形式:DIP-8

表 1 SD2403AP 管脚功能表

名称

VBAT

NC

GND

SDA

功能

特征

备用电源(电池)输入脚.当 VDD 电源失效时 VBAT 为

1.8V~5.5V,不用时应将

IC 提供电源.(VBAT 与电池之间的接法请参见本资

其接 GND.

料中的“应用参考电路”章节)

没有与芯片内部连接

负电源(GND)

悬空或接地

串行数据输入/输出脚,此管脚通常用一电阻上拉

N 沟道开路输出, CMOS 输

至 VDD,并与其它漏极开路或集电器开路输出的器

入;当 VBAT 引脚的后备电

件通过线与方式连接.

源被激活时,该引脚被禁

止.

SCL

串行时钟输入脚,由于在 SCL 上升/下降沿处理信

CMOS 输入. 当 VBAT 引脚的

号,要特别注意 SCL 信号的上升/下降升降时间,

后备电源被激活时,该引

应严格遵守说明书。

脚被禁止.

INT

报警中断输出脚,根据控制寄存器来设置其工作的

N-沟道开路输出

模式,它可通过重写控制寄存器来禁止.

VDD

正电源

1.8V~5.5V

2

�

SD2403AP

5.5.5.5. 寄存器寄存器寄存器寄存器

I IC 串行接口的实时时钟 IC V1.3

D6

S40

MN40

0

0

0

0

Y40

AS40

D5

S20

MN20

H20

P/A_

0

D20

0

Y20

AS20

BIT

D4

S10

MN10

H10

0

D10

MO10

Y10

AS10

D3

S8

MN8

H8

0

D8

MO8

Y8

AS8

D2

S4

MN4

H4

W4

D4

MO4

Y4

AS4

D1

S2

MN2

H2

W2

D2

MO2

Y2

AS2

D0

S1

MN1

H1

W1

D1

MO1

Y1

AS1

AMN40

AMN20

AMN10

AMN8

AMN4

AMN2

AMN1

AH20

AP/A_

AW5

AD20

AH10

AW4

AD10

AH8

AW3

AD8

AH4

AW2

AD4

0

AMO10

AMO8

AMO4

AY5

EAMO

AY4

EAD

INTAF

INTDF

AY3

EAW

0

AY2

EAH

WRTC2

0

AH2

AW1

AD2

AMO2

AY1

EAMN

AH1

AW0

AD1

AMO1

AY0

EAS

RTCF

5.15.15.15.1 寄存器列表

寄存器列表

寄存器列表

寄存器列表

寄存器名

称

秒

分钟

D7

0

0

小时

12_/24

星期

日

月

年

秒报警

分钟报警

小时报警

星期报警

日报警

月报警

年报警

报警允许

CTR1

CTR2

CTR3

0

0

0

Y80

0

0

0

0

0

0

AY7

0

WRTC3

WRTC1

ARST

时间调整

0

0

AW6

0

0

AY6

EAY

0

IM

0

F6

地

址

00H

01H

02H

03H

04H

05H

06H

07H

08H

09H

0AH

0BH

0CH

0DH

0EH

0FH

10H

11H

12H

13H

14~

1FH

寄存

器段

实时

时钟

寄存

器

时间

报警

寄存

器

控制

寄存

器

通用

RAM

数值范围

缺省值

(十进制)

(二进制)

0-59

0-59

XXXX-XXXX

XXXX-XXXX

0-23

XXXX-XXXX

0-6

1-31

1-12

0-99

0-59

0-59

XXXX-XXXX

XXXX-XXXX

XXXX-XXXX

XXXX-XXXX

0000-0000

0000-0000

0-23

0000-0000

N/A

1-31

1-12

0-99

N/A

N/A

N/A

N/A

N/A

0000-0000

0000-0000

0000-0000

0000-0000

0000-0000

0000-0000

0000-0000

0000-0000

0000-0000

0-255

0000-0000

INTS1

INTS0

FOBAT

INTDE

INTAE

INTFE

TDS1

TDS0

F5

TD5

F4

TD4

FS3

F3

TD3

FS2

F2

TD2

FS1

F1

TD1

FS0

F0

TD0

倒计时定

时器

TD7

TD6

(12Bytes)

BIT7

BIT6

BIT5

BIT4

BIT3

BIT2

BIT1

BIT0

N/A

XXXX-XXXX

5.25.25.25.2 实时实时实时实时时钟时钟时钟时钟数据寄存器

数据寄存器(00H~06H)

数据寄存器

数据寄存器

实时时钟数据寄存器是 7 字节的存储器,它以 BCD 码方式存贮包括年、月、日、星期、时、分 、

秒的数据。

年数据[06H[06H[06H[06H 地址]]]](00~99):设 置 千年(20XX)的 后两位数字(00~99),通过自动日历功能计至 2099

月数据[05H[05H[05H[05H 地址(01~12):::: 每月包含的天数通过自动日历功能来更改。

年 。(注意: 2000 年为闰年)

1,3,5,7,8,10,12: 1~31

4,6,9,11: 1~30

2(闰年): 1~29

2(普通): 1~28

日数据[04H[04H[04H[04H 地址]]]](01~31)

星期数据[03H[03H[03H[03H 地址]]]](00~06):七进制计数器,00 对应星期天,01 对应星期一,依次类推.

小时数据[02H[02H[02H[02H 地址]]]](00~23 或 00~11):小时的最高位 12_/24 是 12 或 24 小时制选择位。

当 12_/24=1 时,24 小时制; 当 12_/24=0 时, 12 小时制。

3

�

SD2403AP

I IC 串行接口的实时时钟 IC V1.3

12 小时制时,H20 为 AM/PM 指示位,H20=0 为 AM,H20=1 为 PM,

见下表:(位 H20H10H8H4H2H1)

注意:::: 当读取小时数据时,要屏蔽掉小时的最高位 12_/24,否则在 24 小时制时会因为 12_/24=1 而显示

不对.

分数据[01[01[01[01HHHH 地址]]]](00~59)

秒数据[00H[00H[00H[00H 地址]]]](00~59)

例如:设时间为 2006 年 12 月 20 日星期三 18 点 19 分 20 秒(24 小时制),则寄存器 00~07H 的赋值应

分别为 20h、19H、98h、03h、20h、12h、06h。要特别注意此处小时位的赋值,因为是 24 小时制

式,小时的 12_/24 位=1,所以小时的赋值为 98h(1001 1000B)。

注:

1. 在上电复位时,芯片内部不对实时时钟数据寄存器作清零或置位处理。

2. 当芯片收到读实时时钟数据命令,则所有实时时钟数据被锁存(时钟走时并不受影响),此功

能可以避免时间数据的错读现象。

5.3 中断中断中断中断(08H~13H 地址)

SD2403AP 有 3 种不同的中断,它们由控制寄存器 2(10H)中的位 INTAE、 INTFE、INTDE 位

来使能:

中断允许位/标志位列表

序

号

1

2

3

中断允许位

(1=允许,0=禁止)

INTAE

INTFE

INTDE

中断名

报警中断

频率中断

倒计时中断

中断标志位

(1=有中断,0=无中断)

INTAF

无

INTDF

当报警中断产生时,置中断标志位 INTAF 为 1;当倒计时中断产生时, 置中断标志位 INTDF 为 1;频

率中断没有标志位.标志位被置 1 后,需要手动清除.

三种中断都是以 INT 脚为输出脚, 通过控制寄存器 2 中的 INTS1、INTS0 位来选择确定 INT 脚输

出何种中断:

INT 脚中断输出选通表

序号

INTS1

INTS0

0

1

2

3

0

0

1

1

0

1

0

1

4

描 述

禁止输出,高阻态

报警中断输出

频率中断输出

倒计时中断输出

�

SD2403AP

I IC 串行接口的实时时钟 IC V1.3

(1) 报警中断

当 INTAE=1 时报警中断被允许,报警中断何时发生由时间报警寄存器(07H~0EH)来确定。这其

中 07H~0DH 依次用于存放报警时间的秒、分钟、小时、星期、日、月、年数据,除小时报警数据寄

存器的最高位始终为”0” 、星期位的定义不同以外,其它的格式与实时时钟寄存器相同。

0EH 为时间报警允许寄存器,如下:

D5

BIT

EAMO

D7

位名(值)

0

报警允许

-

D6

EAY

年

D4

EAD

日

D3

EAW

星期

D2

EAH

小时

D1

EAMN

分钟

月

(0DH)

(0CH)

(0BH)

(0AH)

(09H)

(08H)

D0

EAS

秒(07H)

注:1=允许,0=禁止.

时间报警允许寄存器的使能位是用于确定哪些时间报警寄存器(秒、分钟等)需要与实时时钟

寄存器之间作比较。当 实时时钟运行时,一旦被允许的报警寄存器均与对应的实时时钟寄存器相匹

配,就会触发一次报警中断,同时报警中断标志位 INTAF 位被置”1”.

特别:

1.当日报警与星期报警均被允许即 EAD=EAW=1 时,只有日报警有效,而星期报警无效,所以

时间报警中断共有 96 种组合方式。

2.星期报警 寄存器 的数据 格式与 实时时 钟数据 星期的 格式不 同 ,星期报警 寄存器 的位

AW6.AW5.AW4.AW3.AW2.AW1.AW0 分别对应星期六.星期五.星期四.星期三.星期二.星期一.星期

日,并可多位置 1,例如 AW6,AW1=1,其它位为 0,则对应在星期六.星期一会有报警.

每一次对时间报警允许寄存器的写入都会清 INTAF 为"0".

当设置 INTS1=0、INTS0=1 时,即允许报警中断从 INT 脚输出.该报警中断有两种模式,即单事

件报警和周期性报警, 模式的选定由控制寄存器 2 中的报警中断模式位 IM 的值来定:

IM 位

0

1

报警中断模式

单事件报警

周期性报警

INT 脚

输出低电平直至 INTAF 位清零

输出低电平有效、宽度为 250ms 的周期性脉冲直至

INTAF 位清零

为清除报警中断,可通过写操作将控制寄存器 1 的 INTAF 位置”0”.但当 ARST 位置为”1”,则在

控制寄存器 1 被读取时,INTAF 位会自动清零.

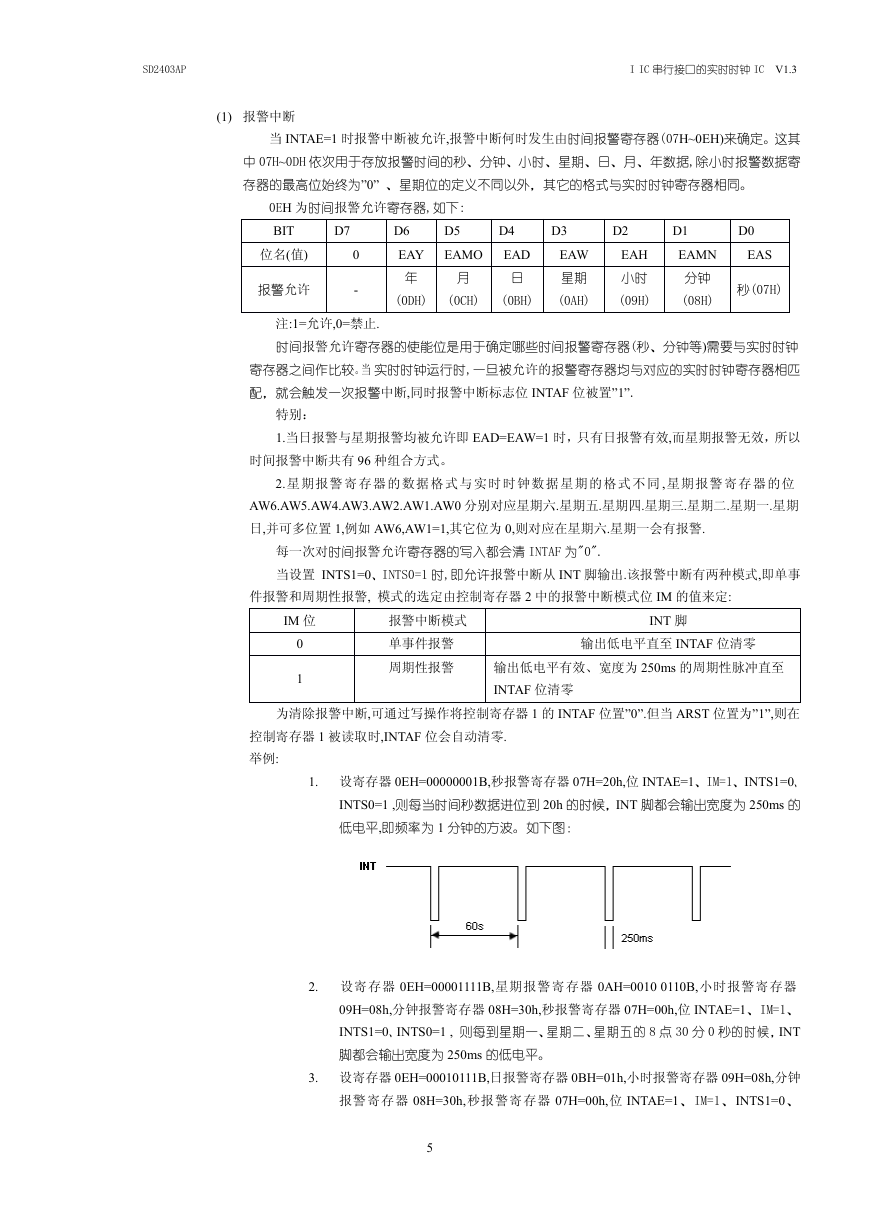

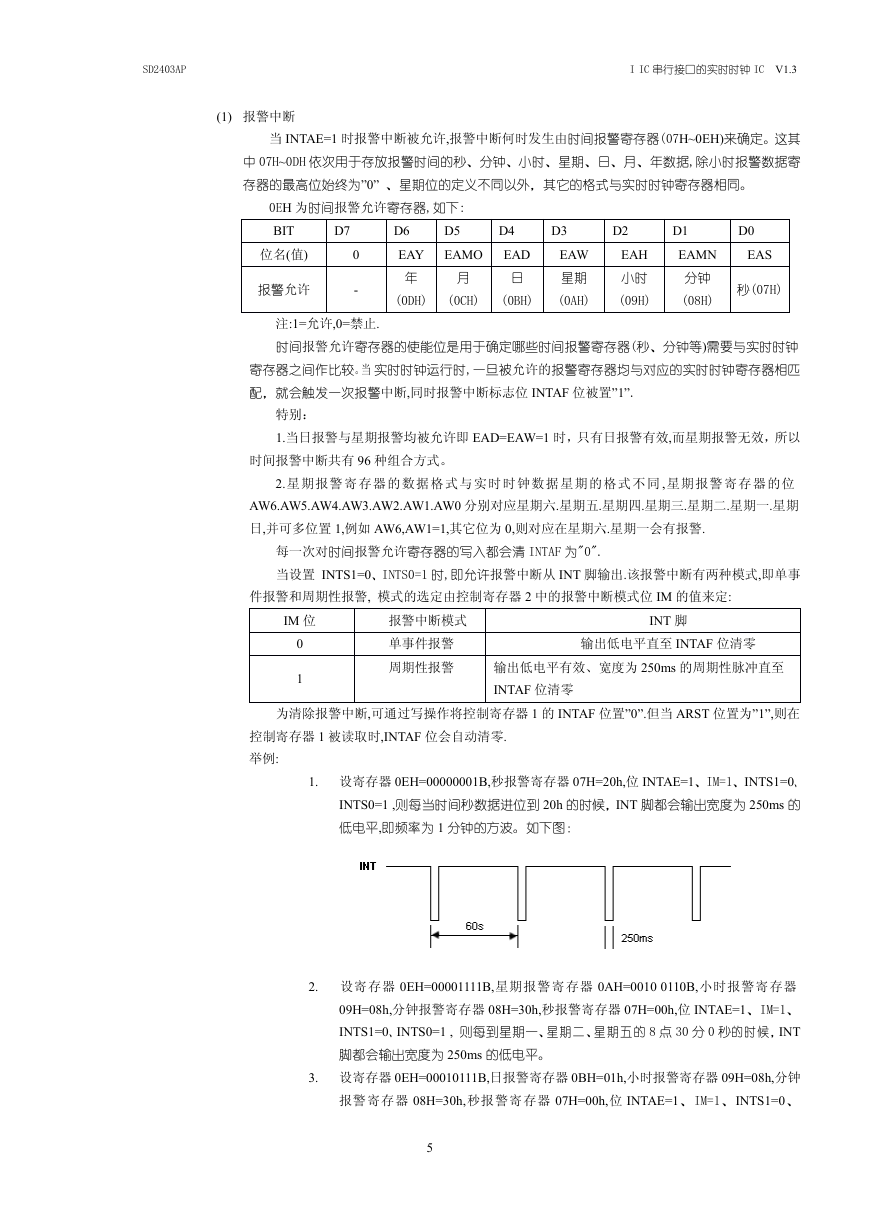

举例:

1. 设寄存器 0EH=00000001B,秒报警寄存器 07H=20h,位 INTAE=1、IM=1、INTS1=0、

INTS0=1 ,则每当时间秒数据进位到 20h 的时候,INT 脚都会输出宽度为 250ms 的

低电平,即频率为 1 分钟的方波。如下图:

2. 设寄存器 0EH=00001111B,星期报警寄存器 0AH=0010 0110B,小时报警寄存器

09H=08h,分钟报警寄存器 08H=30h,秒报警寄存器 07H=00h,位 INTAE=1、IM=1、

INTS1=0、INTS0=1 , 则每到星期一、星期二、星期五的 8 点 30 分 0 秒的时候,INT

脚都会输出宽度为 250ms 的低电平。

3. 设寄存器 0EH=00010111B,日报警寄存器 0BH=01h,小时报警寄存器 09H=08h,分钟

报警寄存器 08H=30h,秒报警寄存器 07H=00h,位 INTAE=1、IM=1、INTS1=0、

5

�

SD2403AP

I IC 串行接口的实时时钟 IC V1.3

INTS0=1 , 则到每个月 1 号的 8 点 30 分 0 秒的 时 候 ,INT 脚都会输出宽度为 250ms

的低电平。

4. 设寄存器 0EH=0111 0100B, 年报警寄存器 0DH=08h,月报警寄存器 0CH=08h,日报

警寄存器 0BH=08h,小时报警寄存器 09H=20h,位 INTAE=1、IM=0、INTS1=0、

INTS0=1、12_/24=1 , 则到 2008 年 8 月 8 日 20 点 0 分 0 秒时,INT 脚会输出低

电平。此后如清零 INTAF,则 INT 脚从低电平变成高电平。

(2) 频率中断

当 INTFE=1 时频率中断被允许; INTFE=0 时频率中断被禁止.

当设置 INTS1=1、INTS0=0 时,即允许频率中断从 INT 脚输出. 频率中断没有标志位.

INT 脚输出频率中断由控制寄存器 3(CTR3)中的 FS3、FS2、FS1、FS0 位来选择确定:

频率(HZ)

0

32768

4096

1024

64

32

16

8

4

2

1

1/2

1/4

1/8

1/16

1 秒

FS3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

FS0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

FS2

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

FS1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

注:INT 脚输出的频率中断除了秒均是由 32768HZ 晶体振荡电路整形及分频得到的;1 秒频率中断是指输

出 500ms 低电平、500ms 高电平的方波,输出低电平的下降沿与秒进位同步; 在数字调整寄存器起作用

时,1 秒和 1Hz 应是不相同的.

(3) 倒计时中断

与倒计时中断相关的寄存器是 8 位的倒数定时器, 当控制寄存器 2 中的位 INTDE=1 时倒计时中断

被允许.

倒数定时器的频率源由控制寄存器 2 中的位 TDS1、TDS0 来选定

TDS1

0

0

1

1

TDS0

定时器频率源(HZ)

0

1

0

1

4096

64

1

1/60

当 INTDE=1 且倒数定时器写入一个八位自动重置的二进制数后, 倒数定时器会按照 TDS1、TDS0

选定的频率时间来减一.每次当倒数定时器为零时,会置倒计时中断的标志位(控制寄存器 1 中的位

INTDF)为 1.

6

�

SD2403AP

I IC 串行接口的实时时钟 IC V1.3

当设置 INTS1=1、INTS0=1 时,即允许倒计时中断的低电平从 INT 脚输出. 置 INTDF=0 时 INT 脚输

出变为高电平直到下一次倒计时中断 INT 脚再次变为低电平.

当设置 INTDE=0 时倒计时中断被禁止.

5.45.45.45.4 数字化时间精度调整电路

数字化时间精度调整电路(12H 地址)

数字化时间精度调整电路

数字化时间精度调整电路

利用数字化时间精度调整电路可以每 20 秒改变当前 1 秒所包含的 32768Hz 脉冲的个数,从而到达

时钟走时调整,使 SD2403AP 保持高的走时精度.相关寄存器为时间调整寄存器(内部地址 12H):

时间调整寄存器:(缺省值为 00H)

D7

0

D6

F6

D5

F5

D4

F4

D3

F3

D2

F2

D1

F1

D0

F0

F6~F0:时间调整位;时间调整电路是在当秒计数为 00,20,40 时刻,根据预先设置的数据(F6~F0)改变 1 秒

时钟内计数的个数.通常每 32768 个脉冲为 1 秒(对寄存器预设初值,才能激活整个调整电路).

当 F6 为”0”时,产生 1 秒的寄存器计数脉冲将增加为 32768+((F5,F4,F3,F2,F1,F0)-1)×2;

当 F6 为”1”时,产生 1 秒的寄存器计数脉冲将减少为 32768-((/F5,/F4,/F3,/F2,/F1,/F0)+1)×2;(/F5

是 F5 的反码,其它类同)

当(F6,F5,F4,F3,F2,F1,F0)预设为(*,0,0,0,0,0,*)时, 产生 1 秒的寄存器计数脉冲不变.

例 : 当 (F6,F5,F4,F3,F2,F1,F0)=(0,1,0,1,0,0,1) 且 当 00,20,40 秒 时 刻 时 , 寄 存 器 计 数 脉 冲 变 为

32768+(41-1) ×2=32848;

当(F6,F5,F4,F3,F2,F1,F0)=(1,1,1,1,1,1,0)且当 00,20,40 秒时刻时,寄存器计数脉冲变为 32768-

(1+1) ×2=32764;

当(F6,F5,F4,F3,F2,F1,F0)=(0,0,0,0,0,0,1)且当 00,20,40 秒时刻时,寄存器计数脉冲保持为 32768

不变.

因为每 20 秒增加或减少计数脉冲的最小个数为 2,,所以时钟调整寄存器的最小调整精度是:2/(32768

×20)=3.015ppm.

注意: 时钟调整电路仅是调整的时钟走时,并不对晶振本身频率调整,所以 32.768KHZ 脉冲输出没有变化.

时钟调整寄存器的调整值计算方法:

1) 当晶振频率大于目标频率(32768HZ),则需要增加 1 秒内的计数脉冲:

调整值=

(晶振频率-目标频率+0.1)

晶振频率*2/目标频率*20

= (晶振频率-目标频率)*10+1

其中:晶振频率是从 INT 脚测出的频率中断标称为 32768HZ 的频率(即 FS3、FS2、FS1、FS0=0001),下

同;

调整值是设置 F6~F0 的数值,该数值是用二进制补码形式表示.下同

2) 当晶振频率小于目标频率(32768HZ),则需要减少 1 秒内的计数脉冲:

调整值=

(晶振频率-目标频率)

晶振频率*2/目标频率*20

= (晶振频率-目标频率)*10

3) 当晶振频率等于目标频率(32768HZ),则不需要改变 1 秒内的计数脉冲.

调整值=0,+1,-64,-63 或者缺省.

计算调整数值大小示例:

7

�

SD2403AP

I IC 串行接口的实时时钟 IC V1.3

1) 晶振频率=32770HZ, 目标频率=32768HZ

调整值=(32770-32768+0.1)/(32770*2/(32768*20))=(32770-32768)*10+1=21

故设置(F6,F5,F4,F3,F2,F1,F0)=(0,0,1,0,1,0,1)

2) 晶振频率=32762HZ, 目标频率=32768HZ

调整值=(32762-32768)/(32762*2/(32768*20))=(32762-32768)*10=-60

因为-60 的 7 位补码是 80H-3CH=44H

故设置(F6,F5,F4,F3,F2,F1,F0)=(1,0,0,0,1,0,0)

经过数字化时间精度电路调整后,时钟精度与目标频率相差±1.5ppm(在室温下)

但是要注意:

1) 时间调整电路不能改变从 INT 输出频率中断的频率;

2) 最大调整范围:

a. 晶振频率大于目标频率时,调整数值范围(F6,F5,F4,F3,F2,F1,F0)=(0,0,0,0,0,0,0)到(0,1,1,1,1,1,1),实

际可调范围从-3.05ppm 到-189.2ppm.

b. 晶振频率小于目标频率时,调整数值范围(F6,F5,F4,F3,F2,F1,F0)=(1,1,1,1,1,1,1)到(1,0,0,0,0,1,0),实

际可调范围从+3.05ppm 到+189.2ppm.

通用通用通用通用 RAMRAMRAMRAM(14H~1FH 地址)

5.5

SD2403AP 内部提供 12 个字节的通用静态 RAM 供用户存储数据.

通用 SRAM 的缺省值是 XXH.(即不确定值)

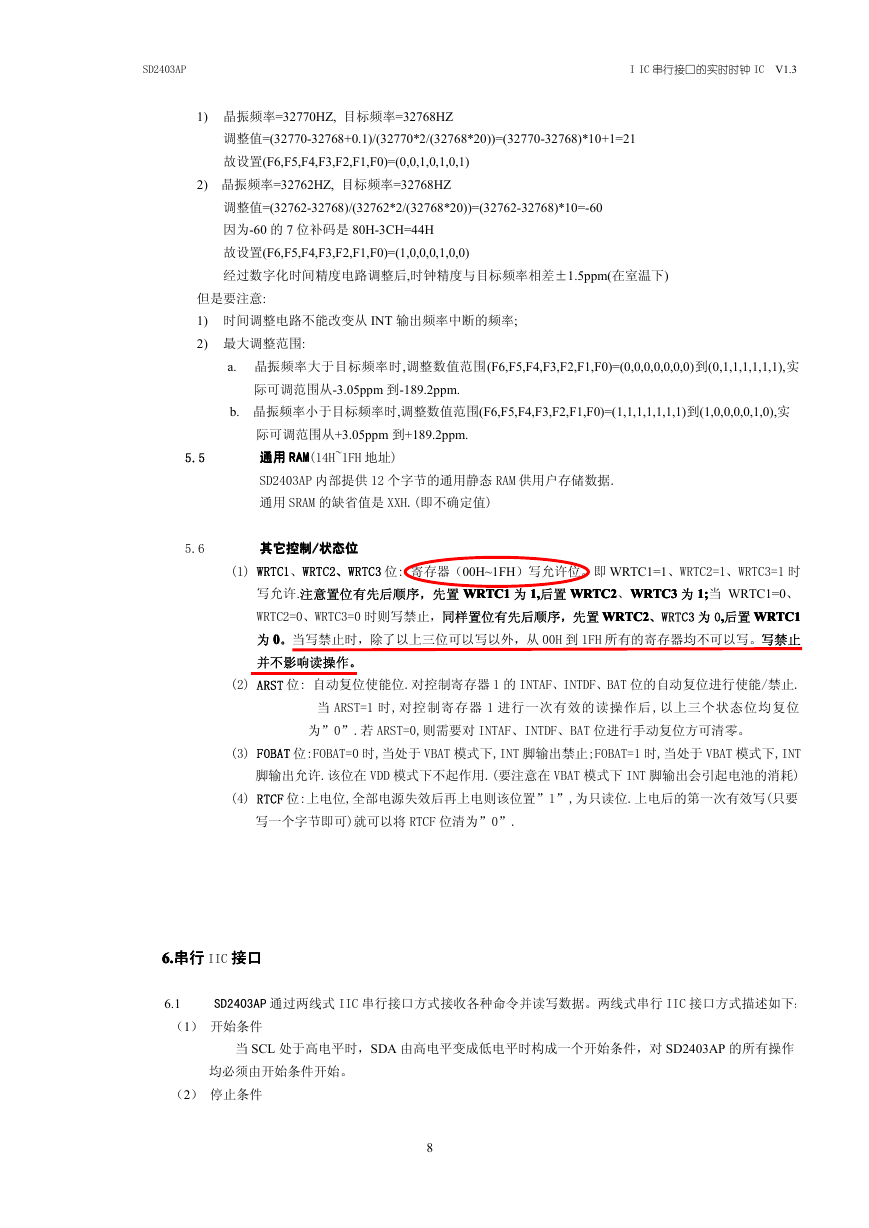

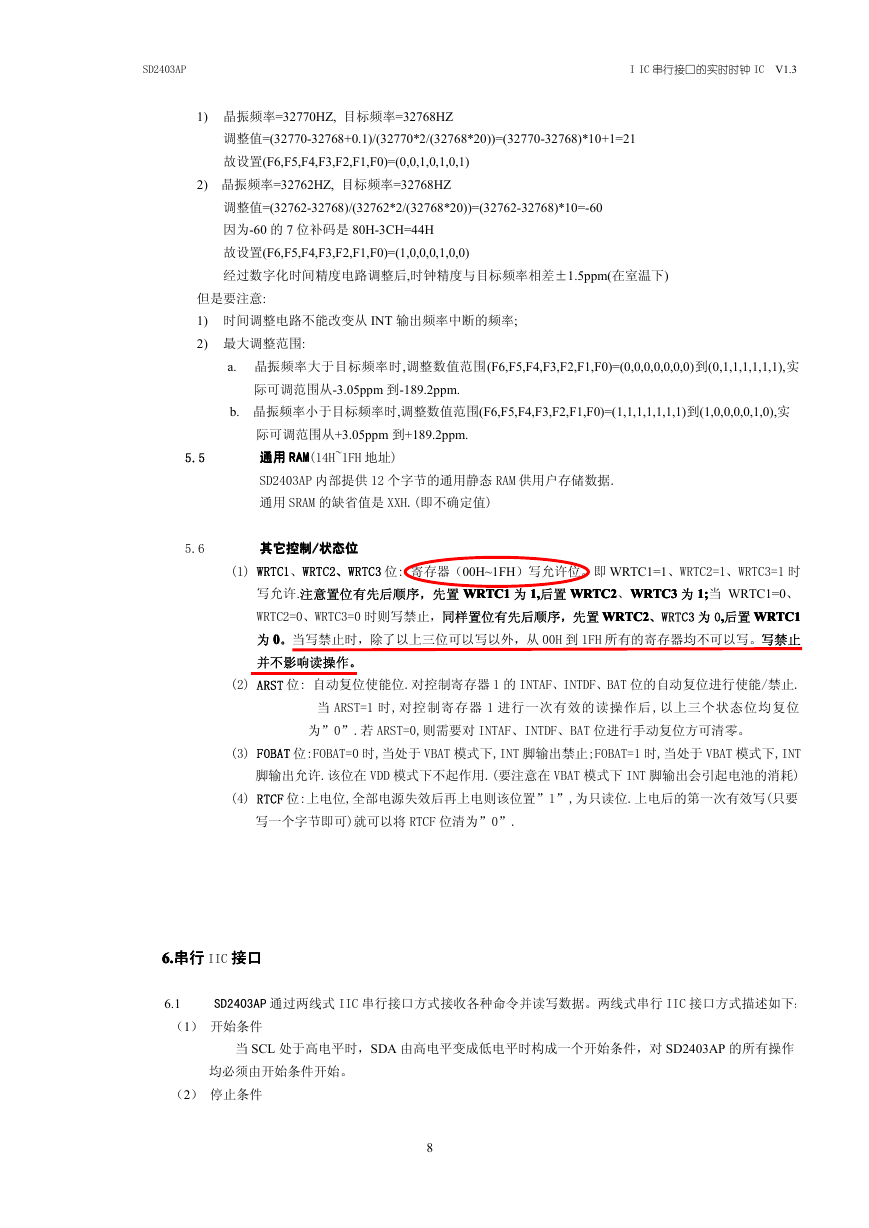

5.6

其它控制其它控制

其它控制////状态位状态位状态位状态位

其它控制

(1) WRTC1、WRTC2、WRTC3 位: 寄存器(00H~1FH)写允许位。即 WRTC1=1、WRTC2=1、WRTC3=1 时

WRTC3 为 1;1;1;1;当 WRTC1=0、

WRTC2

WRTC1 为 1,1,1,1,后置 WRTC2

WRTC1

WRTC3

WRTC1

WRTC2

WRTC3

写允许.注意置位有先后顺序,先置 WRTC1

WRTC2、WRTC3

WRTC2、WRTC3 为 0,,,,后置 WRTCWRTCWRTCWRTC1111

WRTC2

WRTC2

WRTC2=0、WRTC3=0 时则写禁止,同样置位有先后顺序,先置 WRTC2

为 0000。当写禁止时,除了以上三位可以写以外,从 00H 到 1FH 所有的寄存器均不可以写。写禁止

并不影响读操作。

(2) ARST 位: 自动复位使能位.对控制寄存器 1 的 INTAF、INTDF、BAT 位的自动复位进行使能/禁止.

当 ARST=1 时,对控制寄存器 1 进行一次有效的读操作后 ,以上三个状态位均复位

为”0”.若 ARST=0,则需要对 INTAF、INTDF、BAT 位进行手动复位方可清零。

(3) FOBAT 位:FOBAT=0 时,当处于 VBAT 模式下,INT 脚输出禁止;FOBAT=1 时,当处于 VBAT 模式下,INT

脚输出允许.该位在 VDD 模式下不起作用.(要注意在 VBAT 模式下 INT 脚输出会引起电池的消耗)

(4) RTCF 位:上电位,全部电源失效后再上电则该位置”1”,为只读位.上电后的第一次有效写(只要

写一个字节即可)就可以将 RTCF 位清为”0”.

6.6.6.6.串行串行串行串行 IIC 接口接口接口接口

SD2403AP 通过两线式 IIC 串行接口方式接收各种命令并读写数据。两线式串行 IIC 接口方式描述如下:

6.1

(1) 开始条件

当 SCL 处于高电平时,SDA 由高电平变成低电平时构成一个开始条件,对 SD2403AP 的所有操作

均必须由开始条件开始。

(2) 停止条件

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc