科技信息.

高校 理科 研 究

数字 电路 巾 BUS HOLD功 雒的 应用 研夯

南京理 工大 学紫金 学院 电光 系 郁 岚

[摘 要]BUS HOLD 功能已普遍应用在 EPLD、FPGA、245/244驱动等电路 中,深入地 了解 BUS HOLD功能对 电路设计将会有很

好 的改进效果,并具有普遍 的应 用价值。

[关键词 ]BUS HOLD 总线保持

一

、 BUS HOLD功 能 简 介

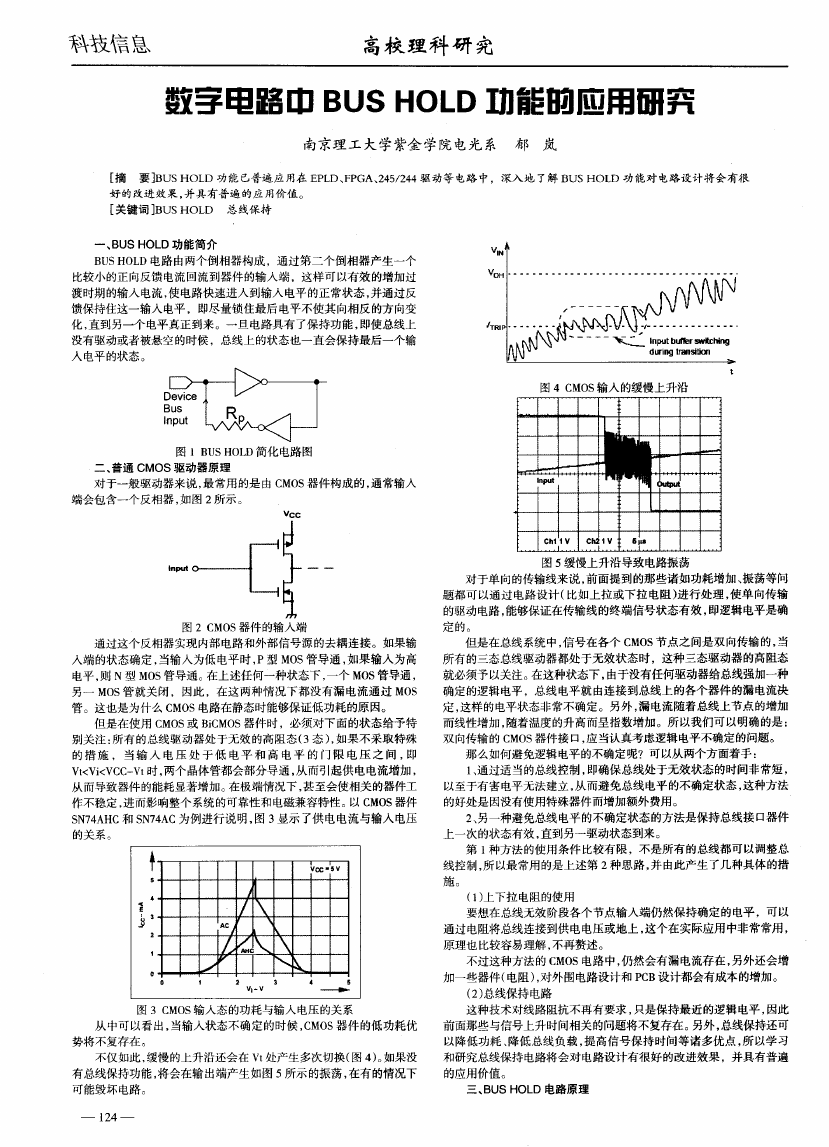

BUS HOLD电路 由两个倒相器构成 ,通过第二个倒相器产生一个

比较小的正 向反馈电流回流到器件 的输入端 ,这样可以有效 的增加过

渡时期的输入电流 ,使 电路快速进入到输入电平的正常状态 ,并通过反

馈保持住这一输入电平 ,即尽量锁住最后电平不使其 向相反 的方 向变

化 ,直到另一个电平真正 到来 。一旦电路具有了保持 功能 ,即使总线上

没有驱动或者被悬空的时候 ,总线上的状态也一直会保持最后一个输

入 电 平 的状 态 。

图 1 BUSHOLD 简化 电路 图

二 、普通 CM0S驱 动 器 原 理

对于一般驱动器来说 ,最常用的是 由 CMOS器 件构成 的 ,通常输入

端 会 包含 一 个 反 相 器 ,如 图 2所 示 。

图 2 CMOS器 件 的输 入 端

通过这个反相器实现 内部 电路 和外部信号源的去耦连接 。如果输

入端 的状态确定 ,当输人为低 电平 时 ,P型 MOS管导通 ,如果输入为高

电平 ,则 N型 MOS管导通。在上述任何一种状态下 ,一个 MOS管导通 ,

另一 MOS管就关 闭,因此 ,在这两种情 况下都没有漏电流通过 MOS

管 。这也是为什么 CMOS电路在静态时能够保证低功耗的原 因。

但是在使用 CMOS或 BiCMOS器件时 ,必须对下 面的状态 给予特

别 关 注 :所 有 的 总 线 驱 动器 处 于无 效 的高 阻 态 (3态 ),如 果 不 采 取 特 殊

的措 施 ,当输 入 电压 处 于低 电平 和 高 电平 的 门 限 电压 之 间 ,即

Vt

科技信息.

高校 理科 研 究

总线保持是通过保持 电路来 确保总线在无效状态时 ,节点 的输人

端仍然有确定状态 的电平 。这类 电路的基本思想是通过反相器将输 出

端 的信号正反馈给其输入端 ,从而形成双稳态 电路(锁定 )。电路原理如

图 6所 示 。

InteltllllI

Circuit

图 8 CMOS输 入 电路 悬 空时 ,可 能 产 生 的 “悬 浮 ”噪 声 电平

由于走线及其 它原器件被连到输入端 ,会使输入端(INPUT)相 当于

并联 了一个 电路 ,等效为 C1(约几十 pF),上 电时这个 电容漏 电,那么 内

部相当于有一个等效上拉 电阻 R1(10K~100K之间 ),于是在上 电过程

中 BUS HOLD功能将输入 的状 态“锁定 ”为高 ,所 以默认 的输 出电平是

高电平 。这一特性在 电路设计时也需要予 以关注。

图 6简 化 BUSHOLD 电 路

总线保持 电路 是由两对互 补倒相 器构成 ,Q1/Q2是一 对互补倒 相

器 ,同理 Q3/Q4也 是一对互补倒相器 ,事实上 BUS HOLD电路被认 为是

由 Q3/Q4构成的,因为加 了 Q3/Q4的反馈 ,电路具有 了保持 的功能 。

假设信号从输入端输入 ,先 由第一对互补倒 相器将其反转 /倒 相

180度 (结点 1一>2),然后再 经过第 二个互补倒 相器反转 /倒想 180度

(结点 3一>4),也就是说信号是经过反相 360度 以后反馈给 了输入端 (结

点 4一>5),那么这两个倒相器 的反馈结果就 形成了一个锁存器—— 在

外部 电平不发生变化 时,它将持 续的保持最后输入 的状态 (确定 的高或

者低 ),所以此电路被称 为总线保持 电路 ,即 BUS HOLD。

根据 BUSHOLD电路原 理(图 6),可 以将两对互补 倒相器简化 ,于

图 9 BUS HOLD功能上电时等效 电路

是 BUS HOLD电路可 以简化为图 1所示。

3、BUS HOLD功 能可以减小输入功率 。

另外 ,又根据不少 厂家提供 的参数 (只有大 于 500uA强电流驱动 ,

才会发生切换(图 7))这个条件 ,可计算 出简化 电路中的电阻 Rp。

Pam m

Description

■In № Unit

IBHL Input Bu~HoldLOW +75

Sustaining Current

18HH Input B HOId HIGH 一75

lI^

Sustaining Cun'ent

IBI,ILO Input Bus-HoRI LOW

+50O pA

OverdriveCuffent

IBt-k]O

Ho :GH

一500 lIA

18HLO and IBHh~ 8re the LOW and HIG H ovecdrive c~q'enls

respectively Inordertochangethestaleofthebus-holdlat~.h.

蝴the st ore ofthe bu s-I~ld latc呲 。h F

咖

iTent

ON

state oft|’etxra-holdlatchisHIGH.∞ external drivermust

sink500uAtochangethestateoftheIxms~oldIalcrltoLOW .

o r

舶cd|rIDIe. tnb

if CU

/

厂

ASl~I:Vec‘5V L

LVlM:Vec-3,3V

LVCH:Vec。3.3V

/

匝 下№..k / J

】

./ r/

/

H — m ^

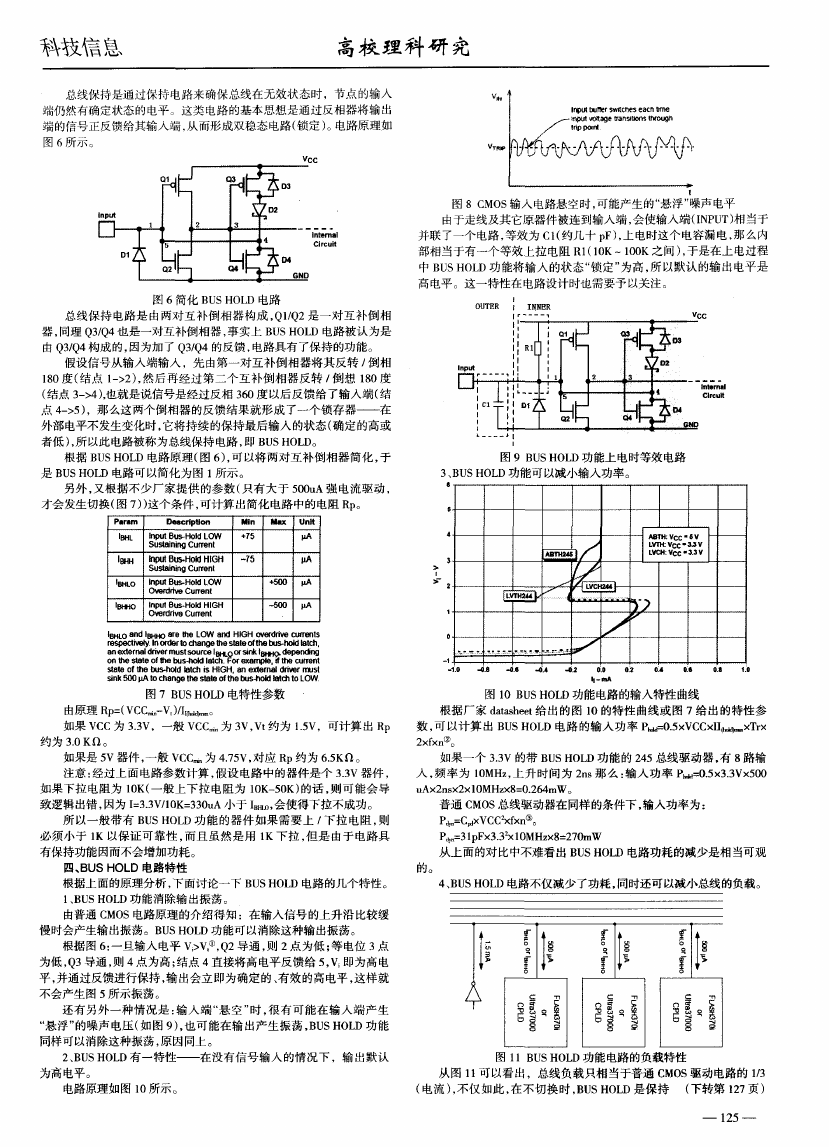

图 7 BUSHOLD电特性参数

图 10 BUS HOLD功能 电路 的输入特性曲线

由原 理 Rp=(VCC~一V )/I。 。

如果 VCC为 3.3V,一般 VCC 为 3V,Vt约为 1.5V,可计算 出 Rp

约 为 3.0Kn 。

如果是 5V器件 ,一般 VCC 为 4.75V,对应 Rp约为 6.5Kn。

注意 :经过上 面电路 参数计 算 ,假设 电路 中的器件是个 3.3V器件 ,

如果下拉电阻为 IOK(一般上下拉 电阻为 IOK一50K)的话 ,则可能会 导

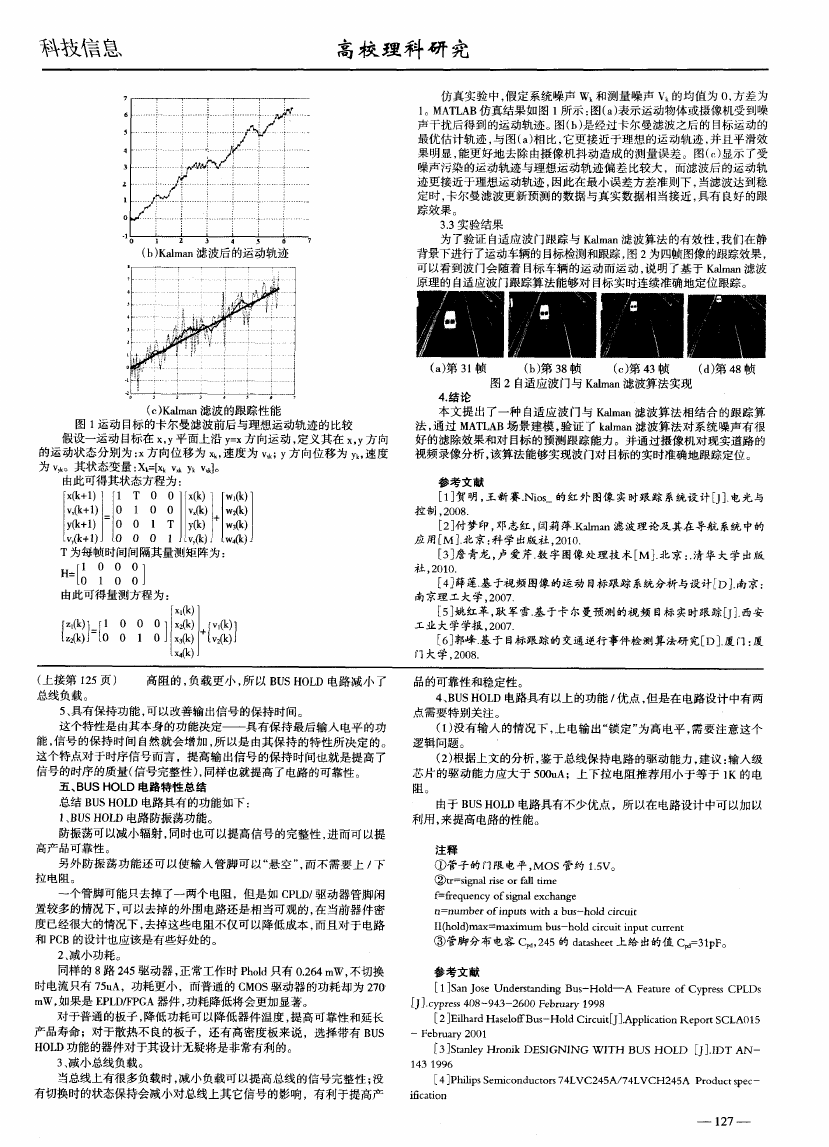

根 据厂家 datasheet给 出的图 1O的特性 曲线或 图 7给 出的特性参

数 ,可 以计 算出 BUS HOLD电路 的输入功 率 P|dd=O.5xVCCxlI~cmxTrx

2xfxn②。

如果 一个 3.3V的带 BUS HOLD功 能的 245总线驱 动器 ,有 8路输

入 ,频率 为 10MHz,上升时 间为 2ns那么 :输人功率 P =0.5x3.3Vx500

uA×2ns×2×1OMHzX8=0.264mW 。

致 逻 辑 出错 ,因为 I=3.3V/10K=330uA 小 于 IBr~o,会 使 得 下 拉 不 成 功 。

普通 CMOS总线驱动器在 同样 的条件下 ,输入功率 为:

所 以一般带有 BUS HOLD功 能的器件 如果需要 上 /下拉 电阻 ,则

必须小于 1K以保证 可靠性 ,而且虽然 是用 1K下 拉 ,但是 由于 电路具

有保持功能因而不会 增加功耗 。

Pdvn=CDdxVCC~ n 。

P,~.=31pFx3.3Zx10M Hzx8=270mW

从上 面的对 比中不难看出 BUS HOLD 电路功耗 的减 少是相当可观

四 、BUS H0LD电 路 特 性

的 。

根 据 上 面 的 原理 分 析 ,下 面 讨 论 一 下 BUS HOLD 电路 的几 个 特 性 。

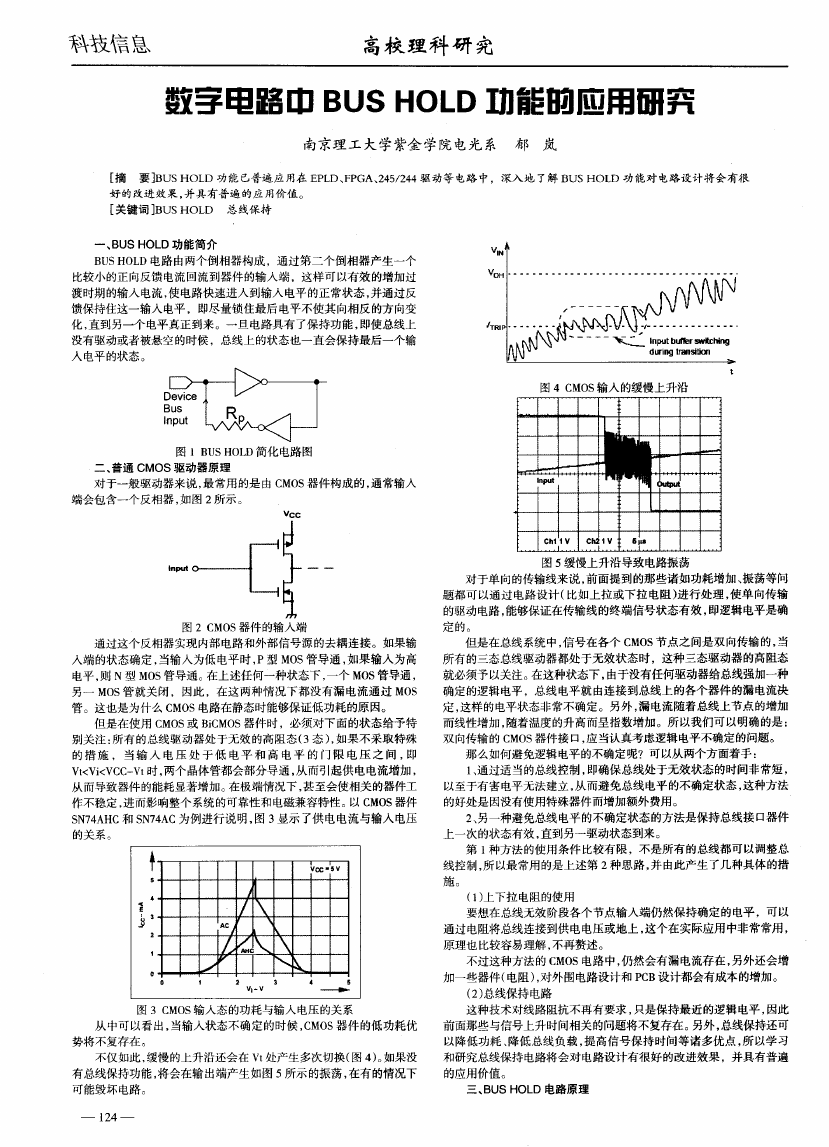

4、BUS HOLD电路不仅减少 了功耗 ,同时还可以减小 总线 的负载 。

1、BUS HOLD功 能 消 除 输 出 振 荡 。

由普通 CMOS电路原理 的介绍 得知 :在输入信号的上升沿 比较缓

慢时会产生输 出振荡 。BUS HOLD功能可以消除这种输 出振荡 。

根据图 6:一旦输入 电平 V,>v ,Q2导通 ,则 2点为低 ;等 电位 3点

为低 ,Q3导通 ,则 4点 为高 ;结点 4直接将高电平反馈给 5,V,即为高 电

平 ,并通过反馈进行保持 ,输 出会立 即为确定 的 、有效的高电平 ,这样就

不会产生图 5所示振荡 。

还有另外 一种情况是 :输入 端“悬 空 ”时 ,很有 可能在 输入端 产生

“悬浮 ”的噪声 电压(如 图 9),也 可能在输 出产 生振荡 ,BUS HOLD功能

同样可以消除这种振荡 ,原 因同上 。

2、BUS HOLD有一特性——在没有 信号输入 的情况 下 ,输 出默认

为高电平。

电路原理 如图 l0所示 。

图 1 1 BUS HOLD功能电路 的负载特性

从图 1 1可以看 出 ,总线负载只相当于普通 CMOS驱动 电路的 1,3

(电流 ),不 仅如此 ,在 不切换 时 ,BUS HOLD是 保持 (下转第 127页 )

一

125 一

�

科技信息.

高校 理科 研 究

Ⅳ

A /

/

/…

/

√

/

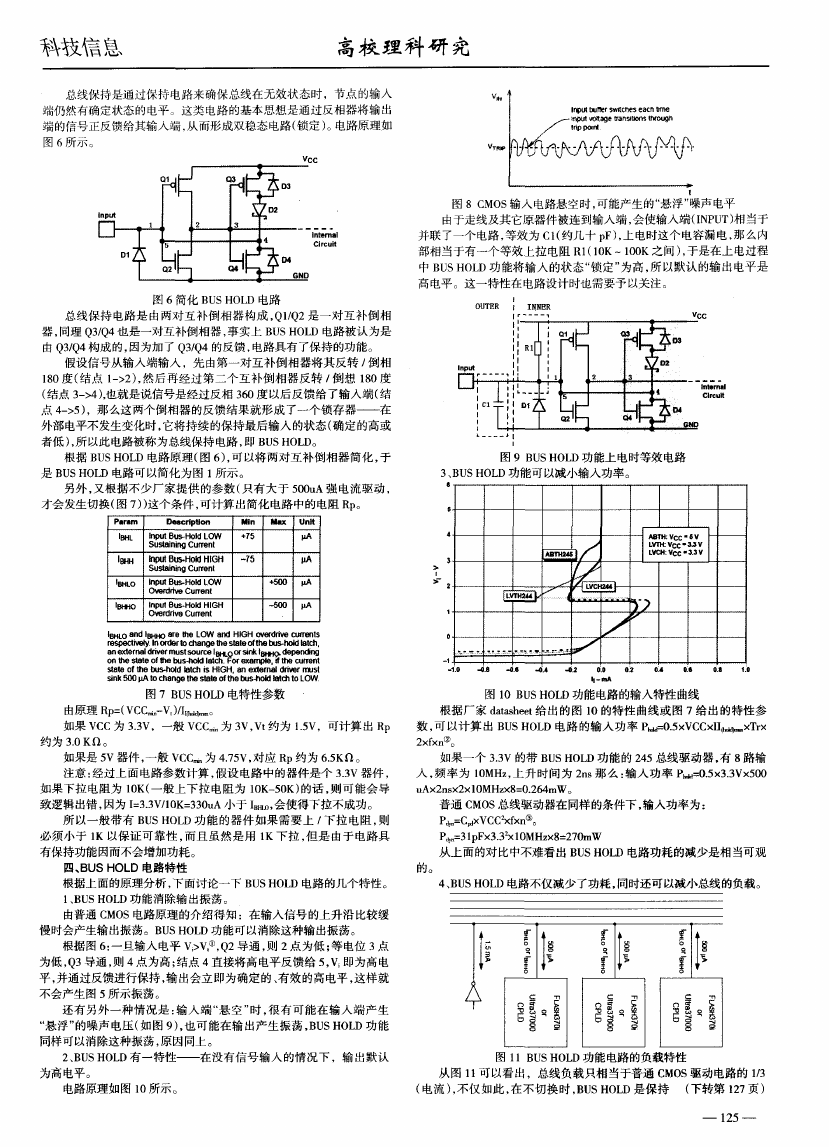

(b)Kalman滤波后 的运动轨迹

文 .≥ l i 。}

:

’

}

羹 麓

. 量

霹

(e)Kalman滤波 的跟踪性能

图 1运动 目标的卡尔曼滤波前后 与理想运动轨迹 的比较

假 设 一 运 动 目标 在 x,Y平 面 上沿 y=x方 向 运 动 ,定 义 其 在 x,Y方 向

的运动状态分别为 :x方向位移 为 x ,速度为 v ;Y方 向位移 为 yk,速度

为 。其状态变量 :XMxk Vxk v 。

由此可得其状态方程为 :

}x(k+1)]f1 T 0 0]fx(k)1『W-(k)]

l vdk+l )} 。0

y(k+l 0 0 1 T +

l y(1【)lllw )I

I )I I

I +1)J【O O 0 1 J Lye)』【w (k)J

T为每帧时间间隔其量测矩 阵为:

H: ::]

由此可得量测方程为 :

x-(k)]

嘲 =[ 。0 0 31 x2(k)]+

【)(4fk)J

(上接第 125页 ) 高阻的 ,负 载更小 ,所以 BUS HOLD 电路 减小 了

总线负载。

5、具有保持 功能,可以改善输 出信号的保持时间。

这个特性是 由其本身 的功 能决定——具 有保持最后输入 电平 的功

能 ,信号 的保 持时间 自然就会增 加 ,所 以是 由其保持的特性所 决定的 。

这个特点对 于时序信号而言 ,提高输 出信号 的保持时间也就是提高 了

信号的时序 的质量(信号完整性 ),同样 也就提高了电路 的可靠性 。

五 、BUS H0LD 电路 特 性 总 结

总结 BUS HOLD电路具有 的功能如下 :

1、BUS HOLD电路 防振荡功能 。

防振荡可以减小辐射 ,同时也可以提高信号 的完整性 ,进 而可 以提

高 产 品可 靠 性 。

另外 防振荡功 能还 可以使输 入管脚 可以“悬空 ”,而不 需要上 /下

拉 电阻 。

一 个管脚可能只去掉 了一两个 电阻 ,但是如 CPLD/驱动器管脚 闲

置较多的情况下,可以去掉 的外 围电路 还是 相当可观的 ,在当前器件 密

度 已经很大的情况下 ,去掉这些 电阻不仅 可以降低成本 ,而且对于 电路

和 PCB的设计也应该是有些好处 的。

2、减小 功耗 。

同样 的 8路 245驱动器 ,正常工作 时 Phnld只有 0.264 mw,不切换

时电流只有 75uA,功耗更小 ,而普通的 CMOS驱动器的功耗却为 270

mW,如果是 EPLD/FPGA器件 ,功耗 降低将 会更加显著 。

对于普通的板子 ,降低功耗可以降低器件温度 ,提 高可靠性 和延 长

产品寿命 ;对于散热不 良的板子 ,还有高密度板来说 ,选择带 有 BUS

HOLD功能的器件对 于其设计无疑将是非常有利的。

3、减小总线负载。

当总线上有很 多负载时 ,减小负载可以提高总线 的信号完整性 ;没

有切换时的状态保 持会减小对总线上其它信号 的影响 ,有利 于提 高产

仿 真实 验中 ,假定系统噪声 w 和测 量噪声 V 的均 值为 0,方差 为

1。MATLAB仿真结果如图 1所示 :图(a)表示运动物体 或摄像机受到噪

声干扰后得到 的运动轨迹。图(b)是经过卡尔曼滤波之后 的 目标运动的

最优估计轨迹 ,与 图(a)相 比,它更接 近于理想 的运 动轨迹 ,并且平滑效

果 明显 ,能更好地 去除由摄像机抖动造成 的测量误差 。图(c)显示了受

噪声污染的运动轨迹与理想运动轨迹偏 差比较 大 ,而滤 波后 的运动轨

迹 更 接 近 于 理 想 运 动 轨 迹 ,因 此 在 最 小 误 差 方 差 准 则 下 ,当滤 波 达 到稳

定 时 ,卡 尔 曼 滤 波 更 新 预 测 的 数 据 与 真 实 数 据 相 当接 近 ,具 有 良好 的 跟

踪 效 果 。

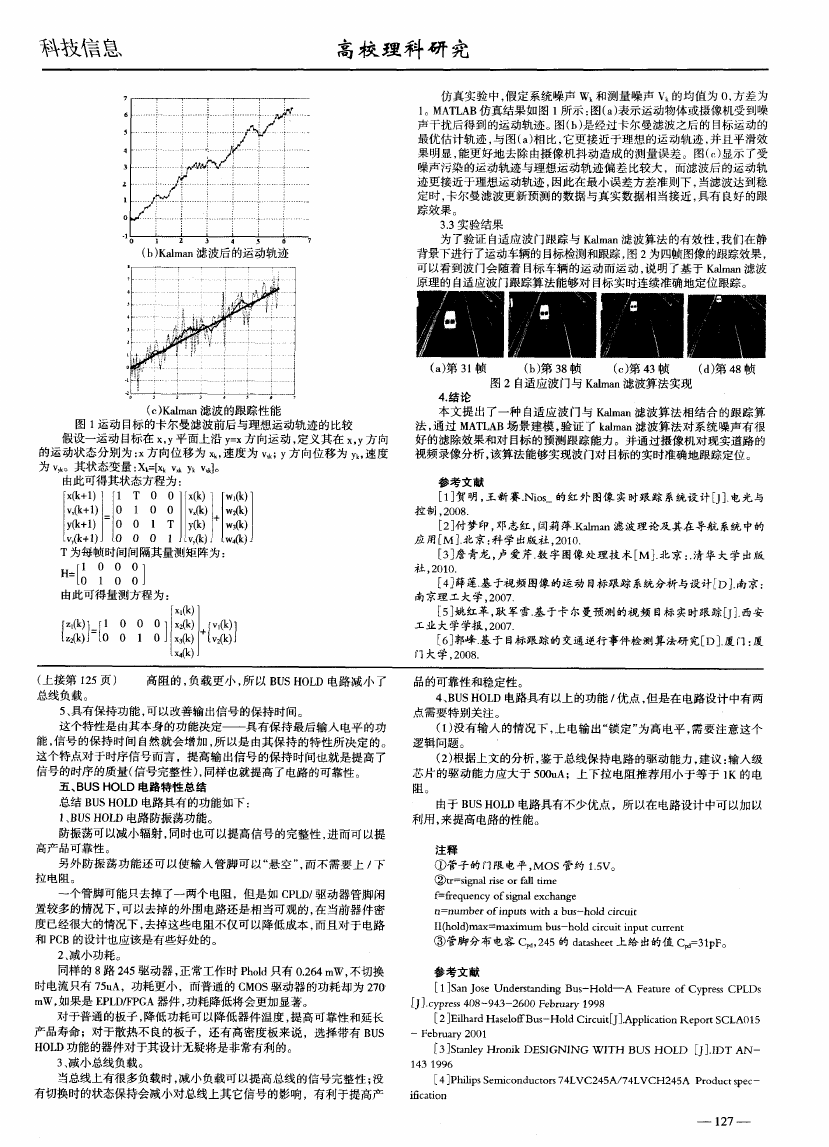

3-3实验结果

为了验证 自适应波门跟踪与 Kalman滤波算法 的有效性 ,我们在静

背景下进行了运动车辆的目标检测和跟踪,图 2为四帧图像的跟踪效果 ,

可以看 到波门会 随着 目标车辆的运动而运动 ,说 明了基 于 Kalman滤波

原理的 自适应波 门跟踪算法能够对 目标实时连续准确地定位跟踪 。

■ ■ 一 一

(a)第 3l帧

(b)第 38帧 (e)第 43帧 (d)第 48帧

图 2自适应 波门与 Kalman滤波算法实现

4.结 论

本文提 出了一种 自适应波 门与 Kalman滤波算 法相结合 的跟踪算

法 ,通过 MATLAB场景建模 ,验证 了 kalman滤波算法对系统 噪声有很

好 的 滤 除 效果 和对 目标 的 预测 跟 踪 能 力 。 并 通 过 摄 像 机 对 现 实 道 路 的

视频 录像分析 ,该算法能够实现波 门对 目标的实时准确 地跟踪定位 。

参 考 文献

[1]贺 明 ,王新赛 .Nios_的红 外图像 实时跟 踪 系统设 计[1]l电光与

控 制 2008.

[2]付梦印 ,邓志红 ,闫莉萍.Kalman滤波理论及 其在 导航 系统 中的

应 用[M].北京:科 学出版社 .2010.

[3]詹 青龙 ,卢 爱芹.数 字图像 处理技 术 [M].北 京 :.清 华大 学出版

社 .2010.

[4]薛莲.基 于视 频图像 的运 动 目标跟踪 系统分析与设计[D]南京:

南京理工大学,2007.

[5]姚红革 ,耿军雪.基 于卡 尔曼预 测的视 频 目标 实时跟踪 [1].西安

工业大学学报 ,2007.

[6]郭峰.基 于 目标跟踪的 交通逆行事件检 测算法研 究[D].厦门:厦

门大 学 ,2008.

品的可靠性和稳定性。

4、BUS HOLD电路具有 以上 的功能 /优点 ,但是在 电路设 计中有两

点需要特别关注。

(1)没有输入 的情况下 ,上 电输出“锁定 ”为高电平 ,需要 注意这个

逻 辑 问 题 。

(2)根据上文的分 析,鉴于总线保持电路的驱动能力 ,建议 :输入级

芯片的驱动 能力 应大于 500uA;上 下拉电阻推荐用 小于等 于 1K的 电

阻 。

由于 BUS HOLD电路具有不少优点 ,所以在电路设计 中可 以加 以

利用 ,来提高 电路的性能。

注释

①管子 的门限 电平 ,MOS管约 1.5V。

(~)tr=signal rise or time

f=ffequency of signal exchange

/2=number ofinputs、vjch a bus—hold circuit

II(hold)max maximum bus——hold circuit input current

③管脚分布电容 CPd,245的 datasheet上给 出的值 C =31pF。

参 考 文献

l 1 jSan Jose Understanding Bus—Hold— A Feature of Cypress CPLDs

[J]cypress 408-943—2600 February 1998

l2 JEilhard HaseloffBus—Hold Circuit[J].Apphcation~eport SCLA015

一 February 2001

【3 JStanley Hronik DESIGNING WITH BUS HOLD [『]lIDT AN一

】43 1996

[4]Philips Semiconductors 74LVc245A/74LVcH245A Product spec

jfication

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc