128Mb: x32 SDRAM

Features

SDR SDRAM

MT48LC4M32B2 – 1 Meg x 32 x 4 Banks

Features

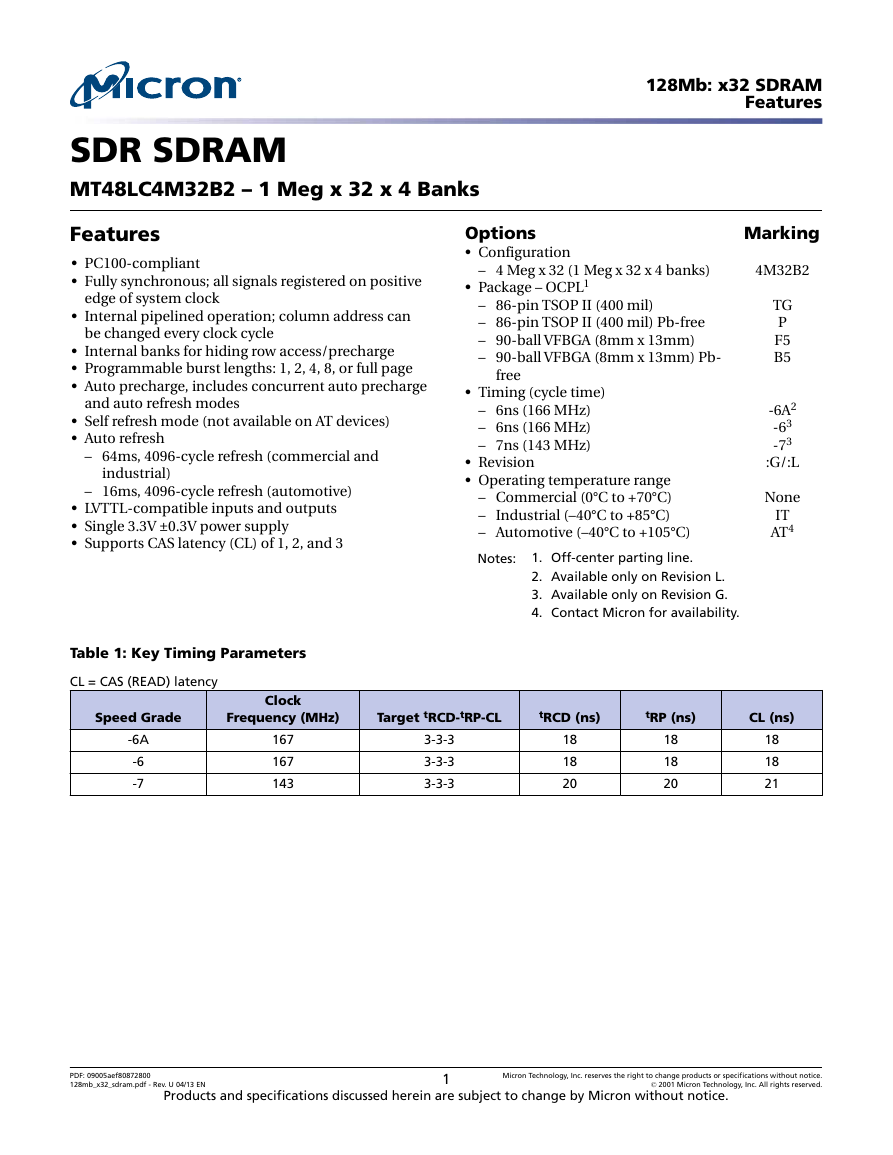

• PC100-compliant

• Fully synchronous; all signals registered on positive

edge of system clock

• Internal pipelined operation; column address can

be changed every clock cycle

• Internal banks for hiding row access/precharge

• Programmable burst lengths: 1, 2, 4, 8, or full page

• Auto precharge, includes concurrent auto precharge

and auto refresh modes

• Self refresh mode (not available on AT devices)

• Auto refresh

– 64ms, 4096-cycle refresh (commercial and

industrial)

– 16ms, 4096-cycle refresh (automotive)

• LVTTL-compatible inputs and outputs

• Single 3.3V ±0.3V power supply

• Supports CAS latency (CL) of 1, 2, and 3

Options

• Configuration

– 4 Meg x 32 (1 Meg x 32 x 4 banks)

• Package – OCPL1

– 86-pin TSOP II (400 mil)

– 86-pin TSOP II (400 mil) Pb-free

– 90-ball VFBGA (8mm x 13mm)

– 90-ball VFBGA (8mm x 13mm) Pb-

free

• Timing (cycle time)

– 6ns (166 MHz)

– 6ns (166 MHz)

– 7ns (143 MHz)

• Revision

• Operating temperature range

– Commercial (0°C to +70°C)

– Industrial (–40°C to +85°C)

– Automotive (–40°C to +105°C)

Notes:

1. Off-center parting line.

2. Available only on Revision L.

3. Available only on Revision G.

4. Contact Micron for availability.

Marking

4M32B2

TG

P

F5

B5

-6A2

-63

-73

:G/:L

None

IT

AT4

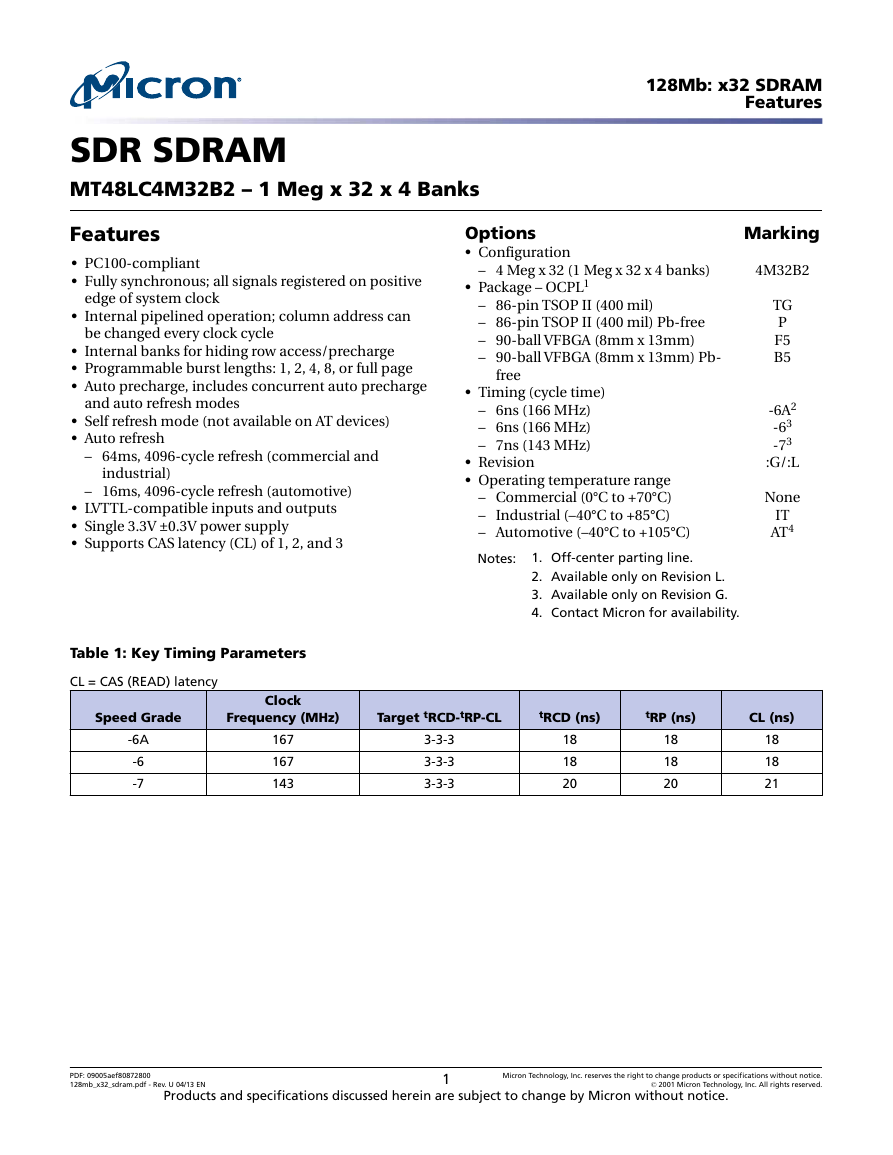

Table 1: Key Timing Parameters

CL = CAS (READ) latency

Clock

Speed Grade

Frequency (MHz)

Target tRCD-tRP-CL

tRCD (ns)

tRP (ns)

CL (ns)

-6A

-6

-7

167

167

143

3-3-3

3-3-3

3-3-3

18

18

20

18

18

20

18

18

21

PDF: 09005aef80872800

128mb_x32_sdram.pdf - Rev. U 04/13 EN

Products and specifications discussed herein are subject to change by Micron without notice.

1

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2001 Micron Technology, Inc. All rights reserved.

�

128Mb: x32 SDRAM

Features

Table 2: Address Table

Parameter

Configuration

Refresh count

Row addressing

Bank addressing

Column addressing

Table 3: 128Mb (x32) SDR Part Numbering

Part Numbers

MT48LC4M32B2TG

MT48LC4M32B2P

MT48LC4M32B2F51

MT48LC4M32B2B51

Note:

1. FBGA Device Decoder: www.micron.com/decoder.

4 Meg x 32

1 Meg x 32 x 4 banks

4K

4K A[11:0]

4 BA[1:0]

256 A[7:0]

Architecture

4 Meg x 32

4 Meg x 32

4 Meg x 32

4 Meg x 32

PDF: 09005aef80872800

128mb_x32_sdram.pdf - Rev. U 04/13 EN

2

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2001 Micron Technology, Inc. All rights reserved.

�

128Mb: x32 SDRAM

Features

Contents

General Description ......................................................................................................................................... 7

Automotive Temperature .............................................................................................................................. 7

Functional Block Diagram ................................................................................................................................ 8

Pin and Ball Assignments and Descriptions ....................................................................................................... 9

Package Dimensions ....................................................................................................................................... 12

Temperature and Thermal Impedance ............................................................................................................ 14

Electrical Specifications .................................................................................................................................. 17

Electrical Specifications – IDD Parameters ........................................................................................................ 18

Electrical Specifications – AC Operating Conditions ......................................................................................... 20

Functional Description ................................................................................................................................... 23

Commands .................................................................................................................................................... 24

COMMAND INHIBIT .................................................................................................................................. 24

NO OPERATION (NOP) ............................................................................................................................... 25

LOAD MODE REGISTER (LMR) ................................................................................................................... 25

ACTIVE ...................................................................................................................................................... 25

READ ......................................................................................................................................................... 26

WRITE ....................................................................................................................................................... 27

PRECHARGE .............................................................................................................................................. 28

BURST TERMINATE ................................................................................................................................... 28

REFRESH ................................................................................................................................................... 29

AUTO REFRESH ..................................................................................................................................... 29

SELF REFRESH ....................................................................................................................................... 29

Truth Tables ................................................................................................................................................... 30

Initialization .................................................................................................................................................. 35

Mode Register ................................................................................................................................................ 37

Burst Length .............................................................................................................................................. 39

Burst Type .................................................................................................................................................. 39

CAS Latency ............................................................................................................................................... 41

Operating Mode ......................................................................................................................................... 41

Write Burst Mode ....................................................................................................................................... 41

Bank/Row Activation ...................................................................................................................................... 42

READ Operation ............................................................................................................................................. 43

WRITE Operation ........................................................................................................................................... 52

Burst Read/Single Write .............................................................................................................................. 59

PRECHARGE Operation .................................................................................................................................. 60

Auto Precharge ........................................................................................................................................... 60

AUTO REFRESH Operation ............................................................................................................................. 72

SELF REFRESH Operation ............................................................................................................................... 74

Power-Down .................................................................................................................................................. 76

Clock Suspend ............................................................................................................................................... 77

PDF: 09005aef80872800

128mb_x32_sdram.pdf - Rev. U 04/13 EN

3

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2001 Micron Technology, Inc. All rights reserved.

�

128Mb: x32 SDRAM

Features

List of Figures

Figure 1: 4 Meg x 32 Functional Block Diagram ................................................................................................. 8

Figure 2: 86-Pin TSOP Pin Assignments (Top View) ........................................................................................... 9

Figure 3: 90-Ball FBGA Ball Assignments (Top View) ....................................................................................... 10

Figure 4: 86-Pin Plastic TSOP II (400 mil) – Package Codes TG/P ...................................................................... 12

Figure 5: 90-Ball VFBGA (8mm x 13mm) ......................................................................................................... 13

Figure 6: Example: Temperature Test Point Location, 54-Pin TSOP (Top View) ................................................. 15

Figure 7: Example: Temperature Test Point Location, 90-Ball VFBGA (Top View) .............................................. 16

Figure 8: ACTIVE Command .......................................................................................................................... 25

Figure 9: READ Command ............................................................................................................................. 26

Figure 10: WRITE Command ......................................................................................................................... 27

Figure 11: PRECHARGE Command ................................................................................................................ 28

Figure 12: Initialize and Load Mode Register .................................................................................................. 36

Figure 13: Mode Register Definition ............................................................................................................... 38

Figure 14: CAS Latency .................................................................................................................................. 41

Figure 15: Example: Meeting tRCD (MIN) When 2 < tRCD (MIN)/tCK < 3 .......................................................... 42

Figure 16: Consecutive READ Bursts .............................................................................................................. 44

Figure 17: Random READ Accesses ................................................................................................................ 45

Figure 18: READ-to-WRITE ............................................................................................................................ 46

Figure 19: READ-to-WRITE With Extra Clock Cycle ......................................................................................... 47

Figure 20: READ-to-PRECHARGE .................................................................................................................. 47

Figure 21: Terminating a READ Burst ............................................................................................................. 48

Figure 22: Alternating Bank Read Accesses ..................................................................................................... 49

Figure 23: READ Continuous Page Burst ......................................................................................................... 50

Figure 24: READ – DQM Operation ................................................................................................................ 51

Figure 25: WRITE Burst ................................................................................................................................. 52

Figure 26: WRITE-to-WRITE .......................................................................................................................... 53

Figure 27: Random WRITE Cycles .................................................................................................................. 54

Figure 28: WRITE-to-READ ............................................................................................................................ 54

Figure 29: WRITE-to-PRECHARGE ................................................................................................................. 55

Figure 30: Terminating a WRITE Burst ............................................................................................................ 56

Figure 31: Alternating Bank Write Accesses ..................................................................................................... 57

Figure 32: WRITE – Continuous Page Burst ..................................................................................................... 58

Figure 33: WRITE – DQM Operation ............................................................................................................... 59

Figure 34: READ With Auto Precharge Interrupted by a READ ......................................................................... 61

Figure 35: READ With Auto Precharge Interrupted by a WRITE ........................................................................ 62

Figure 36: READ With Auto Precharge ............................................................................................................ 63

Figure 37: READ Without Auto Precharge ....................................................................................................... 64

Figure 38: Single READ With Auto Precharge .................................................................................................. 65

Figure 39: Single READ Without Auto Precharge ............................................................................................. 66

Figure 40: WRITE With Auto Precharge Interrupted by a READ ........................................................................ 67

Figure 41: WRITE With Auto Precharge Interrupted by a WRITE ...................................................................... 67

Figure 42: WRITE With Auto Precharge ........................................................................................................... 68

Figure 43: WRITE Without Auto Precharge ..................................................................................................... 69

Figure 44: Single WRITE With Auto Precharge ................................................................................................. 70

Figure 45: Single WRITE Without Auto Precharge ............................................................................................ 71

Figure 46: Auto Refresh Mode ........................................................................................................................ 73

Figure 47: Self Refresh Mode .......................................................................................................................... 75

Figure 48: Power-Down Mode ........................................................................................................................ 76

Figure 49: Clock Suspend During WRITE Burst ............................................................................................... 77

Figure 50: Clock Suspend During READ Burst ................................................................................................. 78

PDF: 09005aef80872800

128mb_x32_sdram.pdf - Rev. U 04/13 EN

4

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2001 Micron Technology, Inc. All rights reserved.

�

Figure 51: Clock Suspend Mode ..................................................................................................................... 79

128Mb: x32 SDRAM

Features

PDF: 09005aef80872800

128mb_x32_sdram.pdf - Rev. U 04/13 EN

5

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2001 Micron Technology, Inc. All rights reserved.

�

128Mb: x32 SDRAM

Features

List of Tables

Table 1: Key Timing Parameters ....................................................................................................................... 1

Table 2: Address Table ..................................................................................................................................... 2

Table 3: 128Mb (x32) SDR Part Numbering ....................................................................................................... 2

Table 4: Pin/Ball Descriptions ........................................................................................................................ 11

Table 5: Temperature Limits .......................................................................................................................... 14

Table 6: Thermal Impedance Simulated Values ............................................................................................... 15

Table 7: Absolute Maximum Ratings .............................................................................................................. 17

Table 8: DC Electrical Characteristics and Operating Conditions ..................................................................... 17

Table 9: Capacitance ..................................................................................................................................... 17

Table 10: IDD Specifications and Conditions – Revision G ................................................................................ 18

Table 11: IDD Specifications and Conditions – Revision L ................................................................................. 18

Table 12: Electrical Characteristics and Recommended AC Operating Conditions ............................................ 20

Table 13: AC Functional Characteristics ......................................................................................................... 21

Table 14: Truth Table – Commands and DQM Operation ................................................................................. 24

Table 15: Truth Table – Current State Bank n, Command to Bank n .................................................................. 30

Table 16: Truth Table – Current State Bank n, Command to Bank m ................................................................. 32

Table 17: Truth Table – CKE ........................................................................................................................... 34

Table 18: Burst Definition Table ..................................................................................................................... 40

PDF: 09005aef80872800

128mb_x32_sdram.pdf - Rev. U 04/13 EN

6

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2001 Micron Technology, Inc. All rights reserved.

�

General Description

128Mb: x32 SDRAM

General Description

The 64Mb SDRAM is a high-speed CMOS, dynamic random-access memory containing

134,217,728 bits. It is internally configured as a quad-bank DRAM with asynchronous

interface (all signals are registered on the positive edge of the clock signal, CLK). Each of

the 33,554,432-bit banks is organized as 4096 rows by 256 columns by 32 bits.

Read and write accesses to the SDRAM are burst oriented; accesses start at a selected

location and continue for a programmed number of locations in a programmed se-

quence. Accesses begin with the registration of an ACTIVE command, which is then fol-

lowed by a READ or WRITE command. The address bits registered coincident with the

ACTIVE command are used to select the bank and row to be accessed (BA[1:0] select the

bank; A[11:0] select the row).The address bits registered coincident with the READ or

WRITE command are used to select the starting column location for the burst access.

The SDRAM provides for programmable read or write burst lengths (BL) of 1, 2, 4, or 8

locations, or the full page, with a burst terminate option. An auto precharge function

may be enabled to provide a self-timed row precharge that is initiated at the end of the

burst sequence.

The 64Mb SDRAM uses an internal pipelined architecture to achieve high-speed opera-

tion. This architecture is compatible with the 2n rule of prefetch architectures, but it al-

so allows the column address to be changed on every clock cycle to achieve a high-

speed, fully random access. Precharging one bank while accessing one of the other

three banks will hide the precharge cycles and provide seamless, high-speed, random-

access operation.

The 64Mb SDRAM is designed to operate in 3.3V memory systems. An auto refresh

mode is provided, along with a power-saving, power-down mode. All inputs and out-

puts are LVTTL-compatible.

The devices offer substantial advances in DRAM operating performance, including the

ability to synchronously burst data at a high data rate with automatic column-address

generation, the ability to interleave between internal banks to hide precharge time, and

the capability to randomly change column addresses on each clock cycle during a burst

access.

Automotive Temperature

The automotive temperature (AT) option adheres to the following specifications:

• 16ms refresh rate

• Self refresh not supported

• Ambient and case temperature cannot be less than –40°C or greater than 105°C

PDF: 09005aef80872800

128mb_x32_sdram.pdf - Rev. U 04/13 EN

7

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2001 Micron Technology, Inc. All rights reserved.

�

128Mb: x32 SDRAM

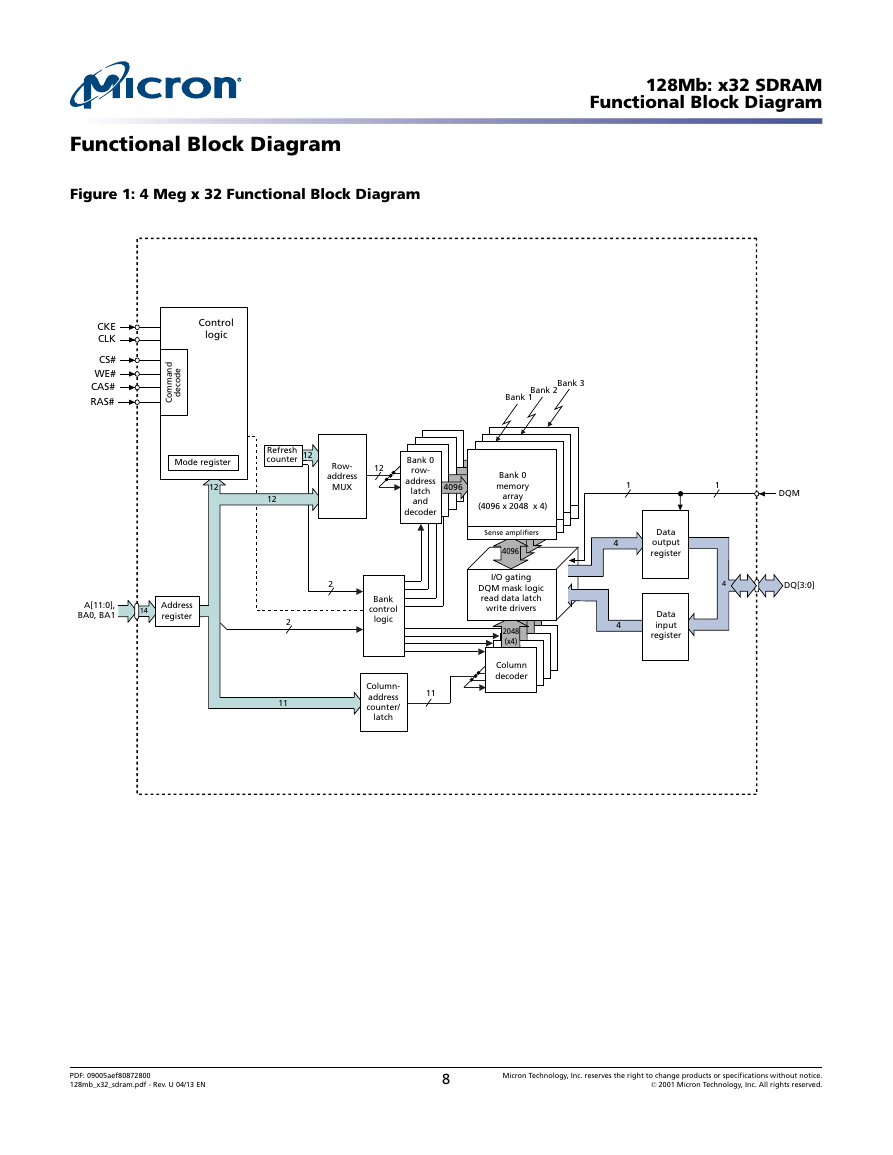

Functional Block Diagram

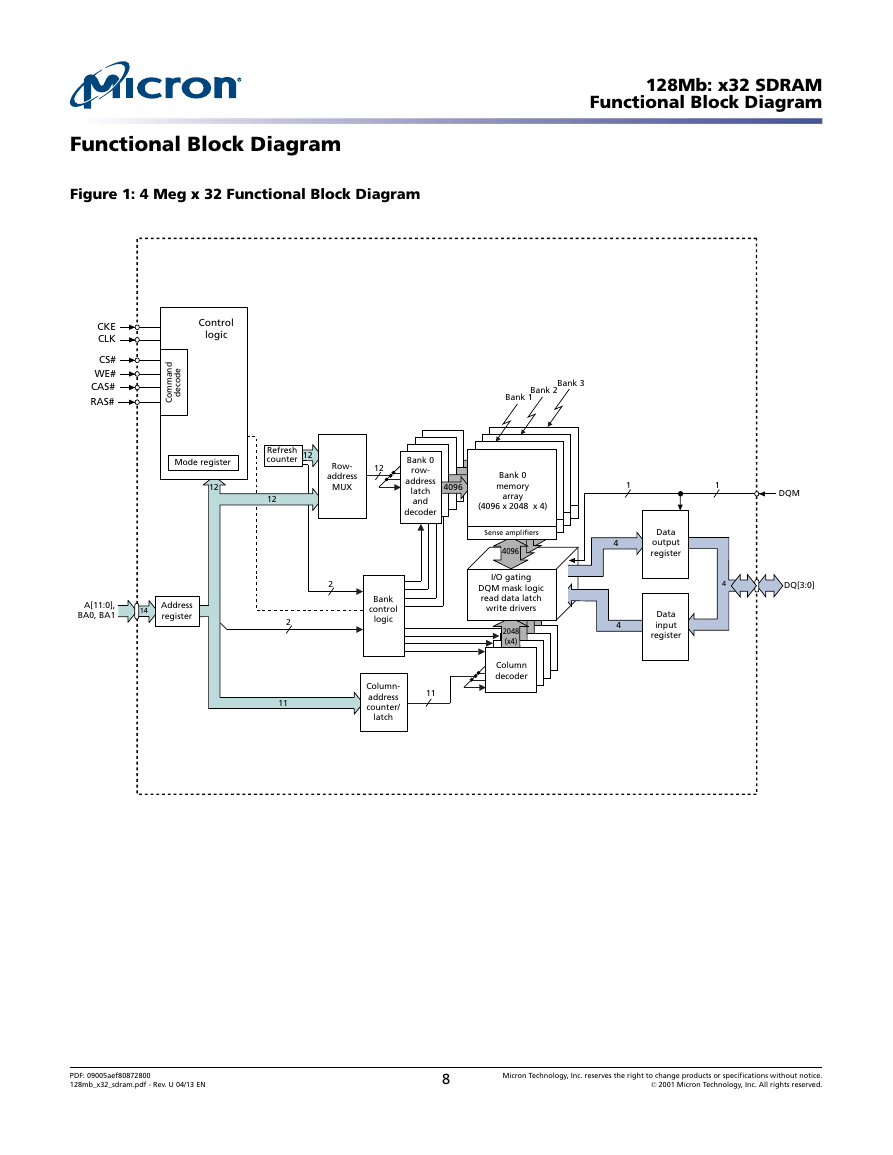

Functional Block Diagram

Figure 1: 4 Meg x 32 Functional Block Diagram

CKE

CLK

CS#

WE#

CAS#

RAS#

Control

logic

d

n

a

m

m

o

C

e

d

o

c

e

d

Bank 3

Bank 2

Bank 1

Mode register

Refresh

counter

12

12

12

12

Row-

address

MUX

Bank 0

row-

address

latch

and

decoder

4096

Bank 0

memory

array

(4096 x 2048 x 4)

1

1

DQM

A[11:0],

BA0, BA1

14

Address

register

2

Bank

control

logic

Column-

address

counter/

latch

11

2

11

Sense amplifiers

4096

I/O gating

DQM mask logic

read data latch

write drivers

2048

(x4)

Column

decoder

4

4

Data

output

register

Data

input

register

4

DQ[3:0]

PDF: 09005aef80872800

128mb_x32_sdram.pdf - Rev. U 04/13 EN

8

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2001 Micron Technology, Inc. All rights reserved.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc