Document Number ENG-46158

Revision

Revision 1.7

Author

Yi-Chin Chu

Project Manager

JR Rivers

Serial-GMII Specification

The Serial Gigabit Media Independent Interface (SGMII) is designed to satisfy the following

requirements:

•

•

Convey network data and port speed between a 10/100/1000 PHY and a MAC with

significantly less signal pins than required for GMII.

Operate in both half and full duplex and at all port speeds.

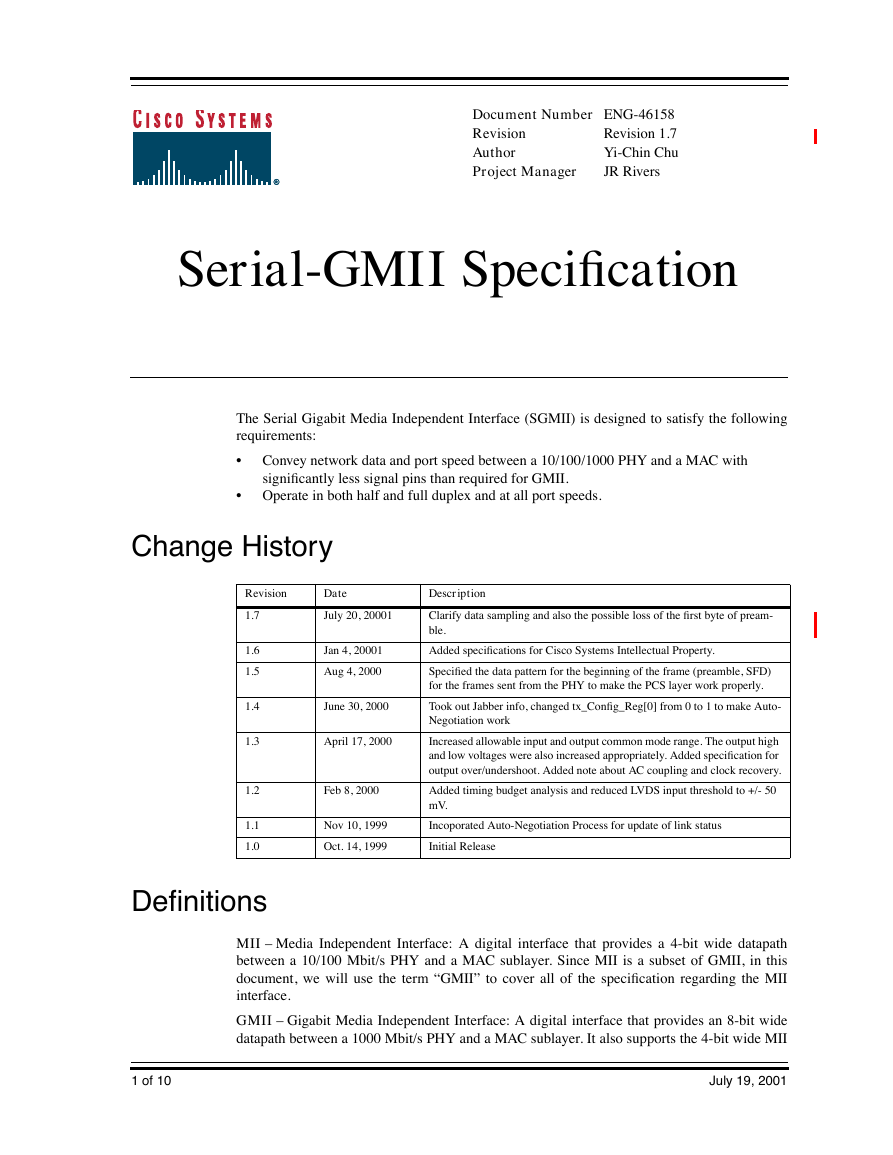

Change History

Revision

Date

Description

1.7

1.6

1.5

1.4

1.3

1.2

1.1

1.0

July 20, 20001

Jan 4, 20001

Aug 4, 2000

June 30, 2000

April 17, 2000

Feb 8, 2000

Nov 10, 1999

Oct. 14, 1999

Clarify data sampling and also the possible loss of the first byte of pream-

ble.

Added specifications for Cisco Systems Intellectual Property.

Specified the data pattern for the beginning of the frame (preamble, SFD)

for the frames sent from the PHY to make the PCS layer work properly.

Took out Jabber info, changed tx_Config_Reg[0] from 0 to 1 to make Auto-

Negotiation work

Increased allowable input and output common mode range. The output high

and low voltages were also increased appropriately. Added specification for

output over/undershoot. Added note about AC coupling and clock recovery.

Added timing budget analysis and reduced LVDS input threshold to +/- 50

mV.

Incoporated Auto-Negotiation Process for update of link status

Initial Release

Definitions

MII – Media Independent Interface: A digital interface that provides a 4-bit wide datapath

between a 10/100 Mbit/s PHY and a MAC sublayer. Since MII is a subset of GMII, in this

document, we will use the term “GMII” to cover all of the specification regarding the MII

interface.

GMII – Gigabit Media Independent Interface: A digital interface that provides an 8-bit wide

datapath between a 1000 Mbit/s PHY and a MAC sublayer. It also supports the 4-bit wide MII

1 of 10

July 19, 2001

�

Serial-GMII Specification: ENG-46158

Revision 1.7

interface as defined in the IEEE 802.3z specification. In this document, the term “GMII”

covers all 10/100/1000 Mbit/s interface operations.

2 of 10

July 19, 2001

�

Overview

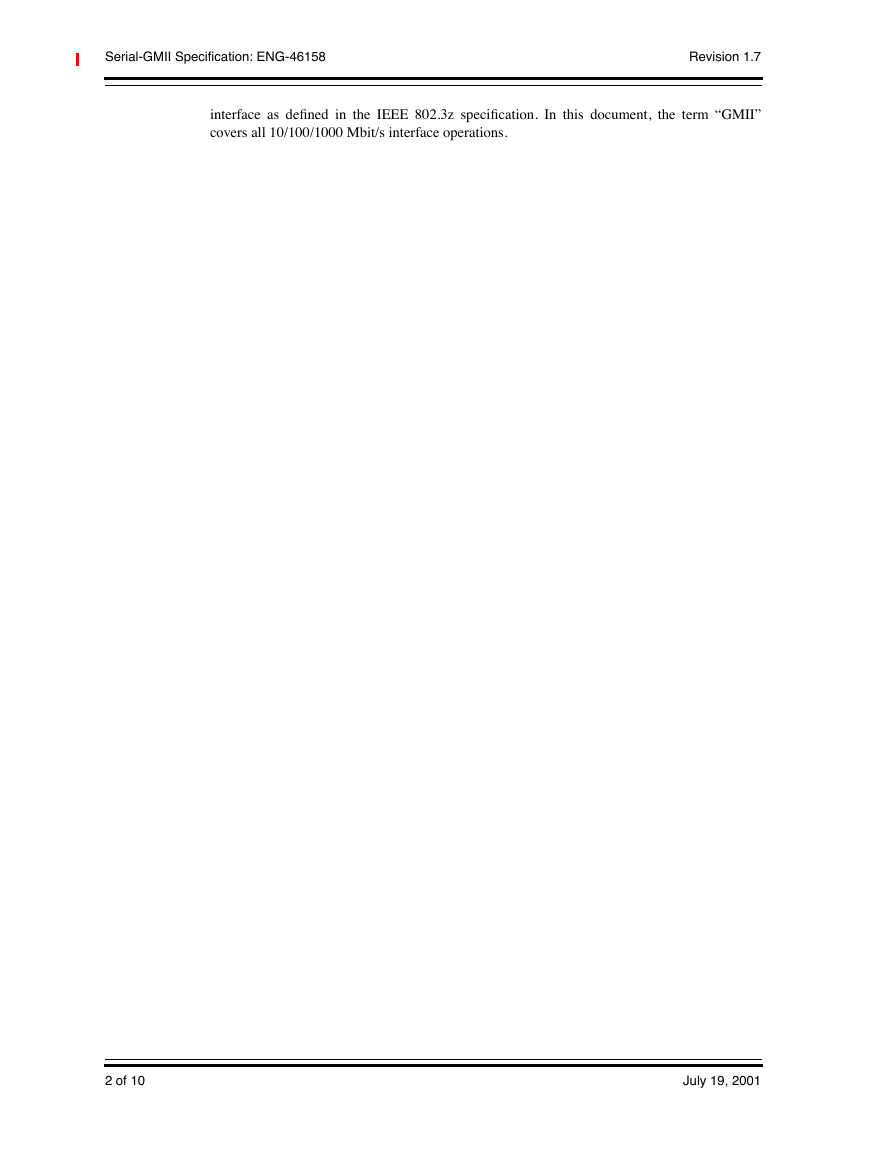

SGMII uses two data signals and two clock signals to convey frame data and link rate

information between a 10/100/1000 PHY and an Ethernet MAC. The data signals operate at

1.25 Gbaud and the clocks operate at 625 MHz (a DDR interface). Due to the speed of

operation, each of these signals is realized as a differential pair thus providing signal integrity

while minimizing system noise.

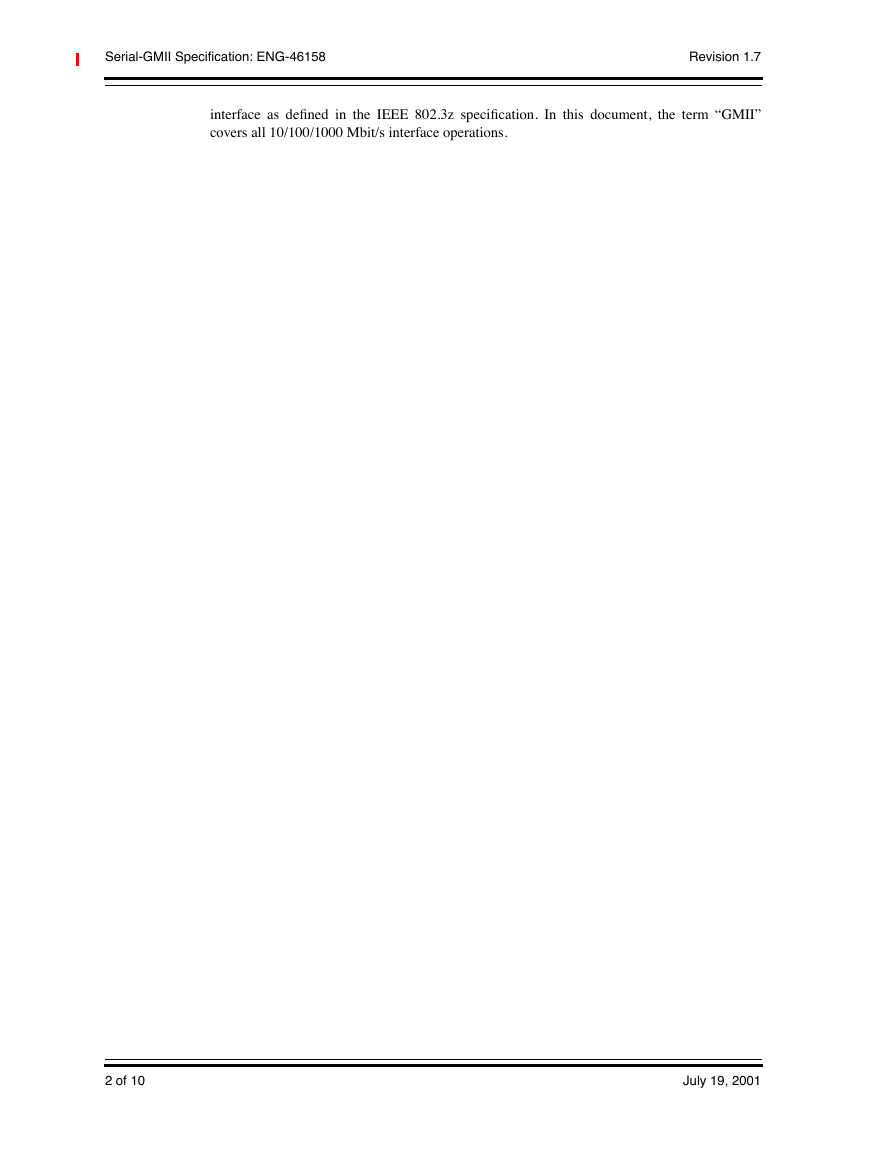

Figure 1 illustrates the simple connections in a system utilizing SGMII.

MAC

PHY

CRS

RX_DV

RX_ER

RXD[7:0]

RX_CLK

COL

TX_EN

TX_ER

TXD[7:0]

TX_CLK

GTX_CLK

8

8

802.3z

Receive

PCS

S

y

n

c

h

8

0

2

.

3

z

802.3z Auto-Negotiation

802.3z

Transmit

PCS

RX

RXCLK

TX

TXCLK

802.3z

Transmit

PCS

802.3z Auto-Negotiation

S

y

n

c

h

8

0

2

.

3

z

802.3z

Receive

PCS

CRS

RX_DV

RX_ER

RXD[7:0]

RX_CK

COL

TX_EN

TX_ER

TXD[7:0]

TX_CLK

GTX_CLK

8

8

Figure 1

SGMII Connectivity

The transmit and receive data paths leverage the 1000BASE-SX PCS defined in the IEEE

802.3z specification (clause 36). The traditional GMII data signals (TXD/RXD), data valid

signals (TX_EN/RX_DV), and error signals (TX_ER/RX_ER) are encoded, serialized and

output with the appropriate DDR clocking. Thus it is a 1.25 Gbaud interface with a 625 MHz

clock. Carrier Sense (CRS) is derived/inferred from RX_DV, and collision (COL) is logically

derived in the MAC when RX_DV and TX_EN are simultaneously asserted.

Control information, as specified in Table 1, is transferred from the PHY to the MAC to signal

the change of the control information. This is achieved by using the Auto-Negotiation

functionality defined in Clause 37 of the IEEE Specification 802.3z. Instead of the ability

advertisement, the PHY sends the control information via its tx_config_Reg[15:0] as specified

in Table 1 whenever the control information changes. Upon receiving control information, the

MAC acknowledges the update of the control

information by asserting bit 14 of its

tx_config_reg{15:0] as specified in Table 1.

SGMII details source synchronous clocking; however, specific implementations may desire to

recover clock from the data rather than use the supplied clock. This operation is allowed;

however, all sources of data must generate the appropriate clock regardless of how they clock

receive data.

3 of 10

July 19, 2001

�

Serial-GMII Specification: ENG-46158

Revision 1.7

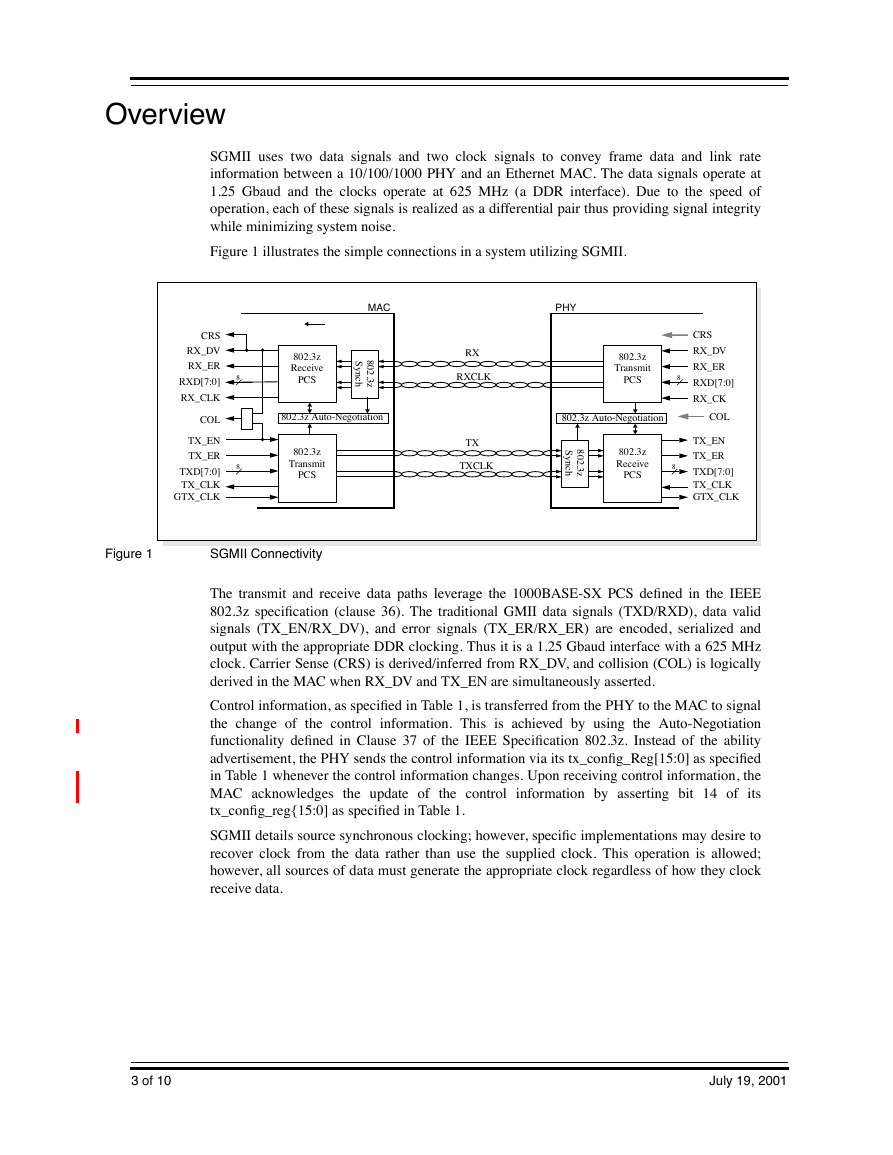

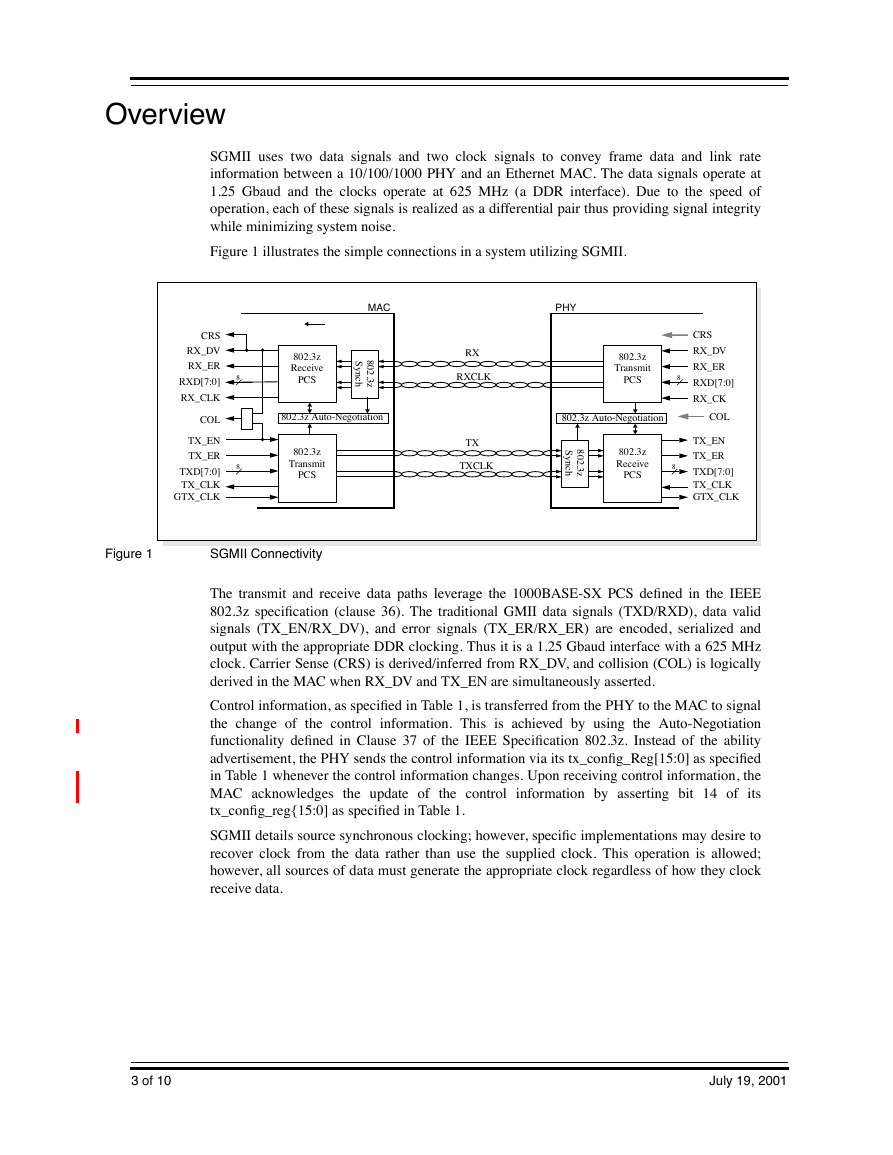

The link_timer inside the Auto-Negotiation has been changed from 10 msec to 1.6 msec to

ensure a prompt update of the link status.

Bit Number

tx_config_Reg[15:0] sent from the PHY to the

MAC

tx_config_Reg[15:0] sent from

the MAC to the PHY

15

14

13

12

11:10

9:1

0

Link: 1 = link up, 0 = link down

0: Reserved for future use

Reserved for Auto-Negotiation acknowledge as

specified in 802.3z

1

0: Reserved for future use

0: Reserved for future use

Duplex mode: 1 = full duplex, 0 = half duplex

0: Reserved for future use

Speed: Bit 11, 10:

1 1 = Reserved

1 0 = 1000 Mbps: 1000BASE-TX, 1000BASE-X

0 1 = 100 Mbps: 100BASE-TX, 100BASE-FX

0 0 = 10 Mbps: 10BASET, 10BASE2, 10BASE5

0: Reserved for future use

0: Reserved for future use

0: Reserved for future use

1

1

table 1

Definition of Control Information passed between links via tx_config_Reg[15:0]

Clearly, SGMII’s 1.25 Gbaud transfer rate is excessive for interfaces operating at 10 or 100

Mbps. When these situations occur, the interface “elongates” the frame by replicating each

frame byte 10 times for 100 Mbps and 100 types for 10 Mbps. This frame elongation takes

place “above” the 802.3z PCS layer, thus the start frame delimiter only appears once per frame.

The 802.3z PCS layer may remove the first byte of the “elongated” frame.

4 of 10

July 19, 2001

�

Implementation Specification

This section discusses how this SGMII interface shall be implemented by incorporating and

modifying the PCS layer of the IEEE Specification 802.3z.

Signal Mapping at the PHY side

Figure 2 shows the PHY functional block diagram. It illustrates how the PCS layer shall be

modified and incorporated at the PHY side in the SGMII interface.

MAC

PHY

PCS Layer from 802.3z Figure 36-2

CRS

RX

RXCLK

Seri-

alizer

ENC_RXD[0:9]

10

RX

RXCLK

PCS Transmit

State Machine

from 802.3z

Figure 36-5,

Figure 36-6

TX_EN

TX_ER

TXD[7:0]

TX_CLK

Auto-Negotiation

Figure 37-6

TX

TXCLK

ENC_TXD[0:9]

Deseri-

alizer

10

Synchronization

Figure 36-9

PCS Receive

State Machine

from 802.3z

Figure 36-7

RX_DV

RX_ER

RXD[7:0]

RX_CLK

RX_DV

RX_ER

RXD[7:0]

RX_CLK @

125 MHz

PHY Receive

Rate Adaptation

GMII Signals from

10/100/1000PHY

RX_CLK @

2.5/25/125 MHz

PHY Transmit

Rate Adaptation

GMII Signals to

10/100/1000PHY

TX_CLK @

2.5/25/125 MHz

TX_EN

TX_ER

TXD[7:0]

TX_CLK @

125 MHz

COL

Figure 2

PHY Functional Block

At the receive side, GMII signals come in at 10/100/1000 Mbps clocked at 2.5/25/125 MHz.

The PHY passes these signals through the PHY Receive Rate Adaptation to output the 8-bit

data RXD[7:0] in 125MHz clock domain. RXD is sent to the PCS Transmit State Machine to

generate an encoded 10-bit segment ENC_RXD[0:9]. The PHY serializes ENC_RXD[0:9] to

create RX and sends it to the MAC at 1.25 Gbit/s data rate along with the 625 MHz DDR

RXCLK.

At the transmit side, the PHY deserializes TX to recover encoded ENC_TXD[0:9]. The PHY

passes ENC_TXD[0:9] through the PCS Receive State Machine to recover the GMII signals.

In the mean time, Synchronization block checks ENC_TXD[0:9]

to determine the

synchronization status between links, and to realign if it detects the loss of synchronization.

5 of 10

July 19, 2001

�

Serial-GMII Specification: ENG-46158

Revision 1.7

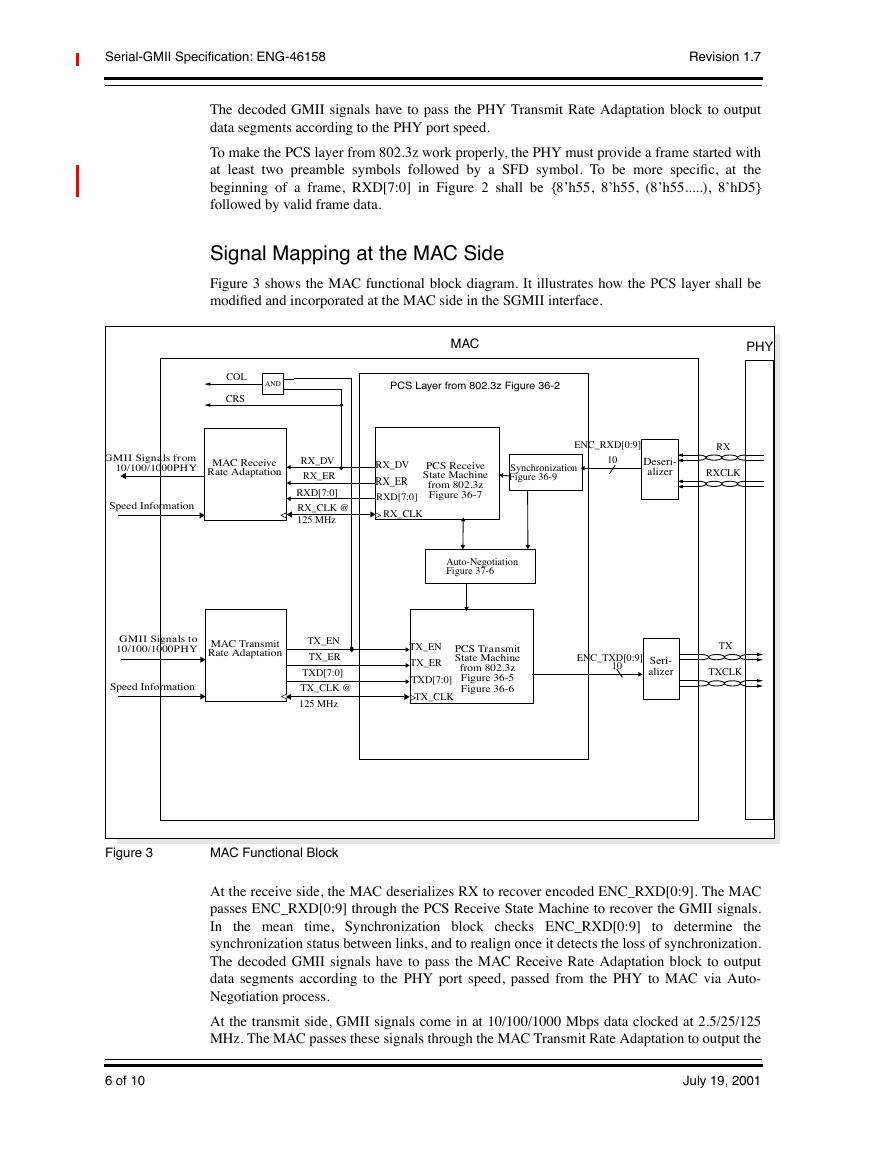

The decoded GMII signals have to pass the PHY Transmit Rate Adaptation block to output

data segments according to the PHY port speed.

To make the PCS layer from 802.3z work properly, the PHY must provide a frame started with

at least two preamble symbols followed by a SFD symbol. To be more specific, at the

beginning of a frame, RXD[7:0] in Figure 2 shall be {8’h55, 8’h55, (8’h55.....), 8’hD5}

followed by valid frame data.

Signal Mapping at the MAC Side

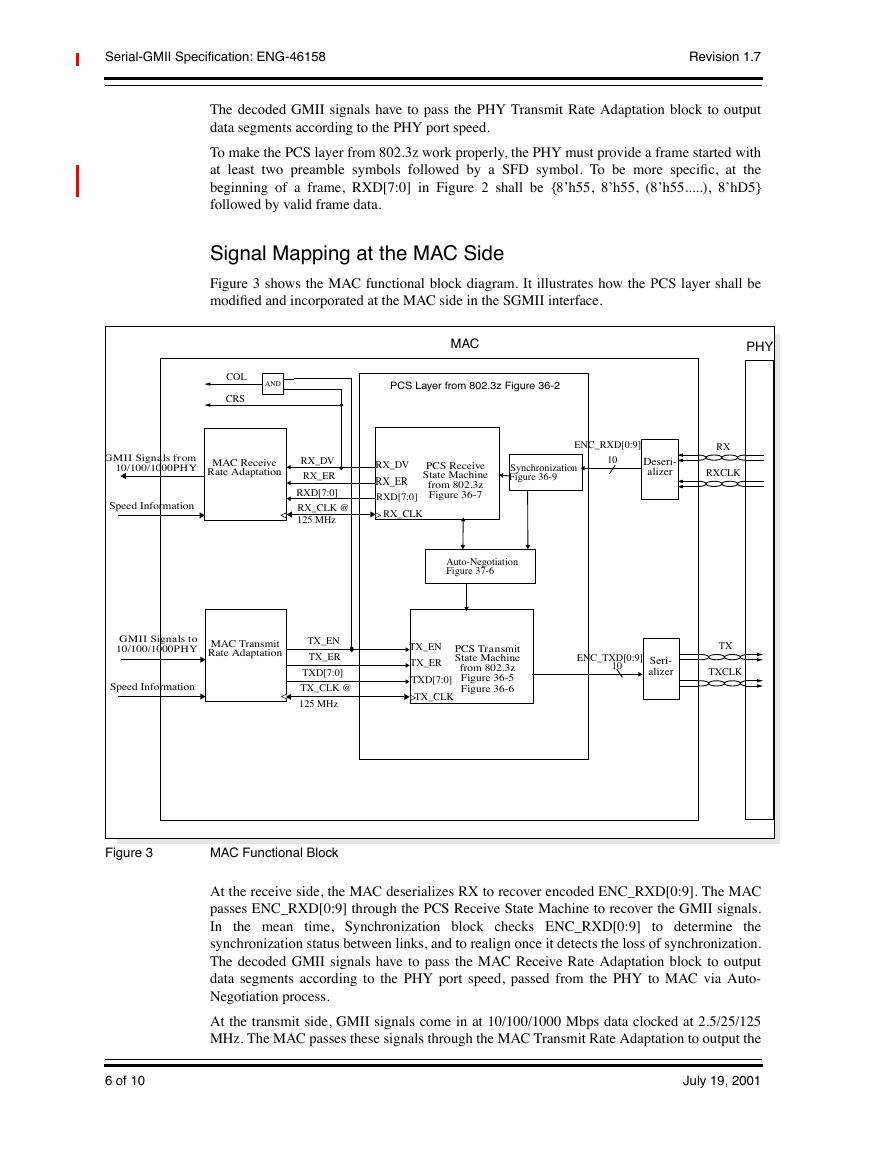

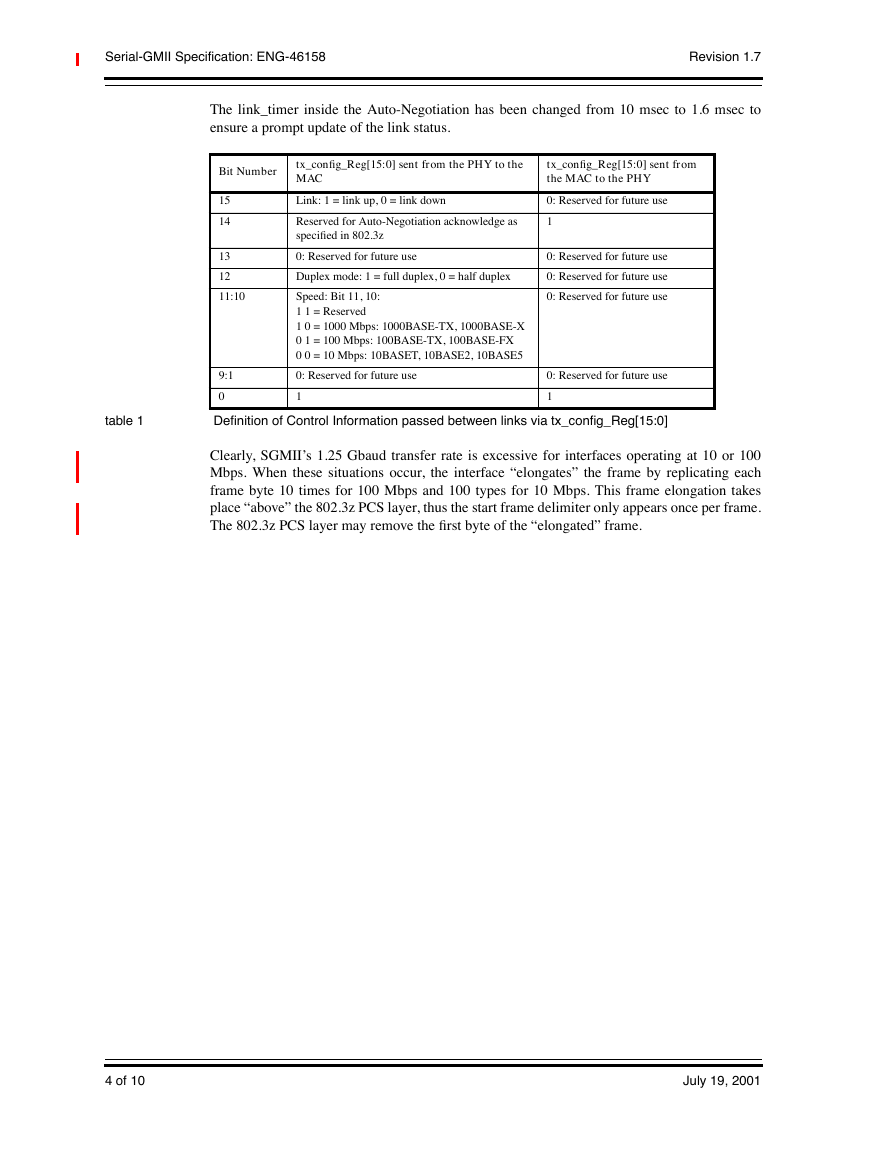

Figure 3 shows the MAC functional block diagram. It illustrates how the PCS layer shall be

modified and incorporated at the MAC side in the SGMII interface.

MAC

PHY

COL

CRS

AND

PCS Layer from 802.3z Figure 36-2

GMII Signals from

10/100/1000PHY MAC Receive

Rate Adaptation

Speed Information

RX_DV

RX_ER

RXD[7:0]

RX_CLK @

125 MHz

PCS Receive

State Machine

from 802.3z

Figure 36-7

RX_DV

RX_ER

RXD[7:0]

RX_CLK

ENC_RXD[0:9]

Synchronization

Figure 36-9

10

Deseri-

alizer

RX

RXCLK

Auto-Negotiation

Figure 37-6

GMII Signals to

10/100/1000PHY MAC Transmit

Rate Adaptation

Speed Information

TX_EN

TX_ER

TXD[7:0]

TX_CLK @

125 MHz

TX_EN

TX_ER

TXD[7:0]

TX_CLK

PCS Transmit

State Machine

from 802.3z

Figure 36-5

Figure 36-6

ENC_TXD[0:9]

10

Seri-

alizer

TX

TXCLK

Figure 3

MAC Functional Block

At the receive side, the MAC deserializes RX to recover encoded ENC_RXD[0:9]. The MAC

passes ENC_RXD[0:9] through the PCS Receive State Machine to recover the GMII signals.

In the mean time, Synchronization block checks ENC_RXD[0:9]

to determine the

synchronization status between links, and to realign once it detects the loss of synchronization.

The decoded GMII signals have to pass the MAC Receive Rate Adaptation block to output

data segments according to the PHY port speed, passed from the PHY to MAC via Auto-

Negotiation process.

At the transmit side, GMII signals come in at 10/100/1000 Mbps data clocked at 2.5/25/125

MHz. The MAC passes these signals through the MAC Transmit Rate Adaptation to output the

6 of 10

July 19, 2001

�

8-bit data TXD[7:0] in 125MHz clock domain. TXD is sent to the PCS Transmit State

Machine to generate an encoded 10-bit segment ENC_TXD[0:9]. The MAC serializes

ENC_TXD[0:9] to create TX and sends it to the PHY at 1.25 Gbit/s data rate along with the

625 MHz DDR TXCLK.

Control Information Exchanged Between Links

As described in Overview, it is necessary for the PHY to pass control information to the MAC

to notify the change of the link status. SGMII interface uses Auto-Negotiation block to pass the

control information via tx_config_Reg[15:0].

If the PHY detects the control information change, it starts its Auto-Negotiation process,

switching its Transmit block from “data” to “configuration” state and sending out the updated

control information via tx_config_Reg[15:0]. The Receive block in the MAC receives and

decodes control information, and starts the MAC’s Auto-Negotiation process. The Transmit

block in the MAC acknowledges the update of link status via tx_config_Reg[15:0] with bit 14

asserted, as specified in Table 1. Upon receiving the acknowledgement from the MAC, the

PHY completes the auto-negotiation process and returns to the normal data process.

As specified in Overview, inside the SGMII interface, the Auto-Negotiation link_timer has

been changed from 10 msec to 1.6 msec, ensuring a prompt update of the link status. The

expected latency for the update of link is 3.4 msec (two link_timer time + an acknowledgement

process).

Data Information Transferred Between Links

Below we briefly describe at receive side how GMII signals get transferred across from the

PHY and recovered at the MAC by using the 8B/10B transmission code. The same method

applies to the transmit side.

According to the assertion and deassertion of RX_DV, the PHY encodes the Start_of_Packet

delimiter (SPD /S/) and the End_Of_Packet delimiter (EPD) to signal the beginning and end of

each packet. The MAC recovers RX_DV signal by detecting these two delimiters.

The PHY encodes the Error_Propagation(/V/) ordered_set to indicate a data transmission error.

The MAC asserts RX_ER signal whenever it detects this ordered_set.

CRS is not directly encoded and passed to the MAC. To regenerate CRS, the MAC shall uses

signal RX_DV before it is being passed to the MAC Receive Rate Adaptation block as shown

in Figure 3.

The MAC decodes ENC_RXD[0:9] to recover RXD[7:0].

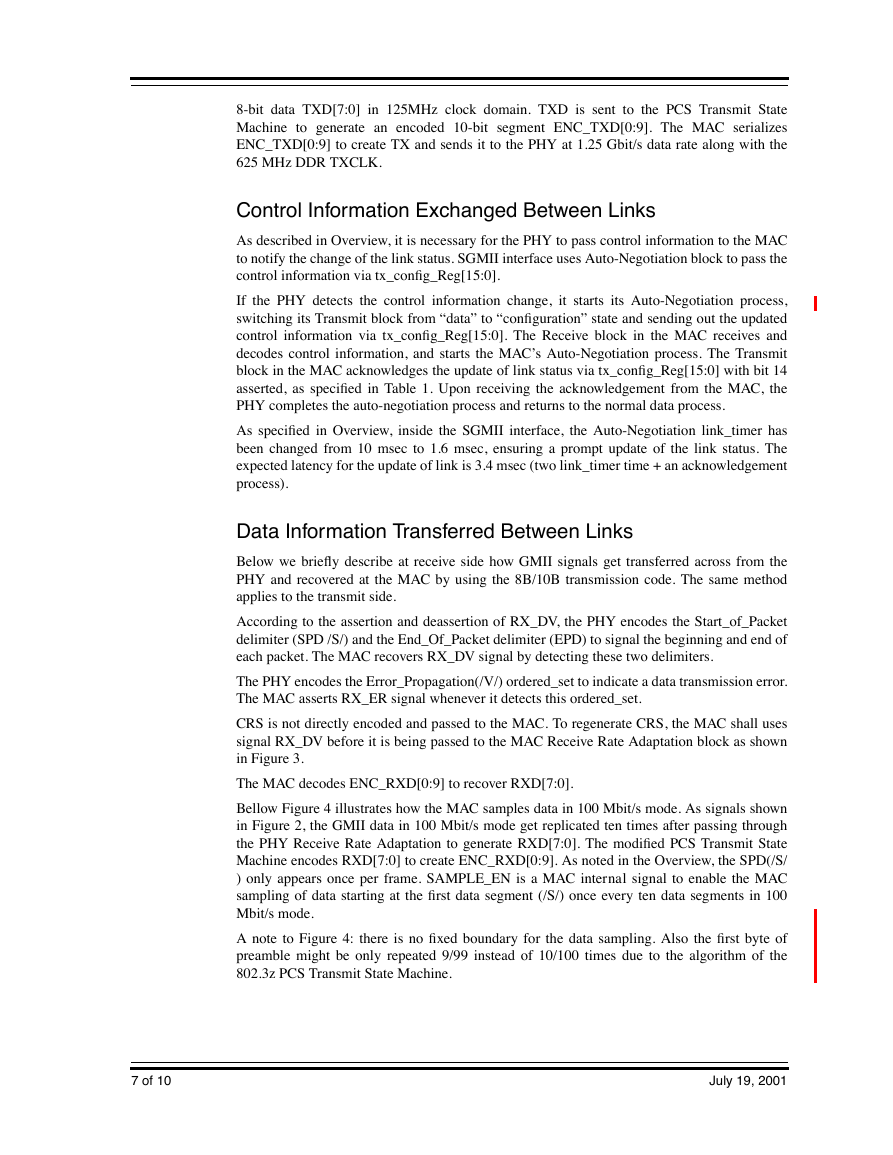

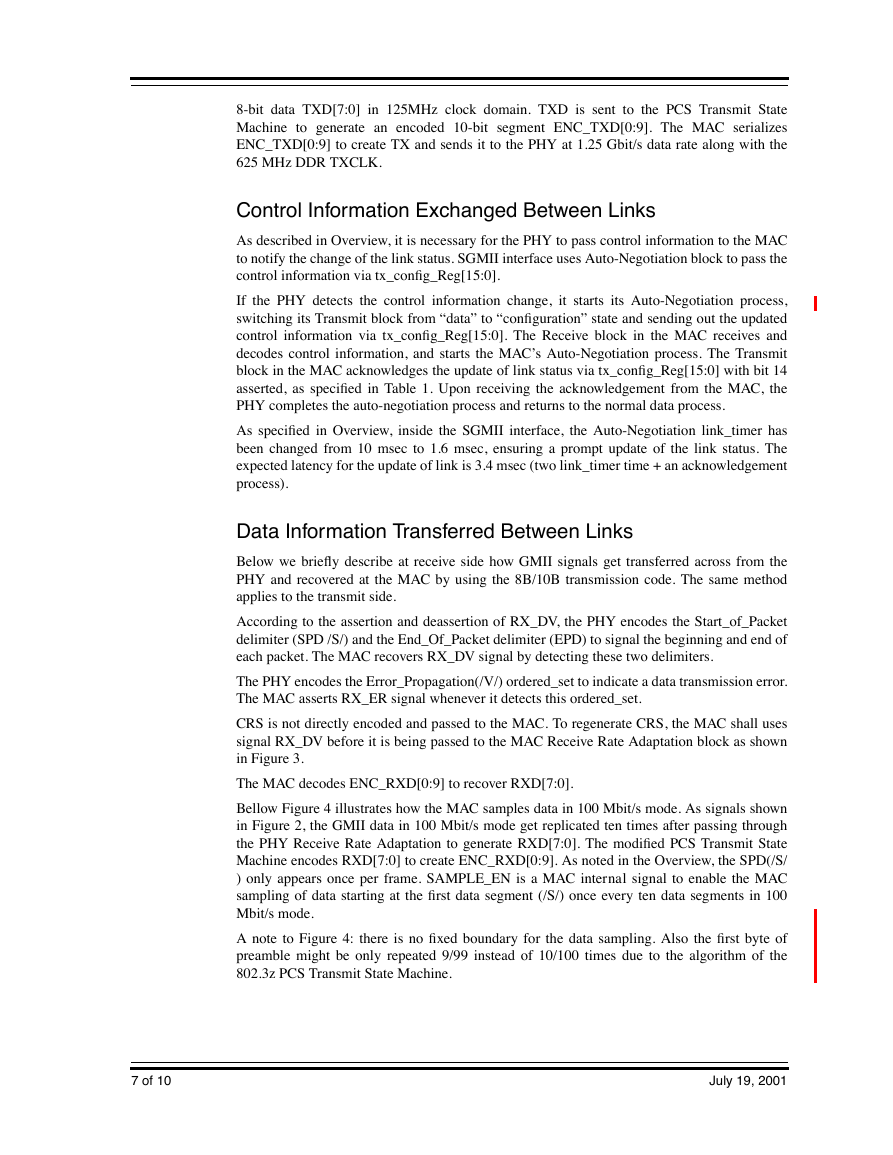

Bellow Figure 4 illustrates how the MAC samples data in 100 Mbit/s mode. As signals shown

in Figure 2, the GMII data in 100 Mbit/s mode get replicated ten times after passing through

the PHY Receive Rate Adaptation to generate RXD[7:0]. The modified PCS Transmit State

Machine encodes RXD[7:0] to create ENC_RXD[0:9]. As noted in the Overview, the SPD(/S/

) only appears once per frame. SAMPLE_EN is a MAC internal signal to enable the MAC

sampling of data starting at the first data segment (/S/) once every ten data segments in 100

Mbit/s mode.

A note to Figure 4: there is no fixed boundary for the data sampling. Also the first byte of

preamble might be only repeated 9/99 instead of 10/100 times due to the algorithm of the

802.3z PCS Transmit State Machine.

7 of 10

July 19, 2001

�

Serial-GMII Specification: ENG-46158

Revision 1.7

125 MHz Clock

RX_DV

Data in 100 Mbit/s

Domain

RXD[7:0] after

Rate Adaptation

ENC_RXD[0:9]

SAMPLE_EN

Data0

Data1

Data2

D0 D0 D0 D0 D0 D0 D0 D0 D0 D0 D1 D1 D1 D1 D1 D1 D1 D1 D1 D1 D2 D2 D2 D2 D2 D2 D2 D2 D2

/S/

d0

d0

d0

d0

d0

d0

d0

d0

d0

d1

d1

d1

d1

d1

d1

d1

d1

d1

d1

d2

d2

d2

d2

d2

d2

d2

d2

d2

Figure 4

Data Sampling in 100 Mbit/s mode

LVDS AC/DC Specification

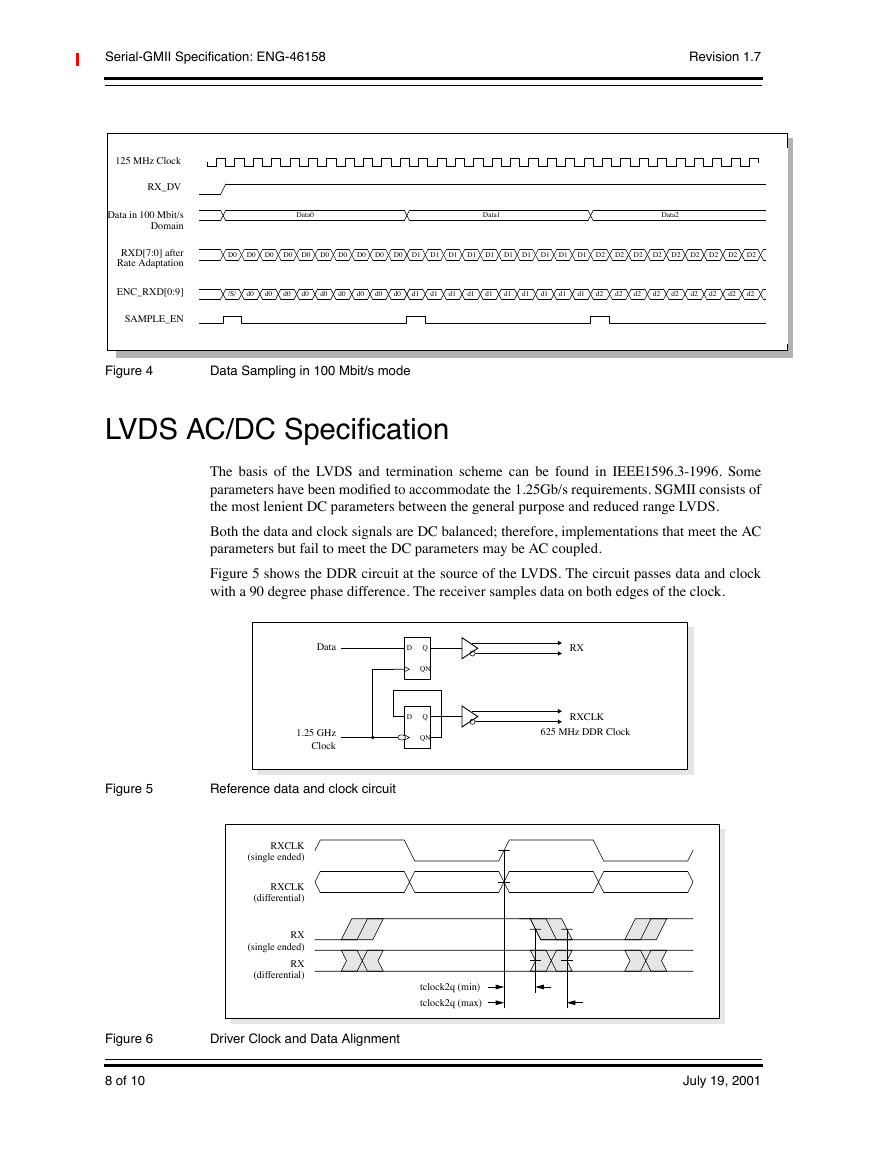

The basis of the LVDS and termination scheme can be found in IEEE1596.3-1996. Some

parameters have been modified to accommodate the 1.25Gb/s requirements. SGMII consists of

the most lenient DC parameters between the general purpose and reduced range LVDS.

Both the data and clock signals are DC balanced; therefore, implementations that meet the AC

parameters but fail to meet the DC parameters may be AC coupled.

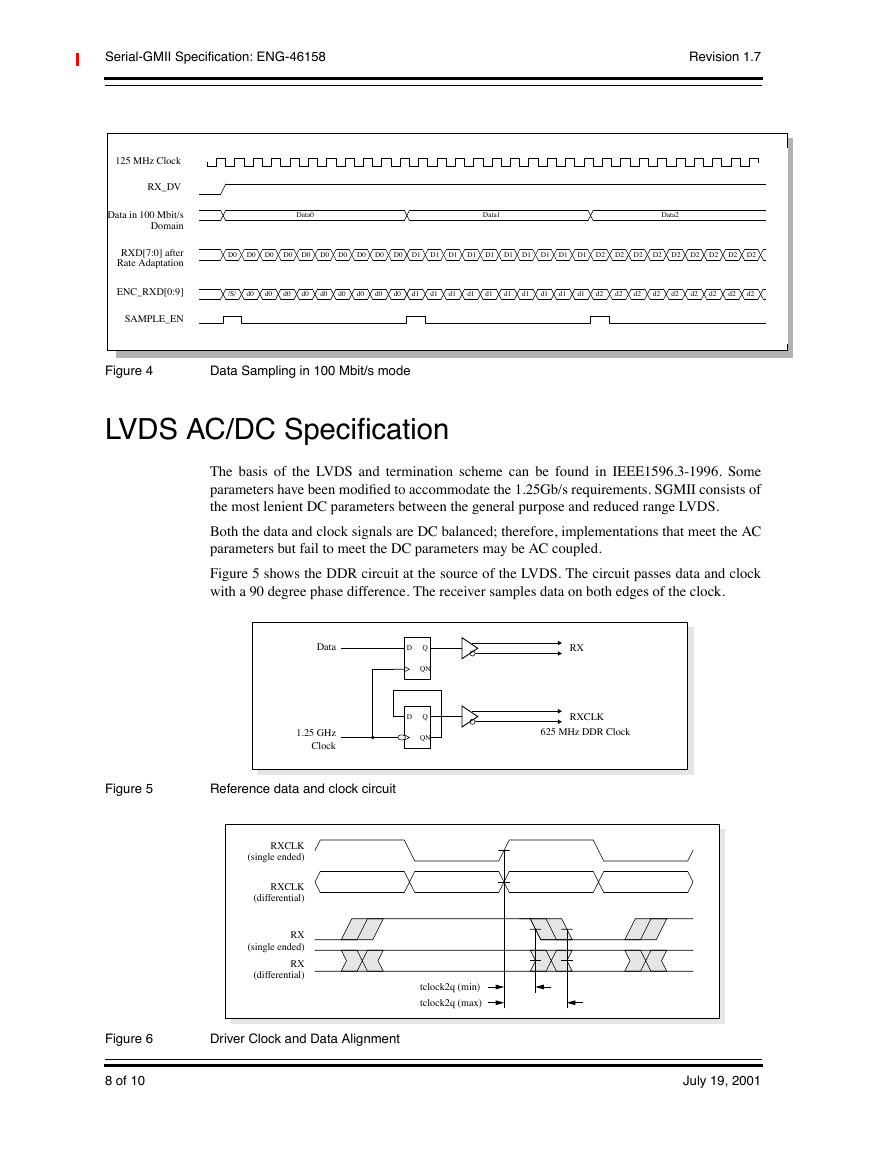

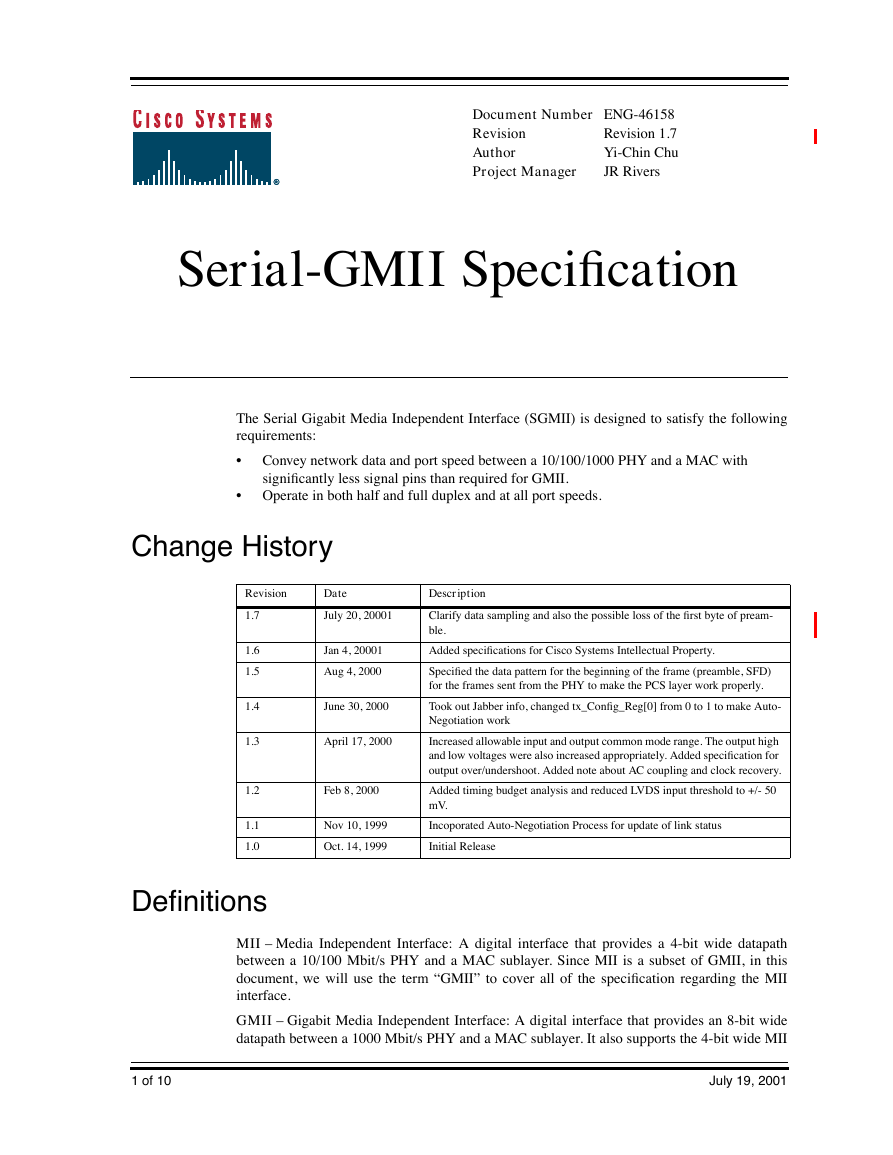

Figure 5 shows the DDR circuit at the source of the LVDS. The circuit passes data and clock

with a 90 degree phase difference. The receiver samples data on both edges of the clock.

Data

1.25 GHz

Clock

D Q

QN

D Q

QN

RX

RXCLK

625 MHz DDR Clock

Figure 5

Reference data and clock circuit

RXCLK

(single ended)

RXCLK

(differential)

RX

(single ended)

RX

(differential)

Figure 6

Driver Clock and Data Alignment

tclock2q (min)

tclock2q (max)

8 of 10

July 19, 2001

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc