OP AMP设计详细文档 .............................................................................................................. 4

1. 引言: ................................................................................................................................ 4

2. 电路功能描述:.............................................................................................................. 5

2.1 运放的设计指标要求................................................................................................... 5

2.2 要求输出的仿真结果................................................................................................... 6

3. 电路整体结构.................................................................................................................. 6

3.1 电路整体结构的选取................................................................................................... 7

3.1.1 输入差分跨导级结构的选择................................................................................ 7

3.1.2 输出级结构的选择................................................................................................ 7

3.1.3 补偿电路................................................................................................................ 7

3.1.4 偏置电路................................................................................................................ 8

3.2 电路符号图(Symbol) ................................................................................................... 8

4. 电路工作原理和子电路详细设计.................................................................................. 9

4.1电路工作原理................................................................................................................. 9

4.1.1 单端输出的Folded cascode结构的输入级........................................................... 9

4.1.2 共源放大结构的输出级........................................................................................ 9

Fig 7 电流源负载共源输出级 ..................................................................................... 10

4.1.3 电路的频率特性和补偿方案.............................................................................. 10

4.1.3.1 负反馈电路稳定的条件................................................................................... 10

4.1.3.2 相位裕度和开环频率特性............................................................................... 10

4.1.3.3运放的零极点分布和Miller阻容补偿方法....................................................... 10

4.1.4偏置电路................................................................................................................ 11

4.1.4.1电流偏置............................................................................................................. 11

4.1.4.2电压偏置............................................................................................................. 11

4.2子电路详细设计........................................................................................................... 12

5. 电路仿真........................................................................................................................ 15

5.1电路仿真方案............................................................................................................... 15

5.1.1直流参数仿真........................................................................................................ 15

5.1.1.1输入失调电压(Vos)及其温度特性的仿真............................................... 15

1

�

5.1.1.2共模电压输入范围(input commom-mode range)的仿真........................... 16

5.1.1.3输出动态范围(output swing) 的仿真...................................................... 16

5.1.2交流参数仿真........................................................................................................ 17

5.1.2.1开环增益(open loop gain)、增益带宽积(GBW)、相位裕度( phase margin)、

增益裕度(gain margin)的仿真.................................................................................. 17

5.1.2.2闭环频率特性仿真......................................................................................... 18

5.1.2.3共模抑制比(CMRR)的仿真..................................................................... 19

5.1.2.4电源电压抑制比(PSRR)的仿真............................................................... 19

5.1.2.5输出阻抗分析................................................................................................. 20

5.1.3瞬态参数仿真........................................................................................................ 21

5.1.3.1转换速率(slew rate)、建立时间(setup time)的仿真............................ 21

5.1.3.2总谐波失真(THD)分析.................................................................................. 22

5.2仿真结果....................................................................................................................... 23

5.2.1参数测试结果列表................................................................................................ 23

5.2.2部分仿真曲线图.................................................................................................... 24

6. 开发环境(工具及其版本、厂家、库等)................................................................ 27

7. 参考资料........................................................................................................................ 28

表目录:

表一:缩略语清单

表二:运放设计指标要求表

表三:运放设计仿真结果表

表四:不同闭环增益下的测试结果

表五:原理图中所有管子的宽长比

图目录:

Fig 1 Opamp整体结构

2

�

Fig 2 电路采用的cascode结构

Fig 3 电流源负载的共源级

Fig 4 偏置电路整体图

Fig 5 电路单元符号图

Fig 6 Opamp的整体原理图

Fig 7 电流源负载共源输出级

Fig 8 负反馈系统框图

Fig 9 自电压偏置电路

Fig 10 输入失调电压仿真原理图

Fig 11 共模电压输入范围仿真原理图

Fig 12 输出动态范围仿真原理图

Fig 13 开环参数仿真原理图

Fig 14 闭环特性仿真原理图

Fig 15 共模抑制比仿真原理图

Fig16 电源电压抑制比仿真原理图

Fig 17 输出阻抗仿真原理图

Fig 18 转换速率与建立时间仿真原理图

Fig 19 总谐波失真仿真原理图

Fig 20 系统输入失调电压VS温度特性曲线

Fig 21 平均温度系数的计算

Fig 22 闭环带宽幅频曲线图

Fig 23 运放开环的幅频、相频曲线

Fig 24 输出阻抗随频率变化的曲线图

Fig 25 共模抑制比的幅频曲线图

3

�

OP AMP设计详细文档

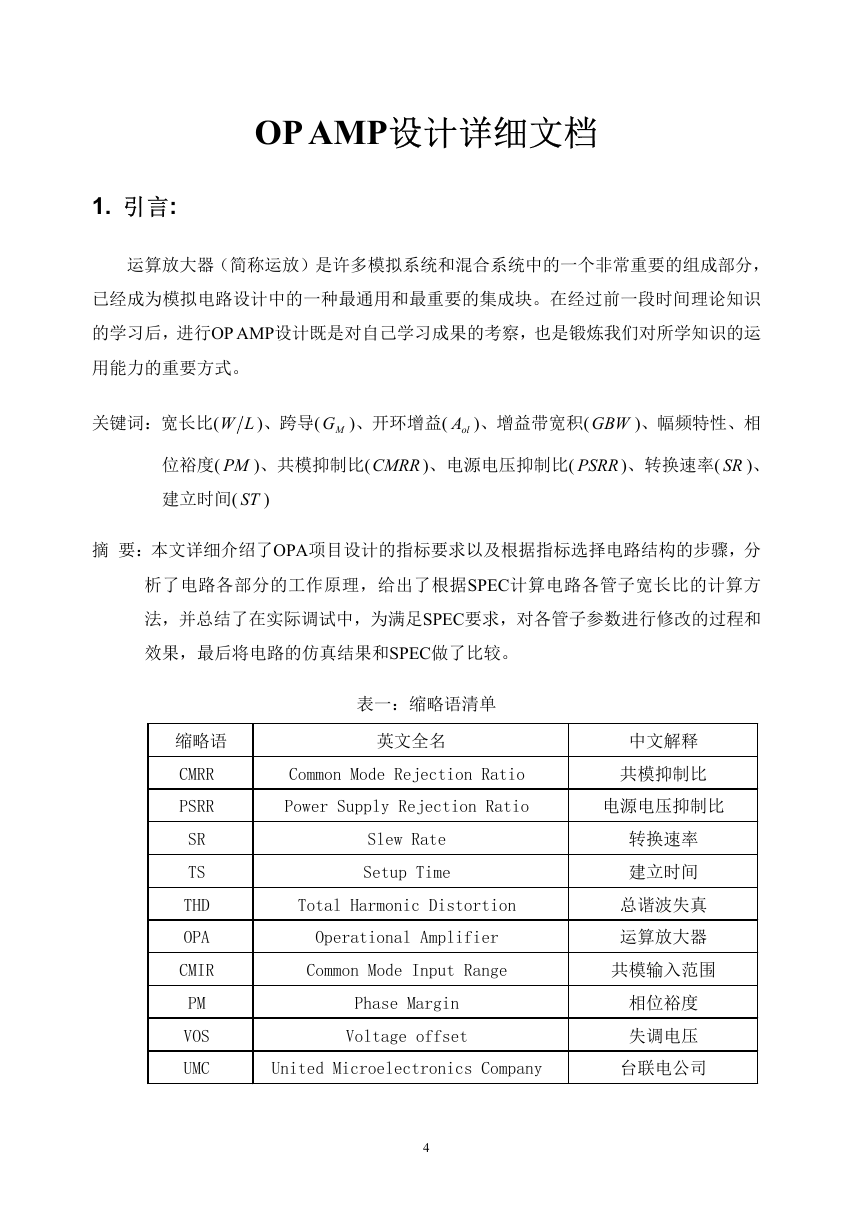

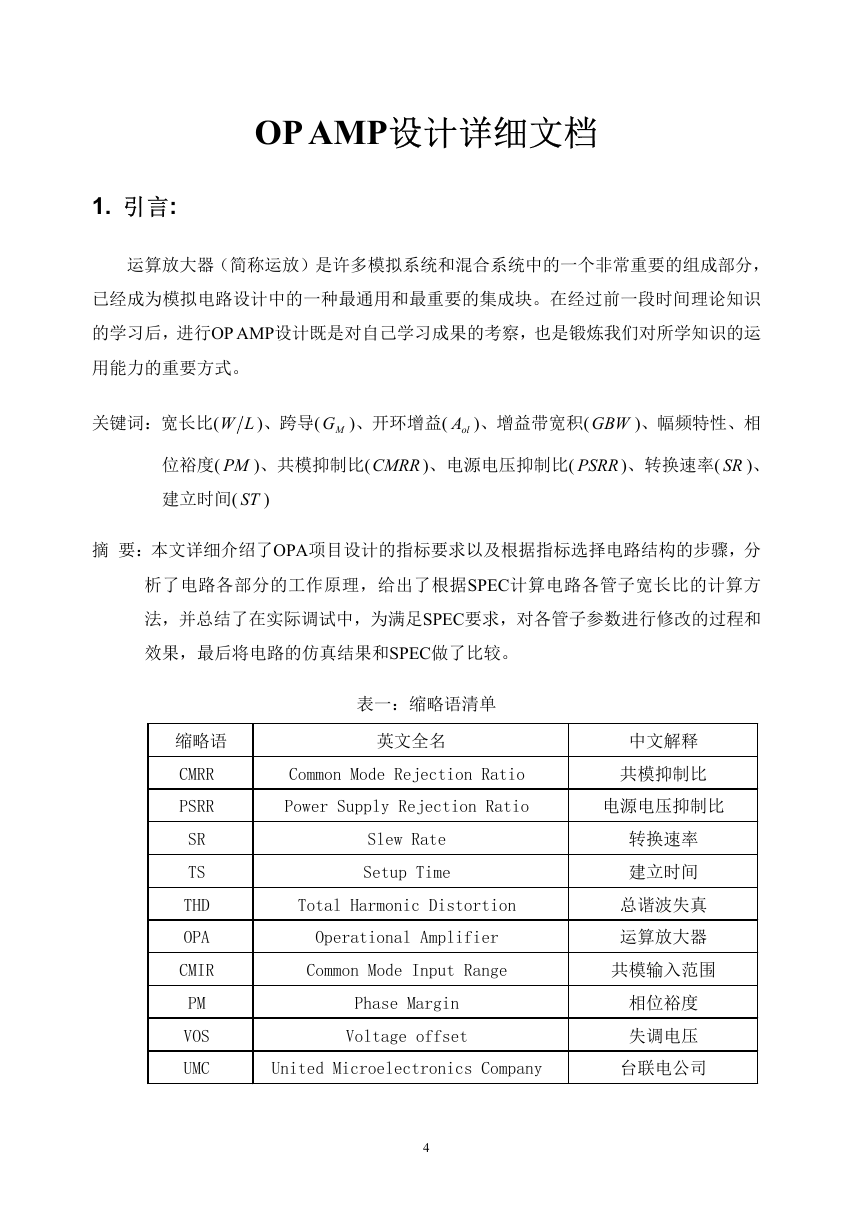

1. 引言:

运算放大器(简称运放)是许多模拟系统和混合系统中的一个非常重要的组成部分,

已经成为模拟电路设计中的一种最通用和最重要的集成块。在经过前一段时间理论知识

的学习后,进行OP AMP设计既是对自己学习成果的考察,也是锻炼我们对所学知识的运

用能力的重要方式。

关键词:宽长比(

LW )、跨导( MG )、开环增益(

olA )、增益带宽积(GBW )、幅频特性、相

位裕度( PM )、共模抑制比(CMRR )、电源电压抑制比( PSRR )、转换速率( SR )、

建立时间( ST )

摘 要:本文详细介绍了OPA项目设计的指标要求以及根据指标选择电路结构的步骤,分

析了电路各部分的工作原理,给出了根据SPEC计算电路各管子宽长比的计算方

法,并总结了在实际调试中,为满足SPEC要求,对各管子参数进行修改的过程和

效果,最后将电路的仿真结果和SPEC做了比较。

缩略语

CMRR

PSRR

SR

TS

THD

OPA

CMIR

PM

VOS

UMC

表一:缩略语清单

英文全名

中文解释

Common Mode Rejection Ratio

共模抑制比

Power Supply Rejection Ratio

电源电压抑制比

Slew Rate

Setup Time

Total Harmonic Distortion

Operational Amplifier

转换速率

建立时间

总谐波失真

运算放大器

Common Mode Input Range

共模输入范围

Phase Margin

Voltage offset

相位裕度

失调电压

United Microelectronics Company

台联电公司

4

�

2. 电路功能描述:

设计的放大器采用3.3V电源电压的0.35µmCMOS工艺, cascode结构的两级运算放

大器,并用Miller方法进行补偿。

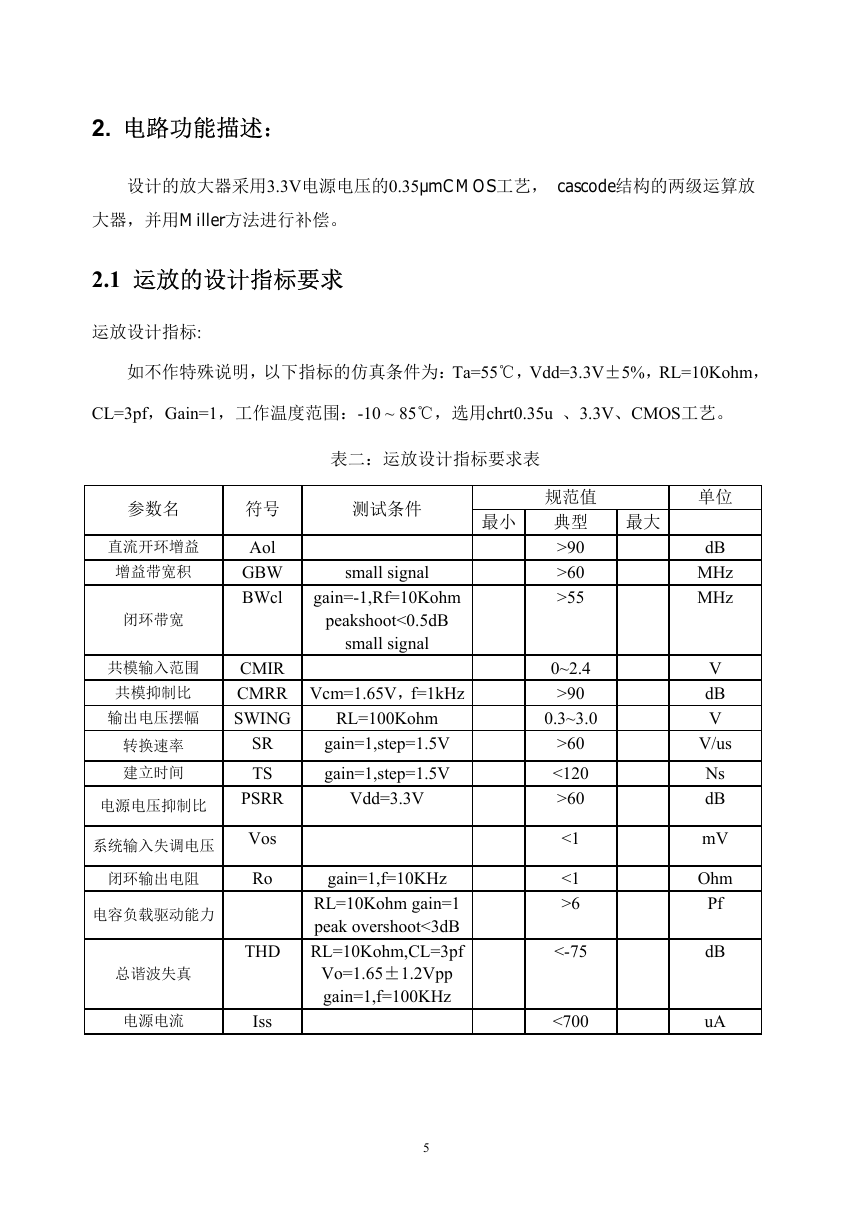

2.1 运放的设计指标要求

运放设计指标:

如不作特殊说明,以下指标的仿真条件为:Ta=55℃,Vdd=3.3V±5%,RL=10Kohm,

CL=3pf,Gain=1,工作温度范围:-10 ~ 85℃,选用chrt0.35u 、3.3V、CMOS工艺。

表二:运放设计指标要求表

规范值

典型 最大

>90

>60

>55

单位

dB

MHz

MHz

0~2.4

>90

0.3~3.0

>60

<120

>60

<1

<1

>6

<-75

<700

V

dB

V

V/us

Ns

dB

mV

Ohm

Pf

dB

uA

最小

参数名

直流开环增益

增益带宽积

闭环带宽

共模输入范围

共模抑制比

输出电压摆幅

转换速率

建立时间

电源电压抑制比

系统输入失调电压

闭环输出电阻

电容负载驱动能力

总谐波失真

电源电流

Iss

符号

Aol

GBW

BWcl

测试条件

small signal

gain=-1,Rf=10Kohm

peakshoot<0.5dB

small signal

CMIR

CMRR Vcm=1.65V,f=1kHz

SWING

RL=100Kohm

SR

TS

PSRR

Vos

Ro

THD

gain=1,step=1.5V

gain=1,step=1.5V

Vdd=3.3V

gain=1,f=10KHz

RL=10Kohm gain=1

peak overshoot<3dB

RL=10Kohm,CL=3pf

Vo=1.65±1.2Vpp

gain=1,f=100KHz

5

�

2.2 要求输出的仿真结果

1、给出系统输入失调电压的温度特性曲线,并求出平均温度系数;

2、给出闭环带宽的幅频曲线,测试0.1dB flatness带宽和-3dB带宽(增益分别

取:-1,-2,-3,-4);

3、给出开环的幅频、相频曲线;

4、给出输出阻抗随频率变化的曲线;

5、给出共模抑制比的幅频曲线;

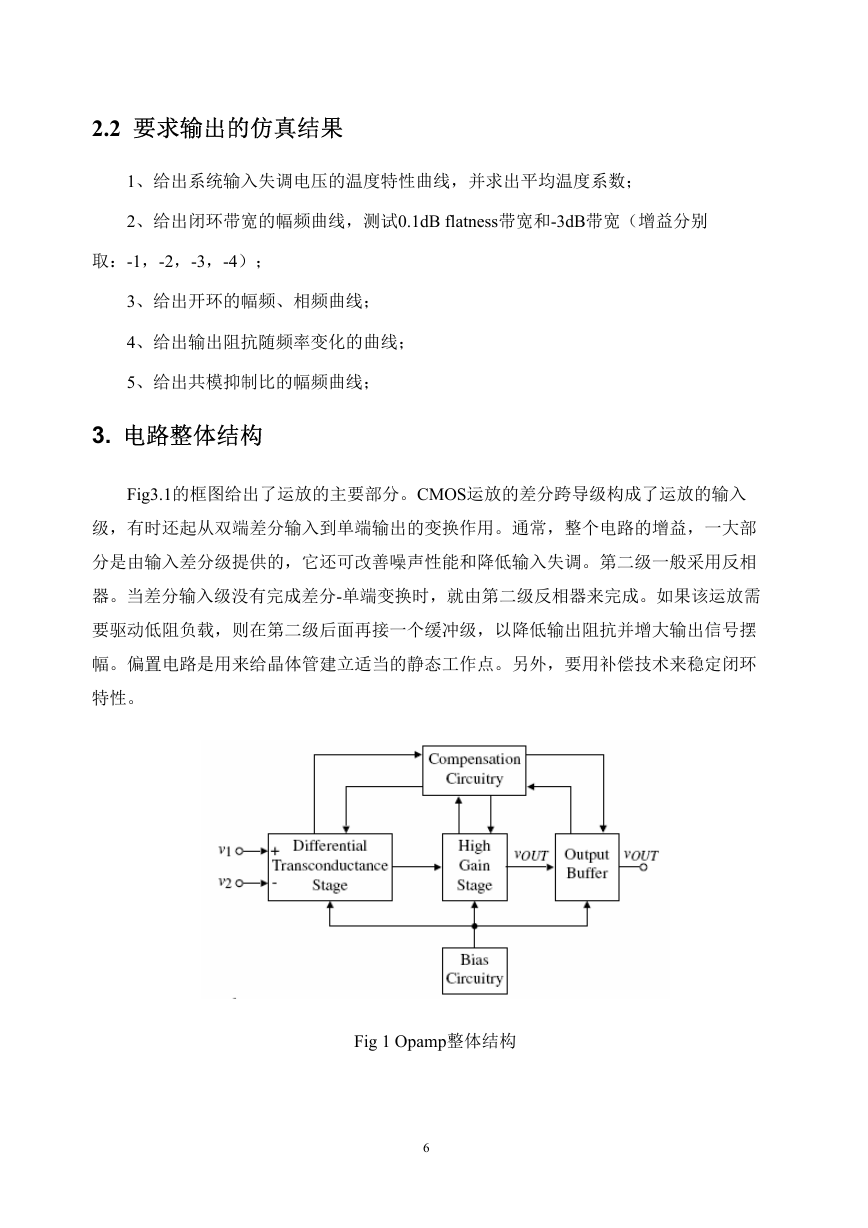

3. 电路整体结构

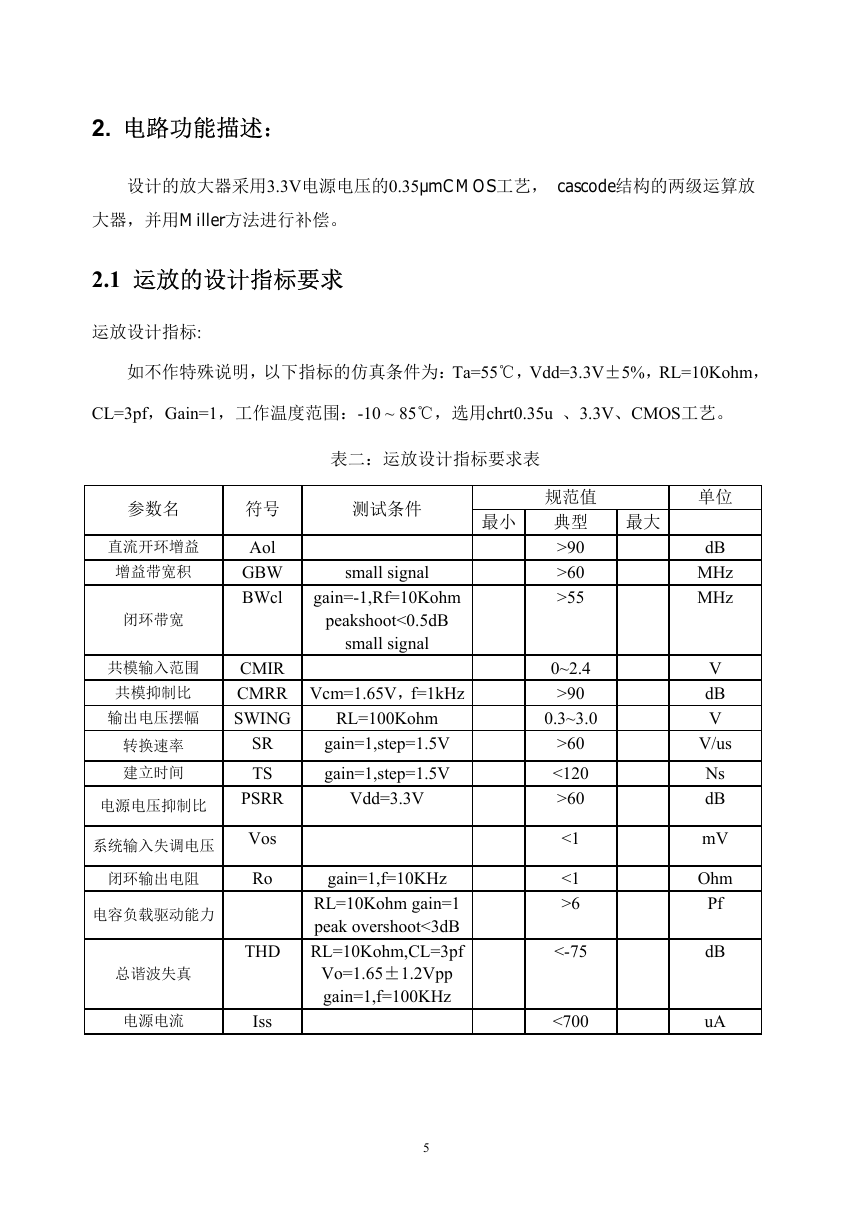

Fig3.1的框图给出了运放的主要部分。CMOS运放的差分跨导级构成了运放的输入

级,有时还起从双端差分输入到单端输出的变换作用。通常,整个电路的增益,一大部

分是由输入差分级提供的,它还可改善噪声性能和降低输入失调。第二级一般采用反相

器。当差分输入级没有完成差分-单端变换时,就由第二级反相器来完成。如果该运放需

要驱动低阻负载,则在第二级后面再接一个缓冲级,以降低输出阻抗并增大输出信号摆

幅。偏置电路是用来给晶体管建立适当的静态工作点。另外,要用补偿技术来稳定闭环

特性。

Fig 1 Opamp整体结构

6

�

3.1 电路整体结构的选取

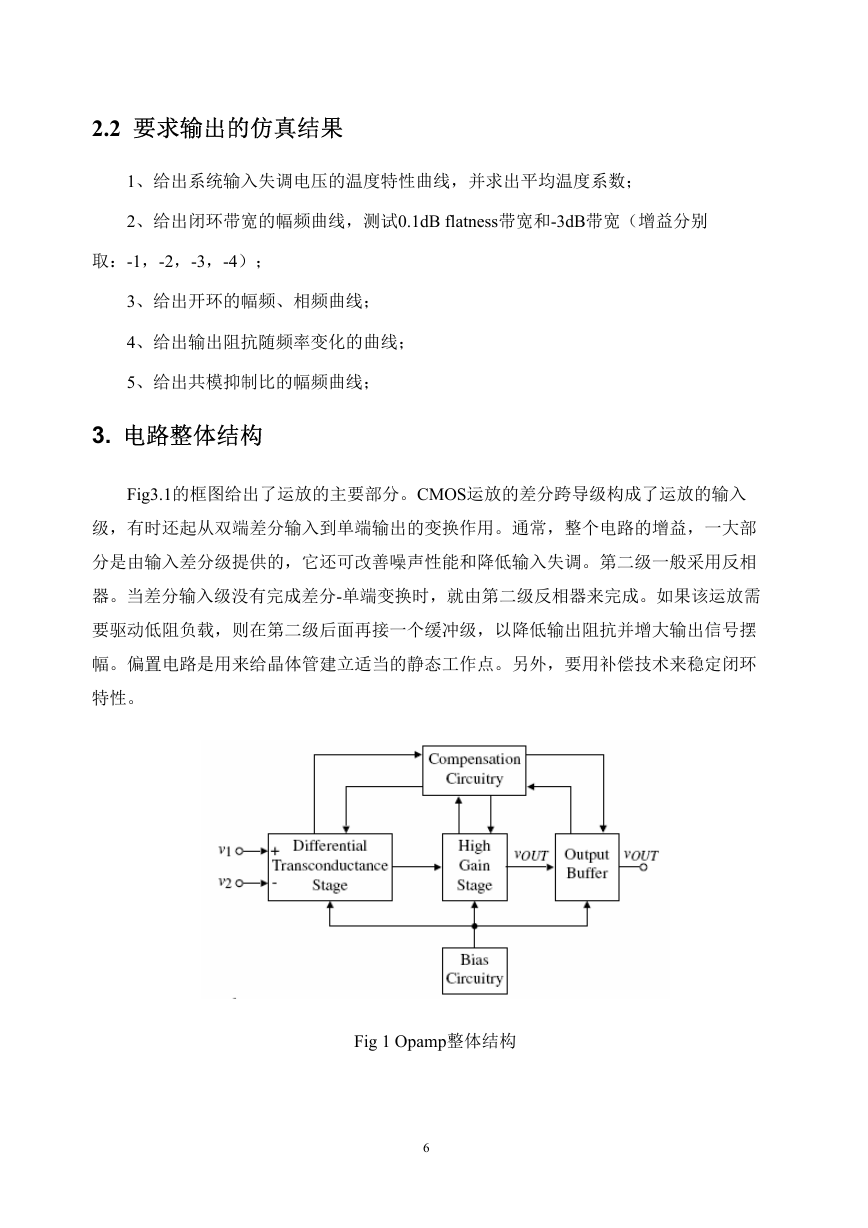

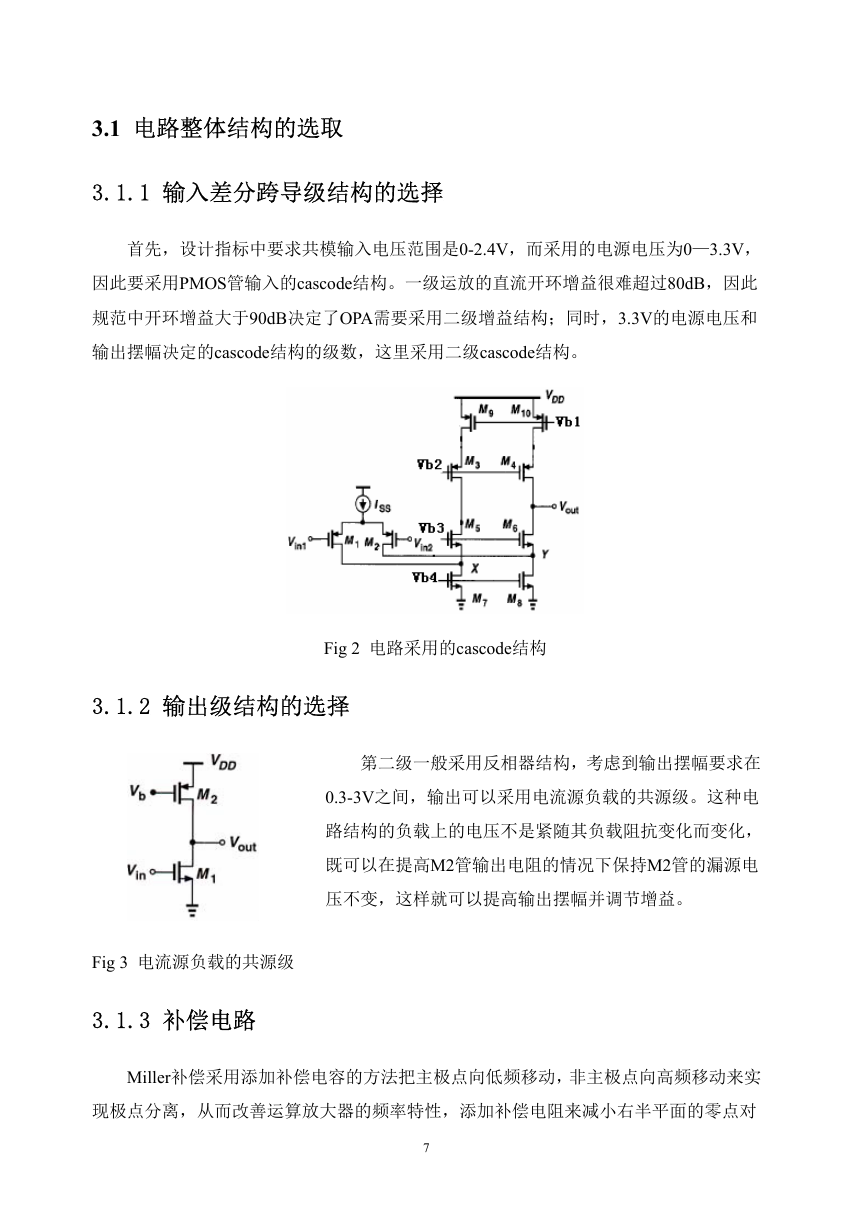

3.1.1 输入差分跨导级结构的选择

首先,设计指标中要求共模输入电压范围是0-2.4V,而采用的电源电压为0—3.3V,

因此要采用PMOS管输入的cascode结构。一级运放的直流开环增益很难超过80dB,因此

规范中开环增益大于90dB决定了OPA需要采用二级增益结构;同时,3.3V的电源电压和

输出摆幅决定的cascode结构的级数,这里采用二级cascode结构。

Fig 2 电路采用的cascode结构

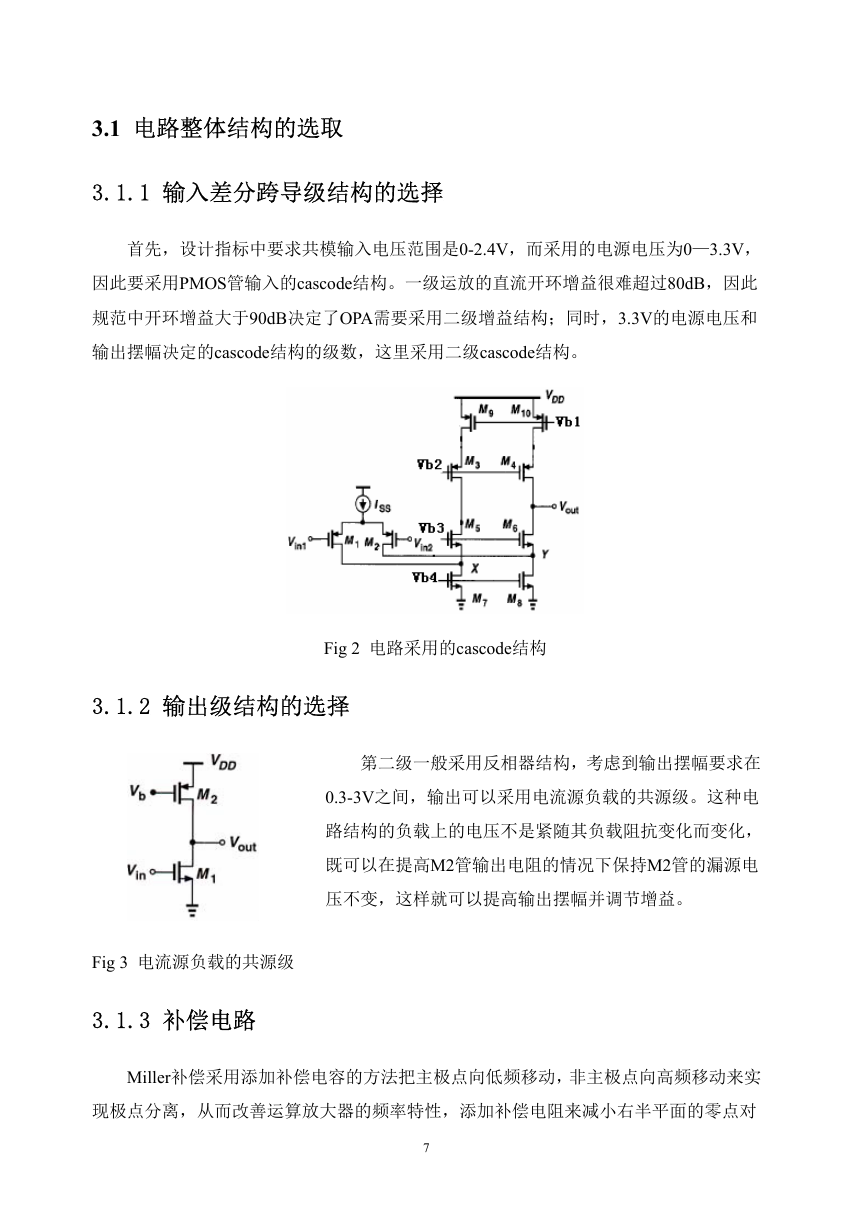

3.1.2 输出级结构的选择

第二级一般采用反相器结构,考虑到输出摆幅要求在

0.3-3V之间,输出可以采用电流源负载的共源级。这种电

路结构的负载上的电压不是紧随其负载阻抗变化而变化,

既可以在提高M2管输出电阻的情况下保持M2管的漏源电

压不变,这样就可以提高输出摆幅并调节增益。

Fig 3 电流源负载的共源级

3.1.3 补偿电路

Miller补偿采用添加补偿电容的方法把主极点向低频移动,非主极点向高频移动来实

现极点分离,从而改善运算放大器的频率特性,添加补偿电阻来减小右半平面的零点对

7

�

系统稳定性的影响。

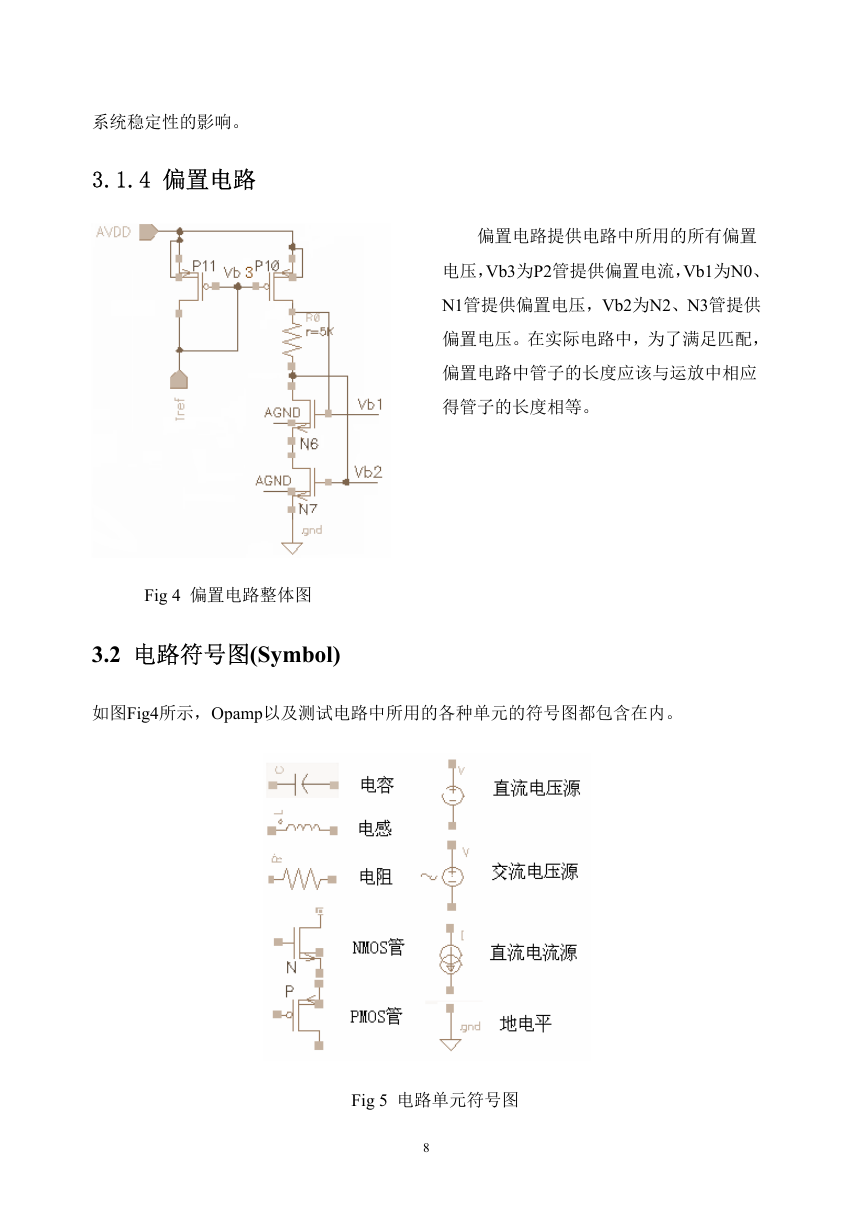

3.1.4 偏置电路

偏置电路提供电路中所用的所有偏置

电压,Vb3为P2管提供偏置电流,Vb1为N0、

N1管提供偏置电压,Vb2为N2、N3管提供

偏置电压。在实际电路中,为了满足匹配,

偏置电路中管子的长度应该与运放中相应

得管子的长度相等。

Fig 4 偏置电路整体图

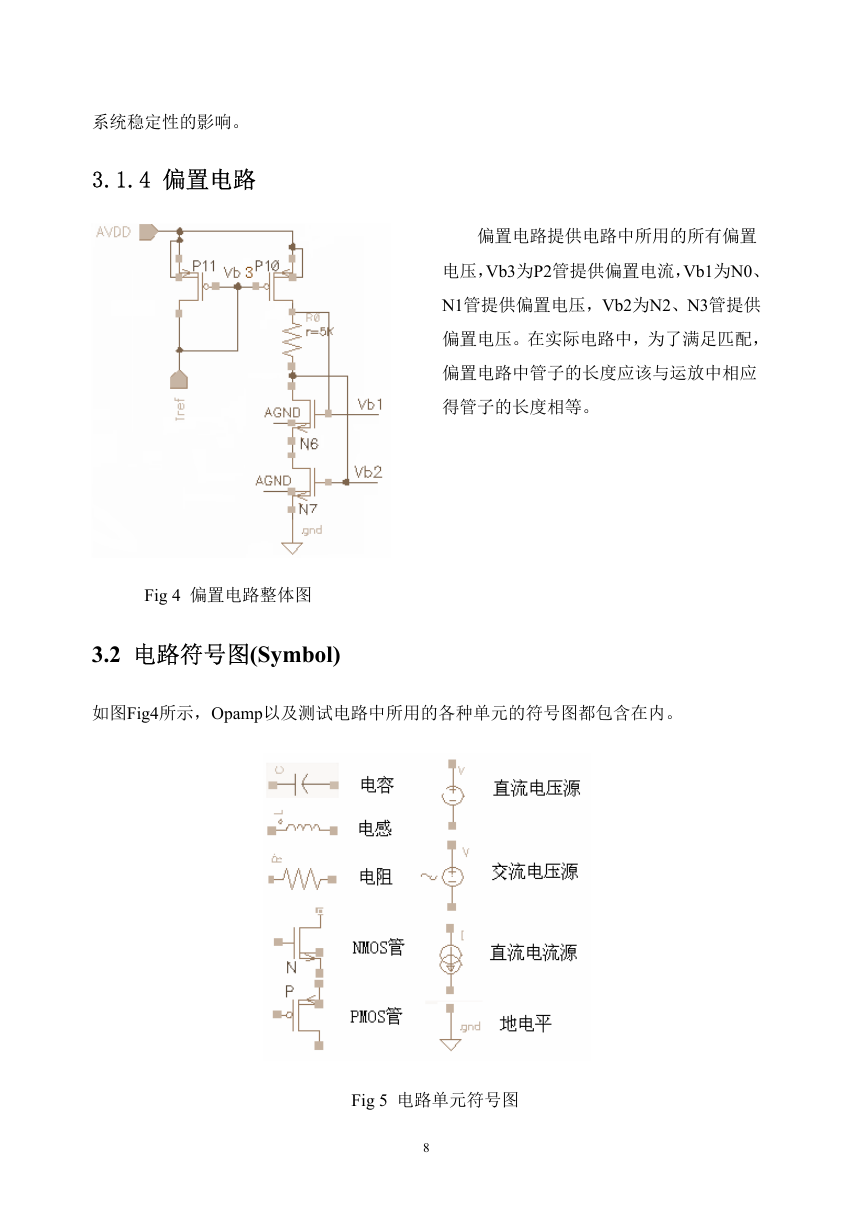

3.2 电路符号图(Symbol)

如图Fig4所示,Opamp以及测试电路中所用的各种单元的符号图都包含在内。

Fig 5 电路单元符号图

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc