中国科技论文在线

http://www.paper.edu.cn

基于 CPLD 的面阵 CCD 驱动发生器的设计

哈尔滨理工大学 测控技术与仪器黑龙江省高校重点实验室,哈尔滨(150080)

童子权,王磊

E-mail:tzq68@yahoo.com.cn

摘 要:针对美国 TI 公司面阵型 CCD 器件 TC341 的驱动时序要求,本文提出了一种基于

可编辑逻辑器件(CPLD)实现的 CCD 驱动发生器的设计方案。通过对 TC341 工作要求和

时序的分析,分别设计了供电电压模块、偏置电压产生模块、驱动器模块、以及时序产生模

块。用 Altera 公司的 Quartus II 9.1 软件对时序驱动设计进行了仿真,并给出了仿真结果。结

果表明,所设计的驱动时序电路完全满足面阵 CCD TC341 驱动时序的要求。

关键词:驱动时序;CCD;复杂可编程逻辑器件(CPLD);Quartus II

中图分类号:TM933.22

1 引言

图像传感技术作为现代信息科学的重要内容,近些年来一直受到人们的关注,成为国内

外研究的热点。其核心部件 CCD 是 20 世纪 70 年代发展起来的一种新型固体成像器件。具

有光电转换、信息存储和传输等功能,集成度高、结构简单、功耗小、性能稳定。在科学研

究的各个领域都有着广泛的应用,以 CCD 应用为核心的图像采集技术,已经在高空卫星摄

像、核爆炸、人体放射检查得到了具体的应用[1~3]。在采用 CCD 图像传感器件作为前端采

集模块的各种系统中,CCD 驱动时序电路的正确设计是各种系统开发的前提,同时也是各

系统能否实现其功能的决定因素。

鉴于此,笔者提出了一种基于复杂可编辑逻辑器件(CPLD)实现的面阵 CCD 驱动电

路的设计方案。

2 TC341 的特点和结构介绍

根据 CCD 结构的不同,面阵型 CCD 分为帧转移(Frame Transfer)CCD、隔列转移

(Interline Transfer)CCD 和全帧(Full Frame)CCD。

本设计选取的 TC341 是美国 TI 公司生产的一款 2/3 英寸高性能帧转移型 CCD。具有

780(H)×488(V)个感光像元,有效像元 754(H)×484(V),支持隔行扫描和逐行扫描两种工作方

式[4](本文中选择逐行扫描工作方式)。该芯片在正常工作状态下不会产生图像的曲解、残

留以及图像的滞后等现象。由于采用了 TI 公司的专有的 Virtual-phase 技术,具有灵敏度高,

暗电流小和响应快的优点。

TC341 帧转移型面阵 CCD 结构由四部分组成,分别是:成像区、存储区、串行寄存器和

输出放大器。成像区由并行排列的若干个电荷耦合沟道组成,各沟道之间用沟阻隔开,水平

电极横贯格沟道。成像区作用是感受光的照射,将外界的光信息转化为电荷信息。存储区的

结构与成像区相同,只是不受光的照射,用来存储成像区转移来的电荷。串行寄存器用于将

存储区中电荷逐行传输给输出放大器。输出放大器由浮动扩散结构和一个射极跟随器组成,

射极跟随器主要是对微弱的电荷起电流放大的作用,并由输出放大器将电流转换为电压。

3 TC341 驱动电路硬件设计

3.1 TC341 驱动电路硬件组成

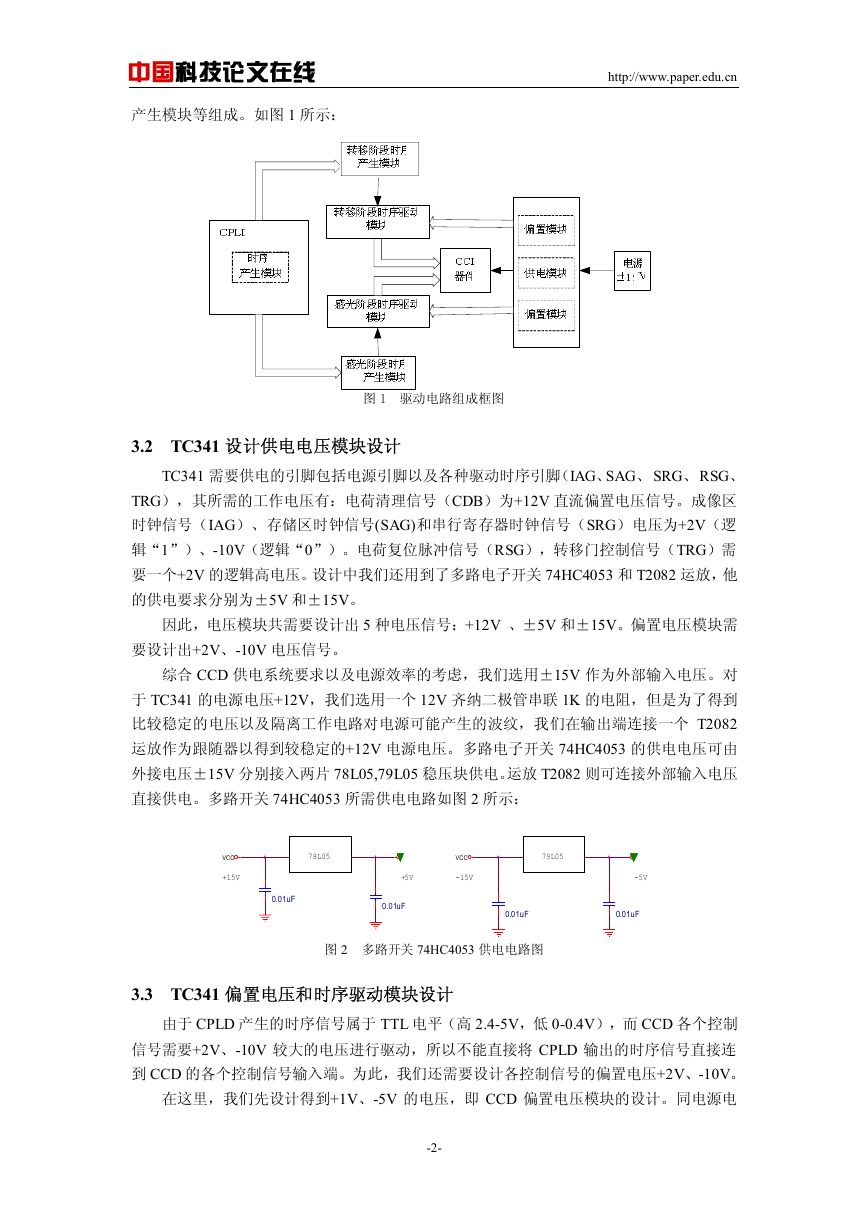

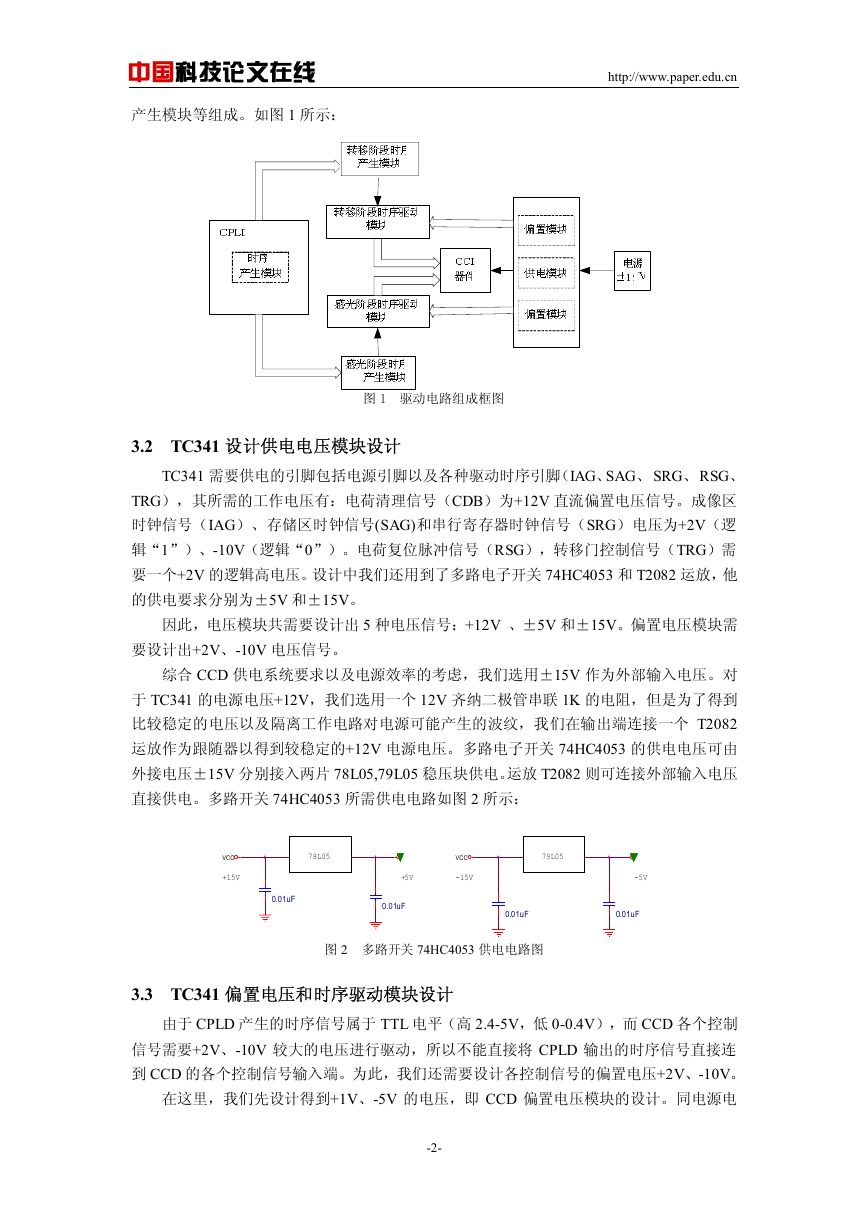

帧转移型 TC341 的驱动发生器主要由供电模块、偏置电压模块、时序驱动模块、时序

-1-

�

中国科技论文在线

产生模块等组成。如图 1 所示:

http://www.paper.edu.cn

图 1 驱动电路组成框图

3.2 TC341 设计供电电压模块设计

TC341 需要供电的引脚包括电源引脚以及各种驱动时序引脚(IAG、SAG、 SRG、 RSG、

TRG),其所需的工作电压有:电荷清理信号(CDB)为+12V 直流偏置电压信号。成像区

时钟信号(IAG)、存储区时钟信号(SAG)和串行寄存器时钟信号(SRG)电压为+2V(逻

辑“1”)、-10V(逻辑“0”)。电荷复位脉冲信号(RSG),转移门控制信号(TRG)需

要一个+2V 的逻辑高电压。设计中我们还用到了多路电子开关 74HC4053 和 T2082 运放,他

的供电要求分别为±5V 和±15V。

因此,电压模块共需要设计出 5 种电压信号:+12V 、±5V 和±15V。偏置电压模块需

要设计出+2V、-10V 电压信号。

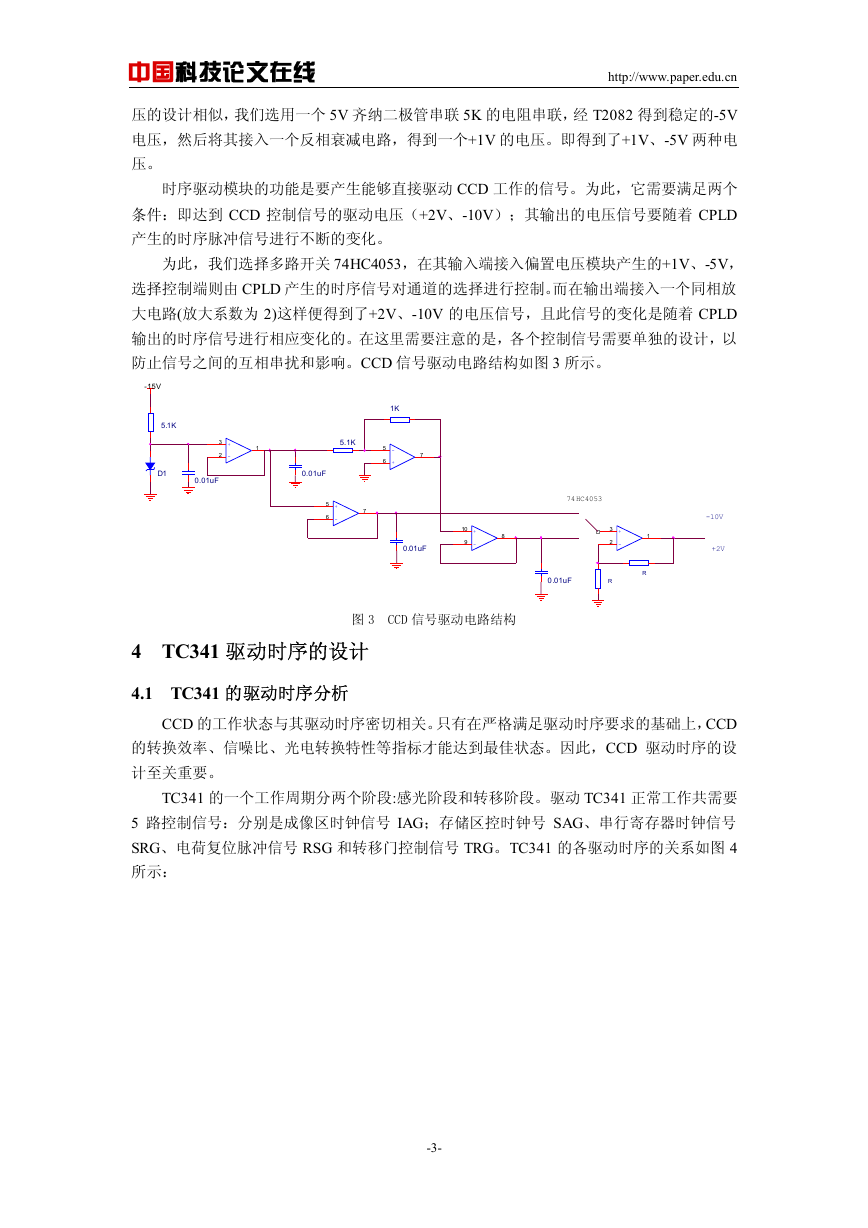

综合 CCD 供电系统要求以及电源效率的考虑,我们选用±15V 作为外部输入电压。对

于 TC341 的电源电压+12V,我们选用一个 12V 齐纳二极管串联 1K 的电阻,但是为了得到

比较稳定的电压以及隔离工作电路对电源可能产生的波纹,我们在输出端连接一个 T2082

运放作为跟随器以得到较稳定的+12V 电源电压。多路电子开关 74HC4053 的供电电压可由

外接电压±15V 分别接入两片 78L05,79L05 稳压块供电。运放 T2082 则可连接外部输入电压

直接供电。多路开关 74HC4053 所需供电电路如图 2 所示:

VCC

+15V

78L05

0.01uF

VCC

-15V

+5V

0.01uF

79L05

-5V

0.01uF

0.01uF

图 2 多路开关 74HC4053 供电电路图

3.3 TC341 偏置电压和时序驱动模块设计

由于 CPLD 产生的时序信号属于 TTL 电平(高 2.4-5V,低 0-0.4V),而 CCD 各个控制

信号需要+2V、-10V 较大的电压进行驱动,所以不能直接将 CPLD 输出的时序信号直接连

到 CCD 的各个控制信号输入端。为此,我们还需要设计各控制信号的偏置电压+2V、-10V。

在这里,我们先设计得到+1V、-5V 的电压,即 CCD 偏置电压模块的设计。同电源电

-2-

�

中国科技论文在线

http://www.paper.edu.cn

压的设计相似,我们选用一个 5V 齐纳二极管串联 5K 的电阻串联,经 T2082 得到稳定的-5V

电压,然后将其接入一个反相衰减电路,得到一个+1V 的电压。即得到了+1V、-5V 两种电

压。

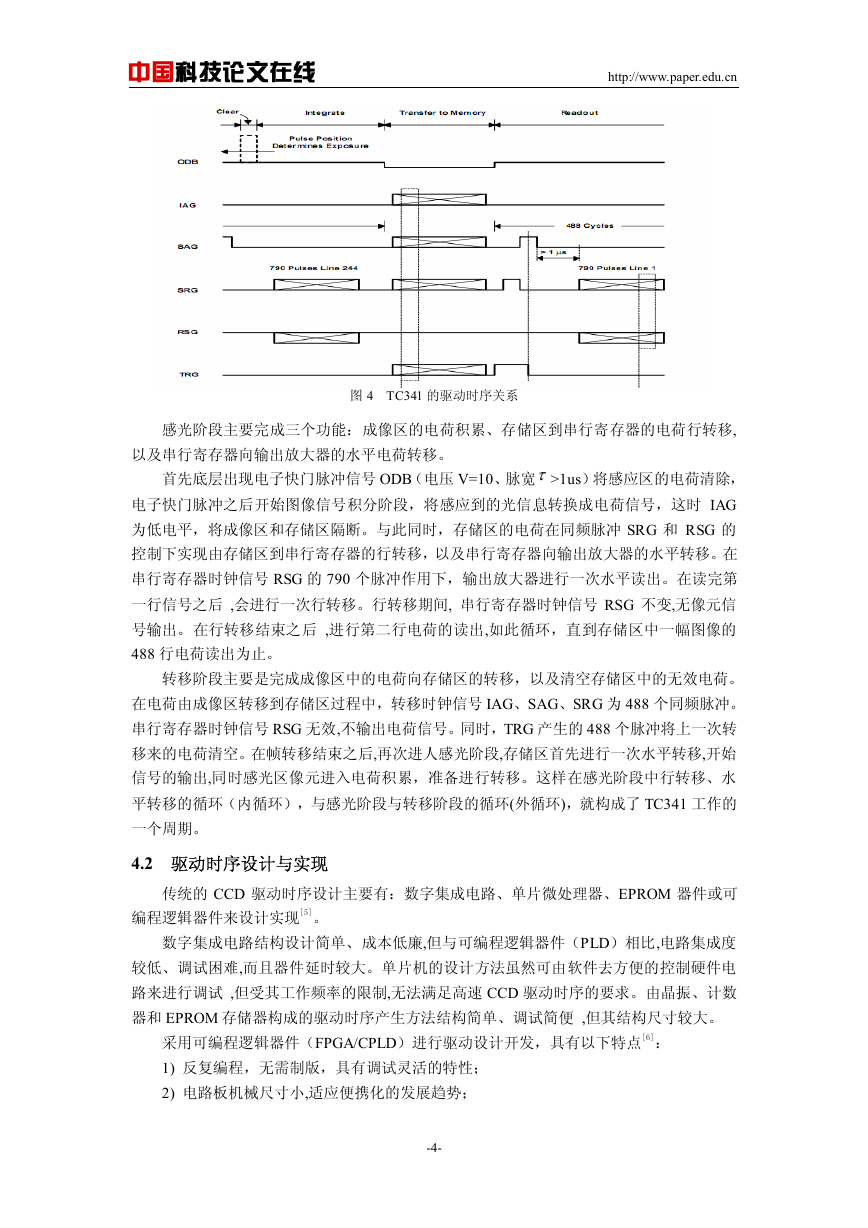

时序驱动模块的功能是要产生能够直接驱动 CCD 工作的信号。为此,它需要满足两个

条件:即达到 CCD 控制信号的驱动电压(+2V、-10V);其输出的电压信号要随着 CPLD

产生的时序脉冲信号进行不断的变化。

为此,我们选择多路开关 74HC4053,在其输入端接入偏置电压模块产生的+1V、-5V,

选择控制端则由 CPLD 产生的时序信号对通道的选择进行控制。而在输出端接入一个同相放

大电路(放大系数为 2)这样便得到了+2V、-10V 的电压信号,且此信号的变化是随着 CPLD

输出的时序信号进行相应变化的。在这里需要注意的是,各个控制信号需要单独的设计,以

防止信号之间的互相串扰和影响。CCD 信号驱动电路结构如图 3 所示。

-15V

5.1K

1K

+3

-

2

1

5.1K

-5

+

6

7

D1

0.01uF

0.01uF

+5

6

-

7

10

9

+

-

8

0.01uF

图 3 CCD 信号驱动电路结构

74HC4053

+3

-

2

0.01uF

R

1

R

-10V

+2V

4 TC341 驱动时序的设计

4.1 TC341 的驱动时序分析

CCD 的工作状态与其驱动时序密切相关。只有在严格满足驱动时序要求的基础上,CCD

的转换效率、信噪比、光电转换特性等指标才能达到最佳状态。因此,CCD 驱动时序的设

计至关重要。

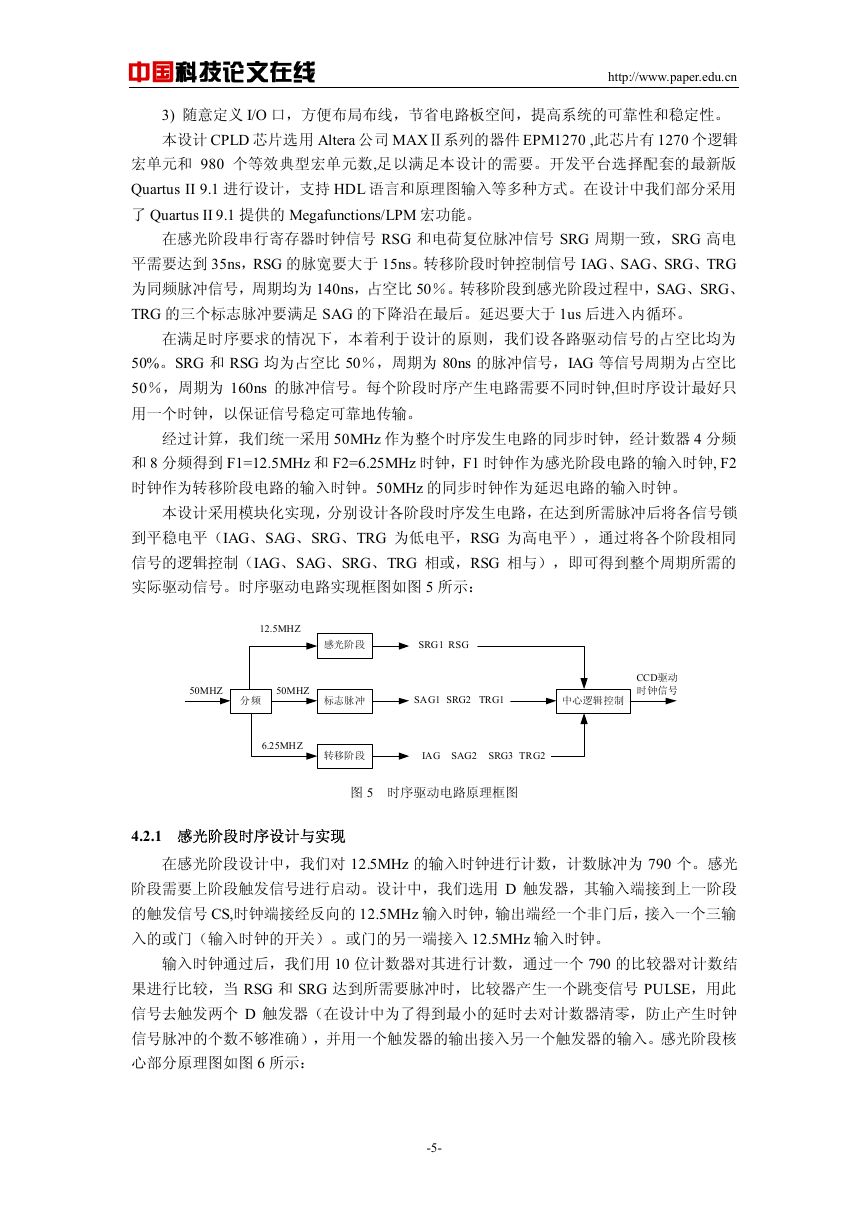

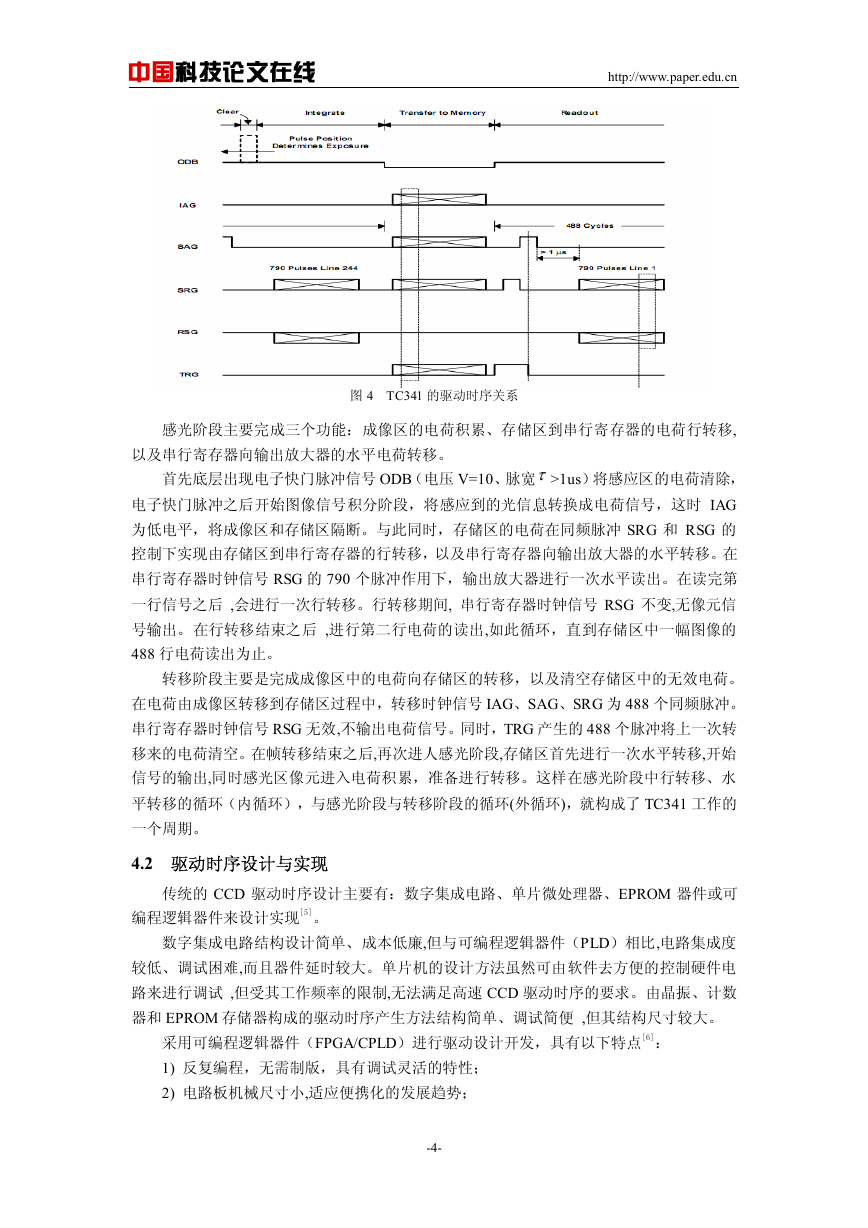

TC341 的一个工作周期分两个阶段:感光阶段和转移阶段。驱动 TC341 正常工作共需要

5 路控制信号:分别是成像区时钟信号 IAG;存储区控时钟号 SAG、串行寄存器时钟信号

SRG、电荷复位脉冲信号 RSG 和转移门控制信号 TRG。TC341 的各驱动时序的关系如图 4

所示:

-3-

�

中国科技论文在线

http://www.paper.edu.cn

图 4 TC341 的驱动时序关系

感光阶段主要完成三个功能:成像区的电荷积累、存储区到串行寄存器的电荷行转移,

以及串行寄存器向输出放大器的水平电荷转移。

首先底层出现电子快门脉冲信号 ODB(电压 V=10、脉宽τ>1us)将感应区的电荷清除,

电子快门脉冲之后开始图像信号积分阶段,将感应到的光信息转换成电荷信号,这时 IAG

为低电平,将成像区和存储区隔断。与此同时,存储区的电荷在同频脉冲 SRG 和 RSG 的

控制下实现由存储区到串行寄存器的行转移,以及串行寄存器向输出放大器的水平转移。在

串行寄存器时钟信号 RSG 的 790 个脉冲作用下,输出放大器进行一次水平读出。在读完第

一行信号之后 ,会进行一次行转移。行转移期间, 串行寄存器时钟信号 RSG 不变,无像元信

号输出。在行转移结束之后 ,进行第二行电荷的读出,如此循环,直到存储区中一幅图像的

488 行电荷读出为止。

转移阶段主要是完成成像区中的电荷向存储区的转移,以及清空存储区中的无效电荷。

在电荷由成像区转移到存储区过程中,转移时钟信号 IAG、SAG、SRG 为 488 个同频脉冲。

串行寄存器时钟信号 RSG 无效,不输出电荷信号。同时,TRG 产生的 488 个脉冲将上一次转

移来的电荷清空。在帧转移结束之后,再次进人感光阶段,存储区首先进行一次水平转移,开始

信号的输出,同时感光区像元进入电荷积累,准备进行转移。这样在感光阶段中行转移、水

平转移的循环(内循环),与感光阶段与转移阶段的循环(外循环),就构成了 TC341 工作的

一个周期。

4.2 驱动时序设计与实现

传统的 CCD 驱动时序设计主要有:数字集成电路、单片微处理器、EPROM 器件或可

编程逻辑器件来设计实现[5]。

数字集成电路结构设计简单、成本低廉,但与可编程逻辑器件(PLD)相比,电路集成度

较低、调试困难,而且器件延时较大。单片机的设计方法虽然可由软件去方便的控制硬件电

路来进行调试 ,但受其工作频率的限制,无法满足高速 CCD 驱动时序的要求。由晶振、计数

器和 EPROM 存储器构成的驱动时序产生方法结构简单、调试简便 ,但其结构尺寸较大。

采用可编程逻辑器件(FPGA/CPLD)进行驱动设计开发,具有以下特点[6]:

1) 反复编程,无需制版,具有调试灵活的特性;

2) 电路板机械尺寸小,适应便携化的发展趋势;

-4-

�

中国科技论文在线

http://www.paper.edu.cn

3) 随意定义 I/O 口,方便布局布线,节省电路板空间,提高系统的可靠性和稳定性。

本设计 CPLD 芯片选用 Altera 公司 MAXⅡ系列的器件 EPM1270 ,此芯片有 1270 个逻辑

宏单元和 980 个等效典型宏单元数,足以满足本设计的需要。开发平台选择配套的最新版

Quartus II 9.1 进行设计,支持 HDL 语言和原理图输入等多种方式。在设计中我们部分采用

了 Quartus II 9.1 提供的 Megafunctions/LPM 宏功能。

在感光阶段串行寄存器时钟信号 RSG 和电荷复位脉冲信号 SRG 周期一致,SRG 高电

平需要达到 35ns,RSG 的脉宽要大于 15ns。转移阶段时钟控制信号 IAG、SAG、SRG、TRG

为同频脉冲信号,周期均为 140ns,占空比 50%。转移阶段到感光阶段过程中,SAG、SRG、

TRG 的三个标志脉冲要满足 SAG 的下降沿在最后。延迟要大于 1us 后进入内循环。

在满足时序要求的情况下,本着利于设计的原则,我们设各路驱动信号的占空比均为

50%。SRG 和 RSG 均为占空比 50%,周期为 80ns 的脉冲信号,IAG 等信号周期为占空比

50%,周期为 160ns 的脉冲信号。每个阶段时序产生电路需要不同时钟,但时序设计最好只

用一个时钟,以保证信号稳定可靠地传输。

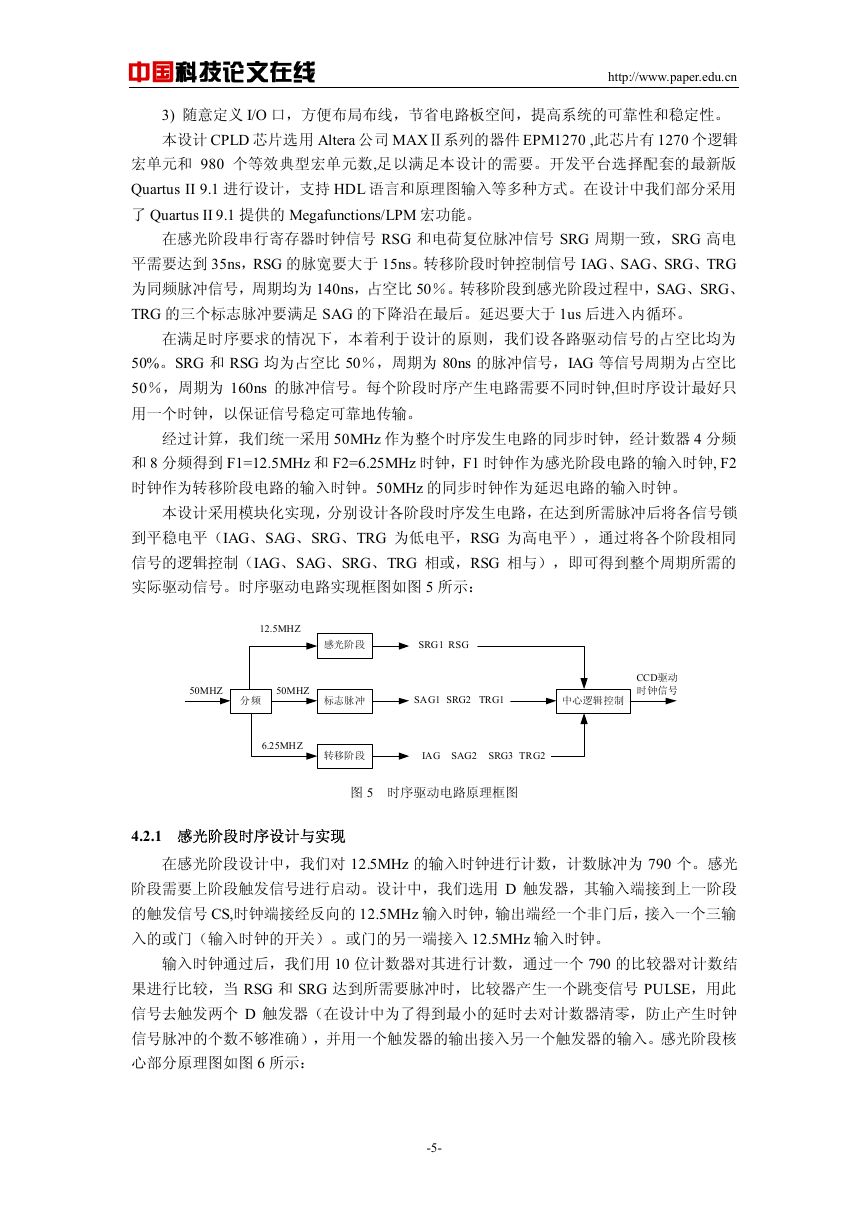

经过计算,我们统一采用 50MHz 作为整个时序发生电路的同步时钟,经计数器 4 分频

和 8 分频得到 F1=12.5MHz 和 F2=6.25MHz 时钟,F1 时钟作为感光阶段电路的输入时钟, F2

时钟作为转移阶段电路的输入时钟。50MHz 的同步时钟作为延迟电路的输入时钟。

本设计采用模块化实现,分别设计各阶段时序发生电路,在达到所需脉冲后将各信号锁

到平稳电平(IAG、SAG、SRG、TRG 为低电平,RSG 为高电平),通过将各个阶段相同

信号的逻辑控制(IAG、SAG、SRG、TRG 相或,RSG 相与),即可得到整个周期所需的

实际驱动信号。时序驱动电路实现框图如图 5 所示:

12.5MHZ

感光阶段

SRG1

RSG

50MHZ

50MHZ

分频

标志脉冲

SAG1

SRG2 TRG1

中心逻辑控制

6.25MHZ

转移阶段

IAG

SAG2

SRG3 TRG2

图 5 时序驱动电路原理框图

CCD驱动

时钟信号

4.2.1 感光阶段时序设计与实现

在感光阶段设计中,我们对 12.5MHz 的输入时钟进行计数,计数脉冲为 790 个。感光

阶段需要上阶段触发信号进行启动。设计中,我们选用 D 触发器,其输入端接到上一阶段

的触发信号 CS,时钟端接经反向的 12.5MHz 输入时钟,输出端经一个非门后,接入一个三输

入的或门(输入时钟的开关)。或门的另一端接入 12.5MHz 输入时钟。

输入时钟通过后,我们用 10 位计数器对其进行计数,通过一个 790 的比较器对计数结

果进行比较,当 RSG 和 SRG 达到所需要脉冲时,比较器产生一个跳变信号 PULSE,用此

信号去触发两个 D 触发器(在设计中为了得到最小的延时去对计数器清零,防止产生时钟

信号脉冲的个数不够准确),并用一个触发器的输出接入另一个触发器的输入。感光阶段核

心部分原理图如图 6 所示:

-5-

�

中国科技论文在线

http://www.paper.edu.cn

CS

IN PU T

VC C

D FF

D PRN Q

CLRN

ins t7

N OT

ins t8

T

O

N

9

t

s

in

CL K_ 70ns

IN PU T

VC C

OR3

inst

NOT

in st1

OR 2

ins t2

OU TPU T

SRG

OU TPU T

RSG

VCC

IN PU T

VC C

ctc

clock

u p co unt er

q[9.. 0]

in st3

r

l

c

a

cmp

com par e

dataa[9.. 0]

datab[]=10

aeb

ins t4

DF F

D PRN Q

CLRN

in st5

CLR

INP UT

V CC

N OT

ins t6

图 6 感光阶段核心部分原理图

OU TPU T

PULSE

OUTP UT

FL IP

我们把前一个触发器输出接入计数器的清零端对其清零,同时接入三输入或门的输入

端,对 SRG 的脉冲进行屏蔽,使其输出为稳定低的电平;另一个触发器的输出接入 RSG 的

三输入或门,对 RSG 的脉冲进行屏蔽,使其输出为稳定高的电平。感光阶段时序仿真结果

如图 7 所示:

图 7 感光阶段时序仿真结果

4.2.2 转移阶段时序设计与实现

转移阶段设计要对 6.25MHz 时钟脉冲进行计数,当 IAG、SAG、SRG、TRG 的 4 路脉

冲信号达到 488 时,比较器输出跳变信号触发 D 触发器,将 D 触发器输出的高电平接入计

数器的清零端对计数器进行清零,同时将其接入到或门的输入端,对脉冲进行屏蔽,使其输

出为稳定低的电平。转移阶段核心部分原理图如图 8 所示:

DFF

D

PRN

Q

CLRN

inst7

NOT

inst8

9

t

s

in

T

O

N

CS

IN PUT

VCC

C LK_140ns

IN PUT

VCC

N OT

inst1

OR3

ins t

OUTPUT

OUTPUT

OUTPUT

OUTPUT

IAG

SAG

SR G

TRG

VC C

INPUT

VCC

ct c

up counter

q [9..0]

clock

lr

c

a

inst3

CMP _TRA NSFE R

compare

data a[9..0 ]

data b[]=1 0

a eb

inst10

D FF

D

PRN

Q

CLRN

inst5

CLR

IN PUT

VCC

NOT

inst6

图 8 转移阶段核心部分原理图

OU TPU T

P ULSE

OU TPU T

F LIP

其中,D 触发器的输出的“1”FLIP 作为下一阶段的启动信号,比较器的跳变信号 PULSE

作为下一阶段的清零信号。转移阶段时序仿真结果如图 9 所示:

图 9 转移阶段时序仿真结果

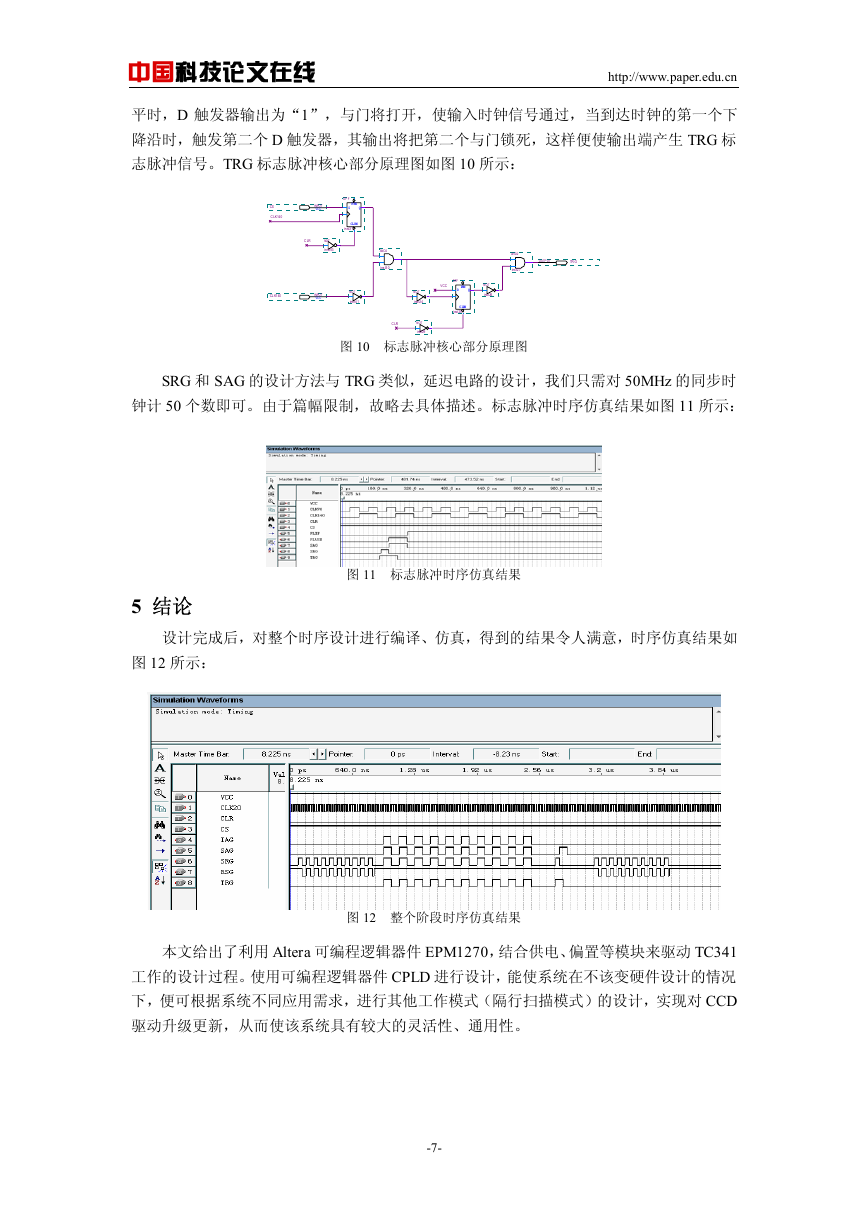

4.2.3 标志脉冲时序设计与实现

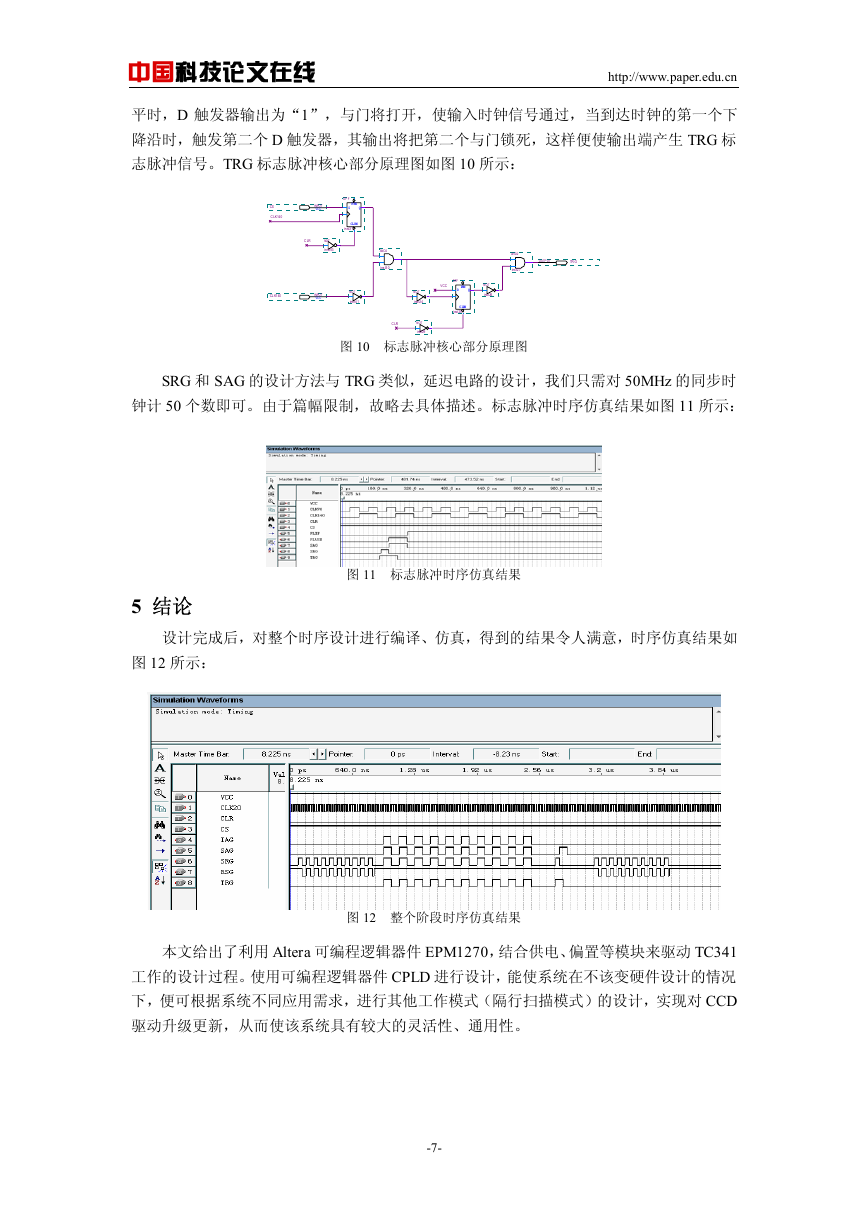

在 TRG 标志脉冲的设计中,我们用第一个与门接受 CS 的信号,当 CS 由低电平到高电

-6-

�

中国科技论文在线

http://www.paper.edu.cn

平时,D 触发器输出为“1”,与门将打开,使输入时钟信号通过,当到达时钟的第一个下

降沿时,触发第二个 D 触发器,其输出将把第二个与门锁死,这样便使输出端产生 TRG 标

志脉冲信号。TRG 标志脉冲核心部分原理图如图 10 所示:

CS

C LK140

INPUT

VCC

DF F

D PRN Q

CLRN

inst31

C LR

NOT

inst 53

CLK140

INPUT

VCC

NOT

ins t41

AND2

ins t27

OUTPUT

TR G

AND2

ins t30

NOT

ins t24

NOT

ins t29

C LR

VCC

DFF

D PRN Q

NOT

inst 26

CLRN

inst 25

图 10 标志脉冲核心部分原理图

SRG 和 SAG 的设计方法与 TRG 类似,延迟电路的设计,我们只需对 50MHz 的同步时

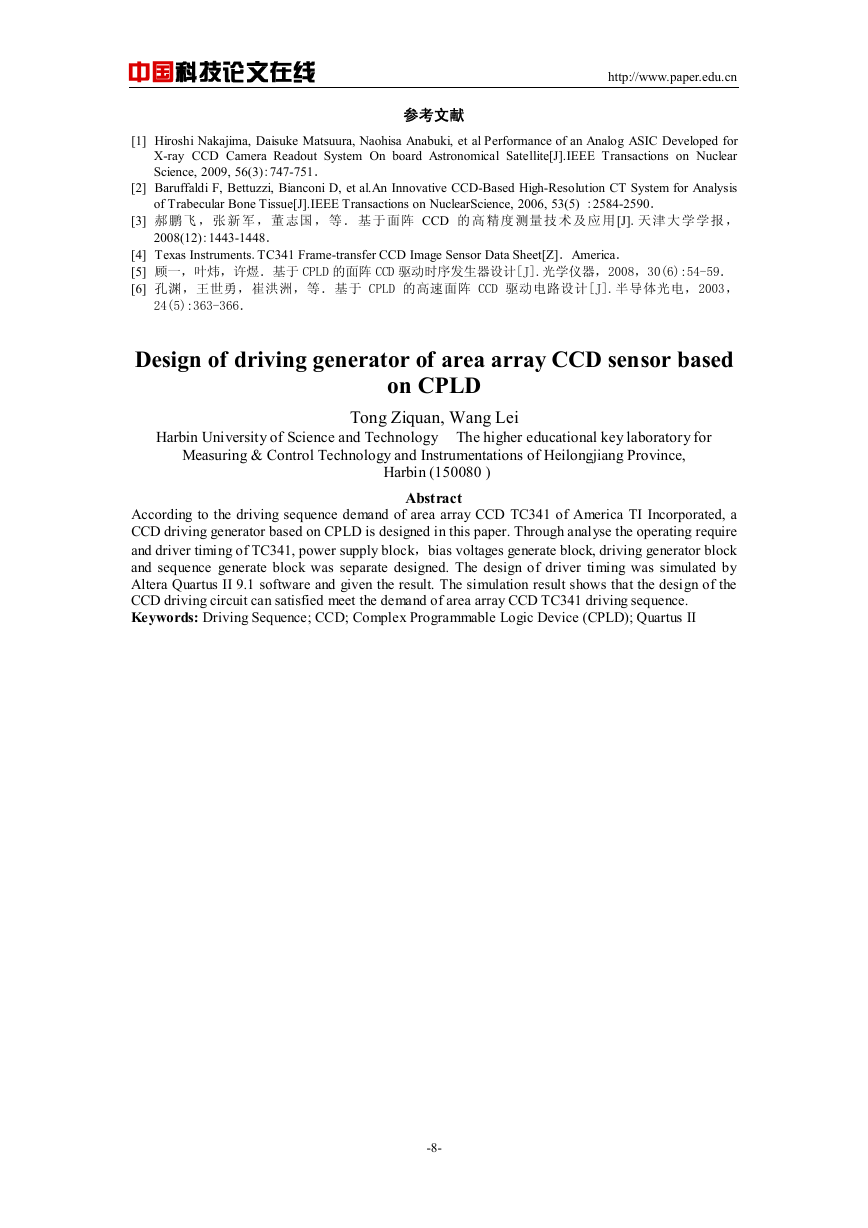

钟计 50 个数即可。由于篇幅限制,故略去具体描述。标志脉冲时序仿真结果如图 11 所示:

图 11 标志脉冲时序仿真结果

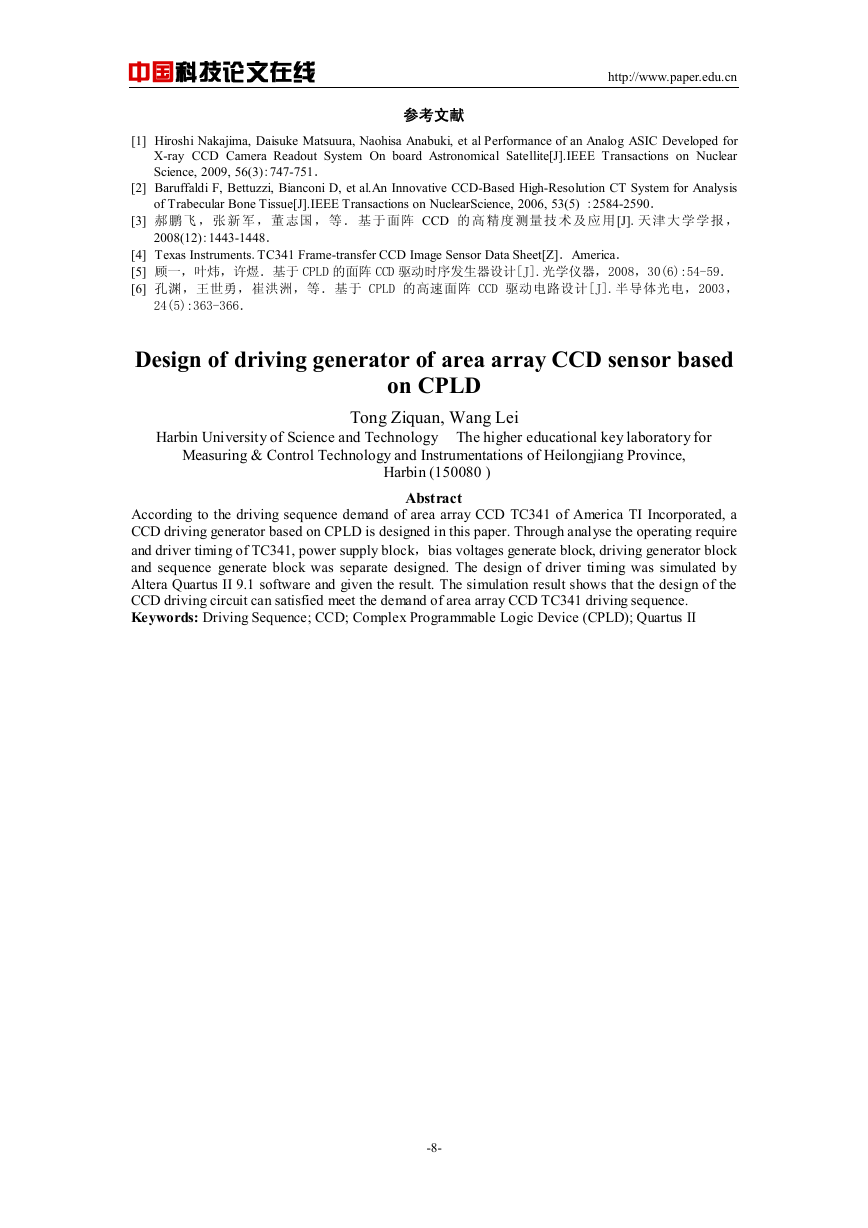

5 结论

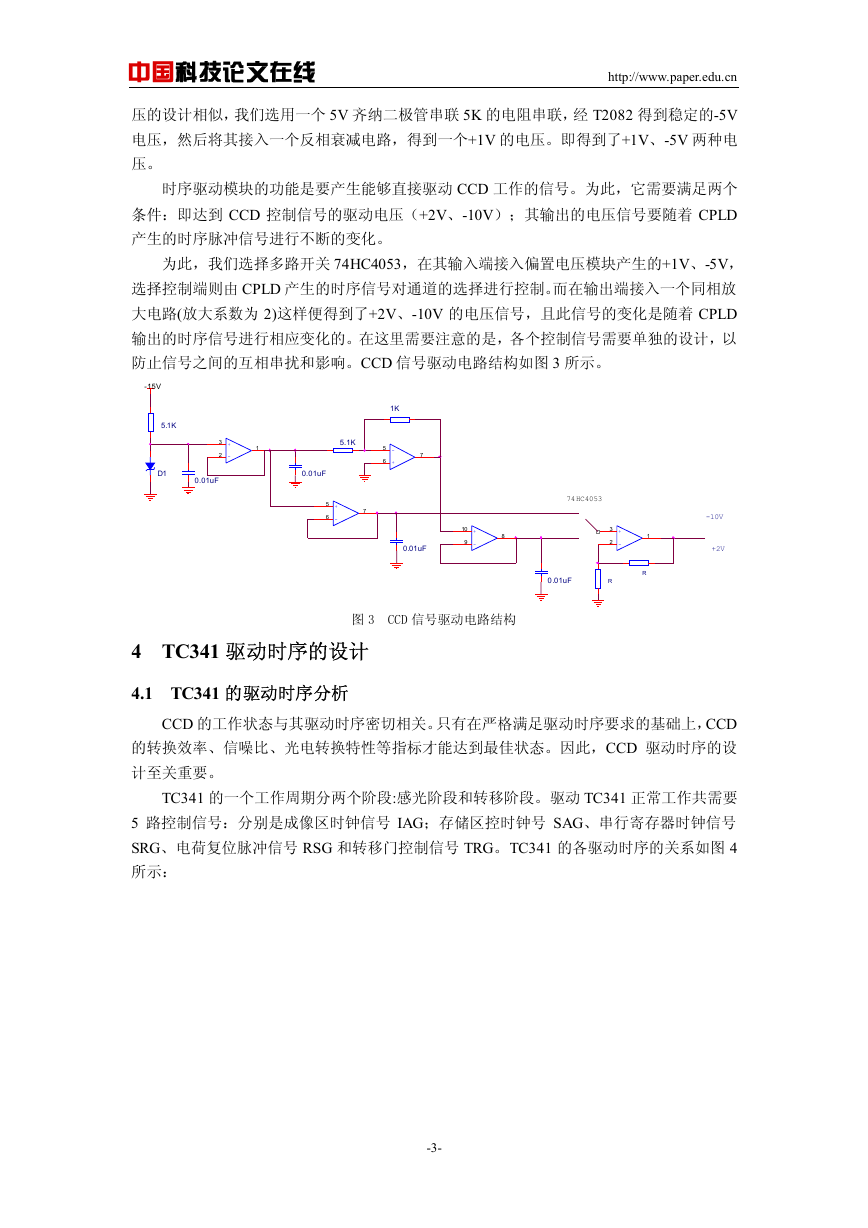

设计完成后,对整个时序设计进行编译、仿真,得到的结果令人满意,时序仿真结果如

图 12 所示:

图 12 整个阶段时序仿真结果

本文给出了利用 Altera 可编程逻辑器件 EPM1270,结合供电、偏置等模块来驱动 TC341

工作的设计过程。使用可编程逻辑器件 CPLD 进行设计,能使系统在不该变硬件设计的情况

下,便可根据系统不同应用需求,进行其他工作模式(隔行扫描模式)的设计,实现对 CCD

驱动升级更新,从而使该系统具有较大的灵活性、通用性。

-7-

�

中国科技论文在线

http://www.paper.edu.cn

参考文献

[1] Hiroshi Nakajima, Daisuke Matsuura, Naohisa Anabuki, et al Performance of an Analog ASIC Developed for

X-ray CCD Camera Readout System On board Astronomical Satellite[J].IEEE Transactions on Nuclear

Science, 2009, 56(3):747-751.

[2] Baruffaldi F, Bettuzzi, Bianconi D, et al.An Innovative CCD-Based High-Resolution CT System for Analysis

of Trabecular Bone Tissue[J].IEEE Transactions on NuclearScience, 2006, 53(5) :2584-2590.

[3] 郝 鹏 飞 , 张 新 军 , 董 志国 , 等 . 基 于 面阵 CCD 的 高 精 度 测量 技 术 及 应 用[J].天 津 大 学 学 报 ,

[4] Texas Instruments.TC341 Frame-transfer CCD Image Sensor Data Sheet[Z].America.

[5] 顾一,叶炜,许煜.基于 CPLD 的面阵 CCD 驱动时序发生器设计[J].光学仪器,2008,30(6):54-59.

[6] 孔渊,王世勇,崔洪洲,等.基于 CPLD 的高速面阵 CCD 驱动电路设计[J].半导体光电,2003,

2008(12):1443-1448.

24(5):363-366.

Design of driving generator of area array CCD sensor based

on CPLD

Tong Ziquan, Wang Lei

Harbin (150080 )

Harbin University of Science and Technology The higher educational key laboratory for

Measuring & Control Technology and Instrumentations of Heilongjiang Province,

Abstract

According to the driving sequence demand of area array CCD TC341 of America TI Incorporated, a

CCD driving generator based on CPLD is designed in this paper. Through analyse the operating require

and driver timing of TC341, power supply block,bias voltages generate block, driving generator block

and sequence generate block was separate designed. The design of driver timing was simulated by

Altera Quartus II 9.1 software and given the result. The simulation result shows that the design of the

CCD driving circuit can satisfied meet the demand of area array CCD TC341 driving sequence.

Keywords: Driving Sequence; CCD; Complex Programmable Logic Device (CPLD); Quartus II

-8-

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc