QCA7000 HomePlug® Green PHY

Single Chip Solution

Data Sheet

MKG-15723 Ver. 11.0

October 8, 2012

Confidential and Proprietary - Qualcomm Atheros, Inc.

Not to be used, copied, reproduced in whole or in part, nor its contents revealed in any manner to others without the

express written permission of Qualcomm Atheros, Inc.

QUALCOMM is a registered trademark of Qualcomm Incorporated. ATHEROS is a registered trademark of

Qualcomm Atheros, Inc. All other registered and unregistered trademarks are the property of Qualcomm

Incorporated, Qualcomm Atheros, Inc. or their respective owners and used with permission. Registered marks owned

by Qualcomm Incorporated and Qualcomm Atheros, Inc. are registered in the United States of America and may be

registered in other countries.

This technical data may be subject to U.S. and international export, re-export, or transfer (“export”) laws. Diversion

contrary to U.S. and international law is strictly prohibited.

Qualcomm Atheros, Inc.

1700 Technology Drive

San Jose, CA 95110-1383

U.S.A.

Copyright © 2011-2012 Qualcomm Atheros, Inc.

All rights reserved.

Qualcomm Atheros Confidential�

Revision History

Revision

Ver. 1.0

Ver. 2.0

Ver. 3.0

Date

May 2011

August 2011

October 2011

Ver. 4.0

Ver. 5.0

Ver. 6.0

Ver. 7.0

Ver. 8.0

Ver. 9.0

Description

Preliminary QCA7000 Release

Revised some pinout and signal names

Revised Figure 2-1. QCA7000 8x8 mm 68-Pin QFN and Figure 2-3.

QCA7000 Internal Block Diagram. Updated cpu_on, wrbuf_error and

rd_buf_error descriptions throughout the document. Updated Package

Dimensions content.

Revised Table 2-5 pin assignments.

November 2011

December 6, 2011 Revised Table 6-1 and Figure 6.1

December 16, 2011 Revised Table 2-1 and Table 2-2

February 2012

March 2012

June 2012

Revised Table 2-5; formatted Table 4-1 to stay on same page.

Revised QCA7000 Power Supply Requirements.

Revised SPI Config register (SPI_CONFIG) Table

Revised Recommended Operating Conditions and Power Supply

Requirements. Revised RESET_L leading edge point in timing

diagram.

Ver. 10.0

Ver. 11.0

September 2012 Revised Section 1.2 added Industrial temperature required Firmware

version. Revised Table 2-5; added Table 2-6. Revised Section 4.2.1;

revised Table 4-1; revised Section 4.3.2.

Revised Table 5-2 added Industrial Temperature Tcase values

October 2012

MKG-15723 Ver. 11.0

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

2

Confidential and Proprietary - Qualcomm Atheros, Inc.

Qualcomm Atheros Confidential�

Contents

1 General Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.2

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.3 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.4 QCA7000 Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Conventions Used in this Data Sheet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.5

2 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.1 QCA7000 Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2.1.1 QCA7000 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2.1.2 Signal-to-Pin Relationships and Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . 12

System Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.2.1 System Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.2.2 Integrated Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.3

Zero Cross . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.4 QCA7000 Power On Configuration Strap Values and Defaults . . . . . . . . . . . . . . . . . . . . 18

2.2

3 System Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.1 Architecture Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.2 Host Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.2.1 QCA7000 SPI Master Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.2.2 QCA7000 Serial Host Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.2.3 QCA7000 SPI Slave Interface Command-Data Protocol . . . . . . . . . . . . . . . . . 23

3.2.4 GPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.2 QCA7000 Maximum Throughput Data Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.2.1 UART Baud Rates Set Serial Interface Data Rate . . . . . . . . . . . . . . . . . . . . . . 38

Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

4.3.1 Power Domains . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

4.3.2 Power Management Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Boot Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Serial Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

4.4

4.5

4.3

MKG-15723 Ver. 11.0

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

3

Confidential and Proprietary - Qualcomm Atheros, Inc.

Qualcomm Atheros Confidential�

QCA7000 HomePlug® Green PHY Single Chip Solution Data Sheet

Contents

5 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

5.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

5.2

Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

5.3 QCA7000 Power Supply Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

5.4 DC Switching Thresholds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

5.5

Crystal Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

6.1

6 Timing Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

System Clock and Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

6.1.1 QCA7000 Crystal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

6.1.2 Master Time Base Accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

6.1.3 External Clock Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Zero Crossing Detector Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

SPI Master Bus Timing (Boot FLASH) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

SPI Slave Bus Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

6.2

6.3

6.4

7 Package Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

8 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

MKG-15723 Ver. 11.0

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

4

Confidential and Proprietary - Qualcomm Atheros, Inc.

Qualcomm Atheros Confidential�

1 General Information

1.1 Description

The QCA7000 is the latest addition to the Powerline Communications (PLC) portfolio of

communication ICs from Atheros. It is fully compliant with the HomePlug Green PHY (HPGP)

specification. HomePlug's Green PHY specification was developed specifically to meet the needs

of the home, utility and Smart Grid applications. The QCA7000 uses a robust OFDM (ROBO)

mode of communication that provides extended coverage and reliable communication over

Powerline networks. However, the QCA7000 has been designed to meet specific industry

requirements for HomePlug AV compatibility. The QCA7000 is interoperable up to the HPGP

maximum data rate of 10 Mbps and offers lower power consumption, lower product complexity

and reduced BOM costs.

The QCA7000 is fully interoperable with HomePlug AV and IEEE 1901 compliant products. The

QCA7000 supports HomePlug Green PHY Distributed Bandwidth Control to ensure effective

coexistence with HPAV equipment operating in close proximity on the same Powerline

infrastructure. The IC also supports HPGP Power Save Mode, which enables the IC to enter and

exit a low power state on a scheduled basis to maintain network synchronization.

An integrated switching power supply provides the 1.2 V core voltage. No external active

components are required. Inductors and capacitors are required for the bypass circuit.

1.2 Features

Compliant with HomePlug Green PHY specification

Interoperable with HomePlug AV specification and IEEE 1901 Standard up to the maximum

HPGP data rate

Operates on 240 VAC, 120 VAC, 24 VAC, and DC lines

Single chip solution with integrated analog front end and line driver

Lower cost and power consumption than existing HPAV solutions for lower data rates - ideal

for Smart Grid applications

Industrial temperature range for extended temperature and smart meter applications

Requires QCA7000 HomePlug Green PHY Firmware v1.0.0-07 and higher

Host interfaces: SPI (Slave) and UART

Boot from host or external FLASH memory

Dedicated FLASH memory port (SPI master)

Supports Robust OFDM (ROBO) mode modulation: 4 Mbps to 10 Mbps PHY rates

Powered from single 3.3 VDC rail with integrated Power Management Unit

RoHS Compliant: 8 x 8 mm 68 pin QFN

MKG-15723 Ver. 11.0

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

5

Confidential and Proprietary - Qualcomm Atheros, Inc.

Qualcomm Atheros Confidential�

QCA7000 HomePlug® Green PHY Single Chip Solution Data Sheet

General Information

1.3 Applications

Smart Meters

Energy Management Systems

Programmable Controlled Thermostats

Remote Metering Devices

Solar Panels

Industrial Applications

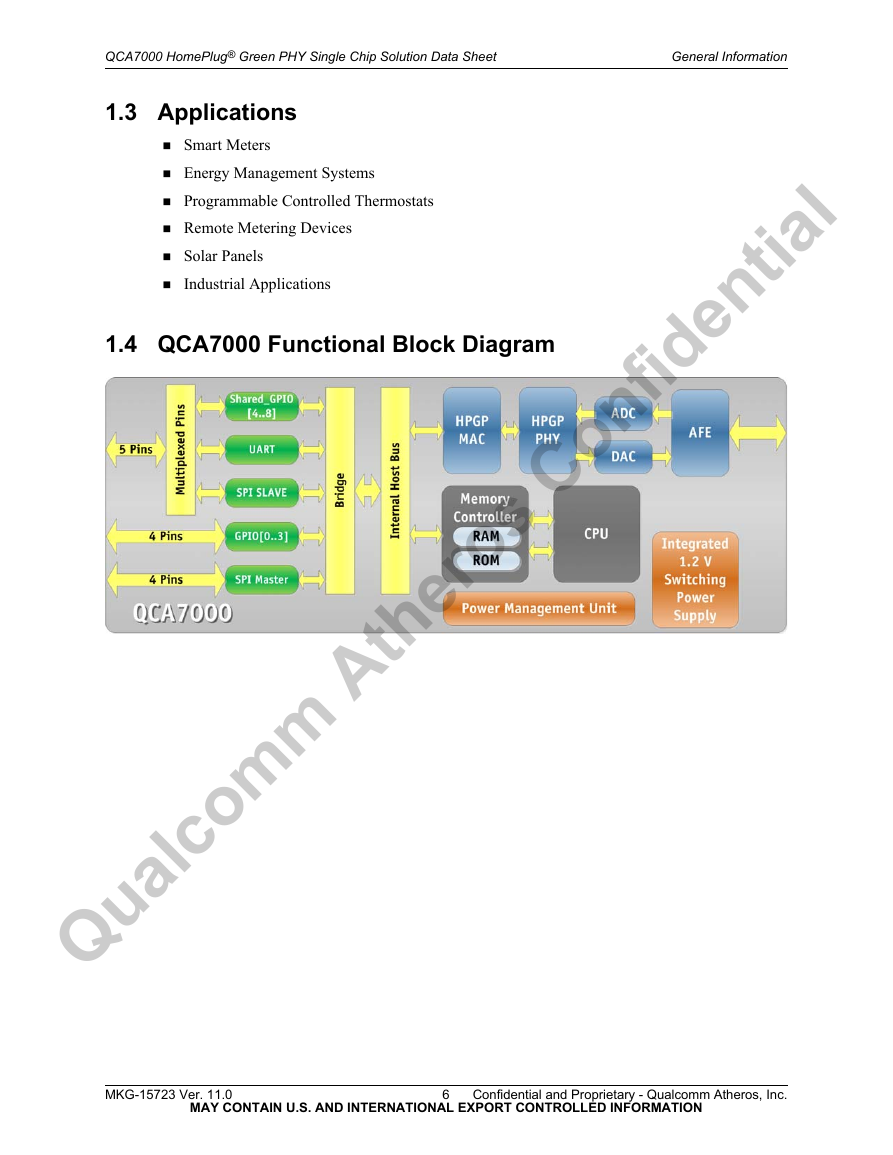

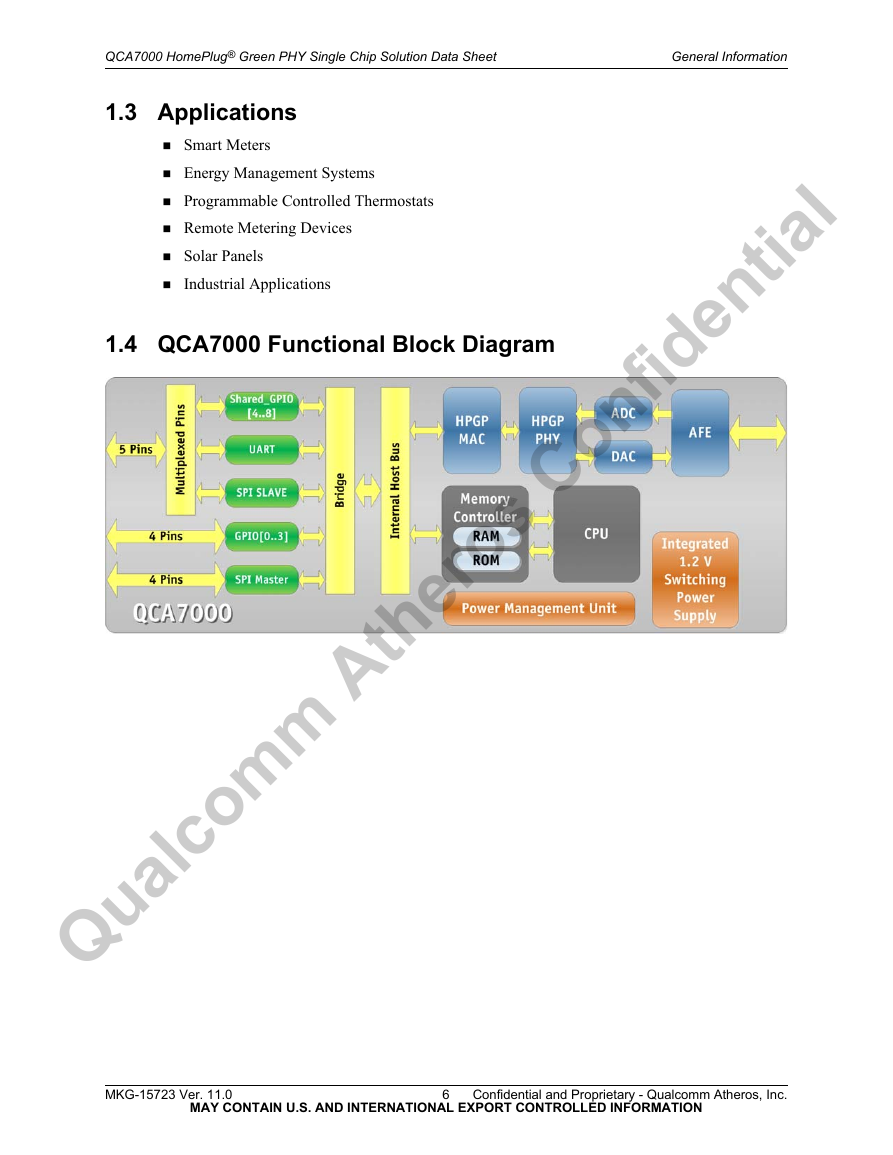

1.4 QCA7000 Functional Block Diagram

MKG-15723 Ver. 11.0

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

6

Confidential and Proprietary - Qualcomm Atheros, Inc.

Qualcomm Atheros Confidential�

QCA7000 HomePlug® Green PHY Single Chip Solution Data Sheet

General Information

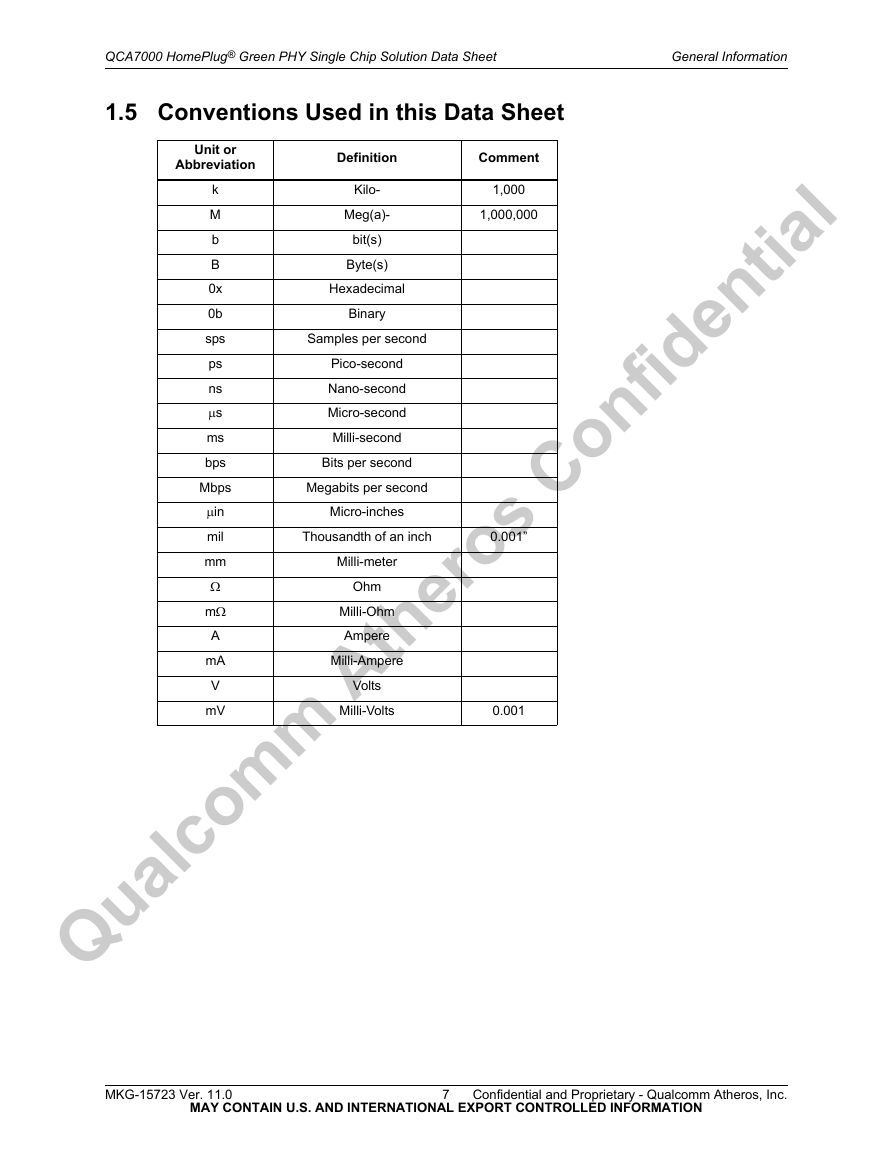

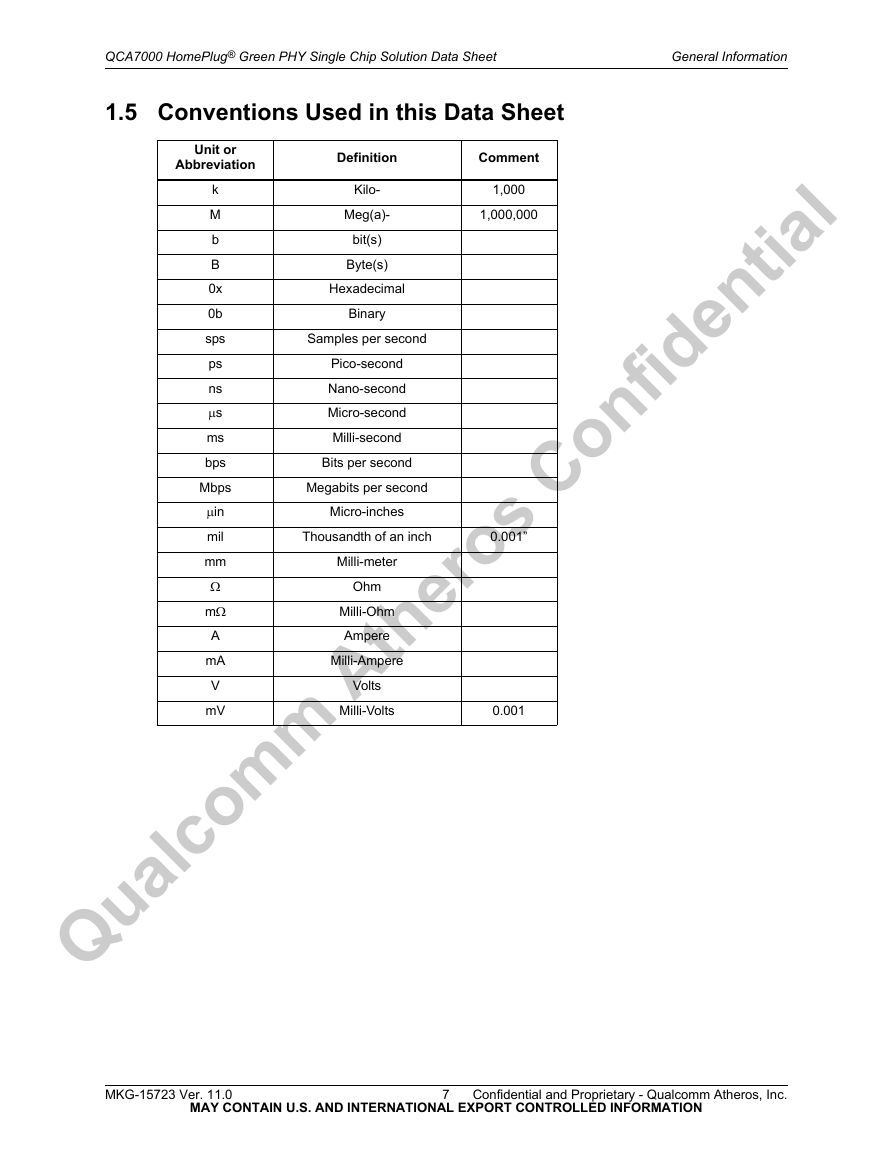

1.5 Conventions Used in this Data Sheet

Unit or

Abbreviation

k

M

b

B

0x

0b

sps

ps

ns

s

ms

bps

Mbps

in

mil

mm

m

A

mA

V

mV

Comment

1,000

1,000,000

Definition

Kilo-

Meg(a)-

bit(s)

Byte(s)

Hexadecimal

Binary

Samples per second

Pico-second

Nano-second

Micro-second

Milli-second

Bits per second

Megabits per second

Micro-inches

Thousandth of an inch

0.001”

Milli-meter

Ohm

Milli-Ohm

Ampere

Milli-Ampere

Volts

Milli-Volts

0.001

MKG-15723 Ver. 11.0

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

7

Confidential and Proprietary - Qualcomm Atheros, Inc.

Qualcomm Atheros Confidential�

2 Pin Descriptions

This section contains both a package pinout (see Figure 2-1, Table 2-1 and Table 2-2) and tabular

listings of the signal descriptions.

The following nomenclature is used for signal names:

DNC

_L

_P

_N

RSVD

No connection should be made to this pin

Low true signal

At the end of the signal name, indicates the positive side of a differential signal

At the end of the signal name indicates the negative side of a differential signal

Reserved

The following nomenclature is used for signal types:

GND

I

I/O

IA

IH

IL

O

OA

P

A ground signal

Digital input signal

A digital bidirectional signal

Analog input signal

Input signals with weak internal pull-up, to prevent signals from floating when left

open

Input signals with weak internal pull-down, to prevent signals from floating when

left open

A digital output signal

An analog output signal

A power signal

MKG-15723 Ver. 11.0

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

8

Confidential and Proprietary - Qualcomm Atheros, Inc.

Qualcomm Atheros Confidential�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc