[艾曼

TP:// AM

曼电子技

MFPGA.

技术文档

.TAOBA

AO.COM]

HTT

2013‐2‐21

OV7

7670 摄

摄像头

头彻底解

解读

序

序

本文

文档旨在解决

决 OV7670 开

开发的过程中

中的 3 个问题

题:

1.

OV7670 是什

什么;

2.

OV7670 怎么

么用;

3.

OV7670 怎么

么用好。

文档

档适合在 FPG

GA 上开发 O

OV7670 应用

用的开发人员

员。

一、

、OV7670

0 是什么

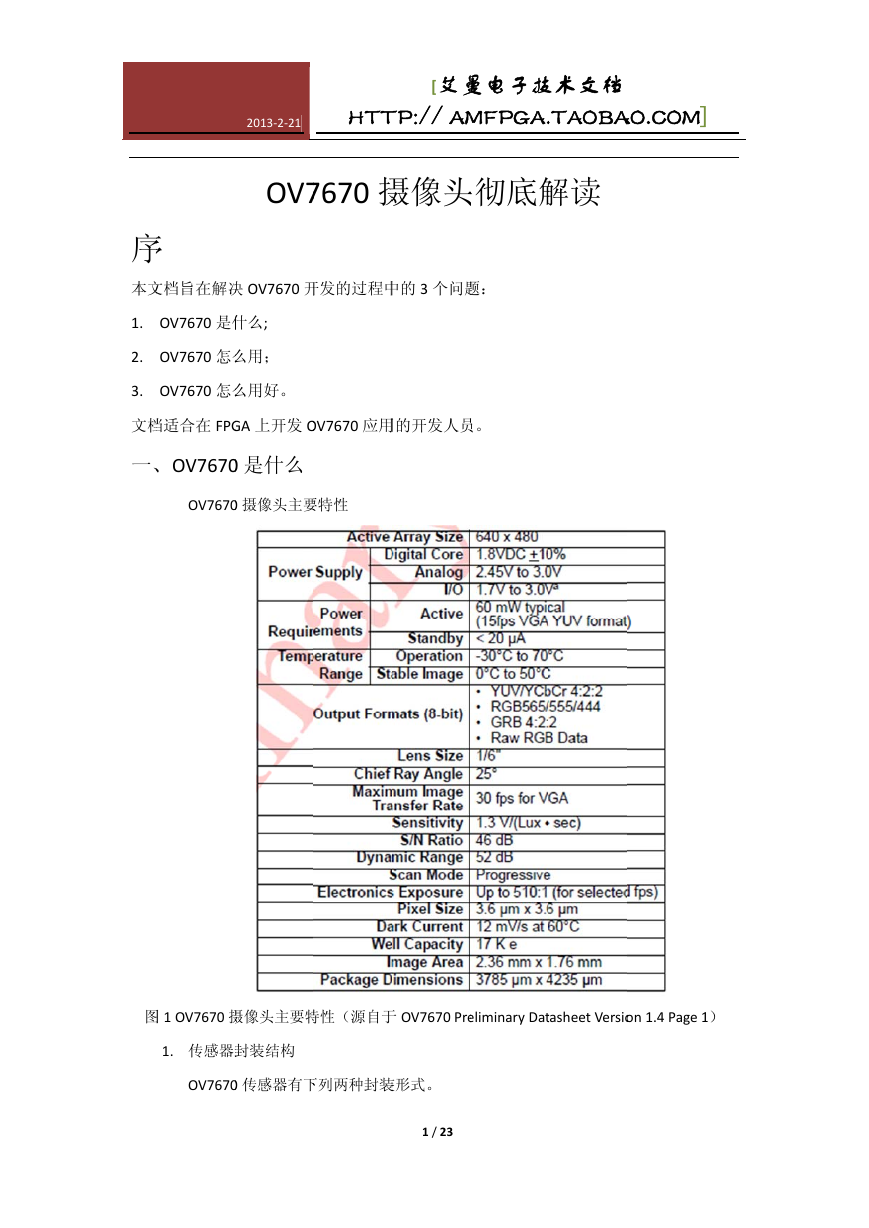

OV7670

0 摄像头主要

要特性

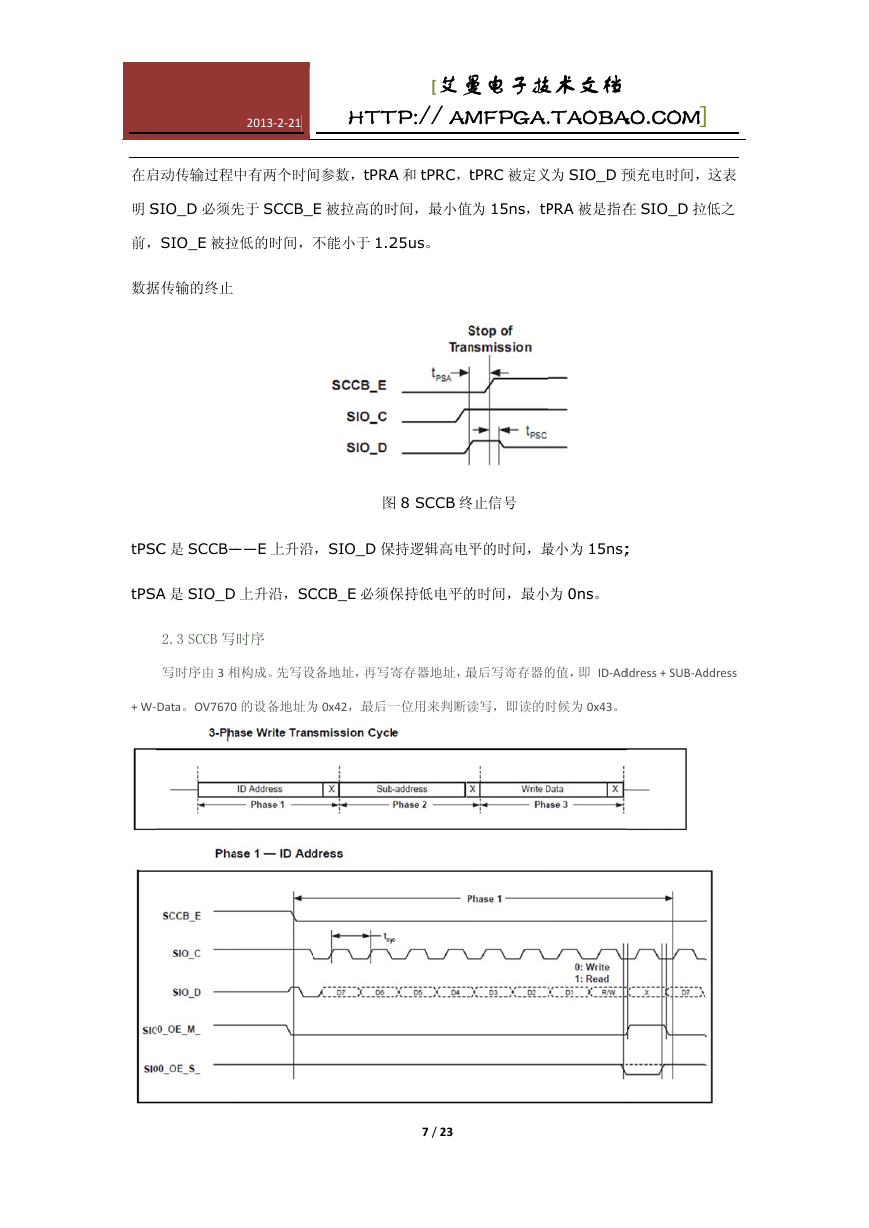

图 1 OV7670 摄

图

摄像头主要特

特性(源自于

于 OV7670 Pre

eliminary Dat

tasheet Versio

on 1.4 Page 1

1)

1. 传感器封

封装结构

OV7670

0 传感器有下

下列两种封装

装形式。

1 / 23

�

[艾曼

TP:// AM

曼电子技

MFPGA.

技术文档

.TAOBA

AO.COM]

HTT

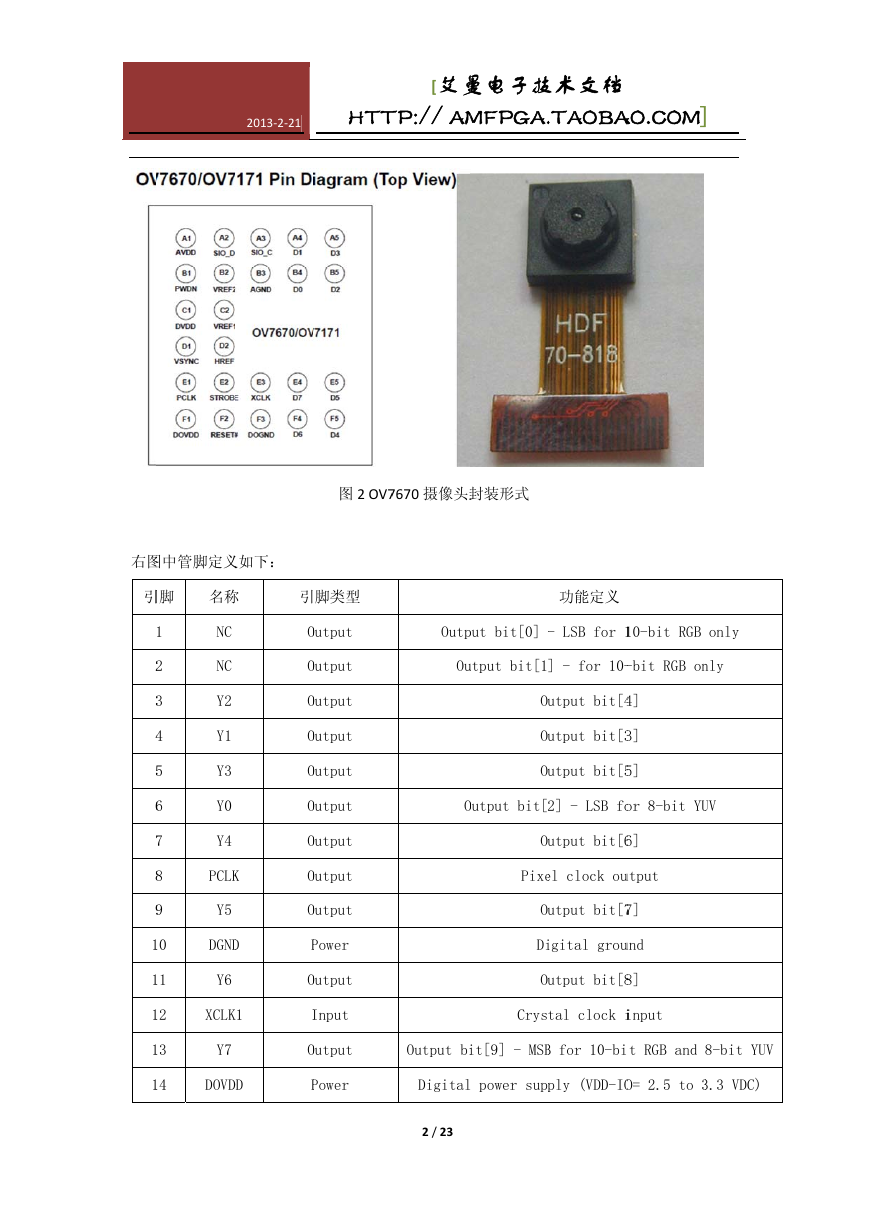

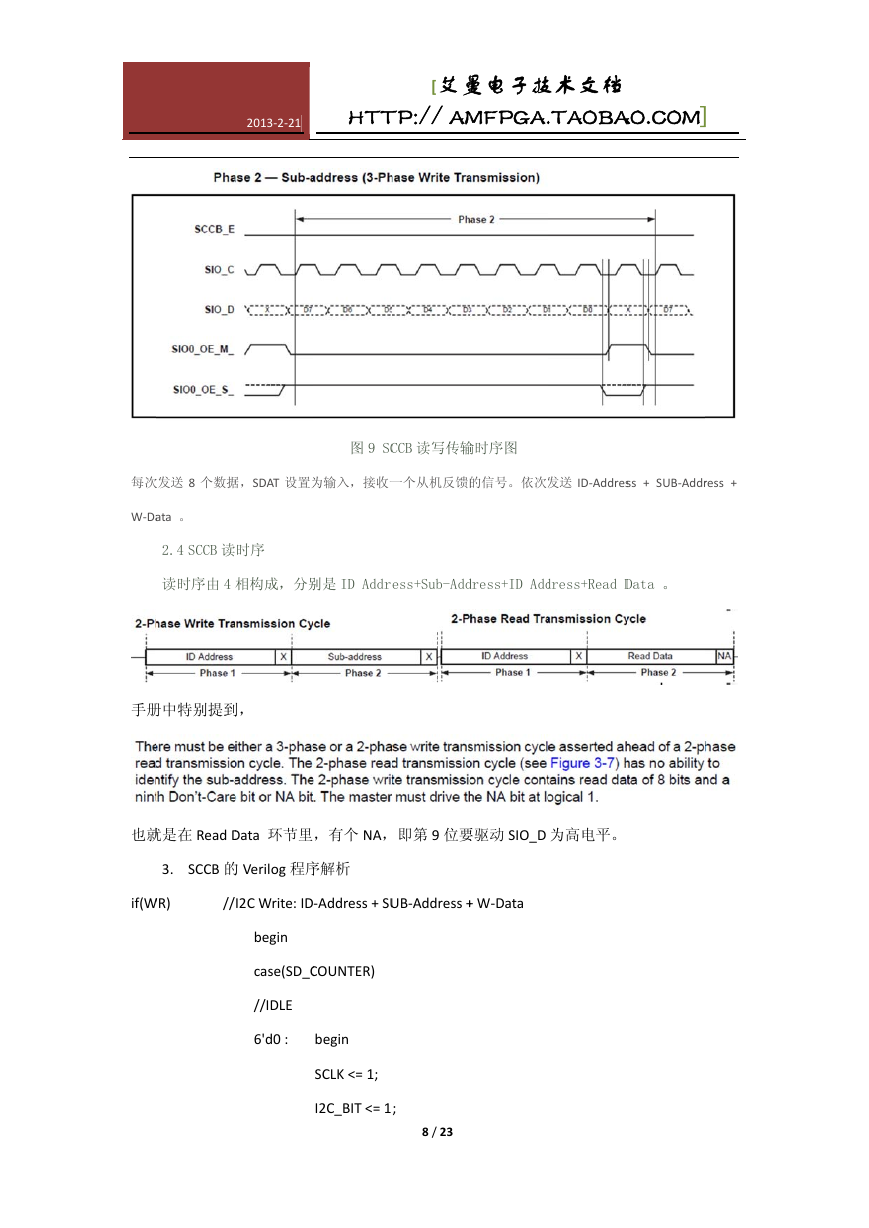

图 2 OV7

7670 摄像头封

封装形式

2013‐2‐21

右图

图中管脚定义

义如下:

引脚 名称

引

称

引

脚类型

功能定义

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

1

11

1

12

1

13

1

14

1

NC

NC

Y2

Y1

Y3

Y0

Y4

K

PCLK

Y5

D

DGND

Y6

Output

O

Output

O

Output

O

Output

O

Output

O

Output

O

Output

O

Output

O

Output

O

Power

P

Output

O

XCLK

K1

Input

I

Y7

Output

O

DOVD

DD

Power

P

Outp

put bit[0] -

- LSB for 1

10-bit RGB

only

Ou

utput bit[1

] - for 10-

-bit RGB on

nly

Ou

utput bit[4

4]

Ou

utput bit[3

3]

Ou

utput bit[5

5]

O

Output bit[2

2] - LSB fo

or 8-bit YU

UV

Ou

utput bit[6

6]

Pixe

el clock ou

utput

Ou

utput bit[7

7]

Di

igital grou

und

Ou

utput bit[8

8]

Crys

tal clock i

input

Output bi

it[9] - MSB

B for 10-bi

t RGB and

8-bit YUV

Digital

power supp

ply (VDD-IO

O= 2.5 to 3

3.3 VDC)

2 / 23

�

[艾曼电子技术文档

2013‐2‐21

HTTP:// AMFPGA.TAOBAO.COM]

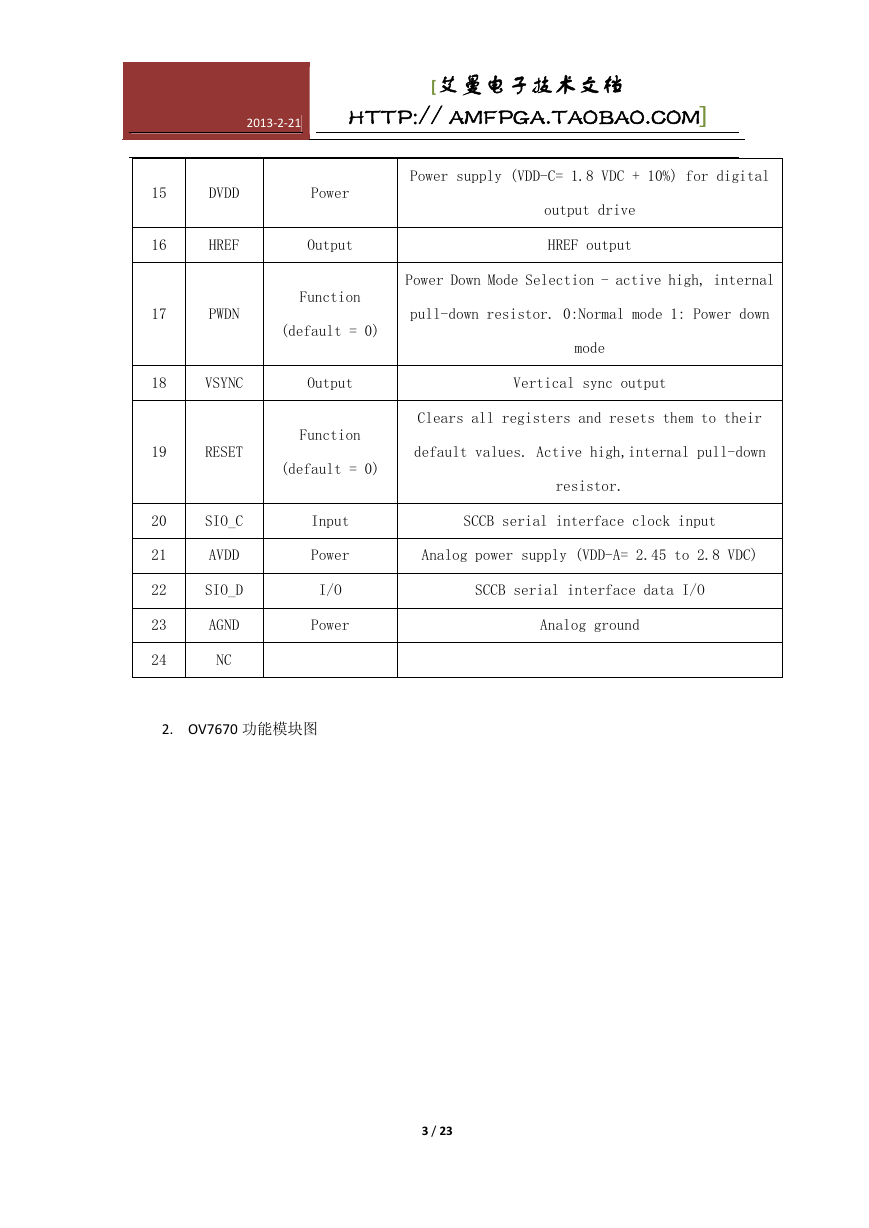

15

DVDD

Power

16

HREF

Output

17

PWDN

Function

(default = 0)

Power supply (VDD-C= 1.8 VDC + 10%) for digital

output drive

HREF output

Power Down Mode Selection - active high, internal

pull-down resistor. 0:Normal mode 1: Power down

mode

18

VSYNC

Output

Vertical sync output

Clears all registers and resets them to their

default values. Active high,internal pull-down

resistor.

SCCB serial interface clock input

Analog power supply (VDD-A= 2.45 to 2.8 VDC)

SCCB serial interface data I/O

Analog ground

19

RESET

Function

(default = 0)

20

21

22

23

24

SIO_C

AVDD

SIO_D

AGND

NC

Input

Power

I/O

Power

2. OV7670 功能模块图

3 / 23

�

[艾曼

TP:// AM

曼电子技

MFPGA.

技术文档

.TAOBA

AO.COM]

HTT

2013‐2‐21

图 3 OV7670

0 功能模块图

图(源自于 O

OV7670 Prelim

minary Datas

sheet Version

n 1.4 Page 2)

由图 3 可知

知,模块由 5

大部分构成

,分别是,1

1:图像模数

数转换(Analog

g Processing)

;2:

测试图案发

发生器(Test

Pattern Gene

erator);3:数

数据输出;4:

656X488 图

图像传感器整

列;5:

SCCB 通信接

接口。

3.1 Image Se

ensor Array

Ov7670

0 传感器阵列

列为 656X488

8,总共有 3

20,128 像素点

点,其中有效

效的为 640X

480,

总共是 307

,200 像素。

2.2 Timing G

Generator

有以下功

功能:

1) 图像

像阵列控制和

和图像帧产生

生;

2) 内部

部时序信号产

产生和分发;

3) 帧率

率时序

4) 自动

动曝光控制

(AEC)相关

寄存器

(C

COM1=0x04;A

AECHH=0x07;

;AECH=0x10,

COM8=0x13

)

5) 外部

部时序输出

(VSYNC,HRE

F/HSYNC,和

PCLK)

4 / 23

�

[艾曼电子技术文档

2013‐2‐21

HTTP:// AMFPGA.TAOBAO.COM]

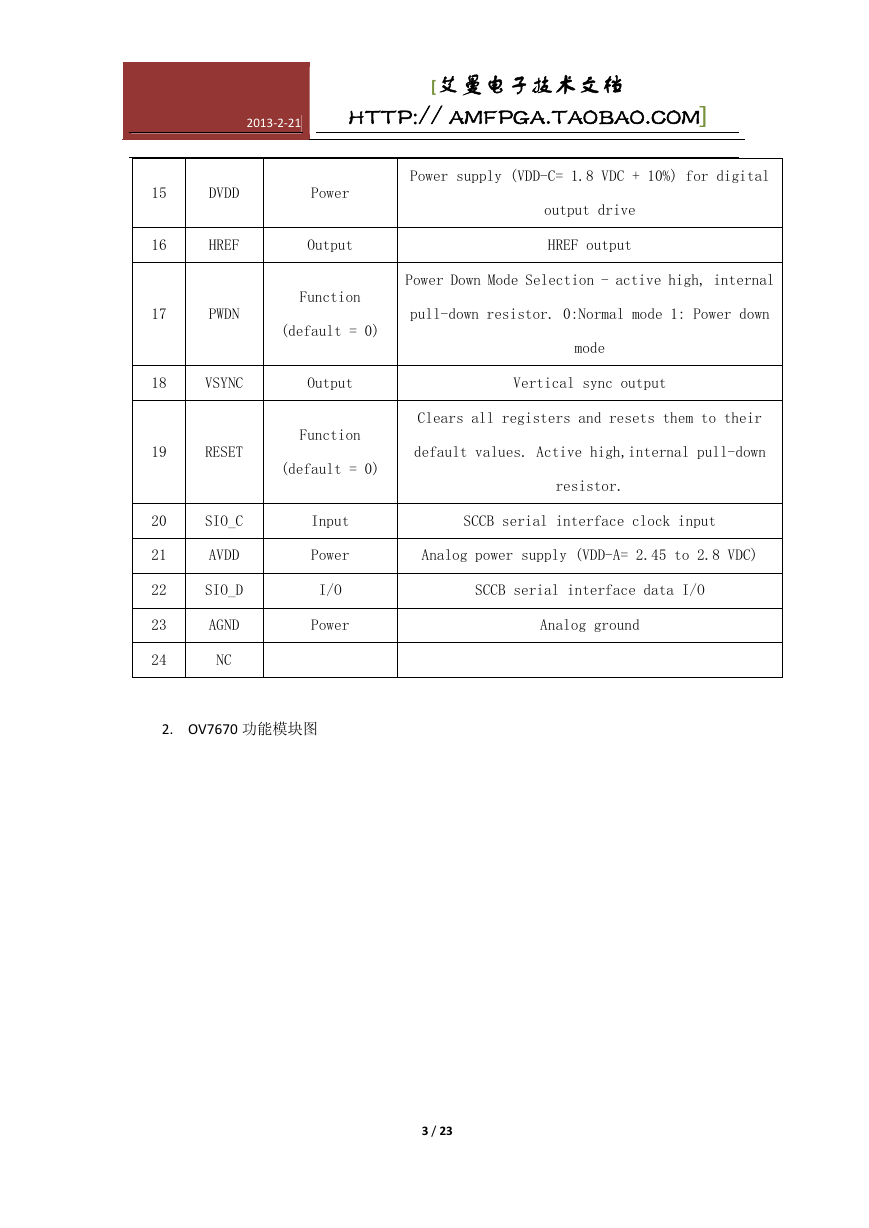

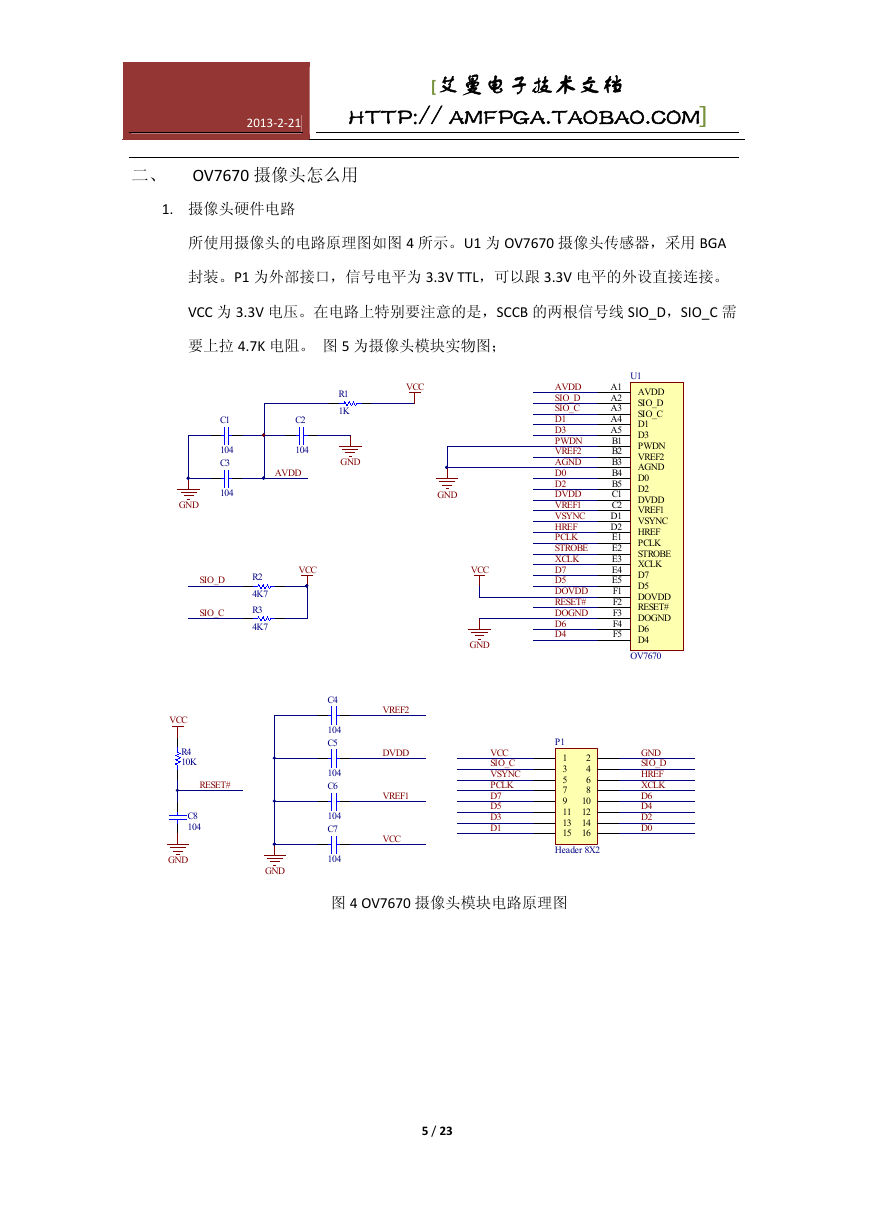

二、 OV7670 摄像头怎么用

1. 摄像头硬件电路

所使用摄像头的电路原理图如图 4 所示。U1 为 OV7670 摄像头传感器,采用 BGA

封装。P1 为外部接口,信号电平为 3.3V TTL,可以跟 3.3V 电平的外设直接连接。

VCC 为 3.3V 电压。在电路上特别要注意的是,SCCB 的两根信号线 SIO_D,SIO_C 需

要上拉 4.7K 电阻。 图 5 为摄像头模块实物图;

R1

1K

GND

C2

104

AVDD

VCC

GND

C1

104

C3

104

GND

VCC

SIO_D

SIO_C

R2

4K7

R3

4K7

VCC

GND

AVDD

SIO_D

SIO_C

D1

D3

PWDN

VREF2

AGND

D0

D2

DVDD

VREF1

VSYNC

HREF

PCLK

STROBE

XCLK

D7

D5

DOVDD

RESET#

DOGND

D6

D4

A1

A2

A3

A4

A5

B1

B2

B3

B4

B5

C1

C2

D1

D2

E1

E2

E3

E4

E5

F1

F2

F3

F4

F5

U1

AVDD

SIO_D

SIO_C

D1

D3

PWDN

VREF2

AGND

D0

D2

DVDD

VREF1

VSYNC

HREF

PCLK

STROBE

XCLK

D7

D5

DOVDD

RESET#

DOGND

D6

D4

OV7670

VCC

R4

10K

RESET#

C8

104

GND

GND

C4

104

C5

104

C6

104

C7

104

VREF2

DVDD

VREF1

VCC

VCC

SIO_C

VSYNC

PCLK

D7

D5

D3

D1

P1

1

3

5

7

9

11

13

15

2

4

6

8

10

12

14

16

Header 8X2

GND

SIO_D

HREF

XCLK

D6

D4

D2

D0

图 4 OV7670 摄像头模块电路原理图

5 / 23

�

[艾曼

TP:// AM

曼电子技

MFPGA.

技术文档

.TAOBA

AO.COM]

HTT

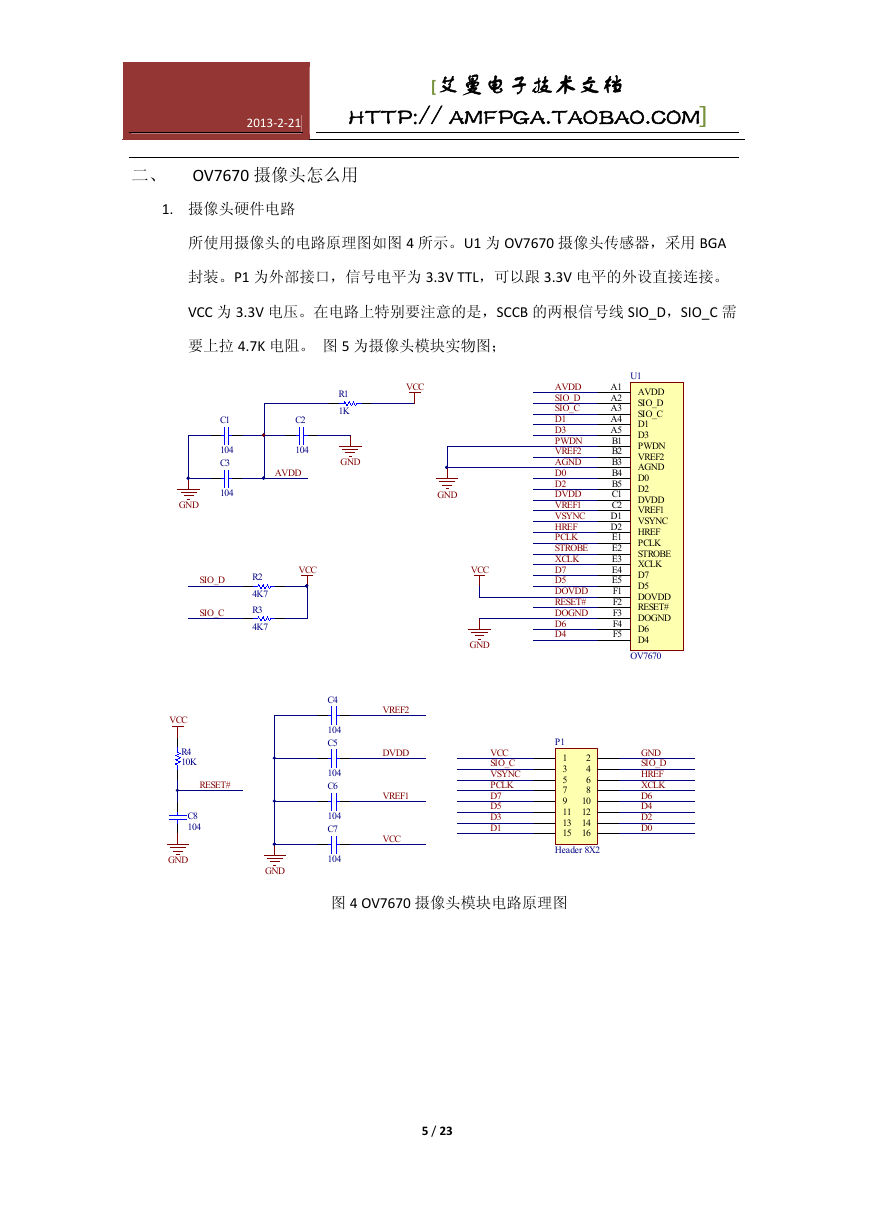

图 5 OV

V7670 摄像头

图

头模块实物图

2013‐2‐21

2. OV7670

0 接口时序

OV7670 接口

口时序包括两

两部分:1)S

SCCB 接口时

时序;2)图像

像数据输出时

时序;

2.1 SCCB 接

接口

图 6 SCCB 功

功能图

SCCB 是欧姆

姆尼图像技术

术公司(OmniV

Vision)开发

发的一种总线

,并广泛的应

应用于 OV 系列

列图

像传

传感器上。SCC

CB 是一种 3 线

线的总线,它

它由 SCCB_E、

SIO_C、SIO_

_D 组成。在为

为了减少引脚

脚的芯

片上

上缩减为 2 根线

线,SIO_C 和

和 SIO_D。

2.2 起始和终

终止时序

图 7 SCCB 起

图

起始信号

6 / 23

�

[艾曼

TP:// AM

曼电子技

MFPGA.

技术文档

.TAOBA

AO.COM]

HTT

2013‐2‐21

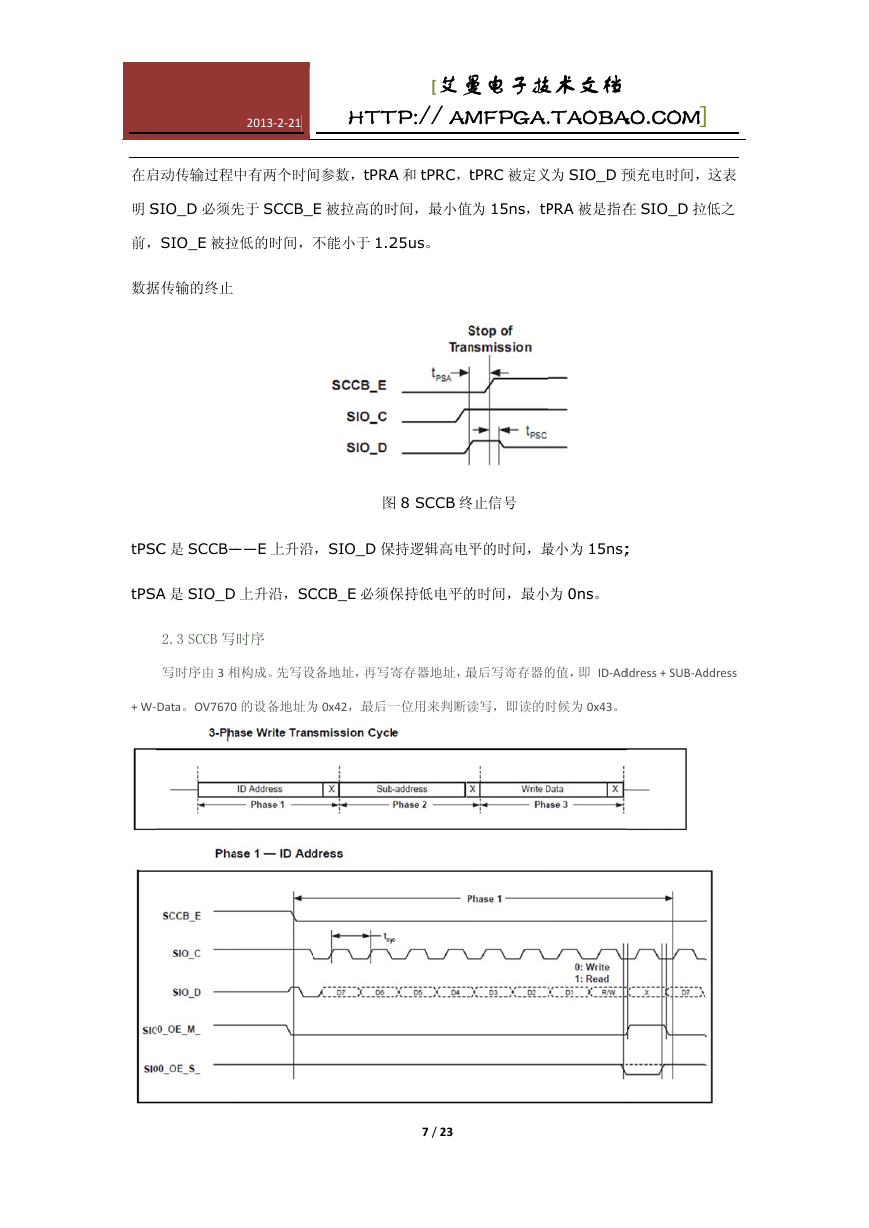

在启

启动传输过程

中有两个时间

间参数,tPRA

A 和 tPRC,t

tPRC 被定义

义为 SIO_D 预

预充电时间,

这表

明 S

SIO_D 必须先

先于 SCCB_

E 被拉高的时

时间,最小值

值为 15ns,tP

PRA 被是指在

在 SIO_D 拉

拉低之

前,

SIO_E 被拉

拉低的时间,不

不能小于 1.2

25us。

数据

据传输的终止

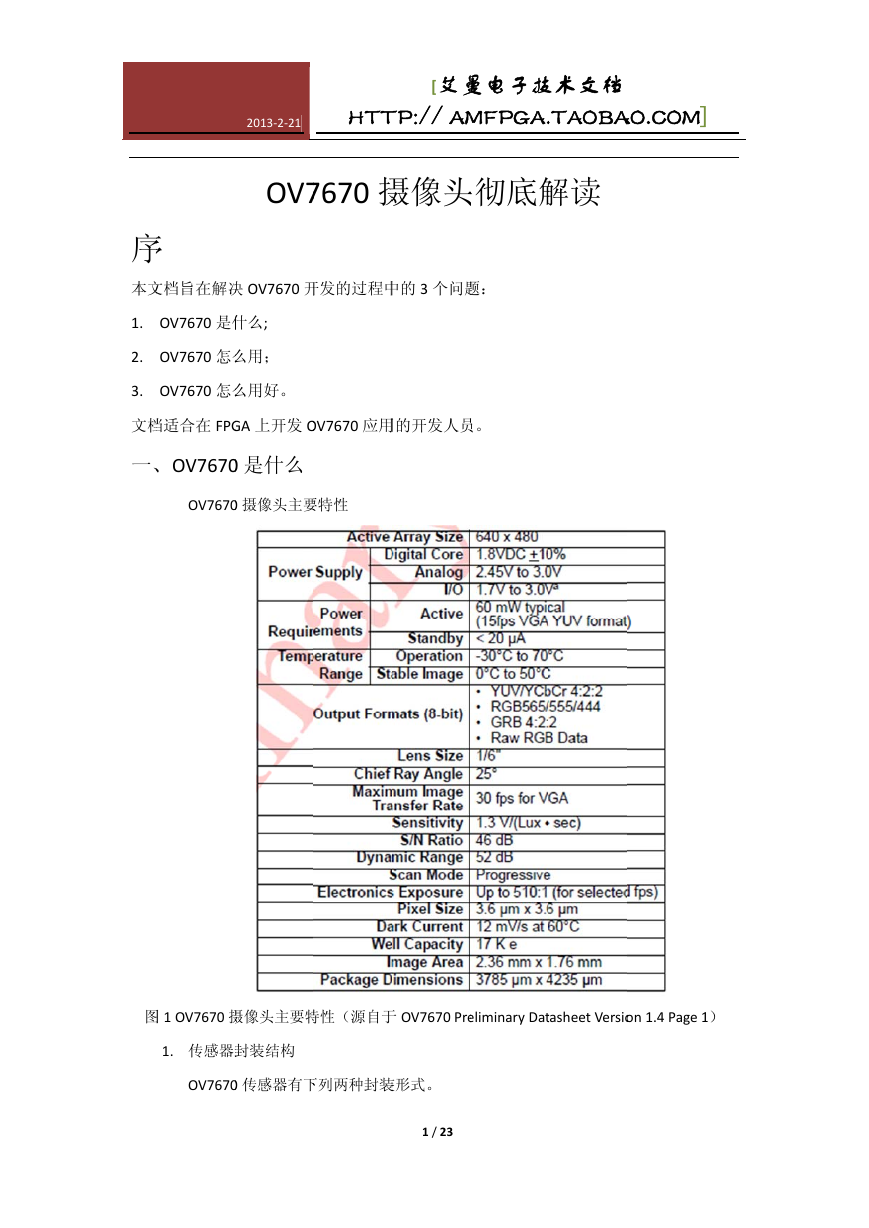

图 8 SCCB 终

图

终止信号

tPSC

C 是 SCCB—

——E 上升沿

,SIO_D 保

保持逻辑高电平

平的时间,最

最小为 15ns;

;

tPSA

A 是 SIO_D

上升沿,SC

CCB_E 必须保

保持低电平的

的时间,最小

为 0ns。

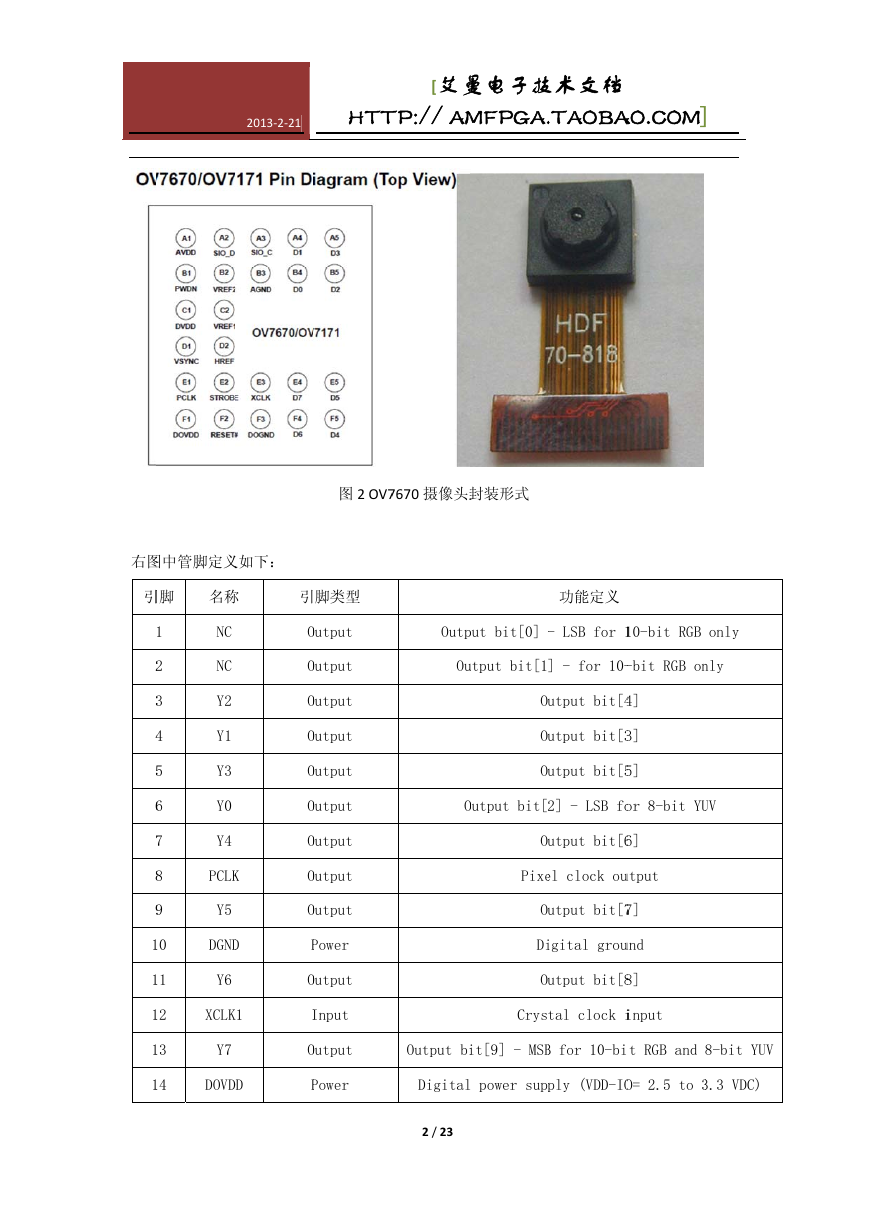

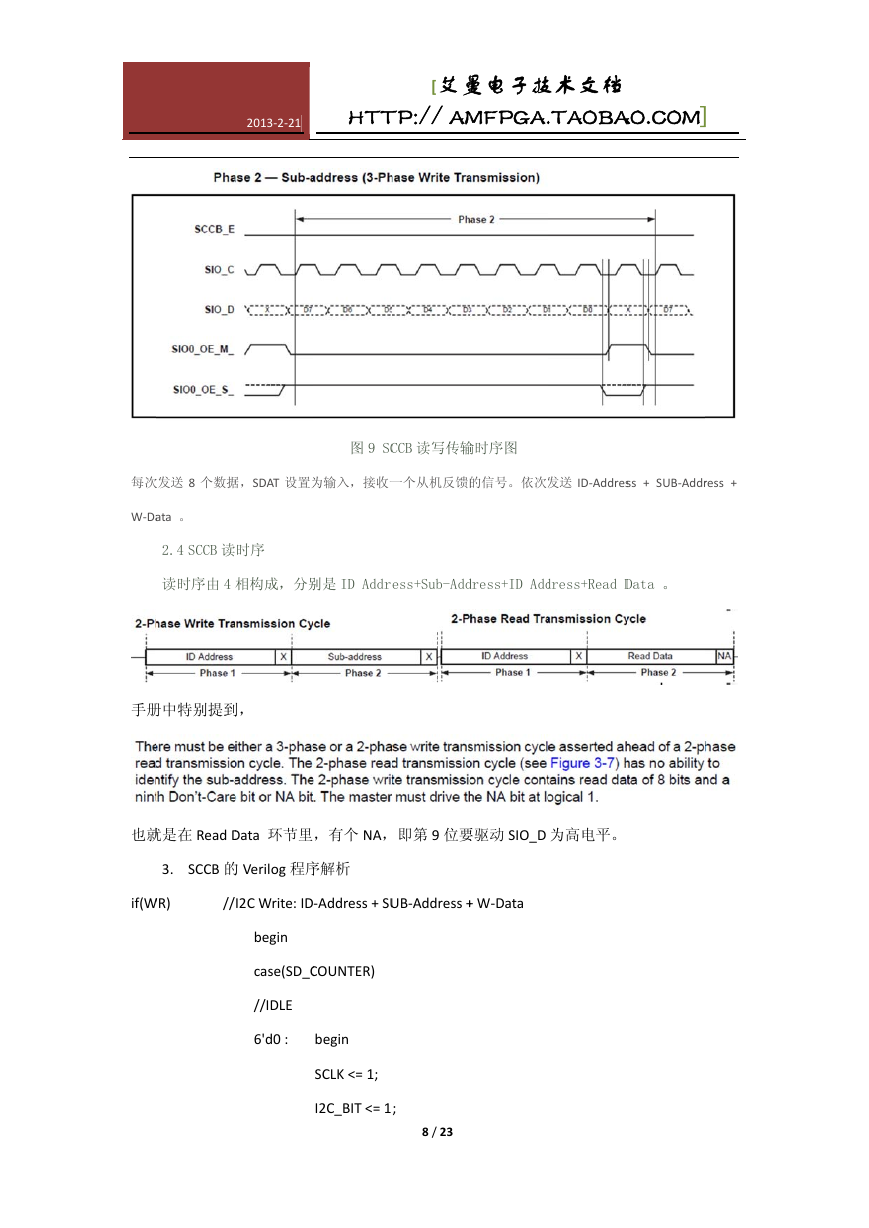

2.3 SCCB 写

时序

写时序由 3 相

相构成。先写设

设备地址,再写寄

寄存器地址,最

最后写寄存器的

的值,即 ID‐Ad

ddress + SUB‐Ad

ddress

+ W‐

Data。OV7670

0 的设备地址为

为 0x42,最后一

一位用来判断读

读写,即读的时

时候为 0x43。

7 / 23

�

[艾曼

TP:// AM

曼电子技

MFPGA.

技术文档

.TAOBA

AO.COM]

HTT

2013‐2‐21

图 9 SC

CCB 读写传输

输时序图

每次

次发送 8 个数据

据,SDAT 设置为

为输入,接收一

一个从机反馈的

的信号。依次发

发送 ID‐Addres

ss + SUB‐Addr

ress +

ess+Sub-Add

dress+ID Add

dress+Read D

Data 。

即第 9 位要

要驱动 SIO_D

为高电平。

W‐Da

ata 。

2.4 SCCB 读

时序

读时序由 4

相构成,分别

别是 ID Addr

手册

册中特别提到

到,

也就

就是在 Read D

Data 环节里

,有个 NA,

3. SCCB 的

的 Verilog 程序

序解析

//

if(W

WR)

I2C Write: ID

‐Address + SU

UB‐Address +

+ W‐Data

begin

case(SD_C

COUNTER)

//IDLE

6'd0 :

begin

SCLK <= 1;

I2C_BIT <= 1

;

8 / 23

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc